Henk Corporaal EE department Delft Univ. of Technology h. corporaal@et. tudelft. nl http: //cs. et. tudelft. nl

Henk Corporaal EE department Delft Univ. of Technology h. corporaal@et. tudelft. nl http: //cs. et. tudelft. nl

Topics

Topics

MOVE project goals

MOVE project goals

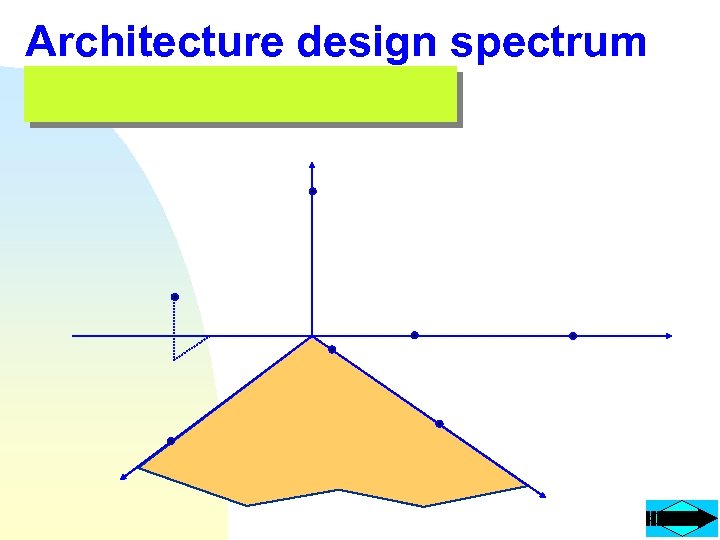

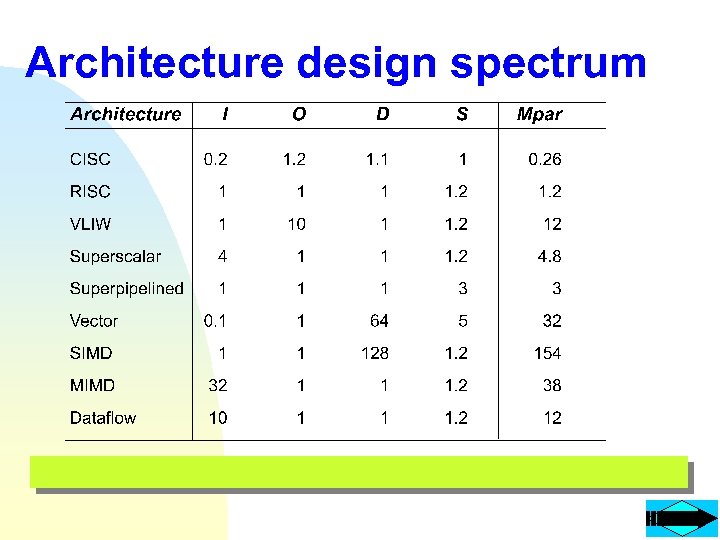

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

Architecture design spectrum

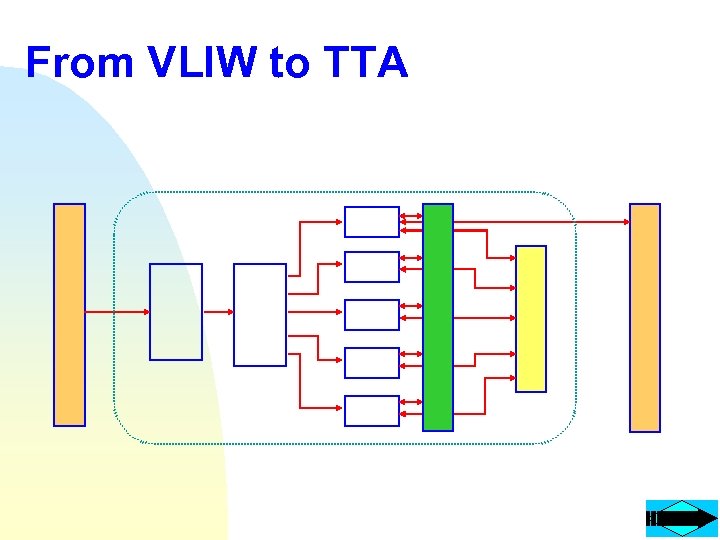

From VLIW to TTA

From VLIW to TTA

From VLIW to TTA

From VLIW to TTA

From VLIW to TTA

From VLIW to TTA

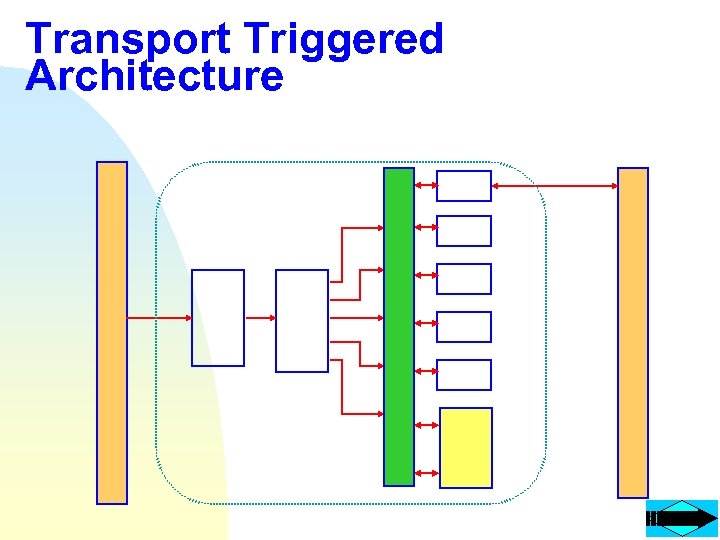

Transport Triggered Architecture

Transport Triggered Architecture

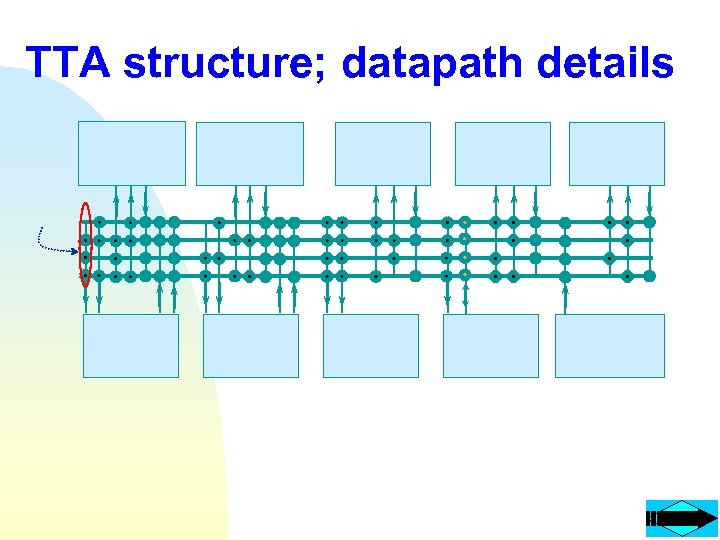

TTA structure; datapath details

TTA structure; datapath details

TTA characteristics

TTA characteristics

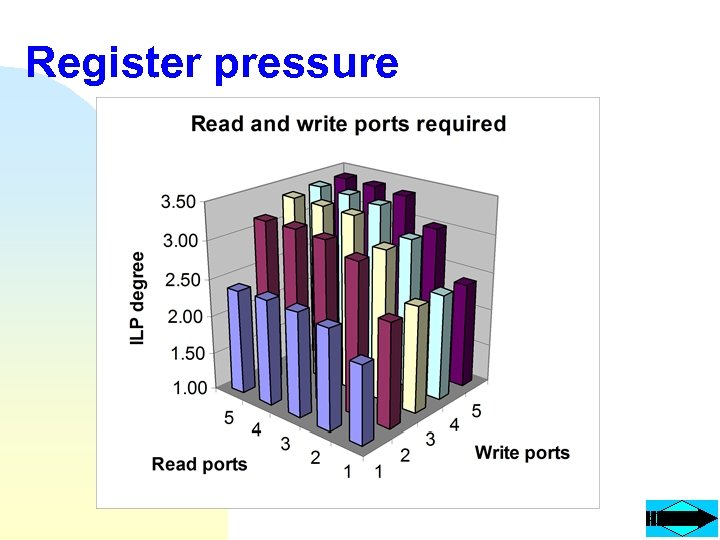

Register pressure

Register pressure

TTA characteristics

TTA characteristics

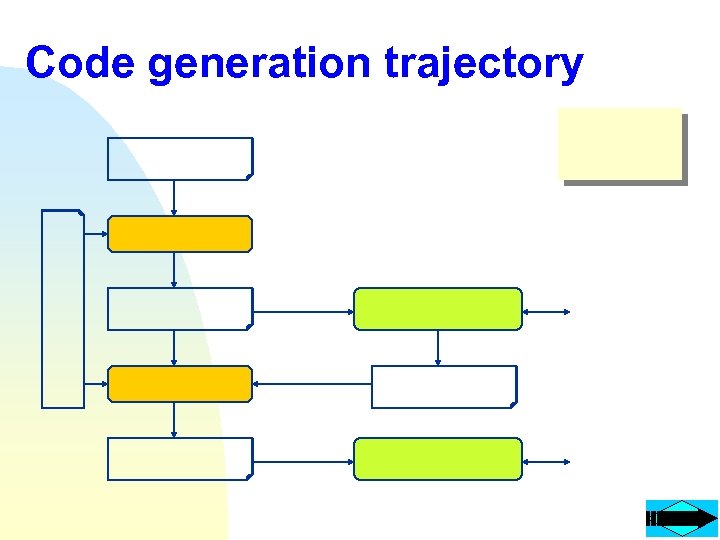

Code generation trajectory

Code generation trajectory

TTA compiler characteristics

TTA compiler characteristics

Code generation for TTAs

Code generation for TTAs

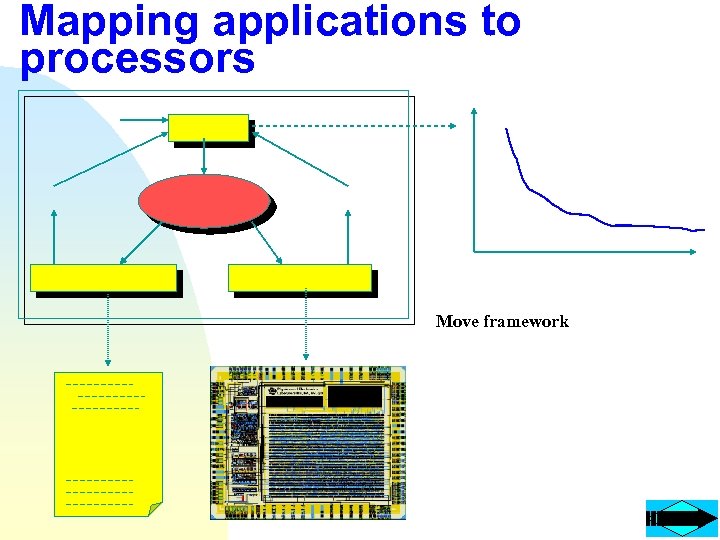

Mapping applications to processors

Mapping applications to processors

Mapping applications to processors Move framework

Mapping applications to processors Move framework

Achievements within the MOVE project

Achievements within the MOVE project

Video stretcher board containing TTA

Video stretcher board containing TTA

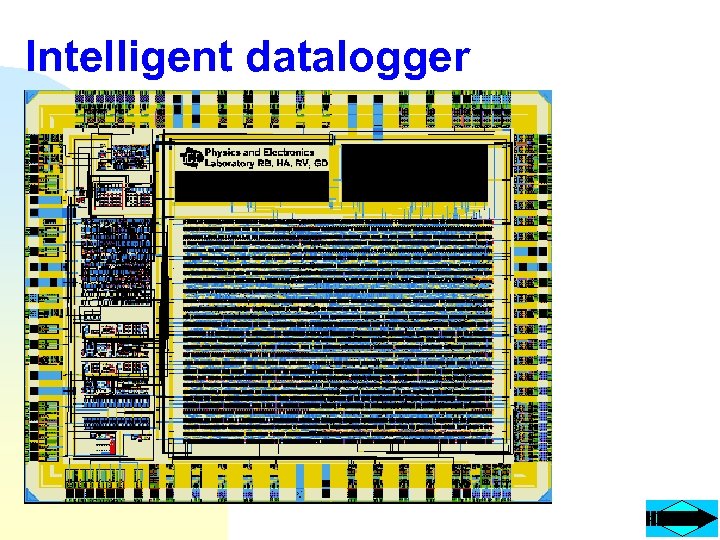

Intelligent datalogger

Intelligent datalogger

TTA related research

TTA related research

Ro. D: Register on Demand scheduling

Ro. D: Register on Demand scheduling

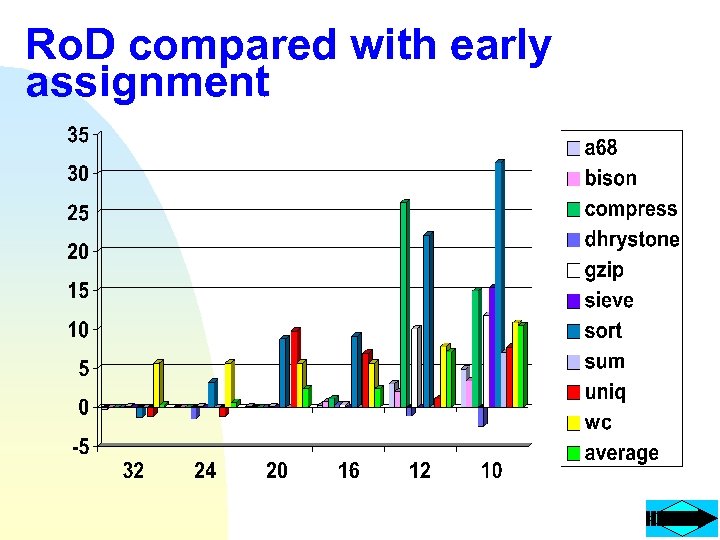

Ro. D compared with early assignment

Ro. D compared with early assignment

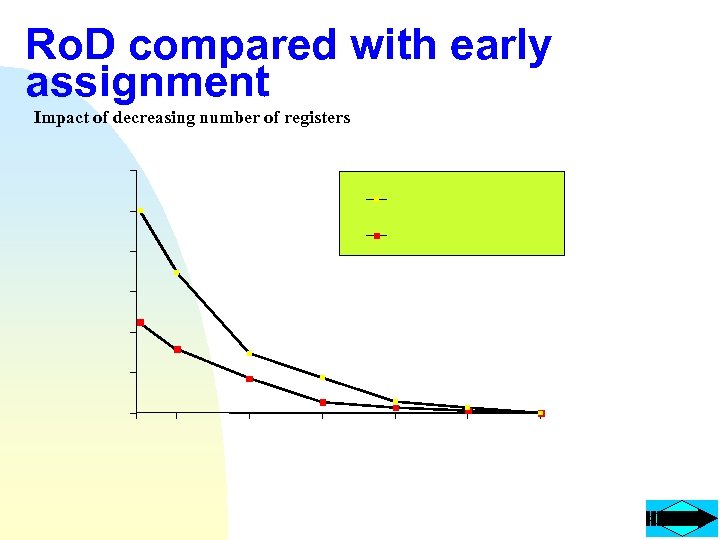

Ro. D compared with early assignment Impact of decreasing number of registers

Ro. D compared with early assignment Impact of decreasing number of registers

Special Functionality: SFUs

Special Functionality: SFUs

Mapping applications to processors

Mapping applications to processors

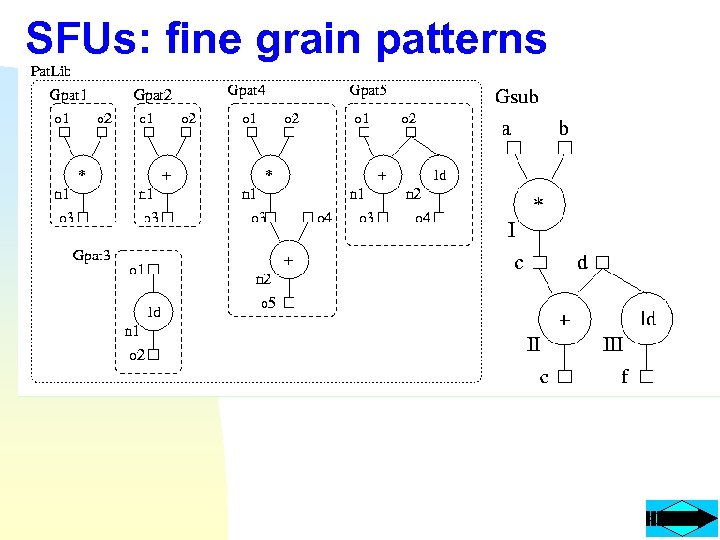

SFUs: fine grain patterns

SFUs: fine grain patterns

SFUs: Pattern identification

SFUs: Pattern identification

SFUs: fine grain patterns

SFUs: fine grain patterns

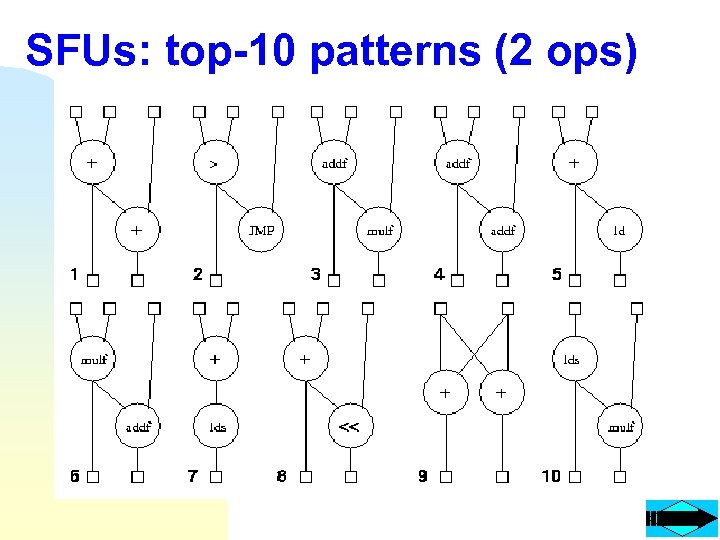

SFUs: top-10 patterns (2 ops)

SFUs: top-10 patterns (2 ops)

SFUs: conclusions

SFUs: conclusions

Source-to. Source transformations

Source-to. Source transformations

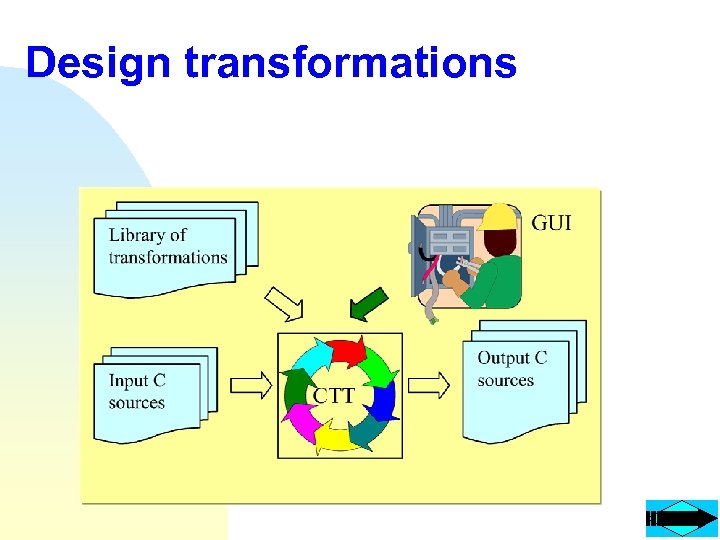

Design transformations

Design transformations

Structure of transformation

Structure of transformation

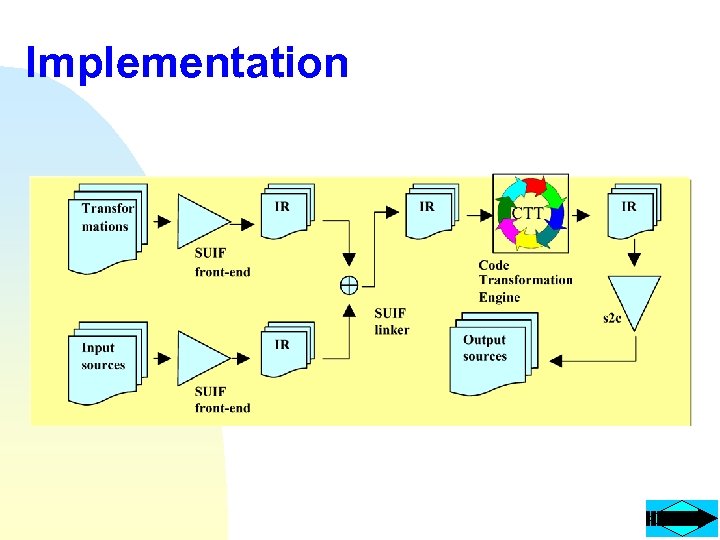

Implementation

Implementation

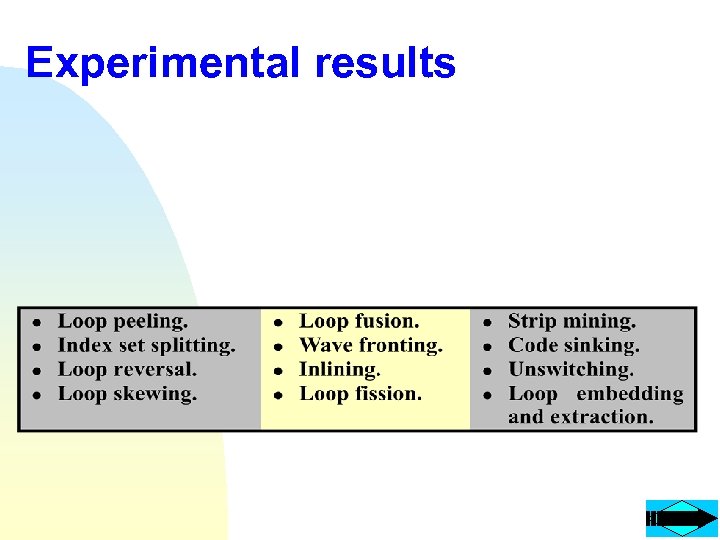

Experimental results

Experimental results

Partitioning your program for Multiprocessor single chip solutions

Partitioning your program for Multiprocessor single chip solutions

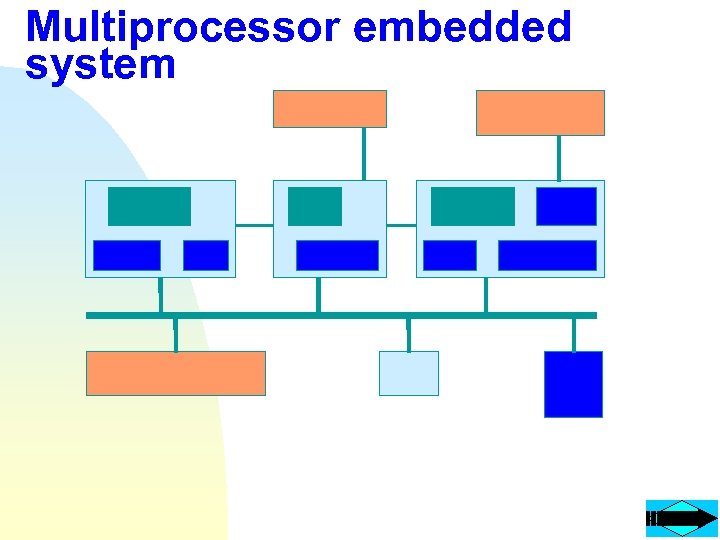

Multiprocessor embedded system

Multiprocessor embedded system

Design transformations

Design transformations

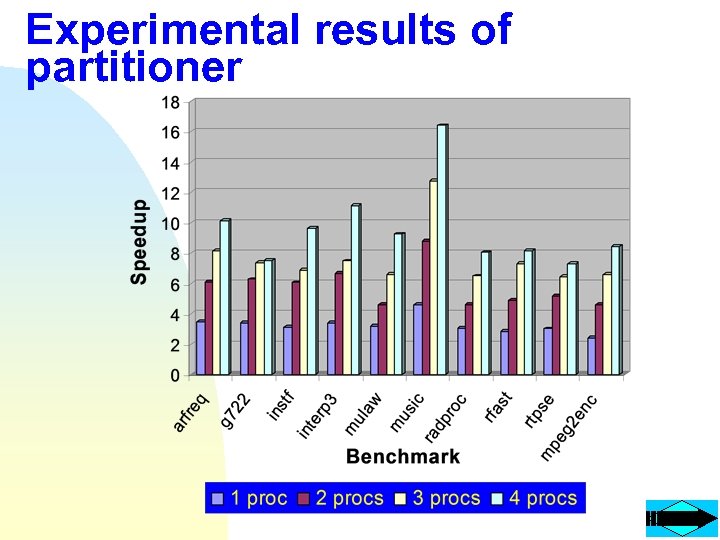

Experimental results of partitioner

Experimental results of partitioner

Global program optimizations

Global program optimizations

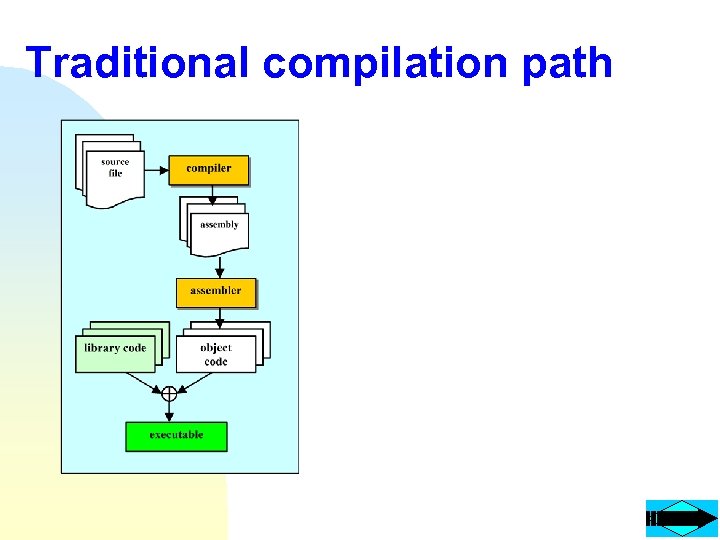

Traditional compilation path

Traditional compilation path

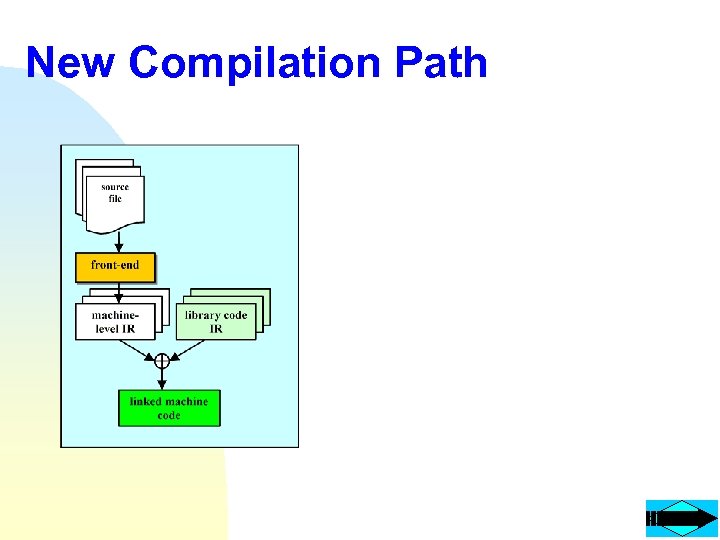

New Compilation Path

New Compilation Path

Inter-module Register Allocation

Inter-module Register Allocation

Fixed-point conversion: motivation

Fixed-point conversion: motivation

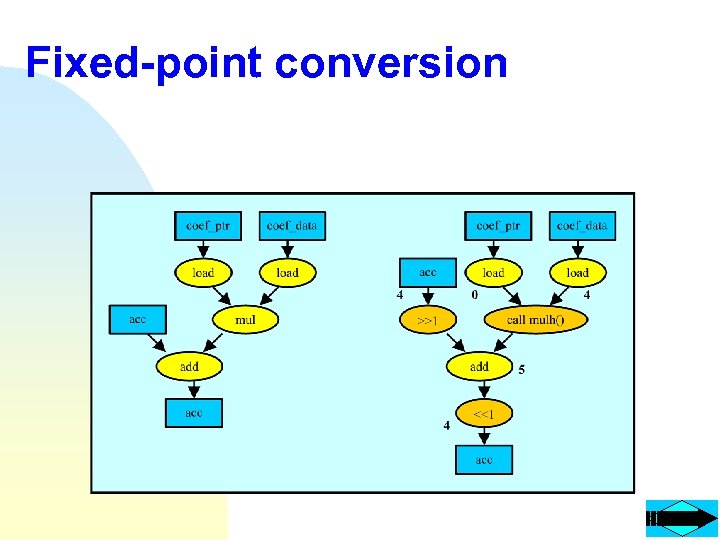

Fixed-point conversion

Fixed-point conversion

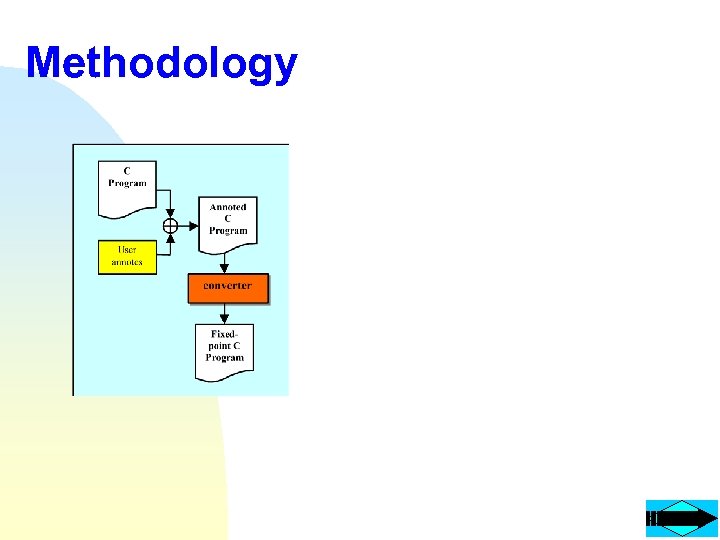

Methodology

Methodology

Link-time code conversion

Link-time code conversion

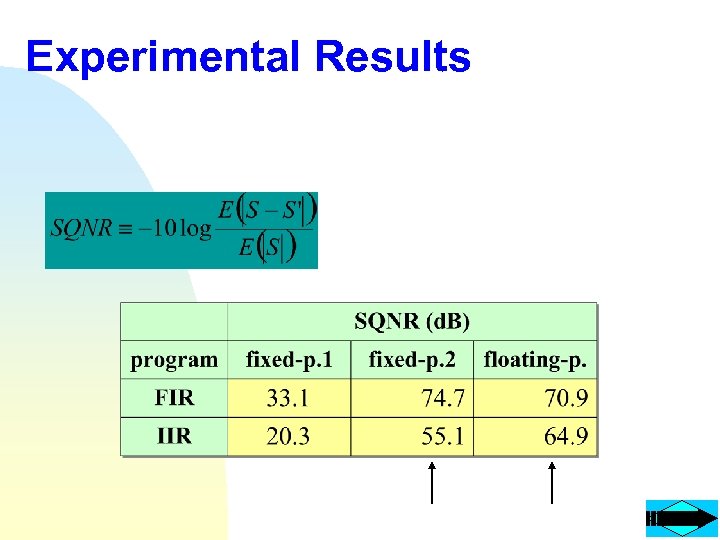

Experimental Results

Experimental Results

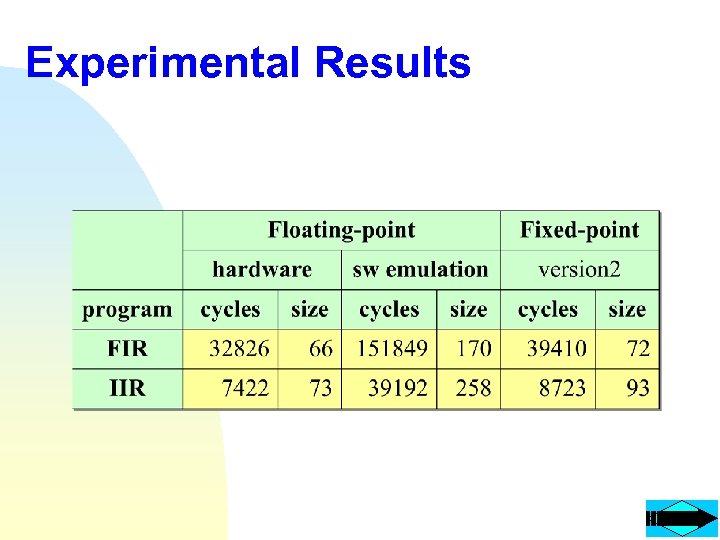

Experimental Results

Experimental Results

What next? L: design level (e. g. architecture, implementation or realization level) A: application compononents D: dependences between application components N: hardware component C: connections between hardware components

What next? L: design level (e. g. architecture, implementation or realization level) A: application compononents D: dependences between application components N: hardware component C: connections between hardware components

Conclusions / Discussion

Conclusions / Discussion