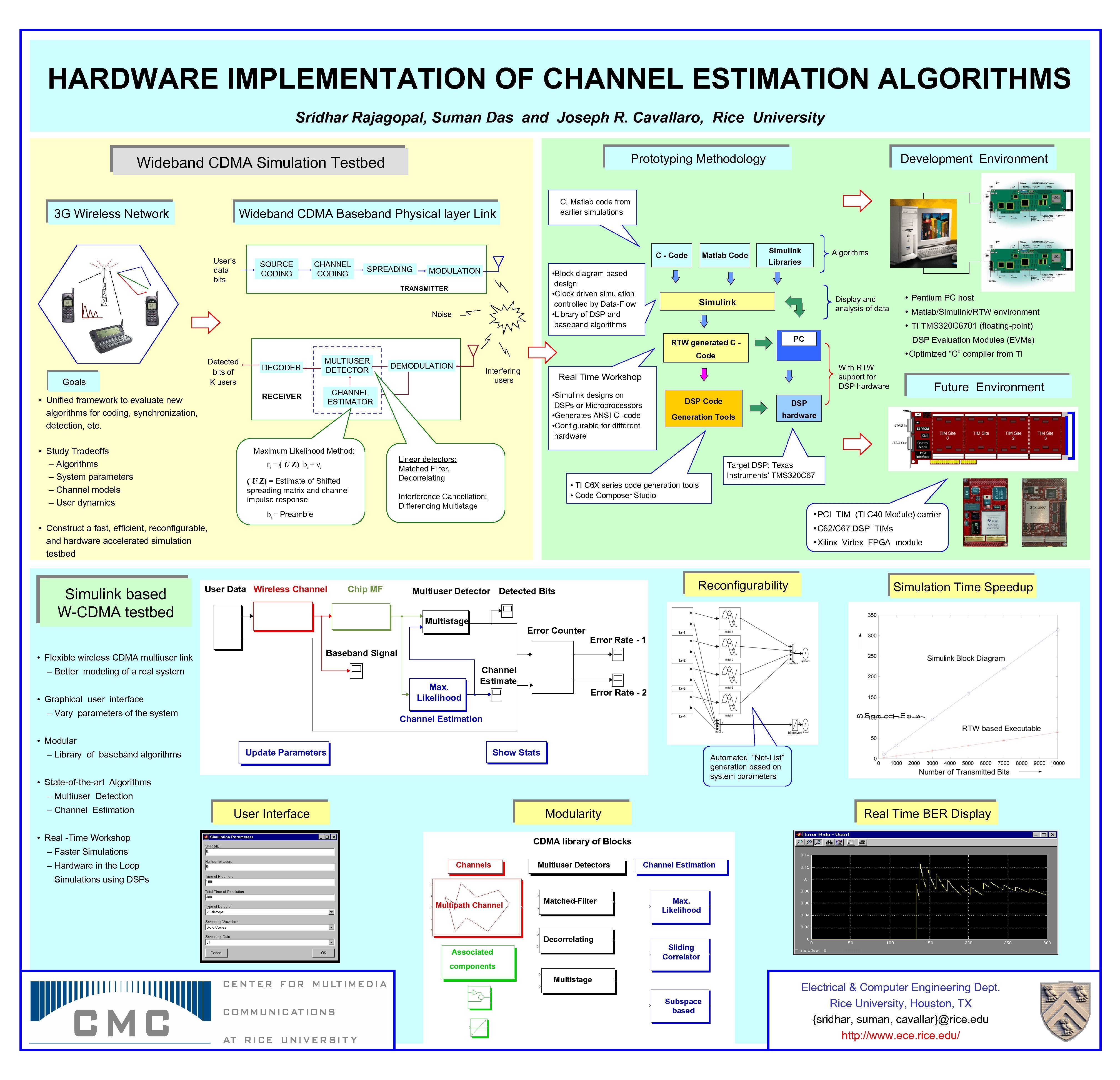

HARDWARE IMPLEMENTATION OF CHANNEL ESTIMATION ALGORITHMS Sridhar Rajagopal, Suman Das and Joseph R. Cavallaro, Rice University Prototyping Methodology Wideband CDMA Simulation Testbed 3 G Wireless Network C, Matlab code from earlier simulations Wideband CDMA Baseband Physical layer Link User’s data bits C - Code SOURCE CODING CHANNEL CODING SPREADING Development Environment MODULATION Matlab Code • Block diagram based design • Clock driven simulation controlled by Data-Flow • Library of DSP and baseband algorithms TRANSMITTER Noise Simulink Libraries Display and analysis of data Simulink Goals DECODER MULTIUSER DETECTOR PC • Study Tradeoffs – Algorithms – System parameters – Channel models – User dynamics • Optimized “C” compiler from TI Maximum Likelihood Method: ri = ( U Z) bi + ni ( U Z) = Estimate of Shifted spreading matrix and channel impulse response bi = Preamble With RTW support for DSP hardware Real Time Workshop CHANNEL ESTIMATOR RECEIVER • Unified framework to evaluate new algorithms for coding, synchronization, detection, etc. Interfering users • Simulink designs on DSPs or Microprocessors • Generates ANSI C -code • Configurable for different hardware Linear detectors: Matched Filter, Decorrelating DSP Code Generation Tools Future Environment DSP hardware Target DSP: Texas Instruments’ TMS 320 C 67 • TI C 6 X series code generation tools • Code Composer Studio Interference Cancellation: Differencing Multistage • PCI TIM (TI C 40 Module) carrier • Construct a fast, efficient, reconfigurable, and hardware accelerated simulation testbed Simulink based W-CDMA testbed • Matlab/Simulink/RTW environment DSP Evaluation Modules (EVMs) Code DEMODULATION • Pentium PC host • TI TMS 320 C 6701 (floating-point) RTW generated C Detected bits of K users Algorithms • C 62/C 67 DSP TIMs • Xilinx Virtex FPGA module User Data Wireless Channel Chip MF Reconfigurability Multiuser Detector Detected Bits Multistage Error Counter Simulation Time Speedup Error Rate - 1 Baseband Signal • Flexible wireless CDMA multiuser link – Better modeling of a real system Max. Likelihood • Graphical user interface – Vary parameters of the system Channel Estimate Error Rate - 2 Channel Estimation • Modular – Library of baseband algorithms Update Parameters Show Stats Automated “Net-List” generation based on system parameters • State-of-the-art Algorithms – Multiuser Detection – Channel Estimation User Interface Modularity • Real -Time Workshop Real Time BER Display CDMA library of Blocks – Faster Simulations – Hardware in the Loop Channels Multiuser Detectors Channel Estimation Simulations using DSPs Multipath Channel Matched-Filter Decorrelating Associated Max. Likelihood Sliding Correlator components Multistage Subspace based Electrical & Computer Engineering Dept. Rice University, Houston, TX {sridhar, suman, cavallar}@rice. edu http: //www. ece. rice. edu/

HARDWARE IMPLEMENTATION OF CHANNEL ESTIMATION ALGORITHMS Sridhar Rajagopal, Suman Das and Joseph R. Cavallaro, Rice University Prototyping Methodology Wideband CDMA Simulation Testbed 3 G Wireless Network C, Matlab code from earlier simulations Wideband CDMA Baseband Physical layer Link User’s data bits C - Code SOURCE CODING CHANNEL CODING SPREADING Development Environment MODULATION Matlab Code • Block diagram based design • Clock driven simulation controlled by Data-Flow • Library of DSP and baseband algorithms TRANSMITTER Noise Simulink Libraries Display and analysis of data Simulink Goals DECODER MULTIUSER DETECTOR PC • Study Tradeoffs – Algorithms – System parameters – Channel models – User dynamics • Optimized “C” compiler from TI Maximum Likelihood Method: ri = ( U Z) bi + ni ( U Z) = Estimate of Shifted spreading matrix and channel impulse response bi = Preamble With RTW support for DSP hardware Real Time Workshop CHANNEL ESTIMATOR RECEIVER • Unified framework to evaluate new algorithms for coding, synchronization, detection, etc. Interfering users • Simulink designs on DSPs or Microprocessors • Generates ANSI C -code • Configurable for different hardware Linear detectors: Matched Filter, Decorrelating DSP Code Generation Tools Future Environment DSP hardware Target DSP: Texas Instruments’ TMS 320 C 67 • TI C 6 X series code generation tools • Code Composer Studio Interference Cancellation: Differencing Multistage • PCI TIM (TI C 40 Module) carrier • Construct a fast, efficient, reconfigurable, and hardware accelerated simulation testbed Simulink based W-CDMA testbed • Matlab/Simulink/RTW environment DSP Evaluation Modules (EVMs) Code DEMODULATION • Pentium PC host • TI TMS 320 C 6701 (floating-point) RTW generated C Detected bits of K users Algorithms • C 62/C 67 DSP TIMs • Xilinx Virtex FPGA module User Data Wireless Channel Chip MF Reconfigurability Multiuser Detector Detected Bits Multistage Error Counter Simulation Time Speedup Error Rate - 1 Baseband Signal • Flexible wireless CDMA multiuser link – Better modeling of a real system Max. Likelihood • Graphical user interface – Vary parameters of the system Channel Estimate Error Rate - 2 Channel Estimation • Modular – Library of baseband algorithms Update Parameters Show Stats Automated “Net-List” generation based on system parameters • State-of-the-art Algorithms – Multiuser Detection – Channel Estimation User Interface Modularity • Real -Time Workshop Real Time BER Display CDMA library of Blocks – Faster Simulations – Hardware in the Loop Channels Multiuser Detectors Channel Estimation Simulations using DSPs Multipath Channel Matched-Filter Decorrelating Associated Max. Likelihood Sliding Correlator components Multistage Subspace based Electrical & Computer Engineering Dept. Rice University, Houston, TX {sridhar, suman, cavallar}@rice. edu http: //www. ece. rice. edu/

![]()