f65bde162713f2e03132ee28b785b438.ppt

- Количество слайдов: 35

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2015/09/10 HDL T. -C. Huang / NCUE Fall 2014 1

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2015/09/10 HDL T. -C. Huang / NCUE Fall 2014 1

Brief Syllabus Ø Visit http: //testlab. ncue. edu. tw/tch for Details Ø Not Programming Only But Also Logic Design Ø Major Content: 1. 2. 3. 4. 5. 6. HDL External and Internal Data Structures of HDLs Logic Design using Verilog Introduction to Rapid Prototyping Introduction to SOPC Introduction to Cell-Base Design Introduction to CPU Design using Verilog T. -C. Huang / NCUE Fall 2014 2

Brief Syllabus Ø Visit http: //testlab. ncue. edu. tw/tch for Details Ø Not Programming Only But Also Logic Design Ø Major Content: 1. 2. 3. 4. 5. 6. HDL External and Internal Data Structures of HDLs Logic Design using Verilog Introduction to Rapid Prototyping Introduction to SOPC Introduction to Cell-Base Design Introduction to CPU Design using Verilog T. -C. Huang / NCUE Fall 2014 2

Hardware-Descriptive Language 硬體描述語言 Ø Ø HDL 軟硬有別:Speed, Power, (Chip) Area, Cost, EZ 軟硬不分:軟硬體在一定前提下可以互換 軟硬共設計:考慮前提決定軟硬架構比例最佳化 This Course: 1. Logic Design硬體基礎 (電子二) 2. 描述硬體的軟體 3. 設計CPU、指令及其組合語言 4. 設計組合語言軟體 5. 由C語言演算法轉換成Verilog硬體有限狀態機 6. (甄戰 !!!) T. -C. Huang / NCUE Fall 2014 3

Hardware-Descriptive Language 硬體描述語言 Ø Ø HDL 軟硬有別:Speed, Power, (Chip) Area, Cost, EZ 軟硬不分:軟硬體在一定前提下可以互換 軟硬共設計:考慮前提決定軟硬架構比例最佳化 This Course: 1. Logic Design硬體基礎 (電子二) 2. 描述硬體的軟體 3. 設計CPU、指令及其組合語言 4. 設計組合語言軟體 5. 由C語言演算法轉換成Verilog硬體有限狀態機 6. (甄戰 !!!) T. -C. Huang / NCUE Fall 2014 3

Overview on HDL Ø Ø Ø Ø Introduction to General HDL including NETLIST Competition btw VHDL and Verilog HDL Tools Application of VLSI HDL Y-Chart: Level and Views Modeling Quick Tutorial using 1 or 2 Tools 1. Gate-Level 2. Behavioral Mode Ø Preparation for Next Course HDL T. -C. Huang / NCUE Fall 2014 4

Overview on HDL Ø Ø Ø Ø Introduction to General HDL including NETLIST Competition btw VHDL and Verilog HDL Tools Application of VLSI HDL Y-Chart: Level and Views Modeling Quick Tutorial using 1 or 2 Tools 1. Gate-Level 2. Behavioral Mode Ø Preparation for Next Course HDL T. -C. Huang / NCUE Fall 2014 4

Usual Applications of HDLs Ø Ø Ø HDL Logic Simulation and Verification Synthesis for FPGA/So. PC Prototyping Synthesis for Cell-base VLSI Design Soft Intellectual Property (IP) Design Modeling Low or Equal Level Circuit T. -C. Huang / NCUE Fall 2014 5

Usual Applications of HDLs Ø Ø Ø HDL Logic Simulation and Verification Synthesis for FPGA/So. PC Prototyping Synthesis for Cell-base VLSI Design Soft Intellectual Property (IP) Design Modeling Low or Equal Level Circuit T. -C. Huang / NCUE Fall 2014 5

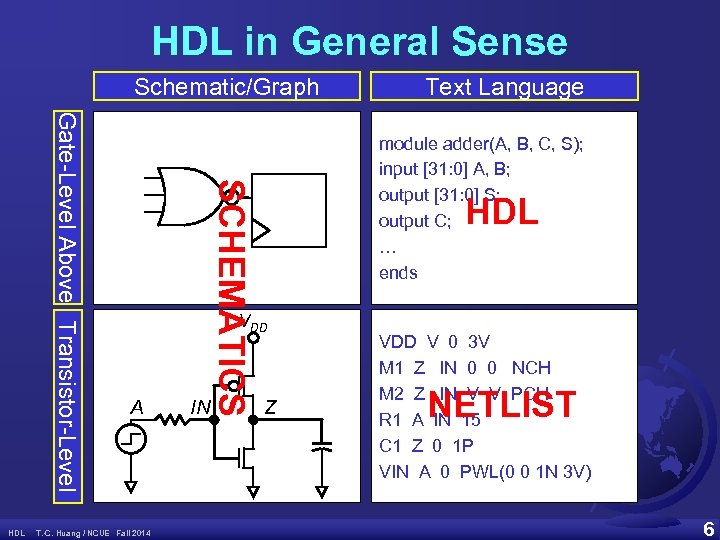

HDL in General Sense Schematic/Graph SCHEMATICS Gate-Level Above Transistor-Level HDL module adder(A, B, C, S); input [31: 0] A, B; output [31: 0] S; output C; … ends HDL VDD A T. -C. Huang / NCUE Fall 2014 IN Text Language Z VDD V 0 3 V M 1 Z IN 0 0 NCH M 2 Z IN V V PCH R 1 A IN 15 C 1 Z 0 1 P VIN A 0 PWL(0 0 1 N 3 V) NETLIST 6

HDL in General Sense Schematic/Graph SCHEMATICS Gate-Level Above Transistor-Level HDL module adder(A, B, C, S); input [31: 0] A, B; output [31: 0] S; output C; … ends HDL VDD A T. -C. Huang / NCUE Fall 2014 IN Text Language Z VDD V 0 3 V M 1 Z IN 0 0 NCH M 2 Z IN V V PCH R 1 A IN 15 C 1 Z 0 1 P VIN A 0 PWL(0 0 1 N 3 V) NETLIST 6

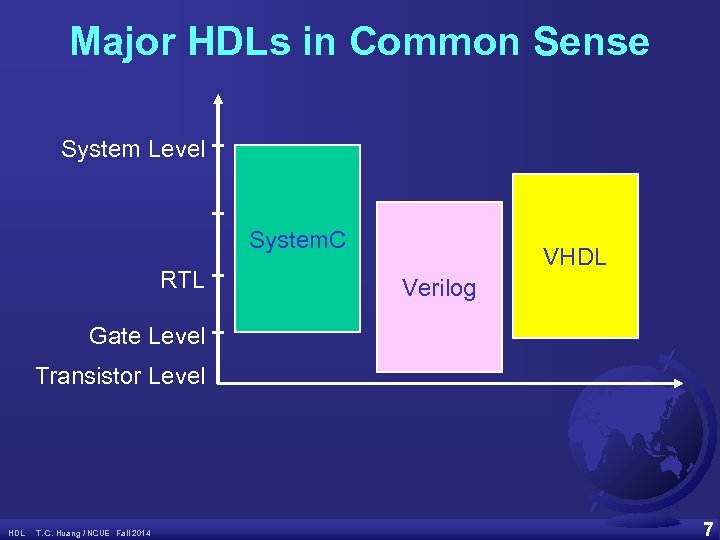

Major HDLs in Common Sense System Level System. C RTL Verilog Industry Verilog VHDL Academic VHDL Gate Level Transistor Level HDL T. -C. Huang / NCUE Fall 2014 7

Major HDLs in Common Sense System Level System. C RTL Verilog Industry Verilog VHDL Academic VHDL Gate Level Transistor Level HDL T. -C. Huang / NCUE Fall 2014 7

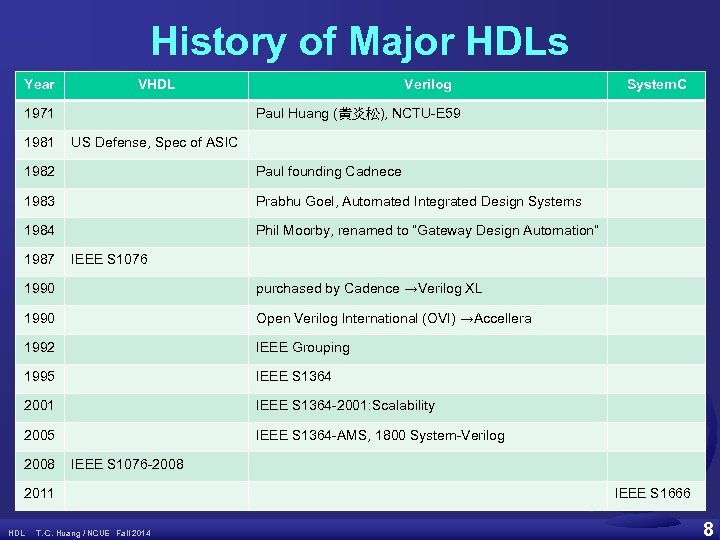

History of Major HDLs Year VHDL System. C Paul Huang (黃炎松), NCTU-E 59 1971 1981 Verilog US Defense, Spec of ASIC 1982 Paul founding Cadnece 1983 Prabhu Goel, Automated Integrated Design Systems 1984 Phil Moorby, renamed to “Gateway Design Automation” 1987 IEEE S 1076 1990 purchased by Cadence →Verilog XL 1990 Open Verilog International (OVI) →Accellera 1992 IEEE Grouping 1995 IEEE S 1364 2001 IEEE S 1364 -2001: Scalability 2005 IEEE S 1364 -AMS, 1800 System-Verilog 2008 IEEE S 1076 -2008 2011 HDL T. -C. Huang / NCUE Fall 2014 IEEE S 1666 8

History of Major HDLs Year VHDL System. C Paul Huang (黃炎松), NCTU-E 59 1971 1981 Verilog US Defense, Spec of ASIC 1982 Paul founding Cadnece 1983 Prabhu Goel, Automated Integrated Design Systems 1984 Phil Moorby, renamed to “Gateway Design Automation” 1987 IEEE S 1076 1990 purchased by Cadence →Verilog XL 1990 Open Verilog International (OVI) →Accellera 1992 IEEE Grouping 1995 IEEE S 1364 2001 IEEE S 1364 -2001: Scalability 2005 IEEE S 1364 -AMS, 1800 System-Verilog 2008 IEEE S 1076 -2008 2011 HDL T. -C. Huang / NCUE Fall 2014 IEEE S 1666 8

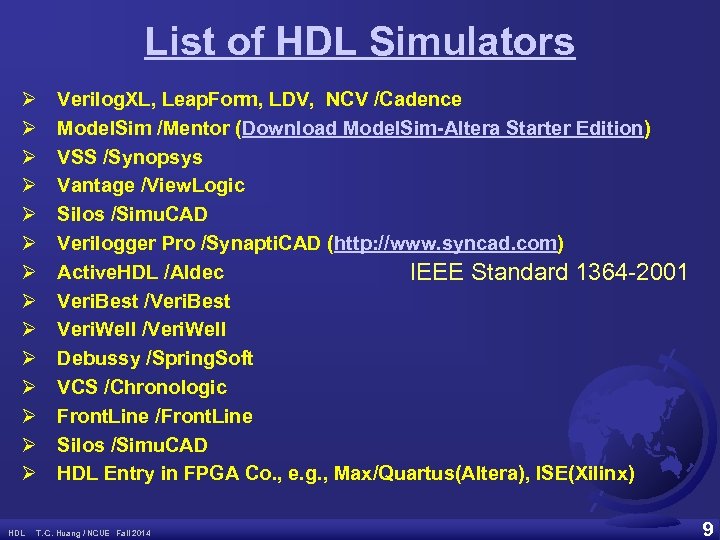

List of HDL Simulators Ø Ø Ø Ø HDL Verilog. XL, Leap. Form, LDV, NCV /Cadence Model. Sim /Mentor (Download Model. Sim-Altera Starter Edition) VSS /Synopsys Vantage /View. Logic Silos /Simu. CAD Verilogger Pro /Synapti. CAD (http: //www. syncad. com) Active. HDL /Aldec IEEE Standard 1364 -2001 Veri. Best /Veri. Best Veri. Well /Veri. Well Debussy /Spring. Soft VCS /Chronologic Front. Line /Front. Line Silos /Simu. CAD HDL Entry in FPGA Co. , e. g. , Max/Quartus(Altera), ISE(Xilinx) T. -C. Huang / NCUE Fall 2014 9

List of HDL Simulators Ø Ø Ø Ø HDL Verilog. XL, Leap. Form, LDV, NCV /Cadence Model. Sim /Mentor (Download Model. Sim-Altera Starter Edition) VSS /Synopsys Vantage /View. Logic Silos /Simu. CAD Verilogger Pro /Synapti. CAD (http: //www. syncad. com) Active. HDL /Aldec IEEE Standard 1364 -2001 Veri. Best /Veri. Best Veri. Well /Veri. Well Debussy /Spring. Soft VCS /Chronologic Front. Line /Front. Line Silos /Simu. CAD HDL Entry in FPGA Co. , e. g. , Max/Quartus(Altera), ISE(Xilinx) T. -C. Huang / NCUE Fall 2014 9

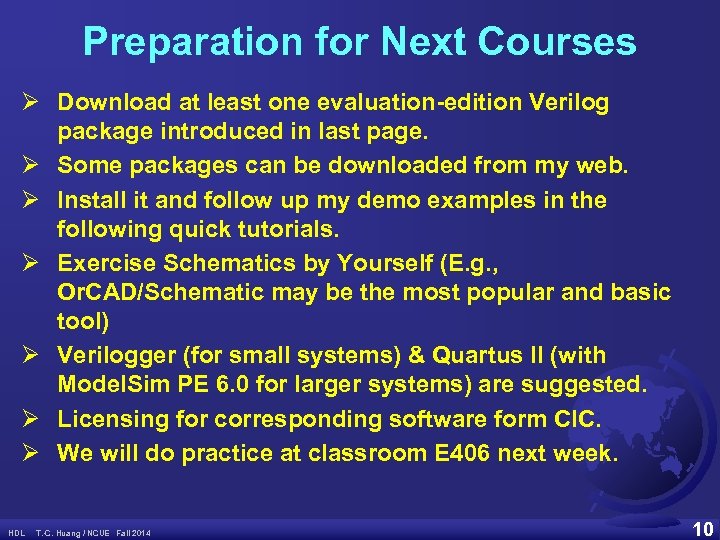

Preparation for Next Courses Ø Download at least one evaluation-edition Verilog package introduced in last page. Ø Some packages can be downloaded from my web. Ø Install it and follow up my demo examples in the following quick tutorials. Ø Exercise Schematics by Yourself (E. g. , Or. CAD/Schematic may be the most popular and basic tool) Ø Verilogger (for small systems) & Quartus II (with Model. Sim PE 6. 0 for larger systems) are suggested. Ø Licensing for corresponding software form CIC. Ø We will do practice at classroom E 406 next week. HDL T. -C. Huang / NCUE Fall 2014 10

Preparation for Next Courses Ø Download at least one evaluation-edition Verilog package introduced in last page. Ø Some packages can be downloaded from my web. Ø Install it and follow up my demo examples in the following quick tutorials. Ø Exercise Schematics by Yourself (E. g. , Or. CAD/Schematic may be the most popular and basic tool) Ø Verilogger (for small systems) & Quartus II (with Model. Sim PE 6. 0 for larger systems) are suggested. Ø Licensing for corresponding software form CIC. Ø We will do practice at classroom E 406 next week. HDL T. -C. Huang / NCUE Fall 2014 10

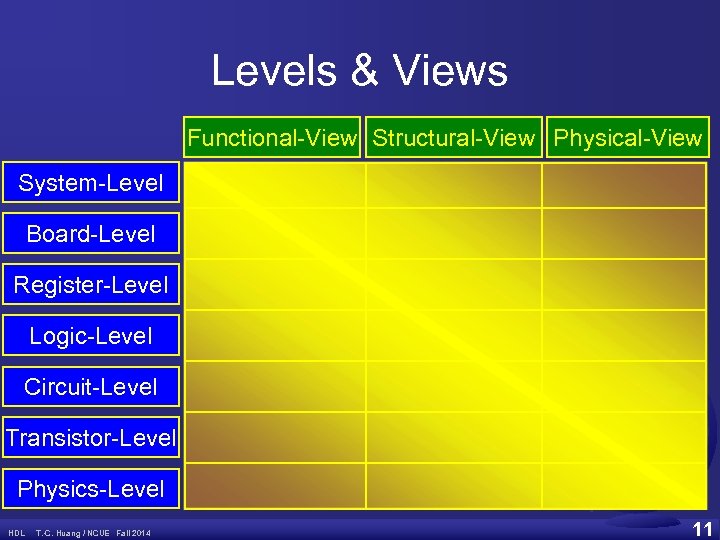

Levels & Views Functional-View Behavioral-View Structural-View Physical-View System-Level Board-Level Register-Level Logic-Level Circuit-Level Transistor-Level Physics-Level HDL T. -C. Huang / NCUE Fall 2014 11

Levels & Views Functional-View Behavioral-View Structural-View Physical-View System-Level Board-Level Register-Level Logic-Level Circuit-Level Transistor-Level Physics-Level HDL T. -C. Huang / NCUE Fall 2014 11

Y-Chart Gajski transferred the level-view table into a sphere chart: HDL T. -C. Huang / NCUE Fall 2014 12

Y-Chart Gajski transferred the level-view table into a sphere chart: HDL T. -C. Huang / NCUE Fall 2014 12

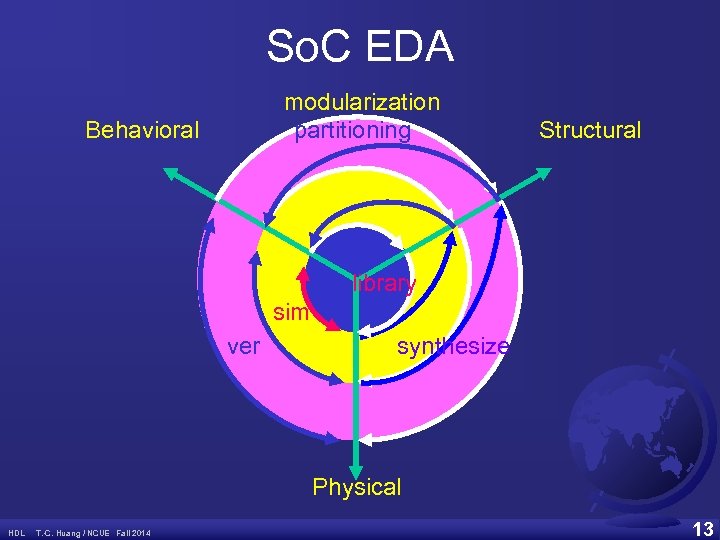

So. C EDA modularization partitioning Behavioral Structural library sim ver synthesize Physical HDL T. -C. Huang / NCUE Fall 2014 13

So. C EDA modularization partitioning Behavioral Structural library sim ver synthesize Physical HDL T. -C. Huang / NCUE Fall 2014 13

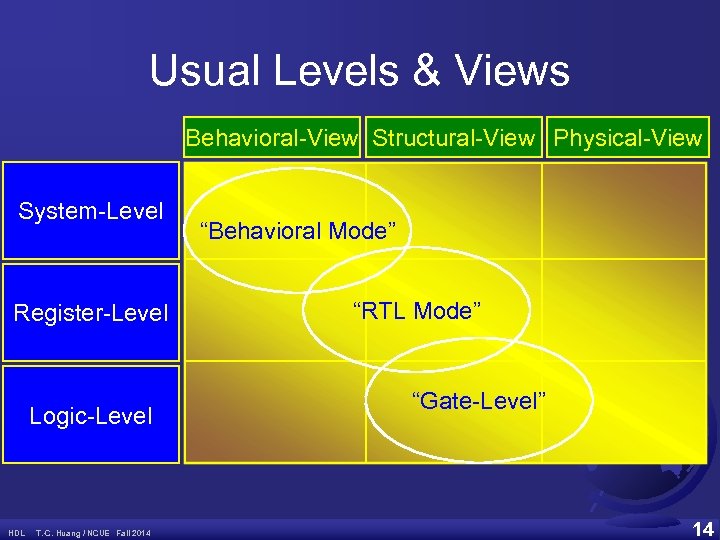

Usual Levels & Views Behavioral-View Structural-View Physical-View System-Level Register-Level Logic-Level HDL T. -C. Huang / NCUE Fall 2014 “Behavioral Mode” “RTL Mode” “Gate-Level” 14

Usual Levels & Views Behavioral-View Structural-View Physical-View System-Level Register-Level Logic-Level HDL T. -C. Huang / NCUE Fall 2014 “Behavioral Mode” “RTL Mode” “Gate-Level” 14

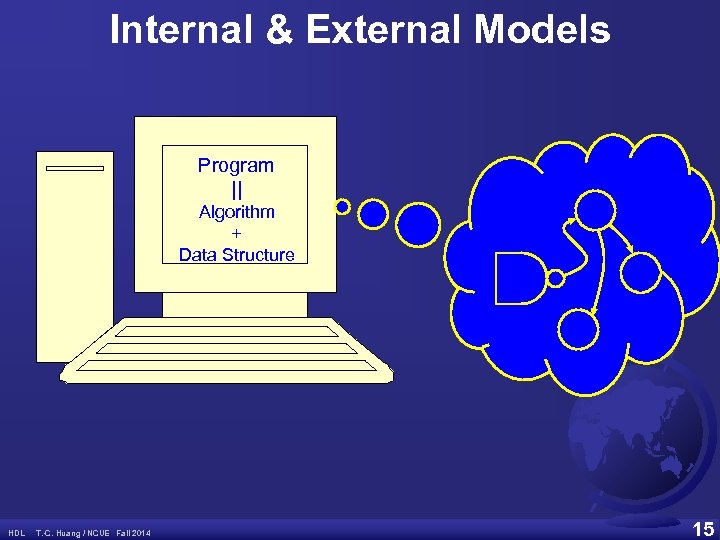

Internal & External Models Program || Algorithm + Data Structure HDL T. -C. Huang / NCUE Fall 2014 15

Internal & External Models Program || Algorithm + Data Structure HDL T. -C. Huang / NCUE Fall 2014 15

Structural & Functional Models HDL T. -C. Huang / NCUE Fall 2014 16

Structural & Functional Models HDL T. -C. Huang / NCUE Fall 2014 16

Structural Models Recursive Definition 1. Symbol View: A system or circuit can be represented by a symbol with its function. 2. A Structural View of a system (or circuit) is a representation or model that consists nodes for subsystems (or subcircuits) and elements (or components) represented by some symbol view, and arcs for their input/output relations. 3. Usually hierarchical. 4. The bottom-level boxes (components) are called primitive elements, which functional model is assumed to be known such as and, nand, or, not, etc. HDL T. -C. Huang / NCUE Fall 2014 17

Structural Models Recursive Definition 1. Symbol View: A system or circuit can be represented by a symbol with its function. 2. A Structural View of a system (or circuit) is a representation or model that consists nodes for subsystems (or subcircuits) and elements (or components) represented by some symbol view, and arcs for their input/output relations. 3. Usually hierarchical. 4. The bottom-level boxes (components) are called primitive elements, which functional model is assumed to be known such as and, nand, or, not, etc. HDL T. -C. Huang / NCUE Fall 2014 17

Structural Modeling at Logic Level 1. 2. 3. 4. 5. HDL External Representation Structural Properties Hardware Descriptive Languages Internal Representation Example: A Simple Verilog Parser in C Language. T. -C. Huang / NCUE Fall 2014 18

Structural Modeling at Logic Level 1. 2. 3. 4. 5. HDL External Representation Structural Properties Hardware Descriptive Languages Internal Representation Example: A Simple Verilog Parser in C Language. T. -C. Huang / NCUE Fall 2014 18

External Representation 1. Text or schematic for human. Connectivity specifies I/O, components with signals. 2. Text or Language: HDL: VHDL, Verilog, C, etc. Netlist: SPICE, gat, tdl, etc. 3. Schematics: Cadence Schedmatics Or. CAD Schedmatics, . . etc. HDL T. -C. Huang / NCUE Fall 2014 19

External Representation 1. Text or schematic for human. Connectivity specifies I/O, components with signals. 2. Text or Language: HDL: VHDL, Verilog, C, etc. Netlist: SPICE, gat, tdl, etc. 3. Schematics: Cadence Schedmatics Or. CAD Schedmatics, . . etc. HDL T. -C. Huang / NCUE Fall 2014 19

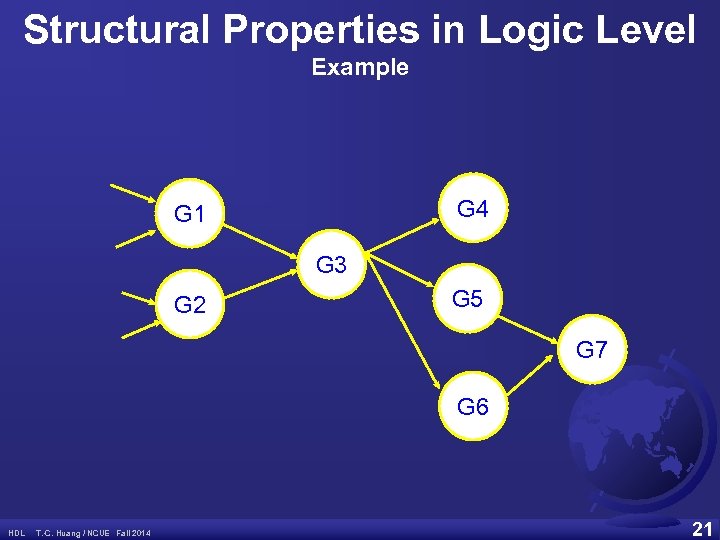

Structural Properties in Logic Level 1. 2. 3. 4. 5. 6. 7. 8. HDL Branches/Fanout Stem Fanout-free Reconvergent Fanout Gate Type Inversion Parity Level of a Gate in Circuit T. -C. Huang / NCUE Fall 2014 20

Structural Properties in Logic Level 1. 2. 3. 4. 5. 6. 7. 8. HDL Branches/Fanout Stem Fanout-free Reconvergent Fanout Gate Type Inversion Parity Level of a Gate in Circuit T. -C. Huang / NCUE Fall 2014 20

Structural Properties in Logic Level Example G 4 G 1 G 3 G 2 G 5 G 7 G 6 HDL T. -C. Huang / NCUE Fall 2014 21

Structural Properties in Logic Level Example G 4 G 1 G 3 G 2 G 5 G 7 G 6 HDL T. -C. Huang / NCUE Fall 2014 21

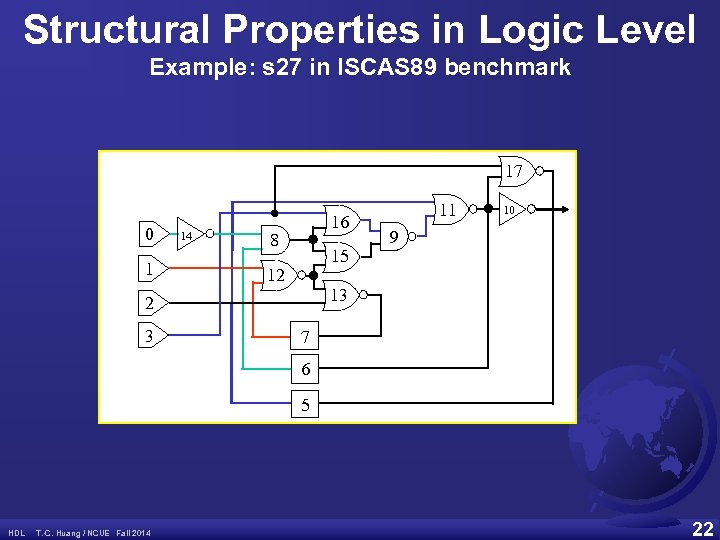

Structural Properties in Logic Level Example: s 27 in ISCAS 89 benchmark 17 0 1 14 16 8 15 12 10 9 13 2 3 11 7 6 5 HDL T. -C. Huang / NCUE Fall 2014 22

Structural Properties in Logic Level Example: s 27 in ISCAS 89 benchmark 17 0 1 14 16 8 15 12 10 9 13 2 3 11 7 6 5 HDL T. -C. Huang / NCUE Fall 2014 22

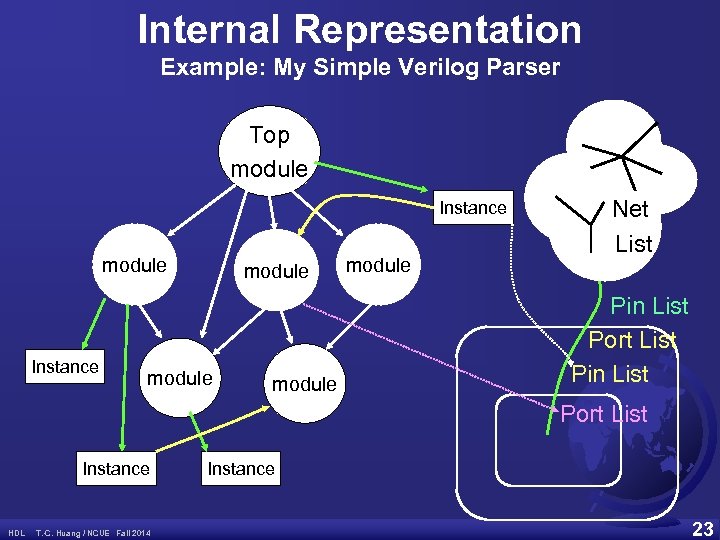

Internal Representation Example: My Simple Verilog Parser Top module Instance module Net List Pin List Port List Instance HDL T. -C. Huang / NCUE Fall 2014 Instance 23

Internal Representation Example: My Simple Verilog Parser Top module Instance module Net List Pin List Port List Instance HDL T. -C. Huang / NCUE Fall 2014 Instance 23

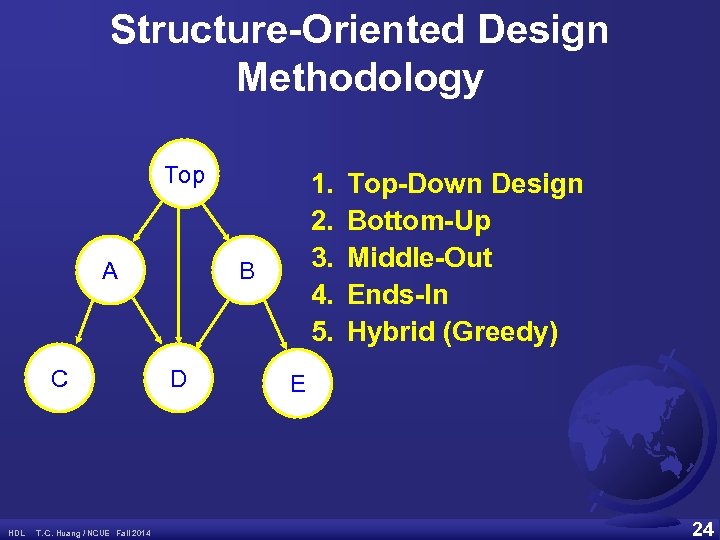

Structure-Oriented Design Methodology Top A C HDL T. -C. Huang / NCUE Fall 2014 1. 2. 3. 4. 5. B D Top-Down Design Bottom-Up Middle-Out Ends-In Hybrid (Greedy) E 24

Structure-Oriented Design Methodology Top A C HDL T. -C. Huang / NCUE Fall 2014 1. 2. 3. 4. 5. B D Top-Down Design Bottom-Up Middle-Out Ends-In Hybrid (Greedy) E 24

Functional Modeling at Logic Level 1. 2. 3. 4. HDL Truth Table & Primitive Cubes. State Table & Flow Table. Binary Decision Diagrams. Programs as Functional Models. T. -C. Huang / NCUE Fall 2014 25

Functional Modeling at Logic Level 1. 2. 3. 4. HDL Truth Table & Primitive Cubes. State Table & Flow Table. Binary Decision Diagrams. Programs as Functional Models. T. -C. Huang / NCUE Fall 2014 25

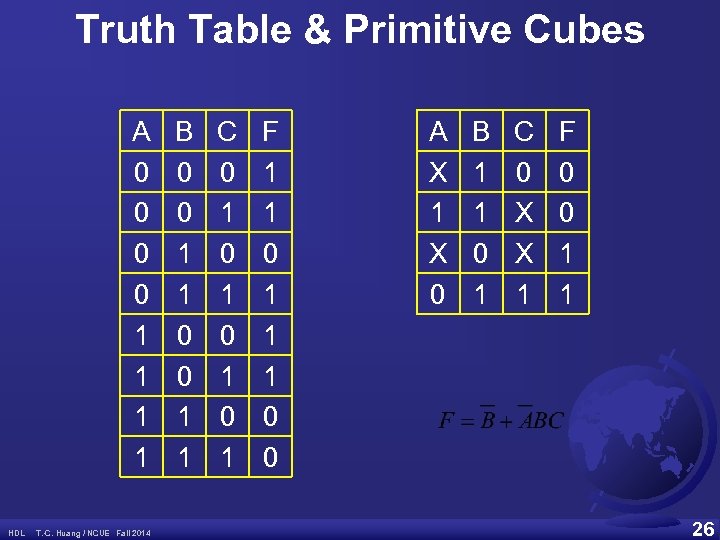

Truth Table & Primitive Cubes A 0 0 1 1 HDL T. -C. Huang / NCUE Fall 2014 B 0 0 1 1 C 0 1 0 1 F 1 1 0 1 1 1 0 0 A X 1 X 0 B 1 1 0 1 C 0 X X 1 F 0 0 1 1 26

Truth Table & Primitive Cubes A 0 0 1 1 HDL T. -C. Huang / NCUE Fall 2014 B 0 0 1 1 C 0 1 0 1 F 1 1 0 1 1 1 0 0 A X 1 X 0 B 1 1 0 1 C 0 X X 1 F 0 0 1 1 26

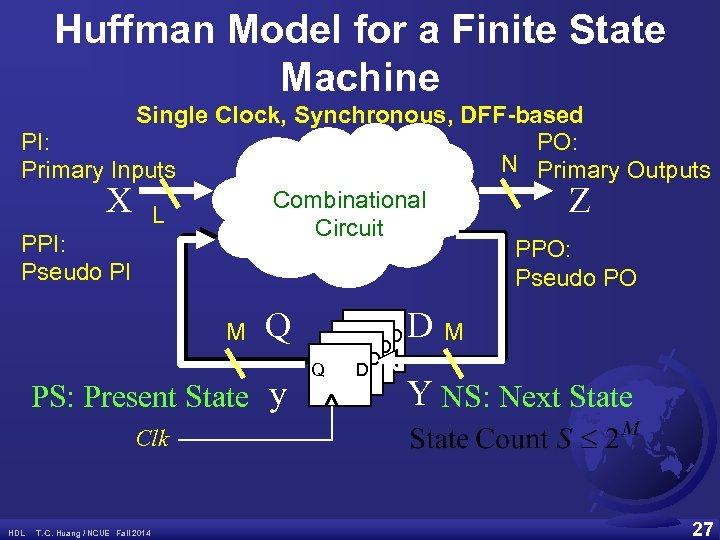

Huffman Model for a Finite State Machine Single Clock, Synchronous, DFF-based PI: PO: N Primary Outputs Primary Inputs Combinational Z X L Circuit PPI: PPO: Pseudo PI Pseudo PO M Q PS: Present State y Q D Q D D M Y NS: Next State Clk HDL T. -C. Huang / NCUE Fall 2014 27

Huffman Model for a Finite State Machine Single Clock, Synchronous, DFF-based PI: PO: N Primary Outputs Primary Inputs Combinational Z X L Circuit PPI: PPO: Pseudo PI Pseudo PO M Q PS: Present State y Q D Q D D M Y NS: Next State Clk HDL T. -C. Huang / NCUE Fall 2014 27

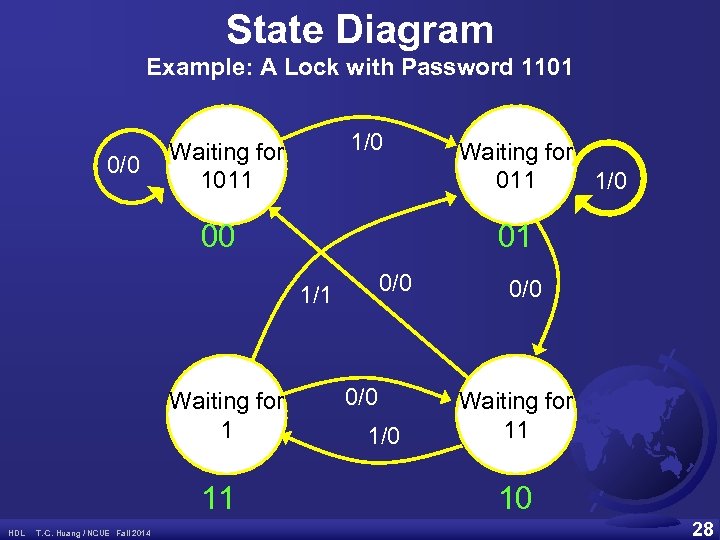

State Diagram Example: A Lock with Password 1101 1/0 Waiting for 1011 0/0 00 01 0/0 1/1 Waiting for 1 11 HDL T. -C. Huang / NCUE Fall 2014 Waiting for 011 1/0 0/0 Waiting for 11 10 28

State Diagram Example: A Lock with Password 1101 1/0 Waiting for 1011 0/0 00 01 0/0 1/1 Waiting for 1 11 HDL T. -C. Huang / NCUE Fall 2014 Waiting for 011 1/0 0/0 Waiting for 11 10 28

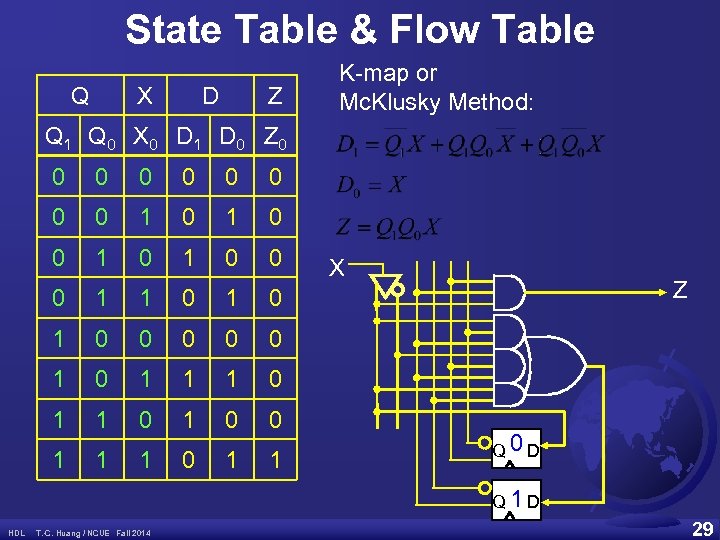

State Table & Flow Table Q X D Z K-map or Mc. Klusky Method: Q 1 Q 0 X 0 D 1 D 0 Z 0 0 0 0 0 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1 1 0 1 1 X Z Q 0 D Q 1 D HDL T. -C. Huang / NCUE Fall 2014 29

State Table & Flow Table Q X D Z K-map or Mc. Klusky Method: Q 1 Q 0 X 0 D 1 D 0 Z 0 0 0 0 0 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1 1 0 1 1 X Z Q 0 D Q 1 D HDL T. -C. Huang / NCUE Fall 2014 29

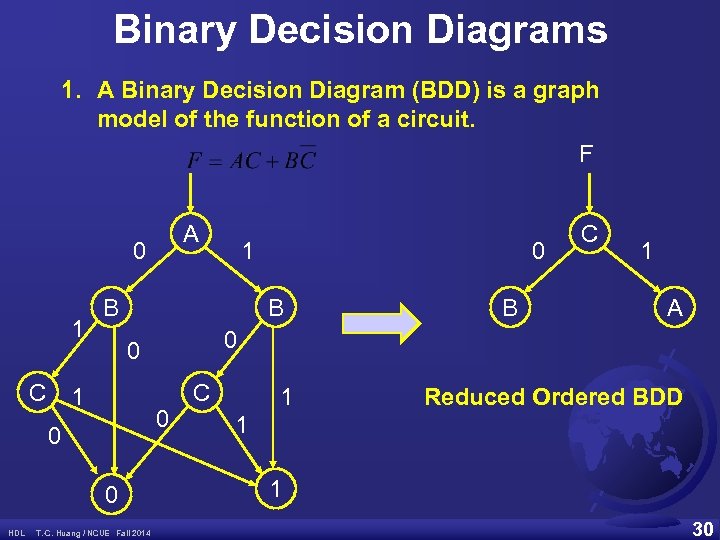

Binary Decision Diagrams 1. A Binary Decision Diagram (BDD) is a graph model of the function of a circuit. F A 0 1 C B 0 B 1 0 0 T. -C. Huang / NCUE Fall 2014 B 1 A 0 0 0 HDL 1 C C 1 Reduced Ordered BDD 1 1 30

Binary Decision Diagrams 1. A Binary Decision Diagram (BDD) is a graph model of the function of a circuit. F A 0 1 C B 0 B 1 0 0 T. -C. Huang / NCUE Fall 2014 B 1 A 0 0 0 HDL 1 C C 1 Reduced Ordered BDD 1 1 30

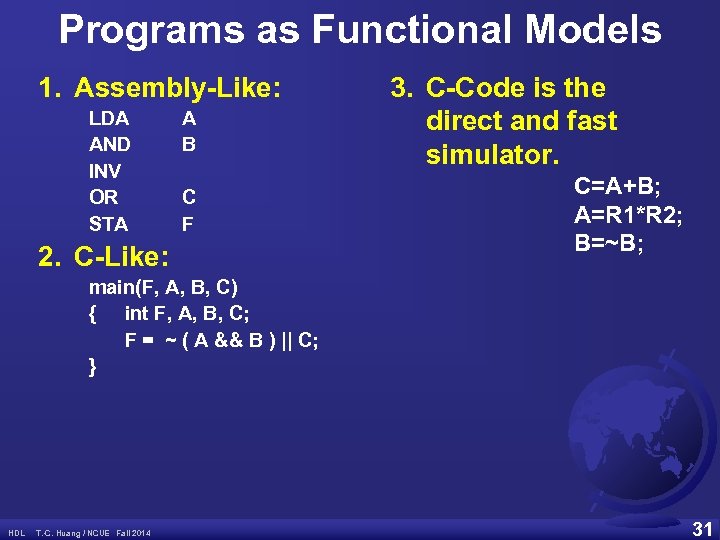

Programs as Functional Models 1. Assembly-Like: LDA AND INV OR STA A B C F 2. C-Like: 3. C-Code is the direct and fast simulator. C=A+B; A=R 1*R 2; B=~B; main(F, A, B, C) { int F, A, B, C; F = ~ ( A && B ) || C; } HDL T. -C. Huang / NCUE Fall 2014 31

Programs as Functional Models 1. Assembly-Like: LDA AND INV OR STA A B C F 2. C-Like: 3. C-Code is the direct and fast simulator. C=A+B; A=R 1*R 2; B=~B; main(F, A, B, C) { int F, A, B, C; F = ~ ( A && B ) || C; } HDL T. -C. Huang / NCUE Fall 2014 31

Functional Modeling at Register Level 1. Basic RTL Constructs 2. Timing Modeling in RTLs 3. Internal RTL Models (See Internal structural model) HDL T. -C. Huang / NCUE Fall 2014 32

Functional Modeling at Register Level 1. Basic RTL Constructs 2. Timing Modeling in RTLs 3. Internal RTL Models (See Internal structural model) HDL T. -C. Huang / NCUE Fall 2014 32

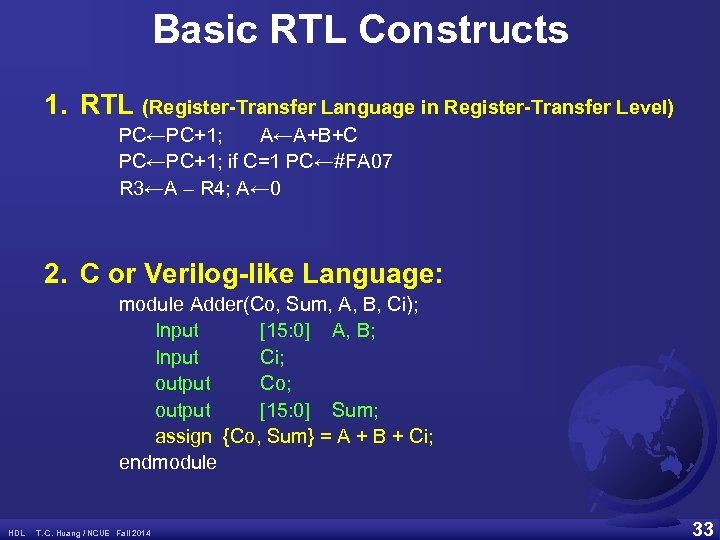

Basic RTL Constructs 1. RTL (Register-Transfer Language in Register-Transfer Level) PC←PC+1; A←A+B+C PC←PC+1; if C=1 PC←#FA 07 R 3←A – R 4; A← 0 2. C or Verilog-like Language: module Adder(Co, Sum, A, B, Ci); Input [15: 0] A, B; Input Ci; output Co; output [15: 0] Sum; assign {Co, Sum} = A + B + Ci; endmodule HDL T. -C. Huang / NCUE Fall 2014 33

Basic RTL Constructs 1. RTL (Register-Transfer Language in Register-Transfer Level) PC←PC+1; A←A+B+C PC←PC+1; if C=1 PC←#FA 07 R 3←A – R 4; A← 0 2. C or Verilog-like Language: module Adder(Co, Sum, A, B, Ci); Input [15: 0] A, B; Input Ci; output Co; output [15: 0] Sum; assign {Co, Sum} = A + B + Ci; endmodule HDL T. -C. Huang / NCUE Fall 2014 33

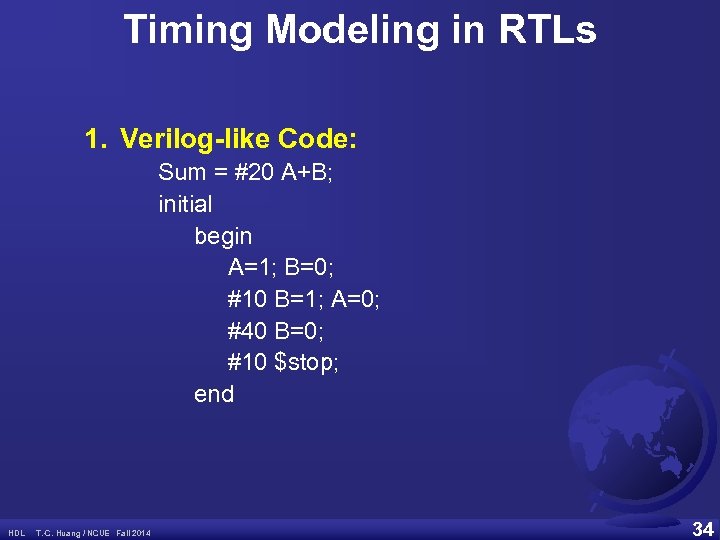

Timing Modeling in RTLs 1. Verilog-like Code: Sum = #20 A+B; initial begin A=1; B=0; #10 B=1; A=0; #40 B=0; #10 $stop; end HDL T. -C. Huang / NCUE Fall 2014 34

Timing Modeling in RTLs 1. Verilog-like Code: Sum = #20 A+B; initial begin A=1; B=0; #10 B=1; A=0; #40 B=0; #10 $stop; end HDL T. -C. Huang / NCUE Fall 2014 34

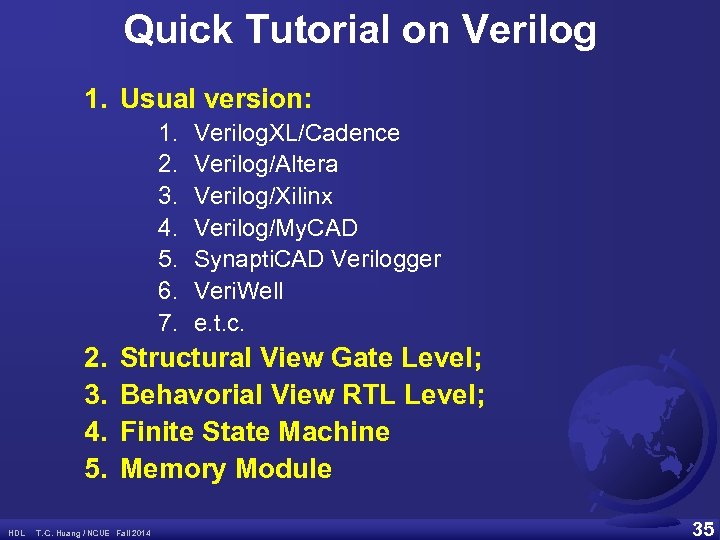

Quick Tutorial on Verilog 1. Usual version: 1. 2. 3. 4. 5. 6. 7. 2. 3. 4. 5. HDL Verilog. XL/Cadence Verilog/Altera Verilog/Xilinx Verilog/My. CAD Synapti. CAD Verilogger Veri. Well e. t. c. Structural View Gate Level; Behavorial View RTL Level; Finite State Machine Memory Module T. -C. Huang / NCUE Fall 2014 35

Quick Tutorial on Verilog 1. Usual version: 1. 2. 3. 4. 5. 6. 7. 2. 3. 4. 5. HDL Verilog. XL/Cadence Verilog/Altera Verilog/Xilinx Verilog/My. CAD Synapti. CAD Verilogger Veri. Well e. t. c. Structural View Gate Level; Behavorial View RTL Level; Finite State Machine Memory Module T. -C. Huang / NCUE Fall 2014 35