023c30108ad15cc79021e22b674f9510.ppt

- Количество слайдов: 24

HAPPEX DAQ / ADC Tests Luis Mercado UMASS 4/17/09

HAPPEX DAQ / ADC Tests Luis Mercado UMASS 4/17/09

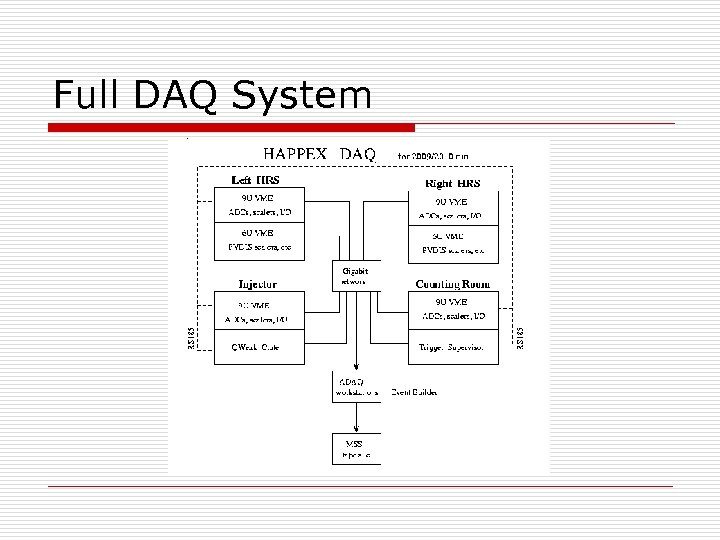

Full DAQ System

Full DAQ System

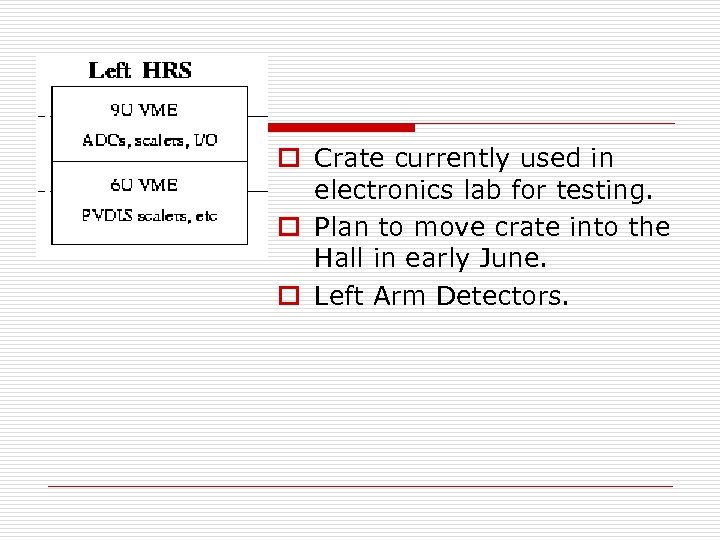

o Crate currently used in electronics lab for testing. o Plan to move crate into the Hall in early June. o Left Arm Detectors.

o Crate currently used in electronics lab for testing. o Plan to move crate into the Hall in early June. o Left Arm Detectors.

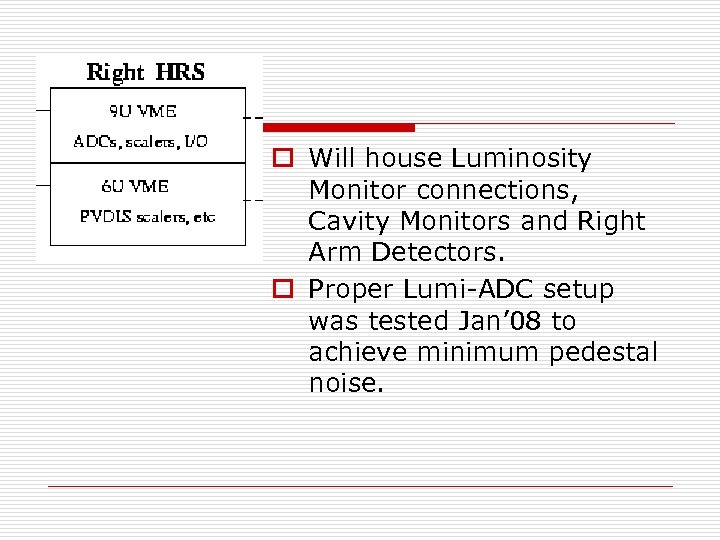

o Will house Luminosity Monitor connections, Cavity Monitors and Right Arm Detectors. o Proper Lumi-ADC setup was tested Jan’ 08 to achieve minimum pedestal noise.

o Will house Luminosity Monitor connections, Cavity Monitors and Right Arm Detectors. o Proper Lumi-ADC setup was tested Jan’ 08 to achieve minimum pedestal noise.

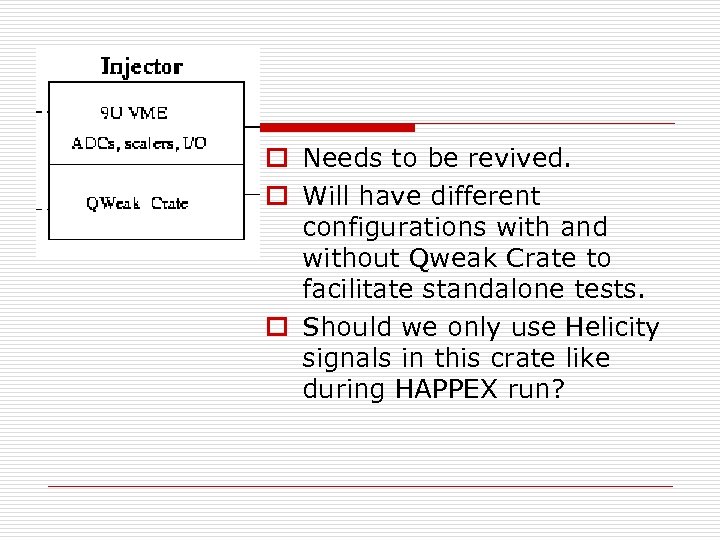

o Needs to be revived. o Will have different configurations with and without Qweak Crate to facilitate standalone tests. o Should we only use Helicity signals in this crate like during HAPPEX run?

o Needs to be revived. o Will have different configurations with and without Qweak Crate to facilitate standalone tests. o Should we only use Helicity signals in this crate like during HAPPEX run?

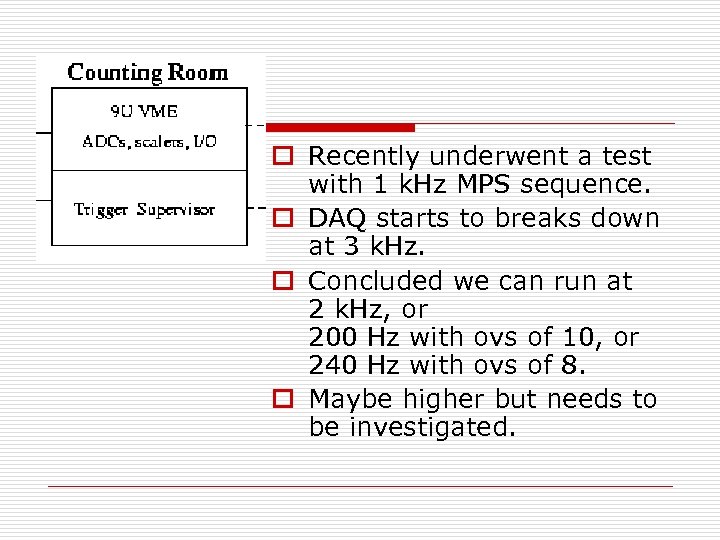

o Recently underwent a test with 1 k. Hz MPS sequence. o DAQ starts to breaks down at 3 k. Hz. o Concluded we can run at 2 k. Hz, or 200 Hz with ovs of 10, or 240 Hz with ovs of 8. o Maybe higher but needs to be investigated.

o Recently underwent a test with 1 k. Hz MPS sequence. o DAQ starts to breaks down at 3 k. Hz. o Concluded we can run at 2 k. Hz, or 200 Hz with ovs of 10, or 240 Hz with ovs of 8. o Maybe higher but needs to be investigated.

Current Plans o Revive synchronization checks. o Replace many 16 -bit ADCs with new 18 -bit boards. o Basic DAQ should be ready for testing by mid-July.

Current Plans o Revive synchronization checks. o Replace many 16 -bit ADCs with new 18 -bit boards. o Basic DAQ should be ready for testing by mid-July.

Future Tests o High rate deadtime. o Checks of new helicity sequence board. o Synch checks. o Pedestal Studies (helicity-correlated noise).

Future Tests o High rate deadtime. o Checks of new helicity sequence board. o Synch checks. o Pedestal Studies (helicity-correlated noise).

Latest 18 -bit ADC Tests

Latest 18 -bit ADC Tests

New 18 -bit ADCs o Received four brand new boards a couple of weeks ago. o Performance matches previous tests with prototypes. o Will be receiving 10 more new boards by June 1 st.

New 18 -bit ADCs o Received four brand new boards a couple of weeks ago. o Performance matches previous tests with prototypes. o Will be receiving 10 more new boards by June 1 st.

Testing of 18 -bit boards. o Setting and recording proper pedestals offsets. o Studying pedestal noise with respect to gain setting (as low as 12 ppm). o Testing linearity of current mode for use with Luminosity Monitors. o Comparing results with previous study done with 16 -bit ADCs.

Testing of 18 -bit boards. o Setting and recording proper pedestals offsets. o Studying pedestal noise with respect to gain setting (as low as 12 ppm). o Testing linearity of current mode for use with Luminosity Monitors. o Comparing results with previous study done with 16 -bit ADCs.

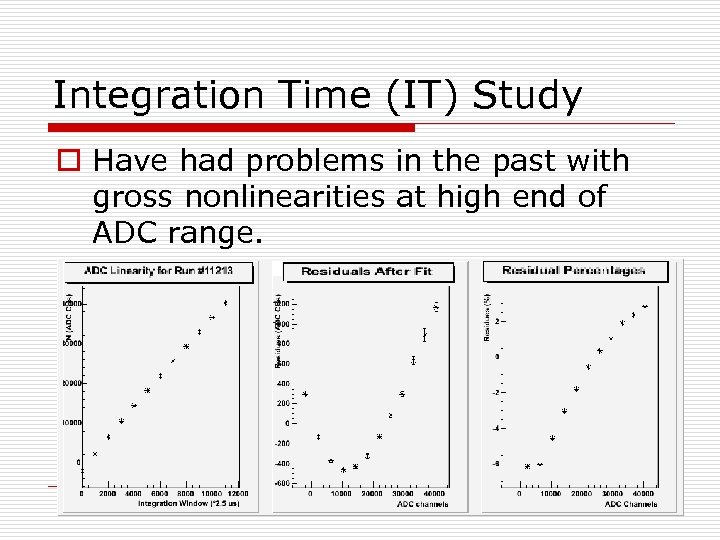

Integration Time (IT) Study o Have had problems in the past with gross nonlinearities at high end of ADC range.

Integration Time (IT) Study o Have had problems in the past with gross nonlinearities at high end of ADC range.

Integration Time (IT) Study o Redid test using new 18 -bit ADCs, with some changes: n Sample more IT values by taking smaller steps up the IT ladder. n More data points for higher IT values to get better error bar. n Go up to 230 -240 K signal to see if it gets worse at the higher end.

Integration Time (IT) Study o Redid test using new 18 -bit ADCs, with some changes: n Sample more IT values by taking smaller steps up the IT ladder. n More data points for higher IT values to get better error bar. n Go up to 230 -240 K signal to see if it gets worse at the higher end.

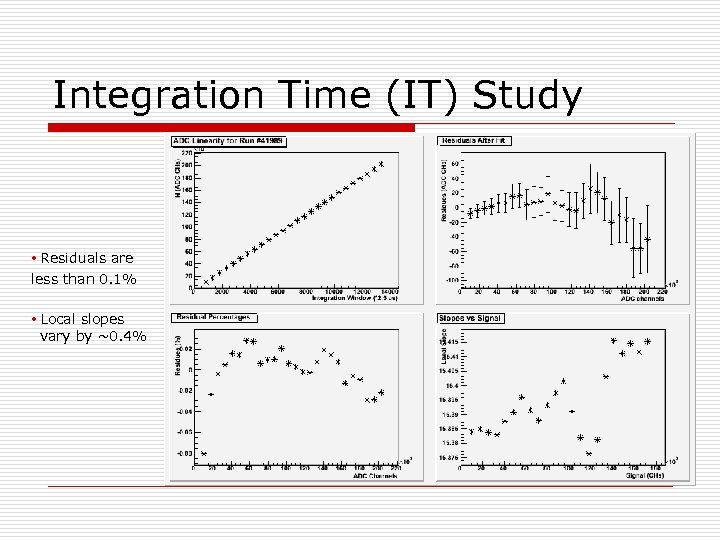

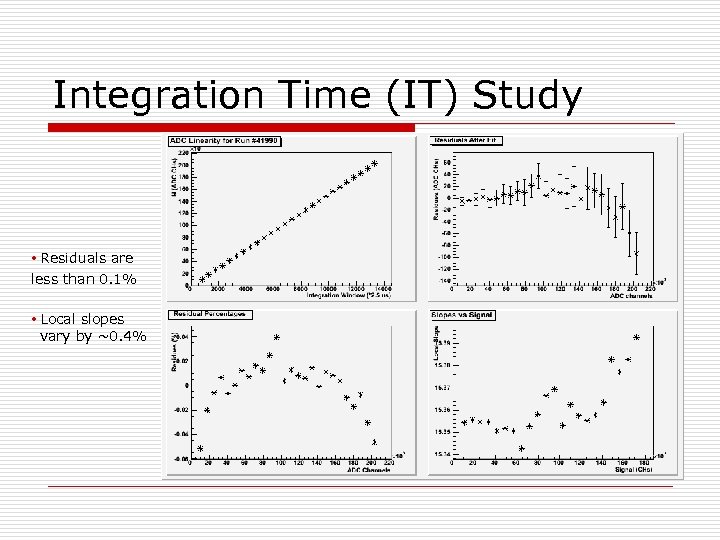

Integration Time (IT) Study • Residuals are less than 0. 1% • Local slopes vary by ~0. 4%

Integration Time (IT) Study • Residuals are less than 0. 1% • Local slopes vary by ~0. 4%

Integration Time (IT) Study • Residuals are less than 0. 1% • Local slopes vary by ~0. 4%

Integration Time (IT) Study • Residuals are less than 0. 1% • Local slopes vary by ~0. 4%

PMT Linearity o Past tests have shown nonlinearities in PMT output dependant on input and gain. o Want to make sure we get similar results with new 18 -bit ADCs. o Showed that results matched in good and bad linearity regions.

PMT Linearity o Past tests have shown nonlinearities in PMT output dependant on input and gain. o Want to make sure we get similar results with new 18 -bit ADCs. o Showed that results matched in good and bad linearity regions.

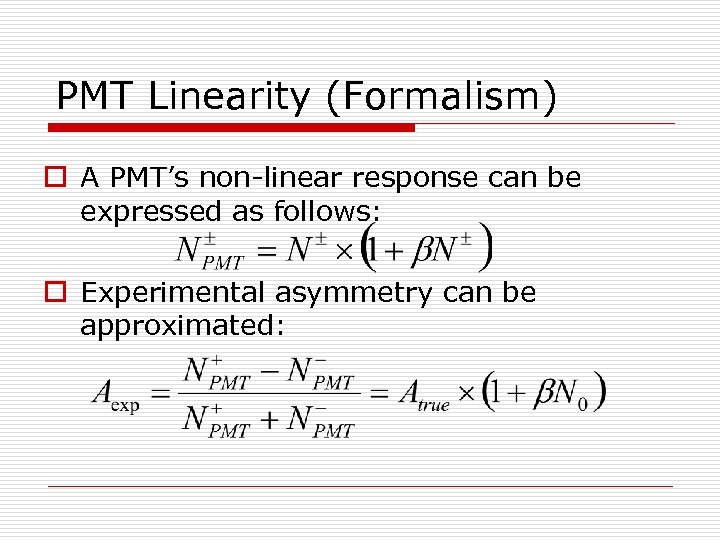

PMT Linearity (Formalism) o A PMT’s non-linear response can be expressed as follows: o Experimental asymmetry can be approximated:

PMT Linearity (Formalism) o A PMT’s non-linear response can be expressed as follows: o Experimental asymmetry can be approximated:

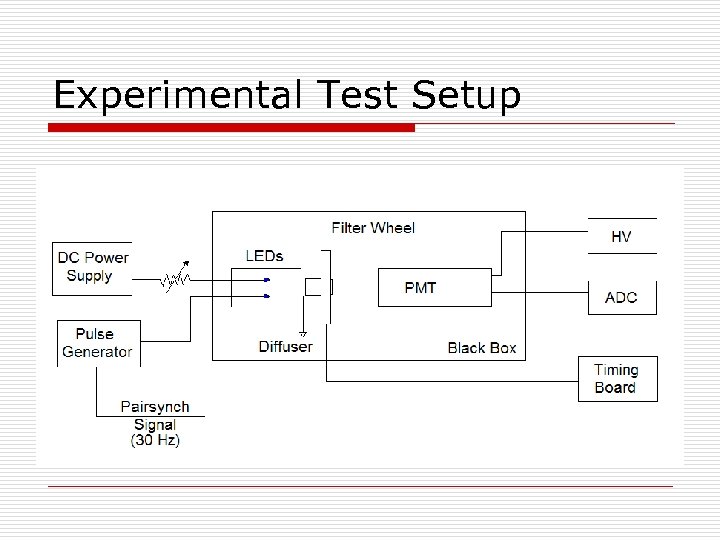

Experimental Test Setup

Experimental Test Setup

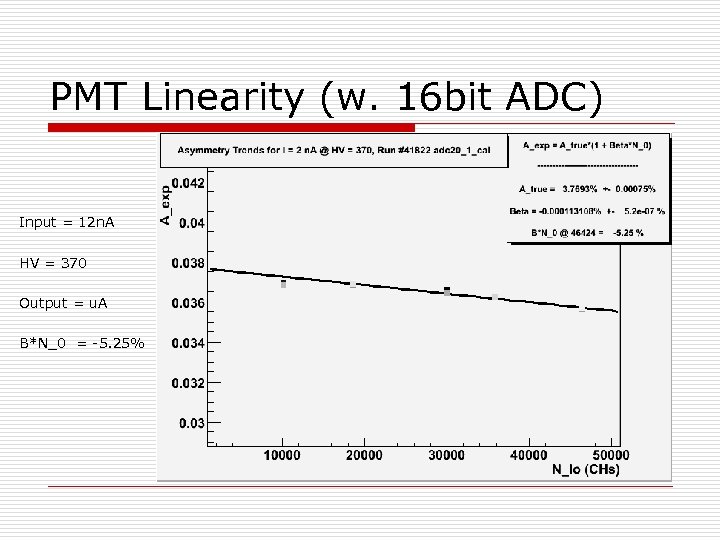

PMT Linearity (w. 16 bit ADC) Input = 12 n. A HV = 370 Output = u. A B*N_0 = -5. 25%

PMT Linearity (w. 16 bit ADC) Input = 12 n. A HV = 370 Output = u. A B*N_0 = -5. 25%

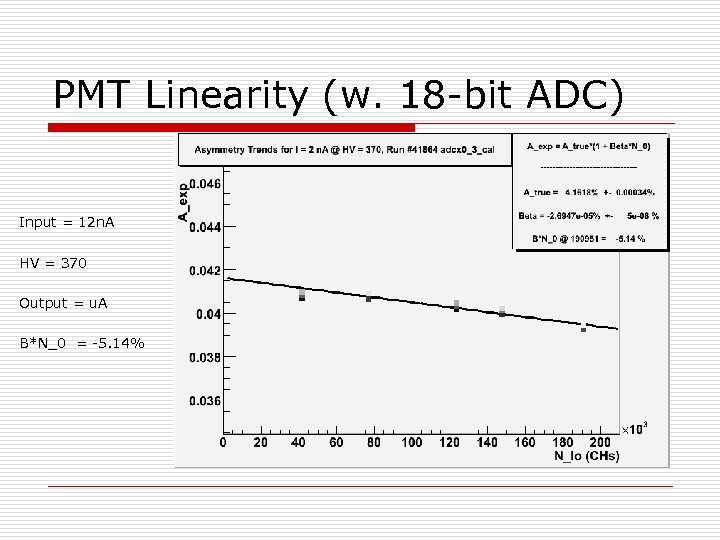

PMT Linearity (w. 18 -bit ADC) Input = 12 n. A HV = 370 Output = u. A B*N_0 = -5. 14%

PMT Linearity (w. 18 -bit ADC) Input = 12 n. A HV = 370 Output = u. A B*N_0 = -5. 14%

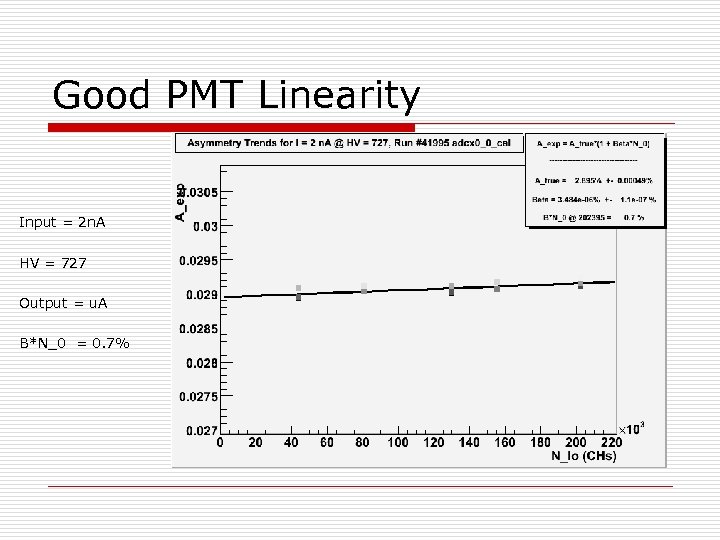

Good PMT Linearity Input = 2 n. A HV = 727 Output = u. A B*N_0 = 0. 7%

Good PMT Linearity Input = 2 n. A HV = 727 Output = u. A B*N_0 = 0. 7%

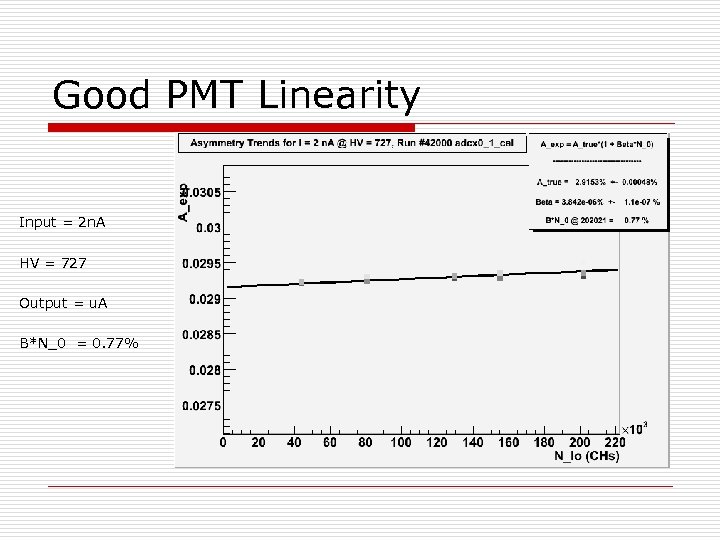

Good PMT Linearity Input = 2 n. A HV = 727 Output = u. A B*N_0 = 0. 77%

Good PMT Linearity Input = 2 n. A HV = 727 Output = u. A B*N_0 = 0. 77%

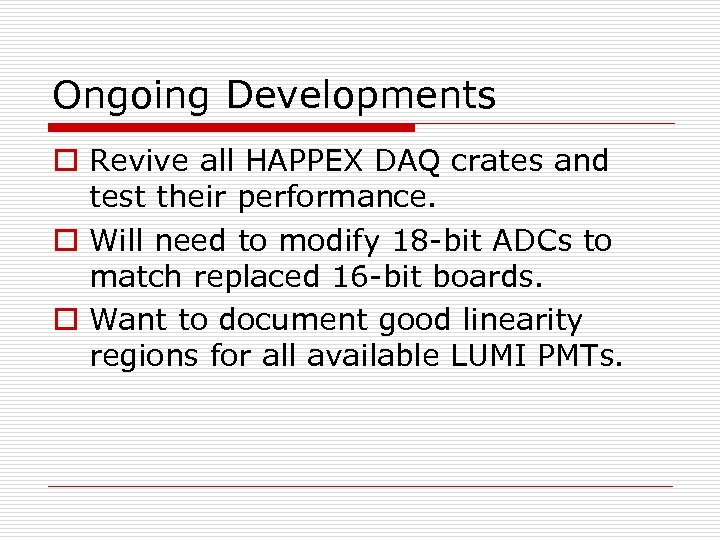

Ongoing Developments o Revive all HAPPEX DAQ crates and test their performance. o Will need to modify 18 -bit ADCs to match replaced 16 -bit boards. o Want to document good linearity regions for all available LUMI PMTs.

Ongoing Developments o Revive all HAPPEX DAQ crates and test their performance. o Will need to modify 18 -bit ADCs to match replaced 16 -bit boards. o Want to document good linearity regions for all available LUMI PMTs.

Acknowledgements o o o Krishna Kumar Kent Pashke Dustin Mc. Nulty Robert Michaels HAPPEX/PREX Collaboration

Acknowledgements o o o Krishna Kumar Kent Pashke Dustin Mc. Nulty Robert Michaels HAPPEX/PREX Collaboration