5e15b8146927a5dc4f694317e63a99db.ppt

- Количество слайдов: 35

Grid. Pix – chip post processing Jurriaan Schmitz Vertex 09 Jurriaan Schmitz - chip postprocessing 1

Grid. Pix – chip post processing Jurriaan Schmitz Vertex 09 Jurriaan Schmitz - chip postprocessing 1

About Jurriaan Schmitz Ph. D. experimental physics 1994 Universiteit van Amsterdam/NIKHEF Senior Scientist at Philips Research 1994 -2002 Full professor at University of Twente 2002 -present Jurriaan Schmitz - chip post-processing Vertex 09 2

About Jurriaan Schmitz Ph. D. experimental physics 1994 Universiteit van Amsterdam/NIKHEF Senior Scientist at Philips Research 1994 -2002 Full professor at University of Twente 2002 -present Jurriaan Schmitz - chip post-processing Vertex 09 2

Outline § § The concept of wafer post-processing Successes of wafer post-processing Recent results Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 3

Outline § § The concept of wafer post-processing Successes of wafer post-processing Recent results Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 3

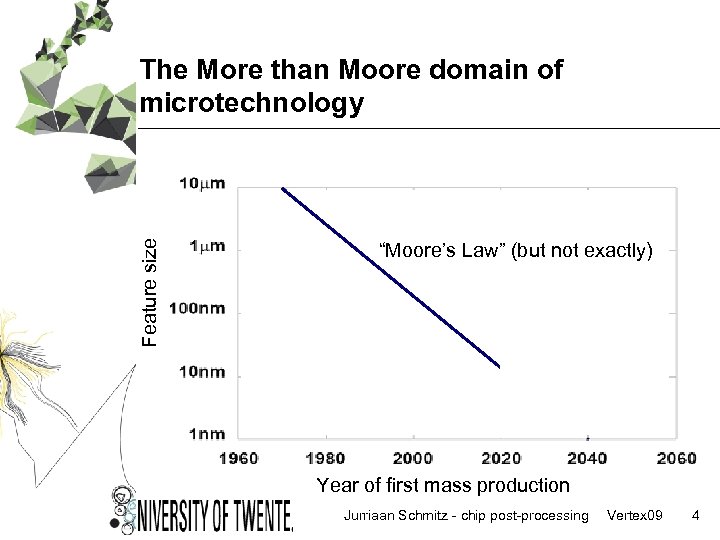

Feature size The More than Moore domain of microtechnology “Moore’s Law” (but not exactly) Year of first mass production Jurriaan Schmitz - chip post-processing Vertex 09 4

Feature size The More than Moore domain of microtechnology “Moore’s Law” (but not exactly) Year of first mass production Jurriaan Schmitz - chip post-processing Vertex 09 4

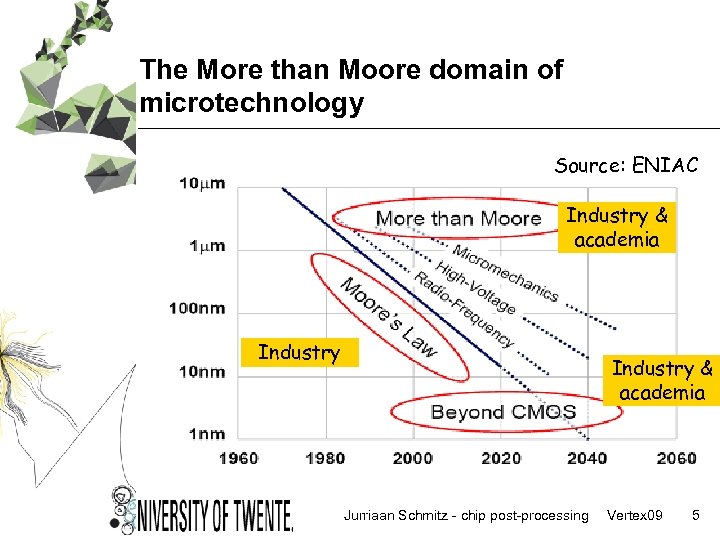

The More than Moore domain of microtechnology Source: ENIAC Industry & academia Jurriaan Schmitz - chip post-processing Vertex 09 5

The More than Moore domain of microtechnology Source: ENIAC Industry & academia Jurriaan Schmitz - chip post-processing Vertex 09 5

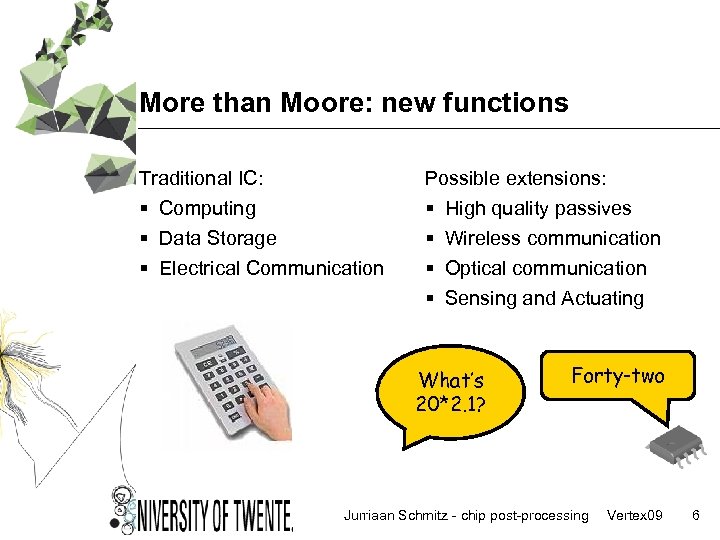

More than Moore: new functions Traditional IC: § Computing § Data Storage § Electrical Communication Possible extensions: § High quality passives § Wireless communication § Optical communication § Sensing and Actuating What’s 20*2. 1? Forty-two Jurriaan Schmitz - chip post-processing Vertex 09 6

More than Moore: new functions Traditional IC: § Computing § Data Storage § Electrical Communication Possible extensions: § High quality passives § Wireless communication § Optical communication § Sensing and Actuating What’s 20*2. 1? Forty-two Jurriaan Schmitz - chip post-processing Vertex 09 6

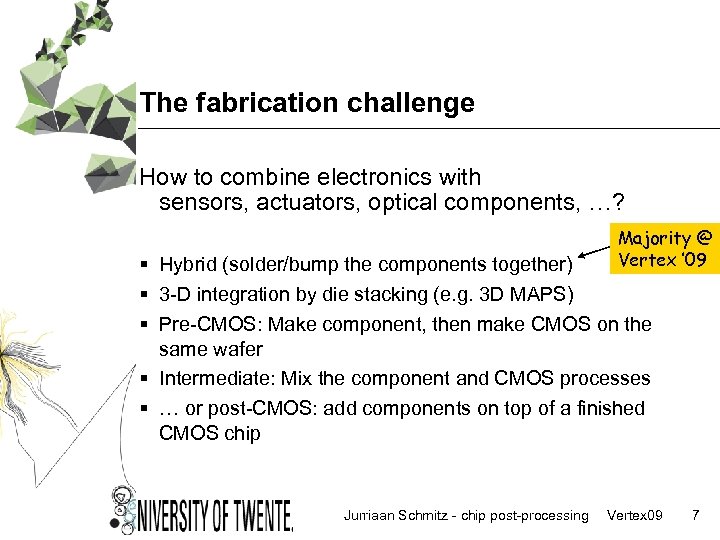

The fabrication challenge How to combine electronics with sensors, actuators, optical components, …? Majority @ Vertex ’ 09 § Hybrid (solder/bump the components together) § 3 -D integration by die stacking (e. g. 3 D MAPS) § Pre-CMOS: Make component, then make CMOS on the same wafer § Intermediate: Mix the component and CMOS processes § … or post-CMOS: add components on top of a finished CMOS chip Jurriaan Schmitz - chip post-processing Vertex 09 7

The fabrication challenge How to combine electronics with sensors, actuators, optical components, …? Majority @ Vertex ’ 09 § Hybrid (solder/bump the components together) § 3 -D integration by die stacking (e. g. 3 D MAPS) § Pre-CMOS: Make component, then make CMOS on the same wafer § Intermediate: Mix the component and CMOS processes § … or post-CMOS: add components on top of a finished CMOS chip Jurriaan Schmitz - chip post-processing Vertex 09 7

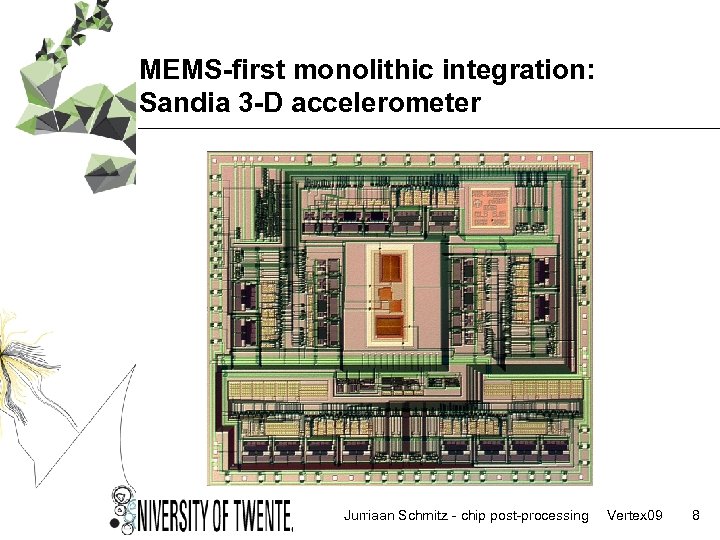

MEMS-first monolithic integration: Sandia 3 -D accelerometer Jurriaan Schmitz - chip post-processing Vertex 09 8

MEMS-first monolithic integration: Sandia 3 -D accelerometer Jurriaan Schmitz - chip post-processing Vertex 09 8

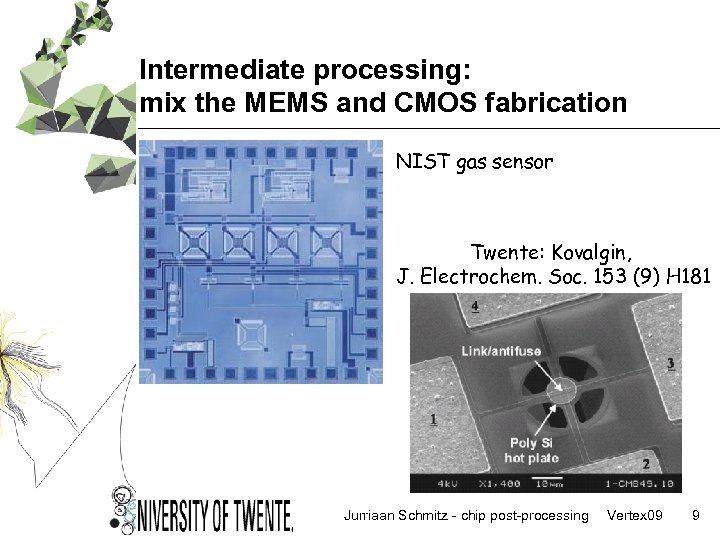

Intermediate processing: mix the MEMS and CMOS fabrication NIST gas sensor Twente: Kovalgin, J. Electrochem. Soc. 153 (9) H 181 Jurriaan Schmitz - chip post-processing Vertex 09 9

Intermediate processing: mix the MEMS and CMOS fabrication NIST gas sensor Twente: Kovalgin, J. Electrochem. Soc. 153 (9) H 181 Jurriaan Schmitz - chip post-processing Vertex 09 9

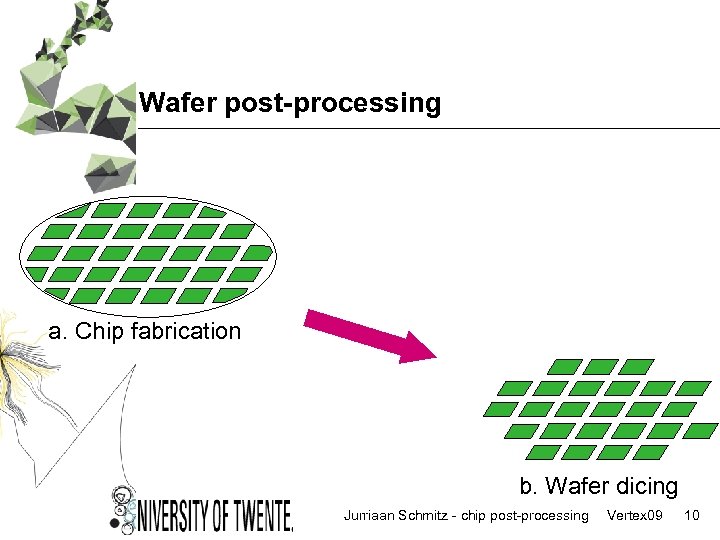

Wafer post-processing a. Chip fabrication b. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 10

Wafer post-processing a. Chip fabrication b. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 10

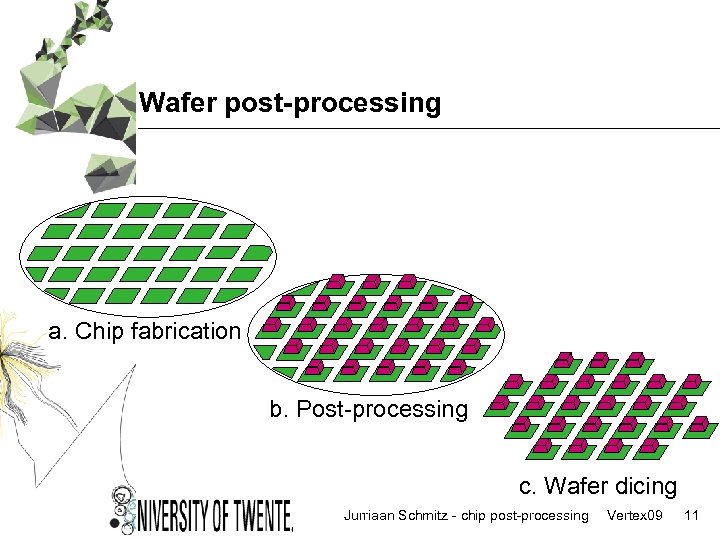

Wafer post-processing a. Chip fabrication b. Post-processing c. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 11

Wafer post-processing a. Chip fabrication b. Post-processing c. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 11

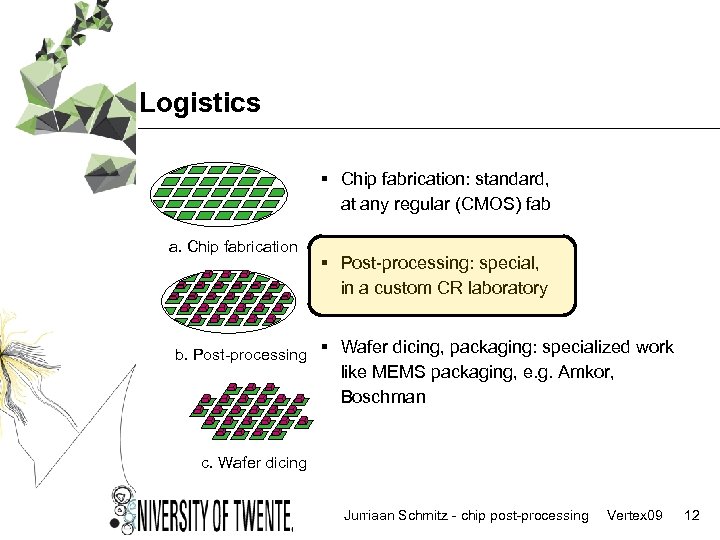

Logistics § Chip fabrication: standard, at any regular (CMOS) fab a. Chip fabrication § Post-processing: special, in a custom CR laboratory b. Post-processing § Wafer dicing, packaging: specialized work like MEMS packaging, e. g. Amkor, Boschman c. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 12

Logistics § Chip fabrication: standard, at any regular (CMOS) fab a. Chip fabrication § Post-processing: special, in a custom CR laboratory b. Post-processing § Wafer dicing, packaging: specialized work like MEMS packaging, e. g. Amkor, Boschman c. Wafer dicing Jurriaan Schmitz - chip post-processing Vertex 09 12

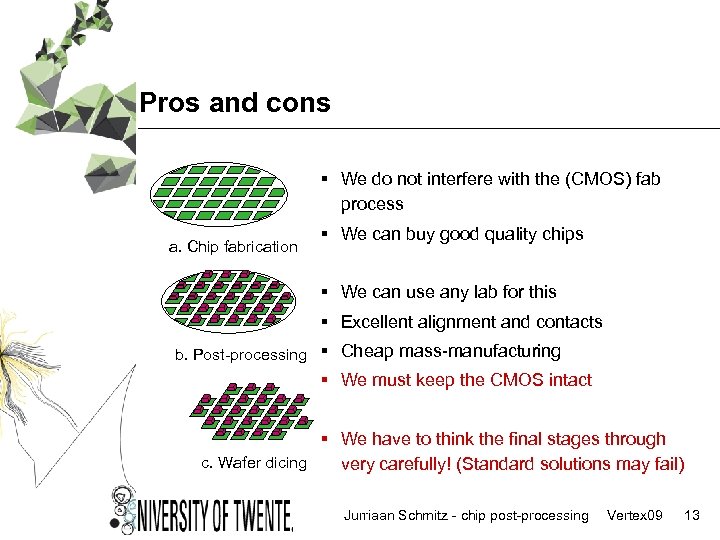

Pros and cons § We do not interfere with the (CMOS) fab process a. Chip fabrication § We can buy good quality chips § We can use any lab for this § Excellent alignment and contacts b. Post-processing § Cheap mass-manufacturing § We must keep the CMOS intact § We have to think the final stages through c. Wafer dicing very carefully! (Standard solutions may fail) Jurriaan Schmitz - chip post-processing Vertex 09 13

Pros and cons § We do not interfere with the (CMOS) fab process a. Chip fabrication § We can buy good quality chips § We can use any lab for this § Excellent alignment and contacts b. Post-processing § Cheap mass-manufacturing § We must keep the CMOS intact § We have to think the final stages through c. Wafer dicing very carefully! (Standard solutions may fail) Jurriaan Schmitz - chip post-processing Vertex 09 13

Outline § The concept of wafer post-processing § Successes of wafer post-processing § Active pixel sensors § LCo. S § Digital Micro. Mirrors § Recent results § Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 14

Outline § The concept of wafer post-processing § Successes of wafer post-processing § Active pixel sensors § LCo. S § Digital Micro. Mirrors § Recent results § Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 14

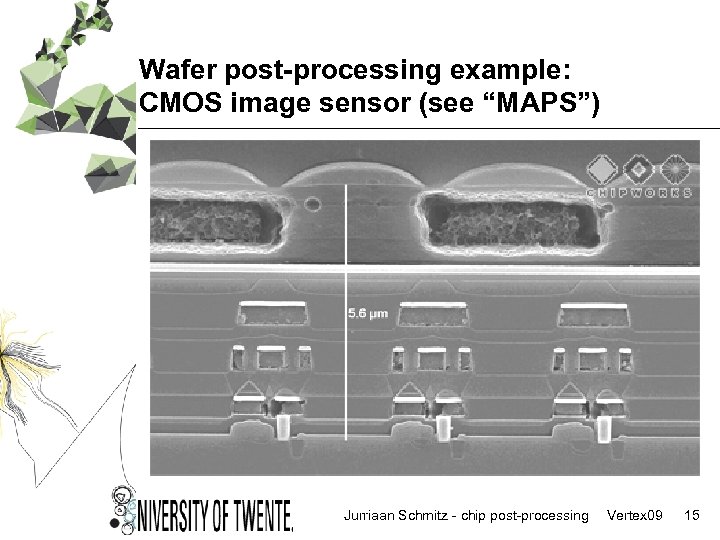

Wafer post-processing example: CMOS image sensor (see “MAPS”) Jurriaan Schmitz - chip post-processing Vertex 09 15

Wafer post-processing example: CMOS image sensor (see “MAPS”) Jurriaan Schmitz - chip post-processing Vertex 09 15

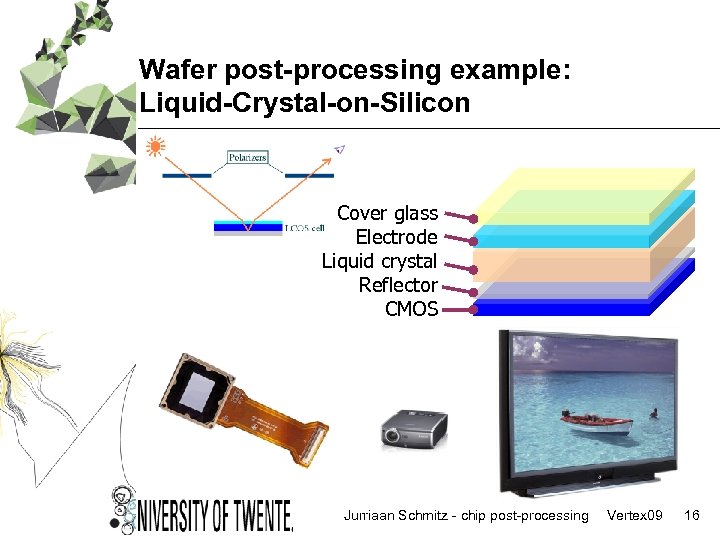

Wafer post-processing example: Liquid-Crystal-on-Silicon Cover glass Electrode Liquid crystal Reflector CMOS Jurriaan Schmitz - chip post-processing Vertex 09 16

Wafer post-processing example: Liquid-Crystal-on-Silicon Cover glass Electrode Liquid crystal Reflector CMOS Jurriaan Schmitz - chip post-processing Vertex 09 16

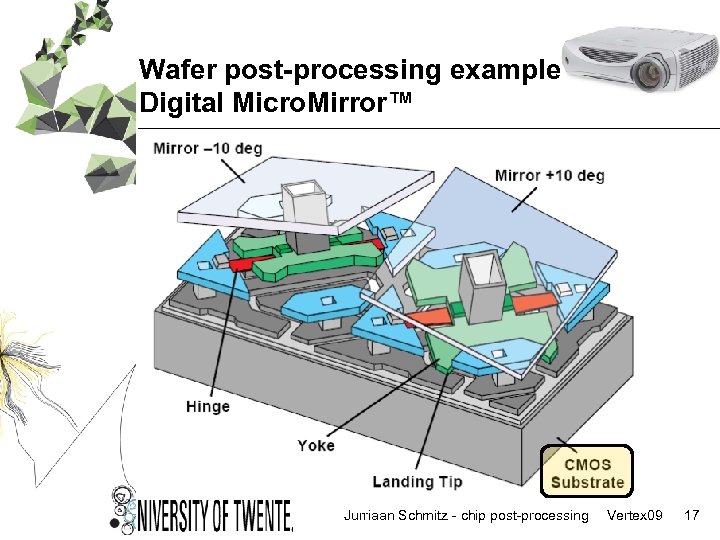

Wafer post-processing example: Digital Micro. Mirror™ Jurriaan Schmitz - chip post-processing Vertex 09 17

Wafer post-processing example: Digital Micro. Mirror™ Jurriaan Schmitz - chip post-processing Vertex 09 17

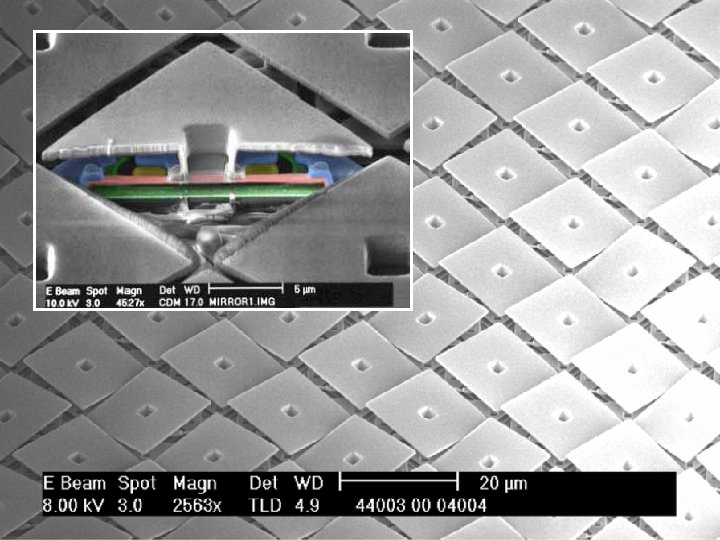

Jurriaan Schmitz - chip post-processing Vertex 09 18

Jurriaan Schmitz - chip post-processing Vertex 09 18

Outline § The concept of wafer post-processing § Successes of wafer post-processing § Recent results § Micromechanical structures § Photodetectors § 3 D electronics § Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 19

Outline § The concept of wafer post-processing § Successes of wafer post-processing § Recent results § Micromechanical structures § Photodetectors § 3 D electronics § Perspective for radiation imaging Jurriaan Schmitz - chip post-processing Vertex 09 19

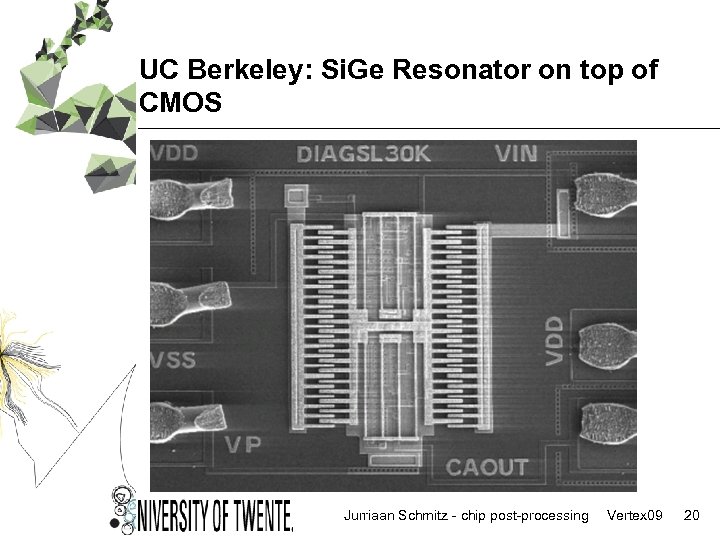

UC Berkeley: Si. Ge Resonator on top of CMOS Jurriaan Schmitz - chip post-processing Vertex 09 20

UC Berkeley: Si. Ge Resonator on top of CMOS Jurriaan Schmitz - chip post-processing Vertex 09 20

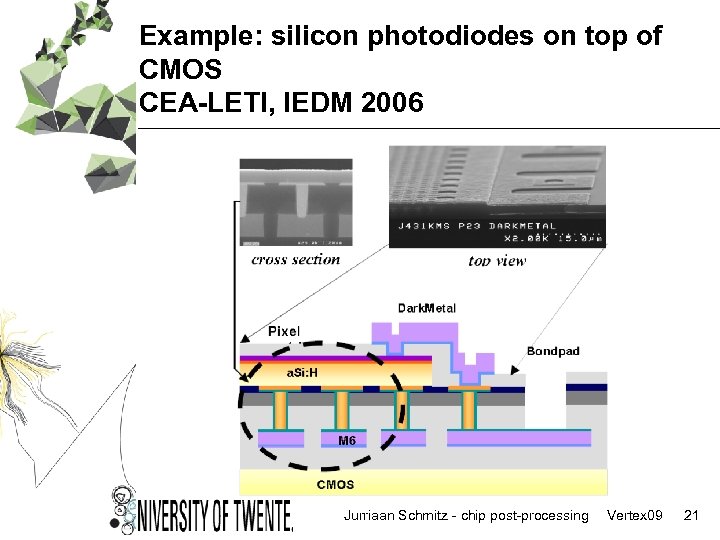

Example: silicon photodiodes on top of CMOS CEA-LETI, IEDM 2006 Jurriaan Schmitz - chip post-processing Vertex 09 21

Example: silicon photodiodes on top of CMOS CEA-LETI, IEDM 2006 Jurriaan Schmitz - chip post-processing Vertex 09 21

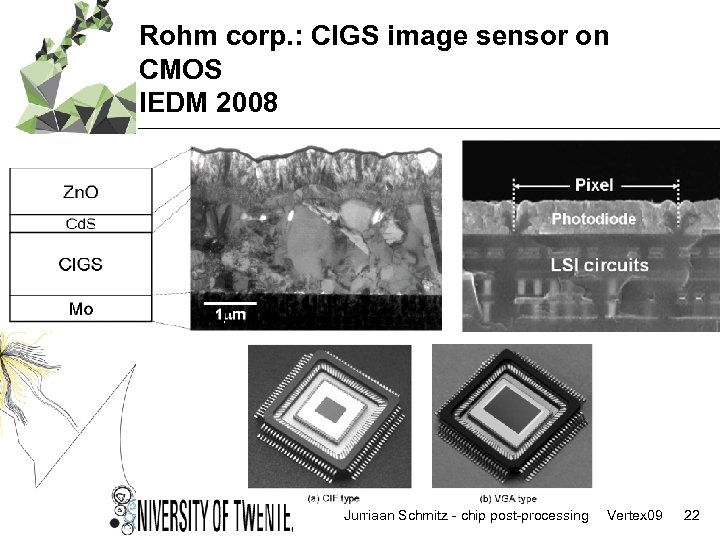

Rohm corp. : CIGS image sensor on CMOS IEDM 2008 Jurriaan Schmitz - chip post-processing Vertex 09 22

Rohm corp. : CIGS image sensor on CMOS IEDM 2008 Jurriaan Schmitz - chip post-processing Vertex 09 22

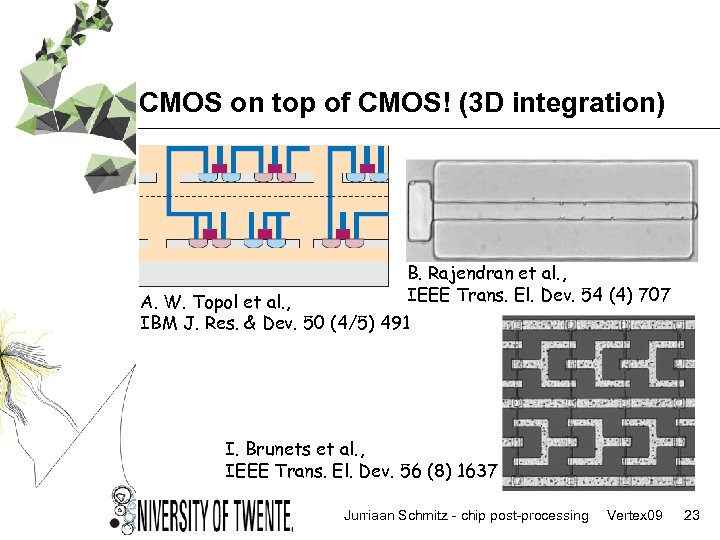

CMOS on top of CMOS! (3 D integration) B. Rajendran et al. , IEEE Trans. El. Dev. 54 (4) 707 A. W. Topol et al. , IBM J. Res. & Dev. 50 (4/5) 491 I. Brunets et al. , IEEE Trans. El. Dev. 56 (8) 1637 Jurriaan Schmitz - chip post-processing Vertex 09 23

CMOS on top of CMOS! (3 D integration) B. Rajendran et al. , IEEE Trans. El. Dev. 54 (4) 707 A. W. Topol et al. , IBM J. Res. & Dev. 50 (4/5) 491 I. Brunets et al. , IEEE Trans. El. Dev. 56 (8) 1637 Jurriaan Schmitz - chip post-processing Vertex 09 23

CMOS post-processing: game rules Careful treatment of the underlying CMOS: § Temperature ≤ 450 °C § Mild (or no) plasmas § Maintain the H balance in the MOSFET § Limited mechanical stress The CMOS properties must remain unchanged: only then the standard infrastructure can be used. Further reading: Jurriaan Schmitz, Nucl. Instr. Meth. A 576 (2007) 142. Jurriaan Schmitz - chip post-processing Vertex 09 24

CMOS post-processing: game rules Careful treatment of the underlying CMOS: § Temperature ≤ 450 °C § Mild (or no) plasmas § Maintain the H balance in the MOSFET § Limited mechanical stress The CMOS properties must remain unchanged: only then the standard infrastructure can be used. Further reading: Jurriaan Schmitz, Nucl. Instr. Meth. A 576 (2007) 142. Jurriaan Schmitz - chip post-processing Vertex 09 24

Outline § § The concept of wafer post-processing Successes of wafer post-processing Recent results Perspective for radiation imaging § MPGD: In. Grid/Grid. Pix § Future Jurriaan Schmitz - chip post-processing Vertex 09 25

Outline § § The concept of wafer post-processing Successes of wafer post-processing Recent results Perspective for radiation imaging § MPGD: In. Grid/Grid. Pix § Future Jurriaan Schmitz - chip post-processing Vertex 09 25

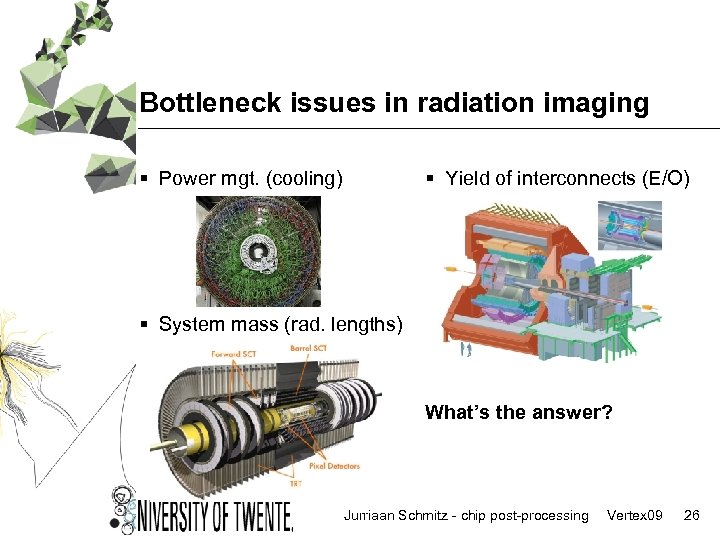

Bottleneck issues in radiation imaging § Power mgt. (cooling) § Yield of interconnects (E/O) § System mass (rad. lengths) What’s the answer? Jurriaan Schmitz - chip post-processing Vertex 09 26

Bottleneck issues in radiation imaging § Power mgt. (cooling) § Yield of interconnects (E/O) § System mass (rad. lengths) What’s the answer? Jurriaan Schmitz - chip post-processing Vertex 09 26

Bottleneck issues in electronics § Power mgt. (cooling) § Yield of interconnects § System mass Solution in electronics: Integration and miniaturization Jurriaan Schmitz - chip post-processing Vertex 09 27

Bottleneck issues in electronics § Power mgt. (cooling) § Yield of interconnects § System mass Solution in electronics: Integration and miniaturization Jurriaan Schmitz - chip post-processing Vertex 09 27

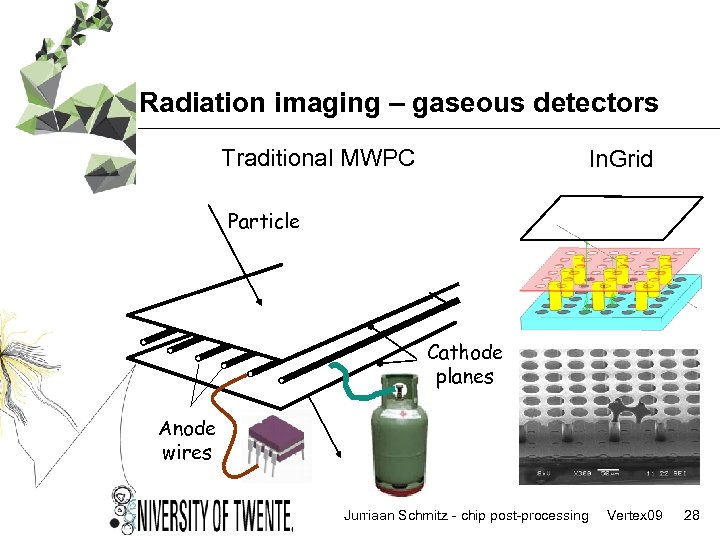

Radiation imaging – gaseous detectors Traditional MWPC In. Grid Particle Cathode planes Anode wires Jurriaan Schmitz - chip post-processing Vertex 09 28

Radiation imaging – gaseous detectors Traditional MWPC In. Grid Particle Cathode planes Anode wires Jurriaan Schmitz - chip post-processing Vertex 09 28

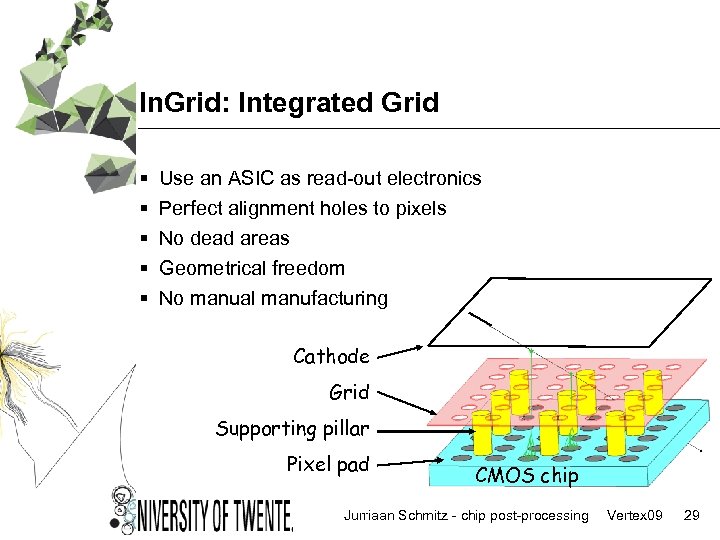

In. Grid: Integrated Grid § § § Use an ASIC as read-out electronics Perfect alignment holes to pixels No dead areas Geometrical freedom No manual manufacturing Cathode Grid Supporting pillar Pixel pad CMOS chip Jurriaan Schmitz - chip post-processing Vertex 09 29

In. Grid: Integrated Grid § § § Use an ASIC as read-out electronics Perfect alignment holes to pixels No dead areas Geometrical freedom No manual manufacturing Cathode Grid Supporting pillar Pixel pad CMOS chip Jurriaan Schmitz - chip post-processing Vertex 09 29

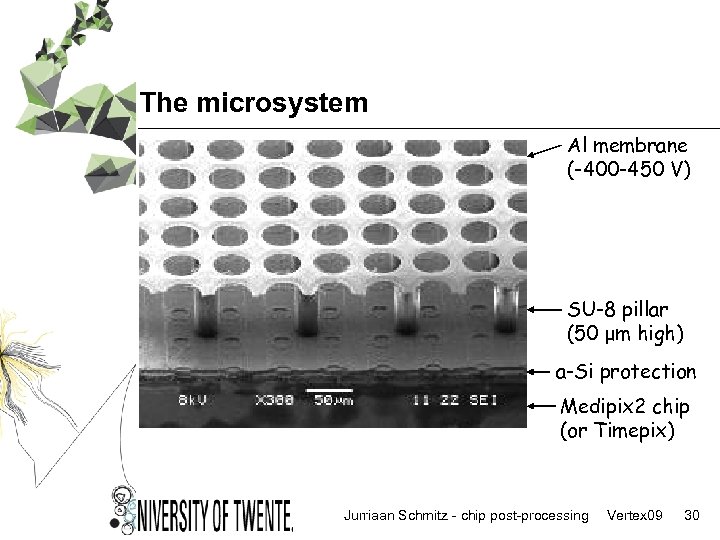

The microsystem Al membrane (-400 -450 V) SU-8 pillar (50 μm high) a-Si protection Medipix 2 chip (or Timepix) Jurriaan Schmitz - chip post-processing Vertex 09 30

The microsystem Al membrane (-400 -450 V) SU-8 pillar (50 μm high) a-Si protection Medipix 2 chip (or Timepix) Jurriaan Schmitz - chip post-processing Vertex 09 30

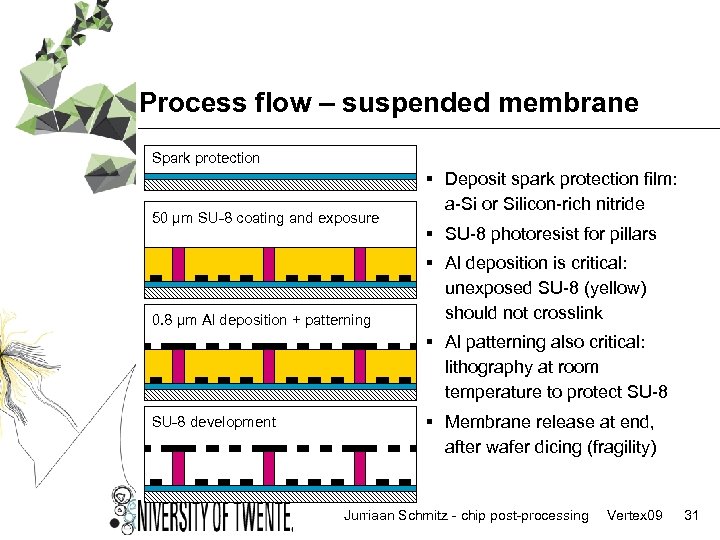

Process flow – suspended membrane Spark protection 50 µm SU-8 coating and exposure 0. 8 µm Al deposition + patterning § Deposit spark protection film: a-Si or Silicon-rich nitride § SU-8 photoresist for pillars § Al deposition is critical: unexposed SU-8 (yellow) should not crosslink § Al patterning also critical: lithography at room temperature to protect SU-8 development § Membrane release at end, after wafer dicing (fragility) Jurriaan Schmitz - chip post-processing Vertex 09 31

Process flow – suspended membrane Spark protection 50 µm SU-8 coating and exposure 0. 8 µm Al deposition + patterning § Deposit spark protection film: a-Si or Silicon-rich nitride § SU-8 photoresist for pillars § Al deposition is critical: unexposed SU-8 (yellow) should not crosslink § Al patterning also critical: lithography at room temperature to protect SU-8 development § Membrane release at end, after wafer dicing (fragility) Jurriaan Schmitz - chip post-processing Vertex 09 31

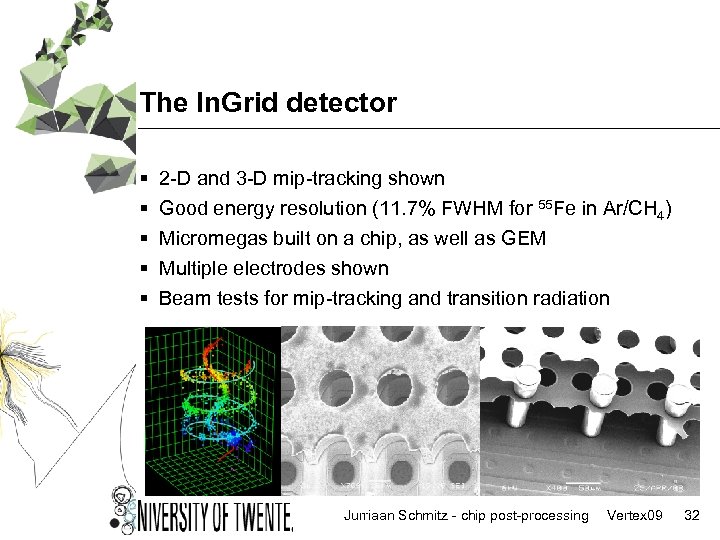

The In. Grid detector § § § 2 -D and 3 -D mip-tracking shown Good energy resolution (11. 7% FWHM for 55 Fe in Ar/CH 4) Micromegas built on a chip, as well as GEM Multiple electrodes shown Beam tests for mip-tracking and transition radiation Jurriaan Schmitz - chip post-processing Vertex 09 32

The In. Grid detector § § § 2 -D and 3 -D mip-tracking shown Good energy resolution (11. 7% FWHM for 55 Fe in Ar/CH 4) Micromegas built on a chip, as well as GEM Multiple electrodes shown Beam tests for mip-tracking and transition radiation Jurriaan Schmitz - chip post-processing Vertex 09 32

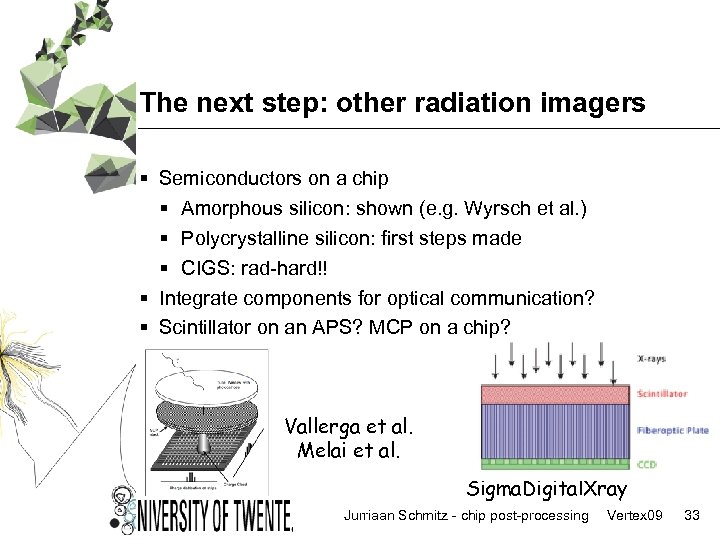

The next step: other radiation imagers § Semiconductors on a chip § Amorphous silicon: shown (e. g. Wyrsch et al. ) § Polycrystalline silicon: first steps made § CIGS: rad-hard!! § Integrate components for optical communication? § Scintillator on an APS? MCP on a chip? Vallerga et al. Melai et al. Sigma. Digital. Xray Jurriaan Schmitz - chip post-processing Vertex 09 33

The next step: other radiation imagers § Semiconductors on a chip § Amorphous silicon: shown (e. g. Wyrsch et al. ) § Polycrystalline silicon: first steps made § CIGS: rad-hard!! § Integrate components for optical communication? § Scintillator on an APS? MCP on a chip? Vallerga et al. Melai et al. Sigma. Digital. Xray Jurriaan Schmitz - chip post-processing Vertex 09 33

Conclusions What can we build on top of CMOS? § Light projectors § CMOS imagers § More electronics § Radiation imaging detectors § … There’s plenty of room at the top! Jurriaan Schmitz - chip post-processing Vertex 09 34

Conclusions What can we build on top of CMOS? § Light projectors § CMOS imagers § More electronics § Radiation imaging detectors § … There’s plenty of room at the top! Jurriaan Schmitz - chip post-processing Vertex 09 34

Thanks… My low-temperature coworkers: § Tom Aarnink, Victor Blanco Carballo, Arjen Boogaard, Ihor Brunets, Jisk Holleman, Alexey Kovalgin, Jiwu Lu, Joost Melai, Cora Salm, Sander Smits, Rob Wolters, Yevgen Bilevych, Marten Bosma, Max Chefdeville, Harry van der Graaf, Martin Fransen, Jan Visschers, Jan Timmermans Our sponsors: § The Dutch Technology Foundation, FOM § NXP Research, Adixen/Alcatel, ASM International …and the Medipix consortium Jurriaan Schmitz - chip post-processing Vertex 09 35

Thanks… My low-temperature coworkers: § Tom Aarnink, Victor Blanco Carballo, Arjen Boogaard, Ihor Brunets, Jisk Holleman, Alexey Kovalgin, Jiwu Lu, Joost Melai, Cora Salm, Sander Smits, Rob Wolters, Yevgen Bilevych, Marten Bosma, Max Chefdeville, Harry van der Graaf, Martin Fransen, Jan Visschers, Jan Timmermans Our sponsors: § The Dutch Technology Foundation, FOM § NXP Research, Adixen/Alcatel, ASM International …and the Medipix consortium Jurriaan Schmitz - chip post-processing Vertex 09 35