Гр. 140 301 Рощин Л. Ю.

Гр. 140 301 Рощин Л. Ю.

DRAM (Dynamic Random Access Memory) — тип энергозависимой полупроводниковой памяти с произвольным доступом (RAM), также запоминающее устройство, наиболее широко используемое в качестве ОЗУ современных компьютеров. Физически DRAM память представляет собой набор запоминающих ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри полупроводниковой микросхем памяти. При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи. Такое динамическое поддержание заряда конденсатора является основополагающим принципом работы памяти типа DRAM. Конденсаторы заряжают в случае, когда в «ячейку» записывается единичный бит, и разряжают в случае, когда в «ячейку» необходимо записывать нулевой бит. Важным элементом памяти этого типа является чувствительный усилитель (англ. sense amp), подключенный к каждому из столбцов «прямоугольника» . Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей. «Прямоугольник» , реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком. Именно страница является минимальной порцией обмена с динамической памятью, потому что обмен данными с отдельно взятой ячейкой невозможен.

DRAM (Dynamic Random Access Memory) — тип энергозависимой полупроводниковой памяти с произвольным доступом (RAM), также запоминающее устройство, наиболее широко используемое в качестве ОЗУ современных компьютеров. Физически DRAM память представляет собой набор запоминающих ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри полупроводниковой микросхем памяти. При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи. Такое динамическое поддержание заряда конденсатора является основополагающим принципом работы памяти типа DRAM. Конденсаторы заряжают в случае, когда в «ячейку» записывается единичный бит, и разряжают в случае, когда в «ячейку» необходимо записывать нулевой бит. Важным элементом памяти этого типа является чувствительный усилитель (англ. sense amp), подключенный к каждому из столбцов «прямоугольника» . Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей. «Прямоугольник» , реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком. Именно страница является минимальной порцией обмена с динамической памятью, потому что обмен данными с отдельно взятой ячейкой невозможен.

Транзистор в динамической ячейке работает как ключ, управляющий передачей заряда. При записи в конденсатор бита информации ключ открывается, заряжая конденсатор до определенной величины.

Транзистор в динамической ячейке работает как ключ, управляющий передачей заряда. При записи в конденсатор бита информации ключ открывается, заряжая конденсатор до определенной величины.

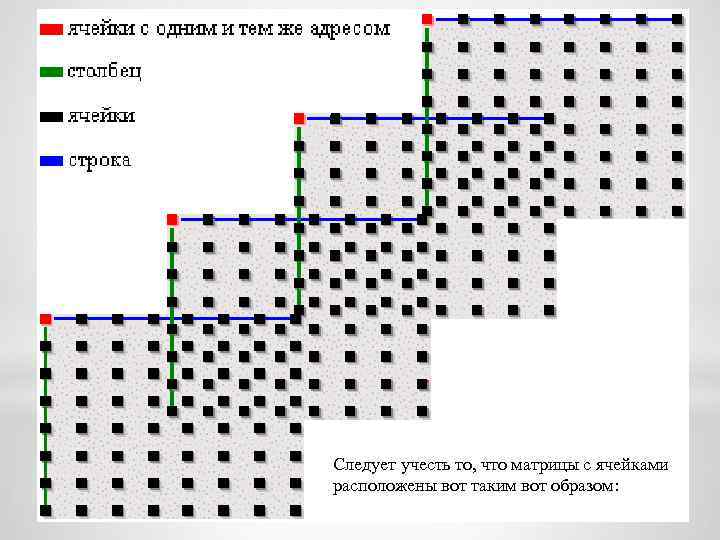

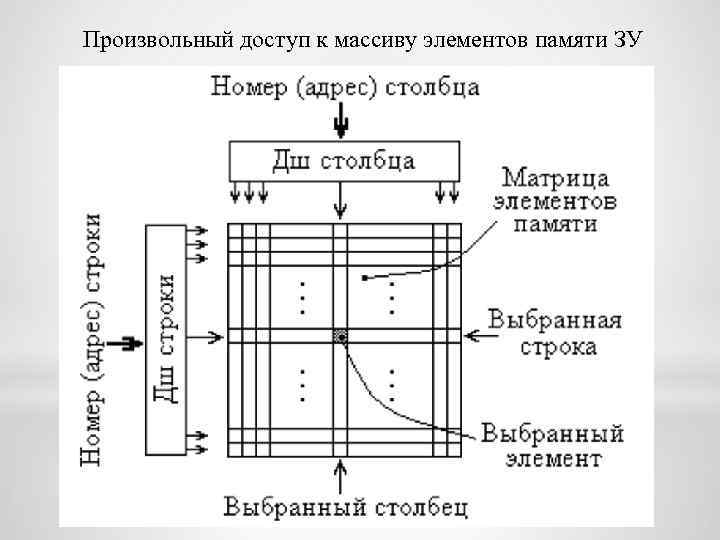

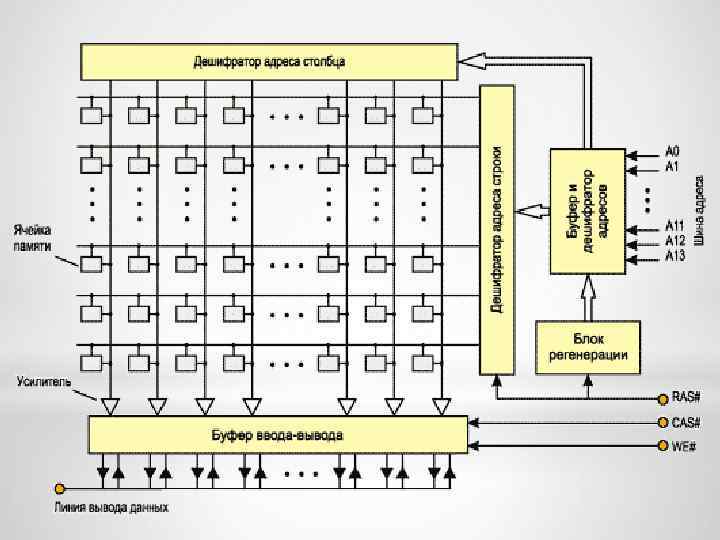

Следует учесть то, что матрицы с ячейками расположены вот таким вот образом:

Следует учесть то, что матрицы с ячейками расположены вот таким вот образом:

Это означает, что за один раз будет считан не один бит, а несколько. Если параллельно расположено 8 матриц, то сразу считан будет один байт. Это называется разрядностью. Количество линий, по которым будут передаваться данные от (или на) параллельных матриц, определяется разрядностью шины ввода/вывода микросхемы. С точки зрения системы команд память это набор слов, каждое из которых имеет уникальный адрес, показывающий расположе ние слова в памяти. Концепция адресов памяти эквивалента концепции телефон ных омеров. Каждый телефон имеет н свой собственный номер в некото ром оле возможных номеров. Подобно этому каждая п ячейка памяти имеет адрес который определяет модуль памяти и расположение ячейки в этом модуле. Каждое слово памяти содержит один или более адресуемых байт. Количество адресуемых байт определяется разрядностью микропроцес сора. Например, восьмибитные микропроцессоры имеют байтовую орга низацию памяти. За одно обращение микропроцессор может обработать только один байт информации. Шестнадца ти разрядные микропроцес соры огут обращаться к одному или двум байтам м одновременно. 32 разрядны микропроцессоры могут работать с 32 разрядными словами 16 разрядными словами и 8 разрядными байтами. Поэтому память для этих микропроцессоров организована таким образом чтобы допускать обращение к одному, двум или четырем байтам одновременно. Количество адресуемых ячеек памяти зависит от количества бит шины адреса микропроцессора. 8 ми разрядные микропроцессоры и микроконтроллеры имеет 16 битную шину адреса позволяя адресовать 64 Кбайт памяти. 16 разрядные микропроцессоры позволяют адресовать несколько мегабайт памяти. Наконец, современ ные икропроцессоры используют 64 разрядную шину адреса, что м позволяет адресовать фактически бесконечный объем памяти.

Это означает, что за один раз будет считан не один бит, а несколько. Если параллельно расположено 8 матриц, то сразу считан будет один байт. Это называется разрядностью. Количество линий, по которым будут передаваться данные от (или на) параллельных матриц, определяется разрядностью шины ввода/вывода микросхемы. С точки зрения системы команд память это набор слов, каждое из которых имеет уникальный адрес, показывающий расположе ние слова в памяти. Концепция адресов памяти эквивалента концепции телефон ных омеров. Каждый телефон имеет н свой собственный номер в некото ром оле возможных номеров. Подобно этому каждая п ячейка памяти имеет адрес который определяет модуль памяти и расположение ячейки в этом модуле. Каждое слово памяти содержит один или более адресуемых байт. Количество адресуемых байт определяется разрядностью микропроцес сора. Например, восьмибитные микропроцессоры имеют байтовую орга низацию памяти. За одно обращение микропроцессор может обработать только один байт информации. Шестнадца ти разрядные микропроцес соры огут обращаться к одному или двум байтам м одновременно. 32 разрядны микропроцессоры могут работать с 32 разрядными словами 16 разрядными словами и 8 разрядными байтами. Поэтому память для этих микропроцессоров организована таким образом чтобы допускать обращение к одному, двум или четырем байтам одновременно. Количество адресуемых ячеек памяти зависит от количества бит шины адреса микропроцессора. 8 ми разрядные микропроцессоры и микроконтроллеры имеет 16 битную шину адреса позволяя адресовать 64 Кбайт памяти. 16 разрядные микропроцессоры позволяют адресовать несколько мегабайт памяти. Наконец, современ ные икропроцессоры используют 64 разрядную шину адреса, что м позволяет адресовать фактически бесконечный объем памяти.

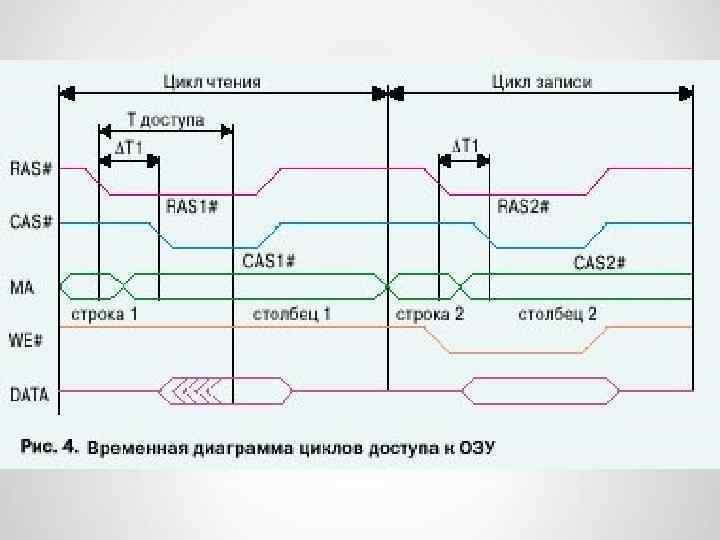

Основными характеристиками DRAM являются рабочая частота и тайминги. При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом. Основными таймингами DRAM являются: RCD (RAS-to-CAS Delay) это задержка между сигналами RAS (Row Address Strobe) и CAS (Column Address Strobe), данный параметр характеризует интервал между доступами на шину контроллером памяти сигналов RAS# и CAS#. CAS Latency (CL) это задержка между командой чтения и доступностью к чтению первого слова. Введена для набора адресными регистрами гарантированно устойчивого уровня сигнала. RAS Precharge (RP) это время повторной выдачи (период накопления заряда) сигнала RAS# через какое время контроллер памяти будет способен снова выдать сигнал инициализации адреса строки. Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Основными характеристиками DRAM являются рабочая частота и тайминги. При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом. Основными таймингами DRAM являются: RCD (RAS-to-CAS Delay) это задержка между сигналами RAS (Row Address Strobe) и CAS (Column Address Strobe), данный параметр характеризует интервал между доступами на шину контроллером памяти сигналов RAS# и CAS#. CAS Latency (CL) это задержка между командой чтения и доступностью к чтению первого слова. Введена для набора адресными регистрами гарантированно устойчивого уровня сигнала. RAS Precharge (RP) это время повторной выдачи (период накопления заряда) сигнала RAS# через какое время контроллер памяти будет способен снова выдать сигнал инициализации адреса строки. Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Произвольный доступ к массиву элементов памяти ЗУ

Произвольный доступ к массиву элементов памяти ЗУ

В процессе обращения к микросхеме динамической памяти для записи и считывания информации на ее адресные входы подается вначале — код адреса и одновременно с ним сигнал RAS, затем с незначительной задержкой, код адреса столбца, сопровождаемый сигналом CAS. Время доступа к блоку RAM определяется в первую очередь временем чтения (разряд конденсатора) и регенерации (заряд конденсатора). Рассмотрим подробнее. При обращении к памяти (независимо от того чтение это или запись) на входы памяти подается адрес строки и сигнал RAS. Это значит, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Поскольку информация хранится в виде заряда конденсатора, то для того чтобы считать записанную в ячейке информацию, необходимо устройство с высоким входным сопротивлением, ограничивающим ток разряда конденсатора, чтобы избежать тока утечки. Таким устройством является считывающий усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помещается в регистр. Как уже отмечалось выше, с незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS. При чтении в соответствии с адресом столбца данные выбираются из регистра строки и подаются на выход динамической памяти. При считывании информации из запоминающих ячеек считывающие усилители разрушают ее, поэтому для сохранения информации необходима ее перезапись: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную из строки информацию. Если выполняется цикл записи в память, то подается сигнал WR (Write) и информация поступает на общую шину столбца не из регистра, а с информационного входа памяти через коммутатор, определенный адресом столбца. Таким образом, прохождение данных при записи определяется комбинацией сигналов адреса столбца и строки и разрешения записи данных в память. При записи данные из регистра строки на выход (Do) не поступают.

В процессе обращения к микросхеме динамической памяти для записи и считывания информации на ее адресные входы подается вначале — код адреса и одновременно с ним сигнал RAS, затем с незначительной задержкой, код адреса столбца, сопровождаемый сигналом CAS. Время доступа к блоку RAM определяется в первую очередь временем чтения (разряд конденсатора) и регенерации (заряд конденсатора). Рассмотрим подробнее. При обращении к памяти (независимо от того чтение это или запись) на входы памяти подается адрес строки и сигнал RAS. Это значит, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Поскольку информация хранится в виде заряда конденсатора, то для того чтобы считать записанную в ячейке информацию, необходимо устройство с высоким входным сопротивлением, ограничивающим ток разряда конденсатора, чтобы избежать тока утечки. Таким устройством является считывающий усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помещается в регистр. Как уже отмечалось выше, с незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS. При чтении в соответствии с адресом столбца данные выбираются из регистра строки и подаются на выход динамической памяти. При считывании информации из запоминающих ячеек считывающие усилители разрушают ее, поэтому для сохранения информации необходима ее перезапись: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную из строки информацию. Если выполняется цикл записи в память, то подается сигнал WR (Write) и информация поступает на общую шину столбца не из регистра, а с информационного входа памяти через коммутатор, определенный адресом столбца. Таким образом, прохождение данных при записи определяется комбинацией сигналов адреса столбца и строки и разрешения записи данных в память. При записи данные из регистра строки на выход (Do) не поступают.

Помимо режимов записи и считывания, которые определяются потенциалом на входе WR, существует режим хранения данных, в котором запись и считывание запрещены. Режим хранения имеет двоякий смысл. Во первых, если в устройстве много микросхем ОЗУ, что характерно, то запись или считывание ведется по одной микросхеме, остальные в этом случае должны быть отключены. Во вторых, в режиме хранения данных энергопотребление намного меньше, чем в режиме записи и считывания (рабочий режим). Для перевода ОЗУ в режим хранения используется сигнал CS, (crystal selection) выбор кристалла. Обычно для перевода в режим хранения на вход CS подается уровень лог. 1, для перевода в рабочий режим лог. 0.

Помимо режимов записи и считывания, которые определяются потенциалом на входе WR, существует режим хранения данных, в котором запись и считывание запрещены. Режим хранения имеет двоякий смысл. Во первых, если в устройстве много микросхем ОЗУ, что характерно, то запись или считывание ведется по одной микросхеме, остальные в этом случае должны быть отключены. Во вторых, в режиме хранения данных энергопотребление намного меньше, чем в режиме записи и считывания (рабочий режим). Для перевода ОЗУ в режим хранения используется сигнал CS, (crystal selection) выбор кристалла. Обычно для перевода в режим хранения на вход CS подается уровень лог. 1, для перевода в рабочий режим лог. 0.

Память DRAM изготавливается на основе конденсаторов небольшой ёмкости, которые быстро теряют заряд, поэтому информацию приходится обновлять через определённые промежутки времени во избежание потерь данных. Этот процесс называется регенерацией памяти. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации, в DRAM перезаписывается целая строка «ячеек» , и через 8 64 мс обновляются все строки памяти. Процесс регенерации памяти в классическом варианте существенно «тормозит» работу системы, поскольку в это время обмен данными с памятью невозможен. Регенерация, основанная на обычном переборе строк, не применяется в современных типах DRAM. Существует несколько более экономичных вариантов этого процесса — расширенный, пакетный, распределенный; наиболее экономичной является скрытая (теневая) регенерация.

Память DRAM изготавливается на основе конденсаторов небольшой ёмкости, которые быстро теряют заряд, поэтому информацию приходится обновлять через определённые промежутки времени во избежание потерь данных. Этот процесс называется регенерацией памяти. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации, в DRAM перезаписывается целая строка «ячеек» , и через 8 64 мс обновляются все строки памяти. Процесс регенерации памяти в классическом варианте существенно «тормозит» работу системы, поскольку в это время обмен данными с памятью невозможен. Регенерация, основанная на обычном переборе строк, не применяется в современных типах DRAM. Существует несколько более экономичных вариантов этого процесса — расширенный, пакетный, распределенный; наиболее экономичной является скрытая (теневая) регенерация.

Процесс регенерации памяти в классическом варианте регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. . В зависимости от объема и организации матрицы для однократной регенерации всего объема требуется 512, 1024, 2048 или 4096 циклов обращений. При равномерном распределении циклов регенерации (distributed refresh) период циклов регенерации (refresh rate) для стандартной памяти принимается 15. 6 мкс. Для памяти с расширенной регенерацией (extended refresh) допустим период между циклами 125 мкс. Возможен также вариант пакетной регенерации (burst refresh), когда все циклы регенерации собираются в пакет, во время которого обращение к памяти по чтению и записи блокируется. При количестве циклов 1024 эти пакеты будут периодически занимать шину памяти примерно на 130 мкс, что далеко не всегда допустимо. По этой причине практически всегда выполняется распределенная регенерация. Из новых технологий регенерации можно выделить тип регенерации PASR (англ. Partial Array Self Refresh), применяемый компанией Samsung в чипах памяти SDRAM с низким уровнем энергопотребления. Регенерация «ячеек» выполняется только в период ожидания в тех банках памяти, в которых «имеются данные» . Параллельно с этой технологией реализуется метод TCSR (англ. Temperature Compensated Self Refresh), который предназначен для регулировки скорости процесса регенерации в зависимости от рабочей температуры.

Процесс регенерации памяти в классическом варианте регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. . В зависимости от объема и организации матрицы для однократной регенерации всего объема требуется 512, 1024, 2048 или 4096 циклов обращений. При равномерном распределении циклов регенерации (distributed refresh) период циклов регенерации (refresh rate) для стандартной памяти принимается 15. 6 мкс. Для памяти с расширенной регенерацией (extended refresh) допустим период между циклами 125 мкс. Возможен также вариант пакетной регенерации (burst refresh), когда все циклы регенерации собираются в пакет, во время которого обращение к памяти по чтению и записи блокируется. При количестве циклов 1024 эти пакеты будут периодически занимать шину памяти примерно на 130 мкс, что далеко не всегда допустимо. По этой причине практически всегда выполняется распределенная регенерация. Из новых технологий регенерации можно выделить тип регенерации PASR (англ. Partial Array Self Refresh), применяемый компанией Samsung в чипах памяти SDRAM с низким уровнем энергопотребления. Регенерация «ячеек» выполняется только в период ожидания в тех банках памяти, в которых «имеются данные» . Параллельно с этой технологией реализуется метод TCSR (англ. Temperature Compensated Self Refresh), который предназначен для регулировки скорости процесса регенерации в зависимости от рабочей температуры.

Экономичный вид памяти. Для хранения разряда (бита или трита) используется схема, состоящая из одного конденсатора и одного транзистора (в некоторых вариациях конденсаторов два) . Такой вид памяти решает: Во первых, проблему дороговизны (один конденсатор и один транзистор дешевле нескольких транзисторов). Во вторых, компактности (там, где в SRAM размещается один триггер, то есть один бит, можно уместить восемь конденсаторов и транзисторов), позволяет создавать память большой ёмкости.

Экономичный вид памяти. Для хранения разряда (бита или трита) используется схема, состоящая из одного конденсатора и одного транзистора (в некоторых вариациях конденсаторов два) . Такой вид памяти решает: Во первых, проблему дороговизны (один конденсатор и один транзистор дешевле нескольких транзисторов). Во вторых, компактности (там, где в SRAM размещается один триггер, то есть один бит, можно уместить восемь конденсаторов и транзисторов), позволяет создавать память большой ёмкости.

Во первых, память на основе конденсаторов работает медленнее, поскольку если в SRAM изменение напряжения на входе триггера сразу же приводит к изменению его состояния, то для того чтобы установить в единицу один разряд (один бит) памяти на основе конденсатора, этот конденсатор нужно зарядить, а для того чтобы разряд установить в ноль, соответственно, разрядить. А это гораздо более длительные операции, чем переключение триггера, даже если конденсатор имеет весьма небольшие размеры. Второй существенный минус — конденсаторы склонны к «стеканию» заряда; проще говоря, со временем конденсаторы разряжаются. Причём разряжаются они тем быстрее, чем меньше их ёмкость. Потери времени на первое обращение к ОЗУ, вне зависимости от типа DRAM, — «ахиллесова пята» динамической памяти. Высокая латентность, в основном, из за внутренней шины данных, в несколько раз более широкой, чем внешняя, и необходимости использования мультиплексора/демультиплексора;

Во первых, память на основе конденсаторов работает медленнее, поскольку если в SRAM изменение напряжения на входе триггера сразу же приводит к изменению его состояния, то для того чтобы установить в единицу один разряд (один бит) памяти на основе конденсатора, этот конденсатор нужно зарядить, а для того чтобы разряд установить в ноль, соответственно, разрядить. А это гораздо более длительные операции, чем переключение триггера, даже если конденсатор имеет весьма небольшие размеры. Второй существенный минус — конденсаторы склонны к «стеканию» заряда; проще говоря, со временем конденсаторы разряжаются. Причём разряжаются они тем быстрее, чем меньше их ёмкость. Потери времени на первое обращение к ОЗУ, вне зависимости от типа DRAM, — «ахиллесова пята» динамической памяти. Высокая латентность, в основном, из за внутренней шины данных, в несколько раз более широкой, чем внешняя, и необходимости использования мультиплексора/демультиплексора;

FPM DRAM (Fast Page Mode Dram) микросхемы памяти, реализующие страничный режим. Этот тип памяти появился в последних моделях компьютеров с процессором 80486 и получил широкое распространение. Время доступа процессора к памяти при использовании микросхем FPM DRAM сокращается на 50% по сравнению с обычными DRAM. EDO DRAM (Extended Data Output) память с расширенным выводом данных Широко применялась в процессорах Pentium. За счет наличия дополнительных регистров для хранения данных увеличивается объем данных, выводимых из памяти в единицу времени. Модули EDO RAM работают на 10 -15% быстрее, чем FPM DRAM. SDRAM (Sychronous DRAM) - Основная особенность данного вида памяти заключается в том, что все операции синхронизированы с тактовой частотой процессора, т. е. память и CPU работают синхронно. Синхронный интерфейс позволяет эффективно использовать шину и обеспечить на частоте 100 МГц пиковую производительность 100 Мбит/пин. При частоте 133 МГц пиковую производительность достигает 1064 Мбайт/с. DDR SDRAM представляет собой дальнейшее развитие SDRAM. Как и следует из названия (Dual Data Rate - удвоенная скорость данных), у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью - они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц DDR SDRAM имеет пиковую производительность 200 Мбит/пин, что в составе 8 -байтных модулей DIMM дает производительность 1600 Мбайт/с. RDRAM (Rambus DRAM) разработанная американской компанией Rambus. Память RDRAM синхронный интерфейс, является 9 -разрядной. Запоминающее ядро этой памяти построено на КМОП-ячейках динамической памяти. Тактовая частота 350 -400 МГц и достигает пиковой скорости передачи данных 1600 Мб/с. По сравнению с DDR SDRAM имеет более компактный интерфейс и большую масштабируемость. NVRAM использует для долговременного хранения данных, которые ни при каких обстоятельствах не должны быть утеряны. Буквы NV в имени обозначают Non Volatile, то есть “не временная”. Элементы NVRAM не нуждаются в электропитании и сохраняют свое содержимое в течение длительного времени.

FPM DRAM (Fast Page Mode Dram) микросхемы памяти, реализующие страничный режим. Этот тип памяти появился в последних моделях компьютеров с процессором 80486 и получил широкое распространение. Время доступа процессора к памяти при использовании микросхем FPM DRAM сокращается на 50% по сравнению с обычными DRAM. EDO DRAM (Extended Data Output) память с расширенным выводом данных Широко применялась в процессорах Pentium. За счет наличия дополнительных регистров для хранения данных увеличивается объем данных, выводимых из памяти в единицу времени. Модули EDO RAM работают на 10 -15% быстрее, чем FPM DRAM. SDRAM (Sychronous DRAM) - Основная особенность данного вида памяти заключается в том, что все операции синхронизированы с тактовой частотой процессора, т. е. память и CPU работают синхронно. Синхронный интерфейс позволяет эффективно использовать шину и обеспечить на частоте 100 МГц пиковую производительность 100 Мбит/пин. При частоте 133 МГц пиковую производительность достигает 1064 Мбайт/с. DDR SDRAM представляет собой дальнейшее развитие SDRAM. Как и следует из названия (Dual Data Rate - удвоенная скорость данных), у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью - они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц DDR SDRAM имеет пиковую производительность 200 Мбит/пин, что в составе 8 -байтных модулей DIMM дает производительность 1600 Мбайт/с. RDRAM (Rambus DRAM) разработанная американской компанией Rambus. Память RDRAM синхронный интерфейс, является 9 -разрядной. Запоминающее ядро этой памяти построено на КМОП-ячейках динамической памяти. Тактовая частота 350 -400 МГц и достигает пиковой скорости передачи данных 1600 Мб/с. По сравнению с DDR SDRAM имеет более компактный интерфейс и большую масштабируемость. NVRAM использует для долговременного хранения данных, которые ни при каких обстоятельствах не должны быть утеряны. Буквы NV в имени обозначают Non Volatile, то есть “не временная”. Элементы NVRAM не нуждаются в электропитании и сохраняют свое содержимое в течение длительного времени.