киселев.ppt

- Количество слайдов: 16

Государственное образовательное учреждение 1 Высшего профессионального образования «Санкт-Петербургский государственный политехнический университет» Факультет технической кибернетики Кафедра «Измерительные информационные технологии» Выпускная работа бакалавра Тема: устройство фазовой автоподстройки частоты на ПЛИС Направление: 230100 - Информатика и вычислительная техника Выполнил студент гр. 4085/11: А. А. Киселев Руководитель: Н. В. Богач Санкт-Петербург 2011

Плис Программируемая логическая интегральная микросхема (ПЛИС) - электронный компонент, используемый для создания цифровых интегральных схем. Отличительные черты ПЛИС : • параллельность • реконфигурируемость • универсальность 2

Классификация ИМС по технологии проектирования и изготовления • технические характеристики платы • время проектирования • функциональные возможности • стоимость разработки 3

Основные средства проектирования ORCAD, PSPICE A/D, Protel, MAX+PLUS II, Foundation, Aldec HDL, Synplicity, Lab. View, ISE Xilinx Функциональные особенности среды разработки ISE Xilinx • графический и текстовый методы описания проектируемых устройств • наличие схемотехнического редактора • поддержка языков VHDL и Verilog • развитые средства верификации проекта • автоматические средства трассировки проекта • поддержка технологий (CPLD и FPGA) • HDL Bencher, Model. Sim XE Starter и State. CAD 4

Преимущества реализации на ПЛИС по сравнению с «жесткой» логикой • возможность перепрограммирования непосредственно в системе • высокая степень интеграции • отладка без физического исполнения устройства • сравнительно низкая стоимость • применение разработанных решений в последующих проектах • ПК и САПР - основные средства разработки 5

Схема ФАПЧ и задачи, решаемые с ее помощью Фазовая автоподстройка частоты (ФАПЧ) – система автоматического регулирования, подстраивающая частоту управляемого генератора так, чтобы она была равна частоте опорного сигнала. Сферы применения: Применяется для: - для устранения дрожания фазы, возникающей по краям цифрового • радиотехника сигнала • телекоммуникационные технологии - для повышения чувствительности приемника • компьютерные системы - для выделения тактовой частоты принимаемого сигнала 6 - для синхронизации приемной и

Структурная схема ЦФАПЧ Режимы работы: - режим биений - процесс захвата - режим слежения - режим срыва 7

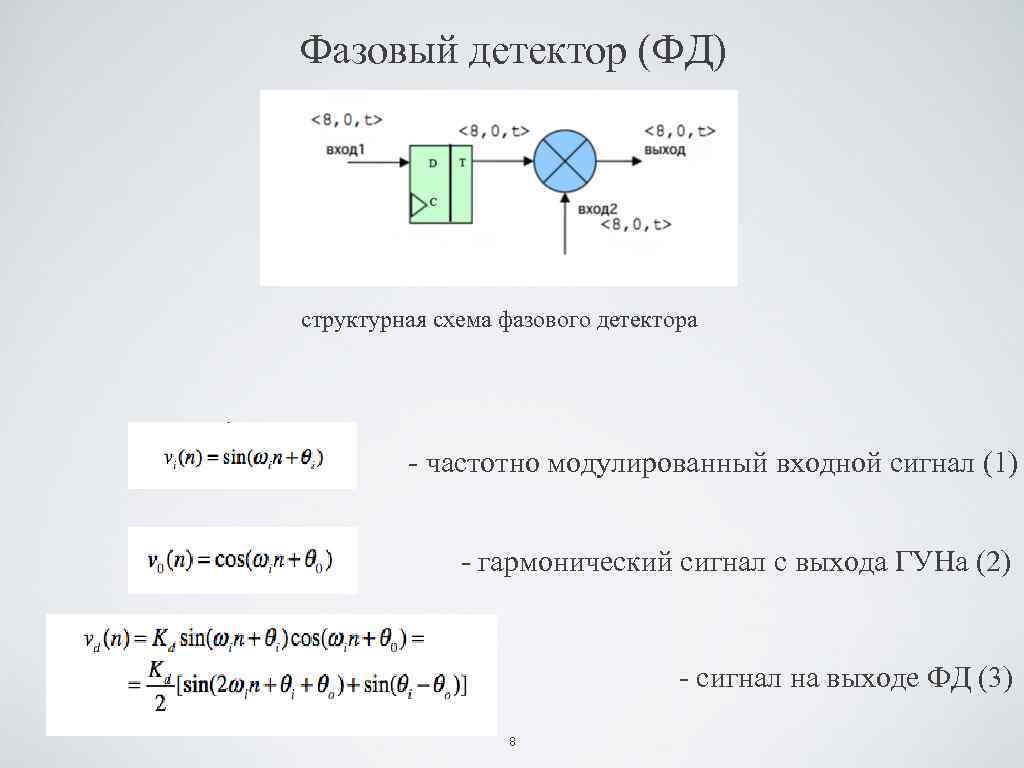

Фазовый детектор (ФД) структурная схема фазового детектора - частотно модулированный входной сигнал (1) - гармонический сигнал с выхода ГУНа (2) - сигнал на выходе ФД (3) 8

Алгоритм Бута 9

Петлевой фильтр Структурная схема петлевого фильтра - передаточная функция петлевого фильтра 10

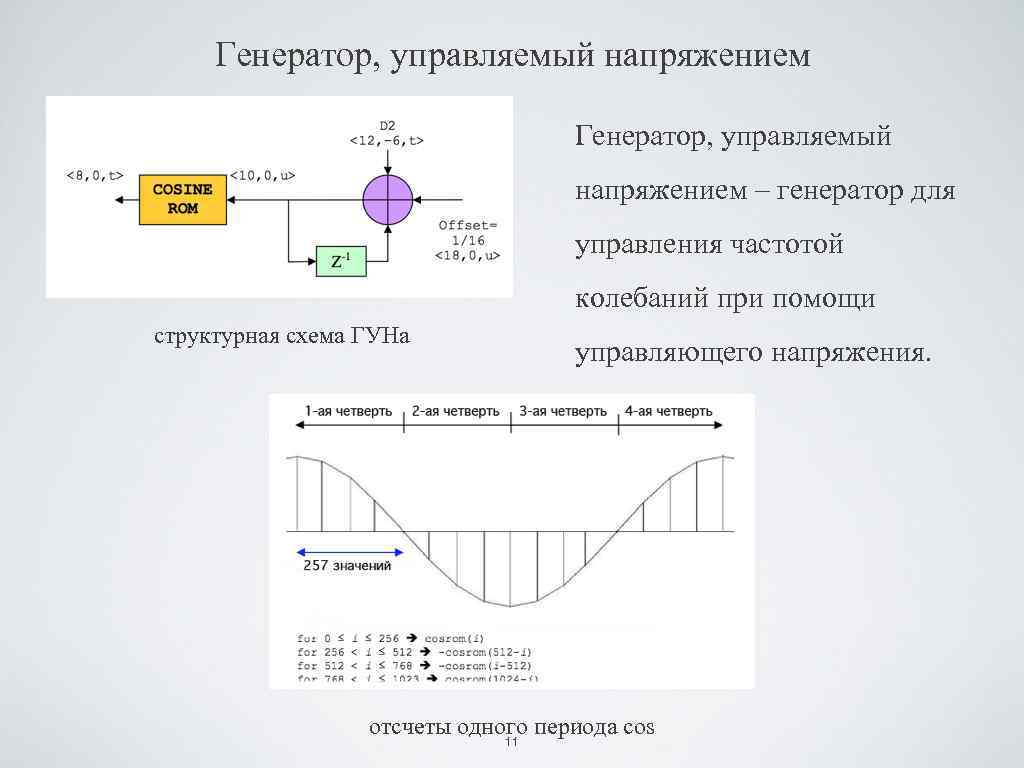

Генератор, управляемый напряжением – генератор для управления частотой колебаний при помощи структурная схема ГУНа управляющего напряжения. отсчеты одного периода cos 11

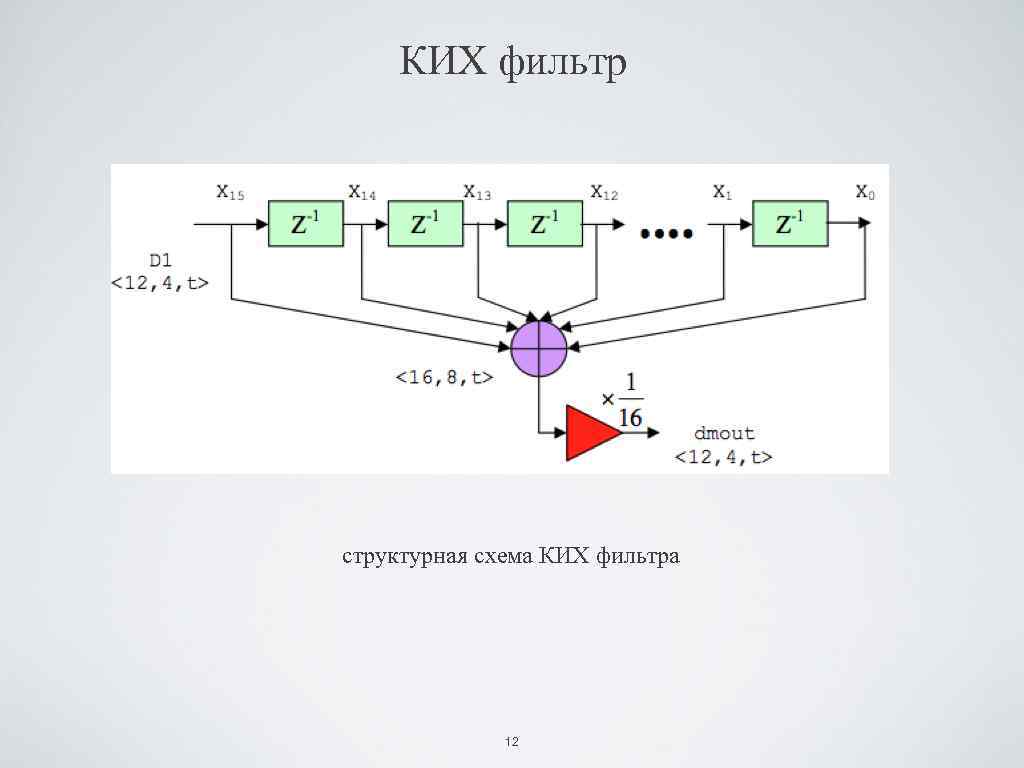

КИХ фильтр структурная схема КИХ фильтра 12

Полная структурная схема демодулирования частотного сигнала на основе ЦФАПЧ 13

Основные этапы проектирования в среде ISE Xilinx 14 1) cоздание принципиальной схемы 2) временное моделирование для выявления ошибок (Behavioral Simulation) 3) привязка выводов проекта к входам-выводам кристалла (Constraints Editor) 4) запуск автоматизированного размещения проекта в кристалле (Implement Design) 5) верификация проекта, т. е. окончательное временное моделирование (Post-Fit Simulation)

Результаты работы 15

Выводы по работе: По итогам работы можно заключить, что схема была реализована. Мы оптимизировали операцию умножения. В результате применения алгоритма Бута, вместо арифметического перемножителя, удалось снизить количество используемых системных вентилей с 689 до 453. Для реализации ГУНа, мы использовали 257 х8 бит ПЗУ вместо 1024 х8, что позволит сэкономить адресную область. К сожалению, в ISE Webpack ограничено время симуляции проекта, что не позволило нам увидеть на графике весь процесс. 16

киселев.ppt