Глава 7 М И К

ddca_ch7.pptx

- Размер: 6.8 Мб

- Автор: Владимир Алексеев

- Количество слайдов: 134

Описание презентации Глава 7 М И К по слайдам

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЦифровая схемотехника и архитектура компьютера, второе издание Глава 7 Дэвид М. Харрис и Сара Л. Харрис

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЦифровая схемотехника и архитектура компьютера, второе издание Глава 7 Дэвид М. Харрис и Сара Л. Харрис

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЦифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника «Цифровая схемотехника и архитектура компьютера» авторов Дэвида Харриса и Сары Харрис. Бесплатный русский перевод второго издания этого учебника можно загрузить с сайта компании Imagination Technologies: https: //community. imgtec. com/downloads/digital-design-and-computer-a rchitecture-russian-edition-second-edition Процедура регистрации на сайте компании Imagination Technologies описана на станице: http: //www. silicon-russia. com/2016/08/04/harris-and-harris-2/

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЦифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника «Цифровая схемотехника и архитектура компьютера» авторов Дэвида Харриса и Сары Харрис. Бесплатный русский перевод второго издания этого учебника можно загрузить с сайта компании Imagination Technologies: https: //community. imgtec. com/downloads/digital-design-and-computer-a rchitecture-russian-edition-second-edition Процедура регистрации на сайте компании Imagination Technologies описана на станице: http: //www. silicon-russia. com/2016/08/04/harris-and-harris-2/

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АБлагодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России, Украины, США в составе: • Александр Барабанов — доцент кафедры компьютерной инженерии факультета радиофизики, электроники и компьютерных систем Киевского национального университета имени Тараса Шевченко, кандидат физ. -мат. наук, Киев, Украина; • Антон Брюзгин — начальник отдела АО «Вибро-прибор» , Санкт-Петербург, Россия. • Евгений Короткий — доцент кафедры конструирования электронно-вычислительной аппаратуры факультета электроники Национального технического университета Украины «Киевский Политехнический Институт» , руководитель открытой лаборатории электроники Lampa, кандидат технических наук, Киев, Украина; • Евгения Литвинова – заместитель декана факультета компьютерной инженерии и управления, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Юрий Панчул — старший инженер по разработке и верификации блоков микропроцессорного ядра в команде MIPS I 6400, Imagination Technologies, отделение в Санта-Кларе, Калифорния, США; • Дмитрий Рожко — инженер-программист АО «Вибро-прибор» , магистр Санкт-Петербургского государственного автономного университета аэрокосмического приборостроения (ГУАП), Санкт-Петербург, Россия; • Владимир Хаханов – декан факультета компьютерной инженерии и управления, проректор по научной работе, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Светлана Чумаченко – заведующая кафедрой автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, доктор технических наук, профессор, Харьков, Украина.

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АБлагодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России, Украины, США в составе: • Александр Барабанов — доцент кафедры компьютерной инженерии факультета радиофизики, электроники и компьютерных систем Киевского национального университета имени Тараса Шевченко, кандидат физ. -мат. наук, Киев, Украина; • Антон Брюзгин — начальник отдела АО «Вибро-прибор» , Санкт-Петербург, Россия. • Евгений Короткий — доцент кафедры конструирования электронно-вычислительной аппаратуры факультета электроники Национального технического университета Украины «Киевский Политехнический Институт» , руководитель открытой лаборатории электроники Lampa, кандидат технических наук, Киев, Украина; • Евгения Литвинова – заместитель декана факультета компьютерной инженерии и управления, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Юрий Панчул — старший инженер по разработке и верификации блоков микропроцессорного ядра в команде MIPS I 6400, Imagination Technologies, отделение в Санта-Кларе, Калифорния, США; • Дмитрий Рожко — инженер-программист АО «Вибро-прибор» , магистр Санкт-Петербургского государственного автономного университета аэрокосмического приборостроения (ГУАП), Санкт-Петербург, Россия; • Владимир Хаханов – декан факультета компьютерной инженерии и управления, проректор по научной работе, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Светлана Чумаченко – заведующая кафедрой автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, доктор технических наук, профессор, Харьков, Украина.

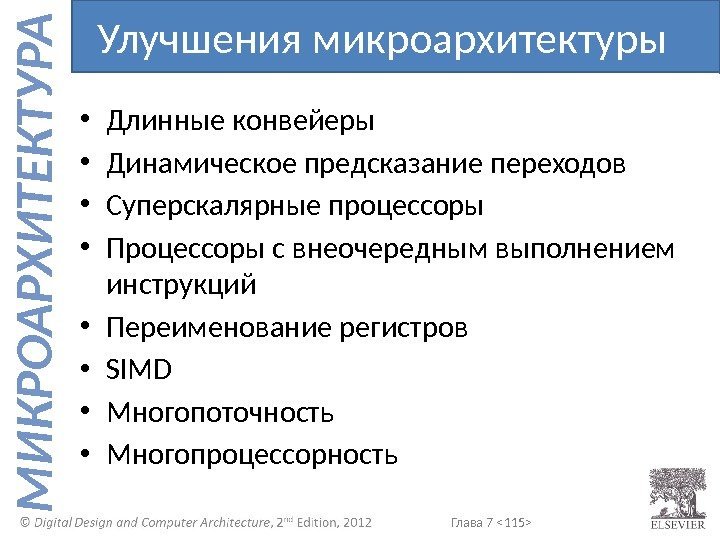

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АГлава 7 : : Темы • Введение • Анализ производительности • Однотактный процессор • Многотактный процессор • Конвейерный процессор • Исключения • Улучшение микроархитектуры

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АГлава 7 : : Темы • Введение • Анализ производительности • Однотактный процессор • Многотактный процессор • Конвейерный процессор • Исключения • Улучшение микроархитектуры

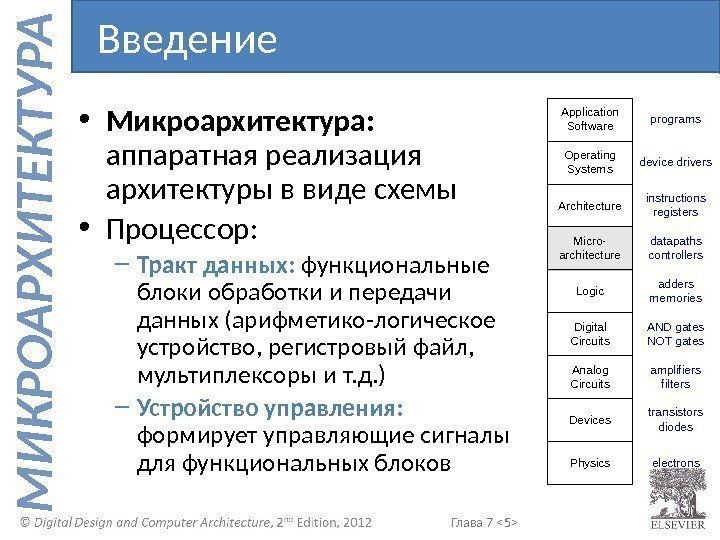

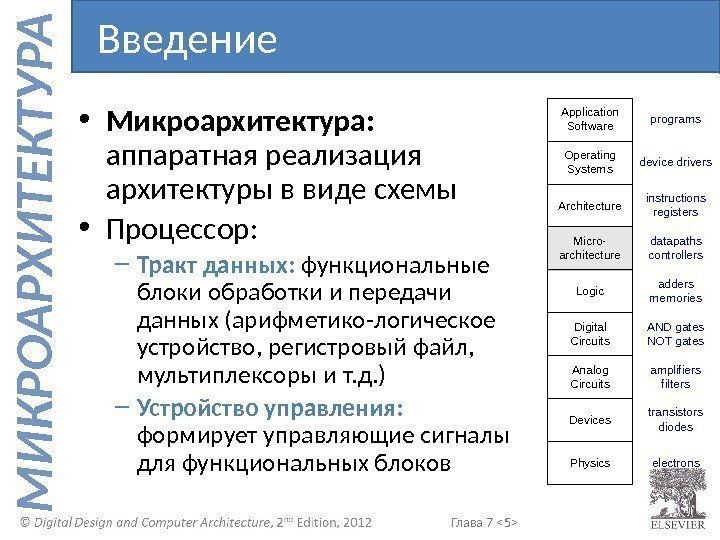

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Микроархитектура: аппаратная реализация архитектуры в виде схемы • Процессор: – Тракт данных: функциональные блоки обработки и передачи данных (арифметико-логическое устройство, регистровый файл, мультиплексоры и т. д. ) – Устройство управления: формирует управляющие сигналы для функциональных блоков. Введение Physics. Devices Analog Circuits Digital Circuits Logic. Micro- architecture. Architecture Operating Systems. Application Software electronstransistors diodesamplifiers filters. AND gates NOT gates adders memories datapaths controllersinstructions registersdevice drivers programs

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Микроархитектура: аппаратная реализация архитектуры в виде схемы • Процессор: – Тракт данных: функциональные блоки обработки и передачи данных (арифметико-логическое устройство, регистровый файл, мультиплексоры и т. д. ) – Устройство управления: формирует управляющие сигналы для функциональных блоков. Введение Physics. Devices Analog Circuits Digital Circuits Logic. Micro- architecture. Architecture Operating Systems. Application Software electronstransistors diodesamplifiers filters. AND gates NOT gates adders memories datapaths controllersinstructions registersdevice drivers programs

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Несколько аппаратных реализаций одной и той же архитектуры: – Однотактная реализация: каждая инструкция выполняется за один такт – Многотактная реализация: каждая инструкция разбивается на несколько шагов и выполняется за несколько тактов – Конвейерная реализация: каждая инструкция разбивается на несколько шагов и несколько инструкций выполняются одновременно. Микроархитектура

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Несколько аппаратных реализаций одной и той же архитектуры: – Однотактная реализация: каждая инструкция выполняется за один такт – Многотактная реализация: каждая инструкция разбивается на несколько шагов и выполняется за несколько тактов – Конвейерная реализация: каждая инструкция разбивается на несколько шагов и несколько инструкций выполняются одновременно. Микроархитектура

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Время выполнения программы Execution Time = (#instructions)(cycles/instruction)(seconds/cycle) Время выполнения = (#инструкции)(такты/инструкция)(секунды/такт) • Определения: – CPI: Количество тактов на выполнение инструкции (Cycles/instruction) – Период тактовой частоты: секунды/такт – IPC: Количество инструкций выполняемых за такт (instructions/cycle = IPC = 1 / CPI) • Необходимо удовлетворять следующие ограничения: – Стоимость – Площадь на кристалле – Энергопотребление – Производительность процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Время выполнения программы Execution Time = (#instructions)(cycles/instruction)(seconds/cycle) Время выполнения = (#инструкции)(такты/инструкция)(секунды/такт) • Определения: – CPI: Количество тактов на выполнение инструкции (Cycles/instruction) – Период тактовой частоты: секунды/такт – IPC: Количество инструкций выполняемых за такт (instructions/cycle = IPC = 1 / CPI) • Необходимо удовлетворять следующие ограничения: – Стоимость – Площадь на кристалле – Энергопотребление – Производительность процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Будем рассматривать подмножество инструкций MIPS: – Инструкции R-типа: and , or , add , sub , slt – Инструкции работы с памятью: lw , sw – Инструкции переходов: beq, j. MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Будем рассматривать подмножество инструкций MIPS: – Инструкции R-типа: and , or , add , sub , slt – Инструкции работы с памятью: lw , sw – Инструкции переходов: beq, j. MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Определяется: – Содержимым счетчика команд (PC) – Содержимым 32 -х регистров общего назначения – Содержимым памяти. Архитектурное состояние

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Определяется: – Содержимым счетчика команд (PC) – Содержимым 32 -х регистров общего назначения – Содержимым памяти. Архитектурное состояние

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЭлементы, хранящие состояние MIPS CLK A RD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File A RD Data Memory WD WEPCPC’ CLK

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЭлементы, хранящие состояние MIPS CLK A RD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File A RD Data Memory WD WEPCPC’ CLK

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Тракт данных • Устройство управления. Однотактный MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Тракт данных • Устройство управления. Однотактный MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 1: Выборка (считывание) инструкции lw из памяти. Однотактный тракт данных: выборка lw CLK A RD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File A RD Data Memory WD WE PC PC’ Instr CLK

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 1: Выборка (считывание) инструкции lw из памяти. Однотактный тракт данных: выборка lw CLK A RD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File A RD Data Memory WD WE PC PC’ Instr CLK

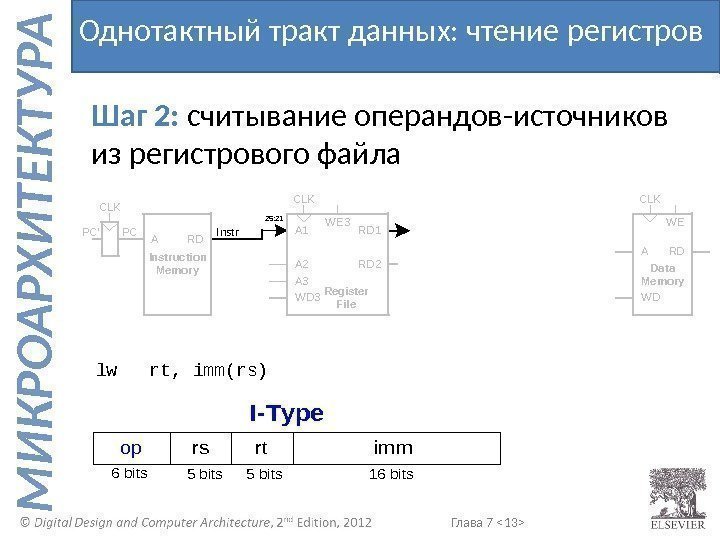

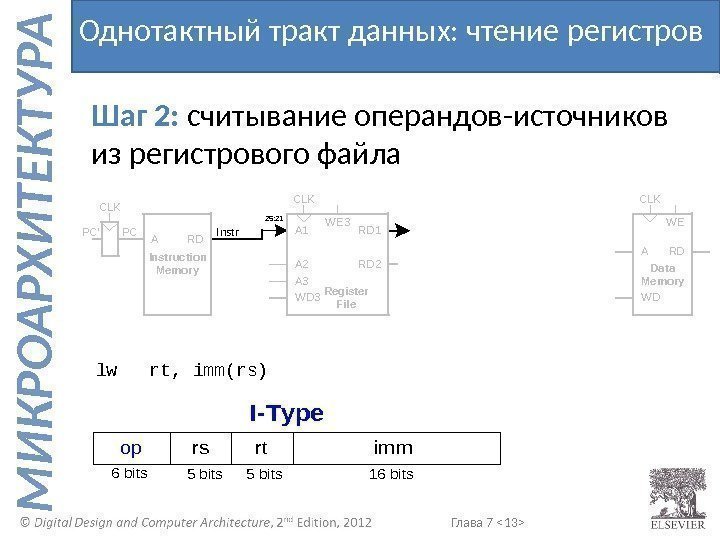

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 2: считывание операндов-источников из регистрового файла. Однотактный тракт данных: чтение регистров lw rt, imm(rs) Instr CLK ARD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File ARD Data Memory WD W E PCPC’ 25: 21 CLK oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 2: считывание операндов-источников из регистрового файла. Однотактный тракт данных: чтение регистров lw rt, imm(rs) Instr CLK ARD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Register File ARD Data Memory WD W E PCPC’ 25: 21 CLK oprsrtimm 6 bits 5 bits 16 bits I-Type

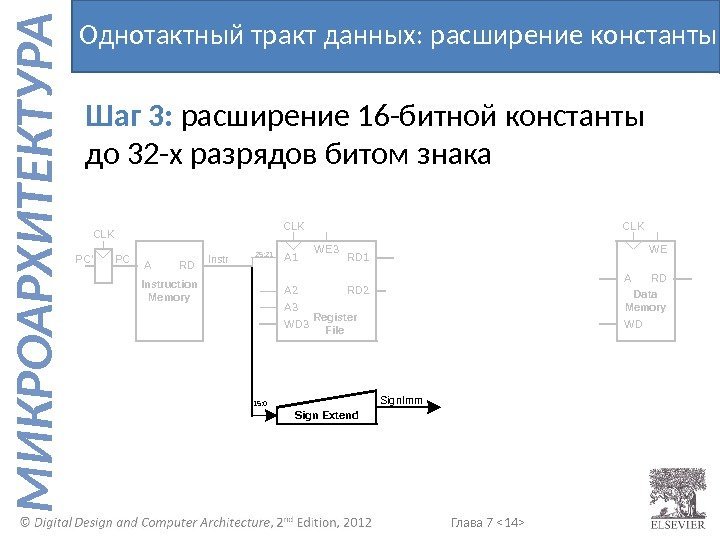

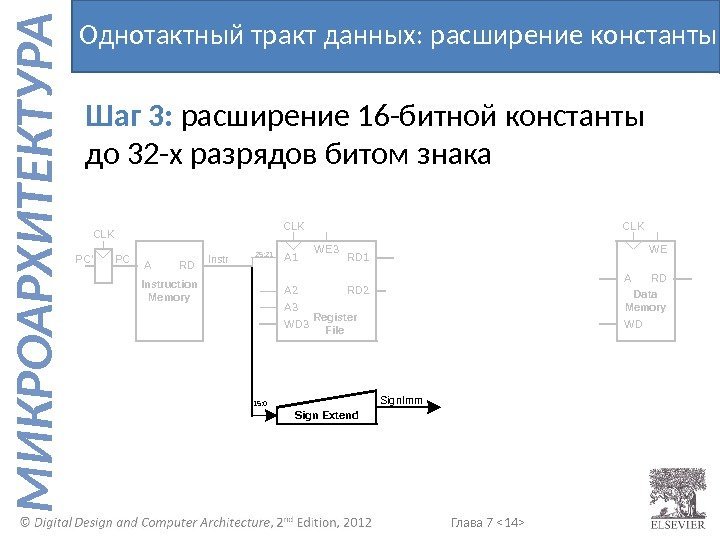

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 3: расширение 16 -битной константы до 32 -х разрядов битом знака. Однотактный тракт данных: расширение константы Sign. Imm CLK ARD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD W E PCPC’Instr 25: 21 15: 0 CLK

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 3: расширение 16 -битной константы до 32 -х разрядов битом знака. Однотактный тракт данных: расширение константы Sign. Imm CLK ARD Instruction Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD W E PCPC’Instr 25: 21 15: 0 CLK

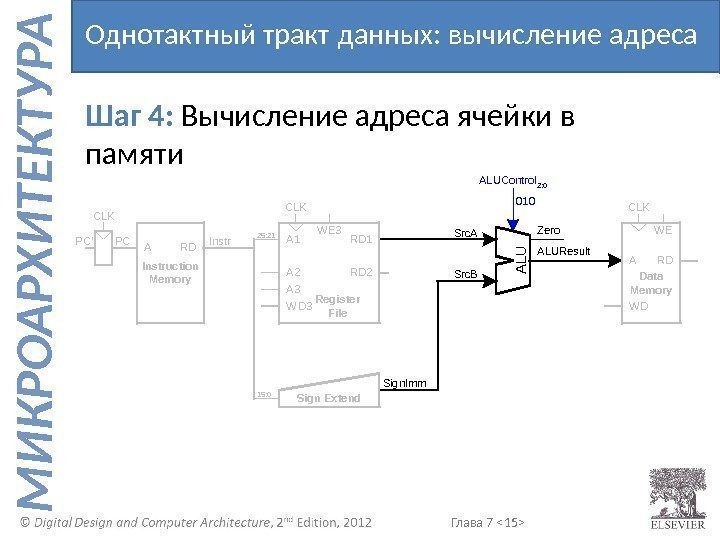

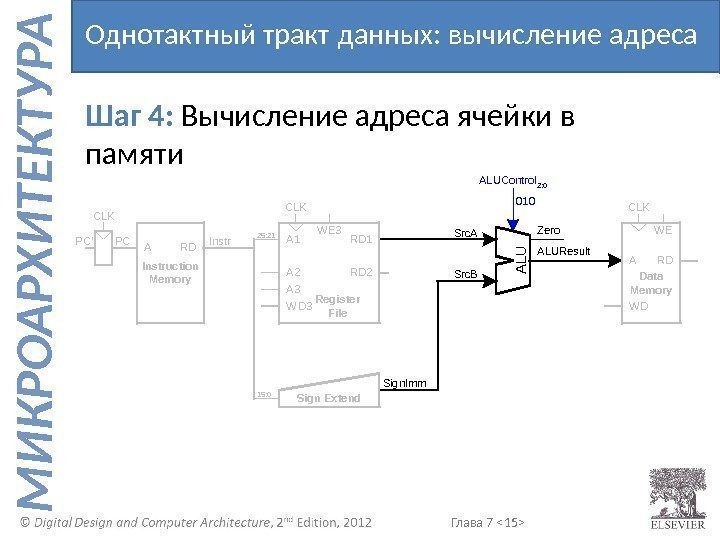

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 4: Вычисление адреса ячейки в памяти. Однотактный тракт данных: вычисление адреса Sign. Imm. CLK A RD Instruction Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File A RD Data Memory WD WE PCPC’ Instr 25: 21 15: 0 Src. B ALUResult. Src. A Zero CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 4: Вычисление адреса ячейки в памяти. Однотактный тракт данных: вычисление адреса Sign. Imm. CLK A RD Instruction Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File A RD Data Memory WD WE PCPC’ Instr 25: 21 15: 0 Src. B ALUResult. Src. A Zero CLKALUControl 2: 0 ALU

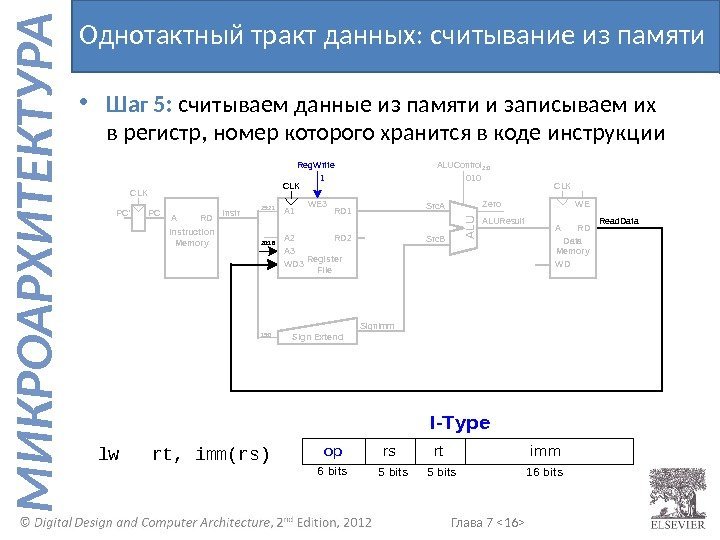

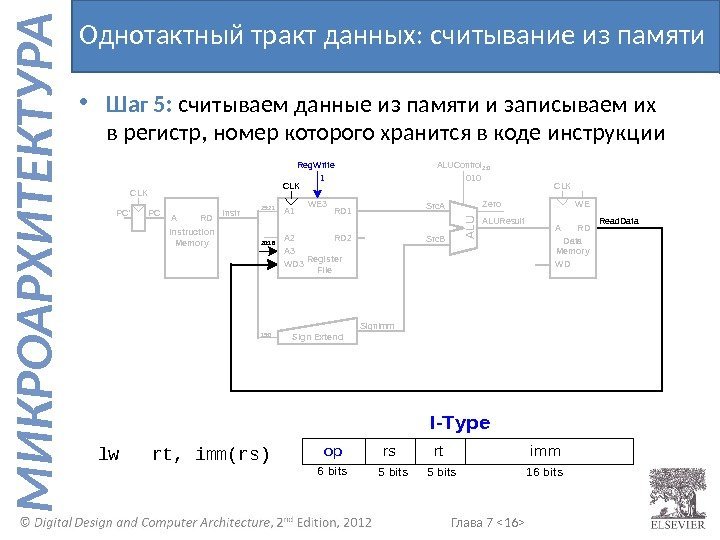

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Шаг 5: считываем данные из памяти и записываем их в регистр, номер которого хранится в коде инструкции. Однотактный тракт данных: считывание из памяти lw rt, imm(rs) A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 Sign. Imm CLK ARD Instruction Memory CLK Sign Extend Register File ARD Data Memory WD W EPCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult. Read. Data Src. A Reg. W rite Zero CLK ALUControl 2: 0 ALU 0101 oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Шаг 5: считываем данные из памяти и записываем их в регистр, номер которого хранится в коде инструкции. Однотактный тракт данных: считывание из памяти lw rt, imm(rs) A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 Sign. Imm CLK ARD Instruction Memory CLK Sign Extend Register File ARD Data Memory WD W EPCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult. Read. Data Src. A Reg. W rite Zero CLK ALUControl 2: 0 ALU 0101 oprsrtimm 6 bits 5 bits 16 bits I-Type

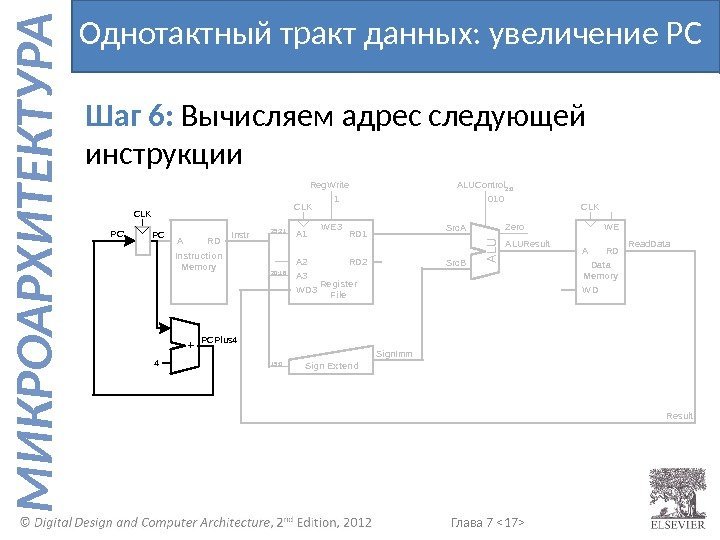

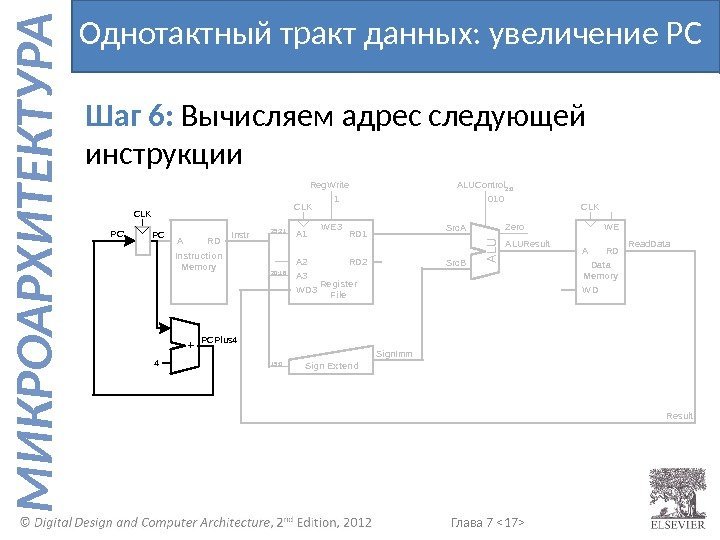

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 6: Вычисляем адрес следующей инструкции. Однотактный тракт данных: увеличение PC Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD WEPCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult. Read. Data Src. A PCPlus 4 Result Reg. W rite Zero CLK ALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 6: Вычисляем адрес следующей инструкции. Однотактный тракт данных: увеличение PC Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD WEPCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult. Read. Data Src. A PCPlus 4 Result Reg. W rite Zero CLK ALUControl 2: 0 ALU

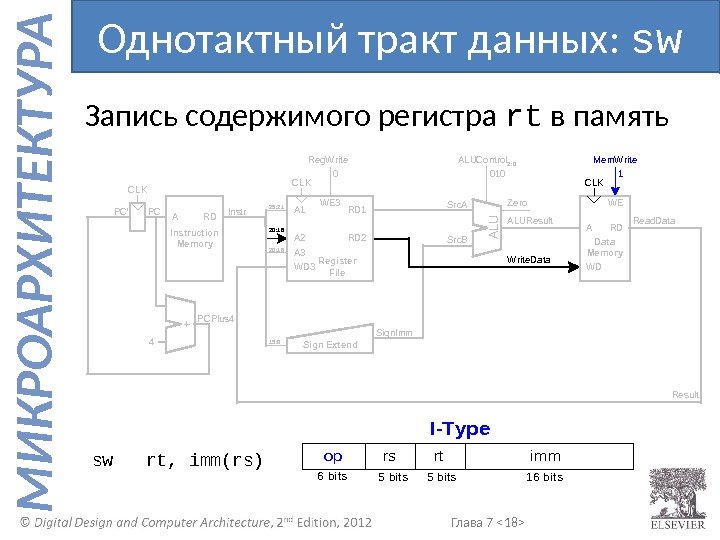

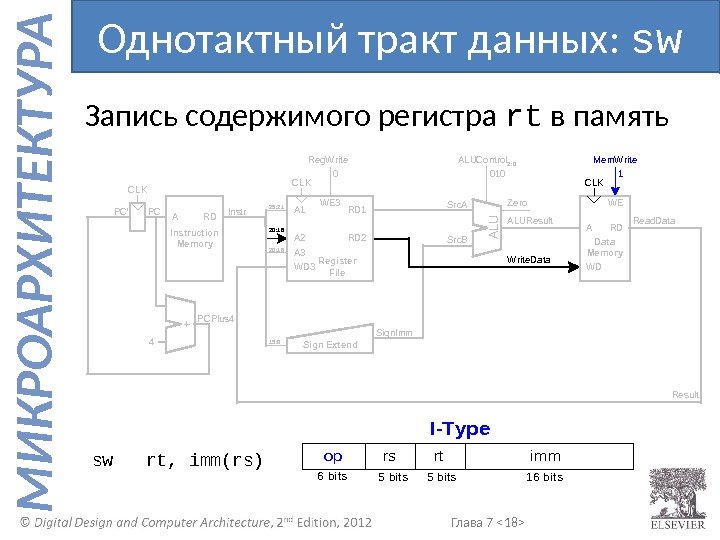

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЗапись содержимого регистра rt в память. Однотактный тракт данных : sw sw rt, imm(rs) Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD W EPCPC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 ALUResult. Read. Data Write. Data Src. A PCPlus 4 Result Mem. Write. Reg. W rite Zero CLK ALUControl 2: 0 ALU 10100 oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЗапись содержимого регистра rt в память. Однотактный тракт данных : sw sw rt, imm(rs) Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File ARD Data Memory WD W EPCPC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 ALUResult. Read. Data Write. Data Src. A PCPlus 4 Result Mem. Write. Reg. W rite Zero CLK ALUControl 2: 0 ALU 10100 oprsrtimm 6 bits 5 bits 16 bits I-Type

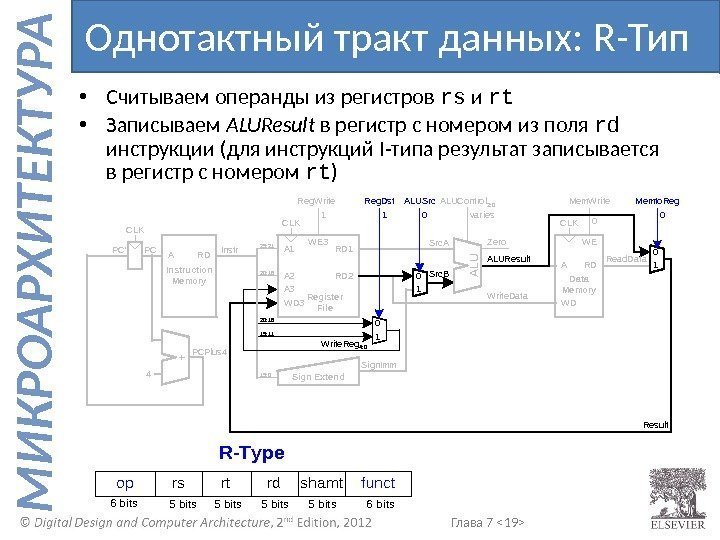

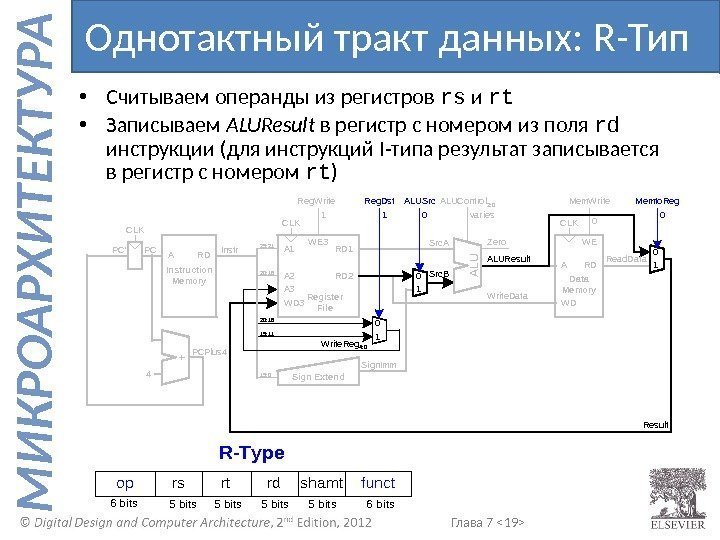

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Считываем операнды из регистров rs и rt • Записываем ALUResult в регистр с номером из поля rd инструкции (для инструкций I-типа результат записывается в регистр с номером rt )Однотактный тракт данных: R-Тип Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 ARD Data Memory W D W E 0 1 PCPC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 ALUResult. Read. Data W rite. Data Src. A PCPlus 4 W rite. Reg 4: 0 Result Reg. Dst. Mem. W rite. Memto. Reg. ALUSrc. Reg. W rite Zero CLK ALUControl 2: 0 ALU 0 varies 1001 oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Считываем операнды из регистров rs и rt • Записываем ALUResult в регистр с номером из поля rd инструкции (для инструкций I-типа результат записывается в регистр с номером rt )Однотактный тракт данных: R-Тип Sign. Imm CLK ARD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 ARD Data Memory W D W E 0 1 PCPC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 ALUResult. Read. Data W rite. Data Src. A PCPlus 4 W rite. Reg 4: 0 Result Reg. Dst. Mem. W rite. Memto. Reg. ALUSrc. Reg. W rite Zero CLK ALUControl 2: 0 ALU 0 varies 1001 oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

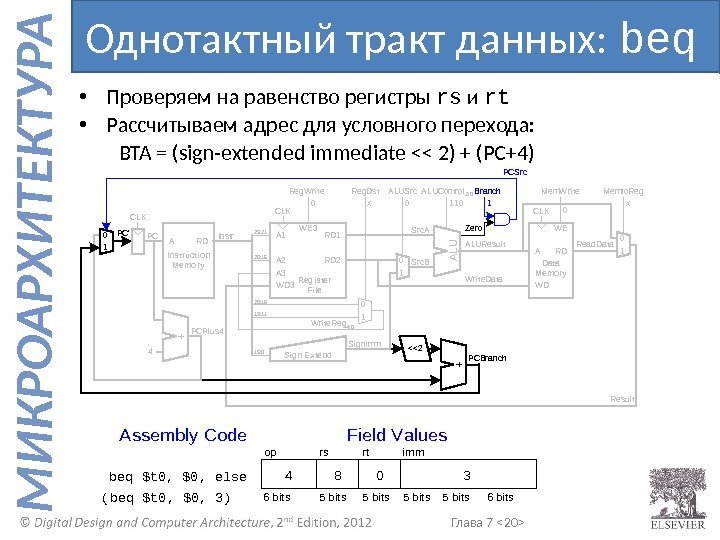

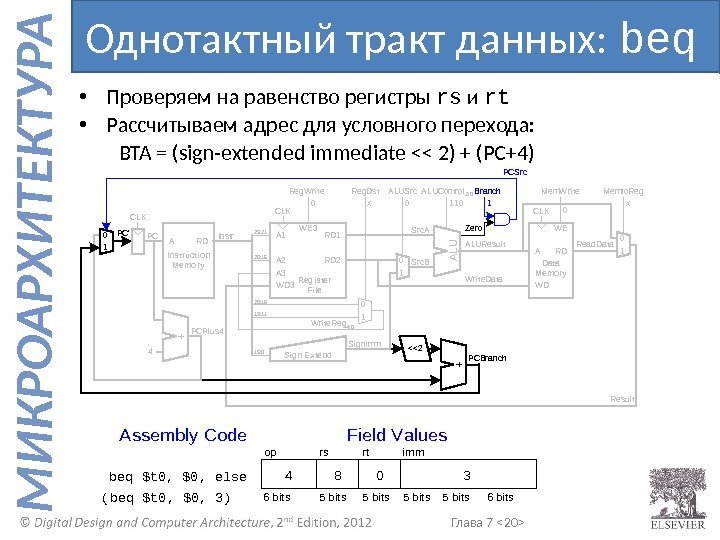

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Проверяем на равенство регистры rs и rt • Рассчитываем адрес для условного перехода: BTA = (sign-extended immediate << 2) + (PC+4)Однотактный тракт данных: beq Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC' Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result. Reg. Dst Branch Mem. Write Memto. Reg. ALUSrc. Reg. W rite Zero PCSrc CLKALUControl 2: 0 ALU 01100 x 0 x 1 beq $t 0, $0, else Assembly Code. Field Values 4 8 0 3 oprsrtimm 6 bits 5 bits 6 bits(beq $t 0, $0, 3)

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Проверяем на равенство регистры rs и rt • Рассчитываем адрес для условного перехода: BTA = (sign-extended immediate << 2) + (PC+4)Однотактный тракт данных: beq Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC' Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result. Reg. Dst Branch Mem. Write Memto. Reg. ALUSrc. Reg. W rite Zero PCSrc CLKALUControl 2: 0 ALU 01100 x 0 x 1 beq $t 0, $0, else Assembly Code. Field Values 4 8 0 3 oprsrtimm 6 bits 5 bits 6 bits(beq $t 0, $0, 3)

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный процессор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный процессор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АУправление однотактным процессором Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc. Opcode 5 : 0 Control Unit ALUControl 2 : 0 Funct 5 : 0 Main Decoder ALUOp 1 : 0 ALU Decoder Reg. Write

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АУправление однотактным процессором Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc. Opcode 5 : 0 Control Unit ALUControl 2 : 0 Funct 5 : 0 Main Decoder ALUOp 1 : 0 ALU Decoder Reg. Write

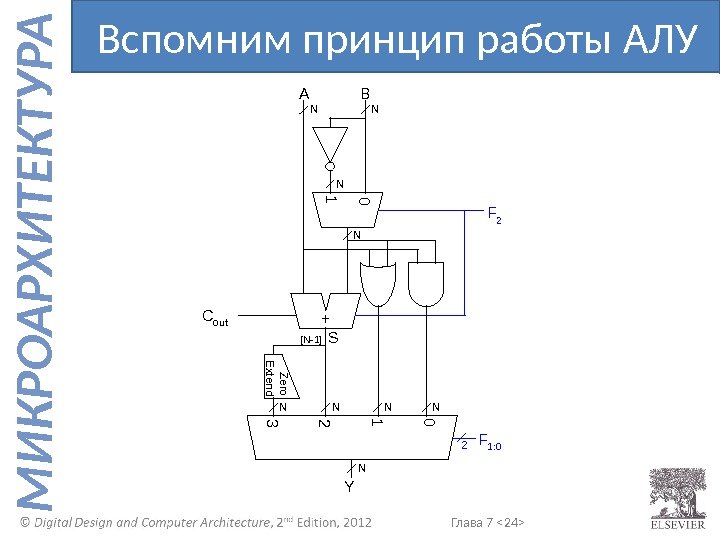

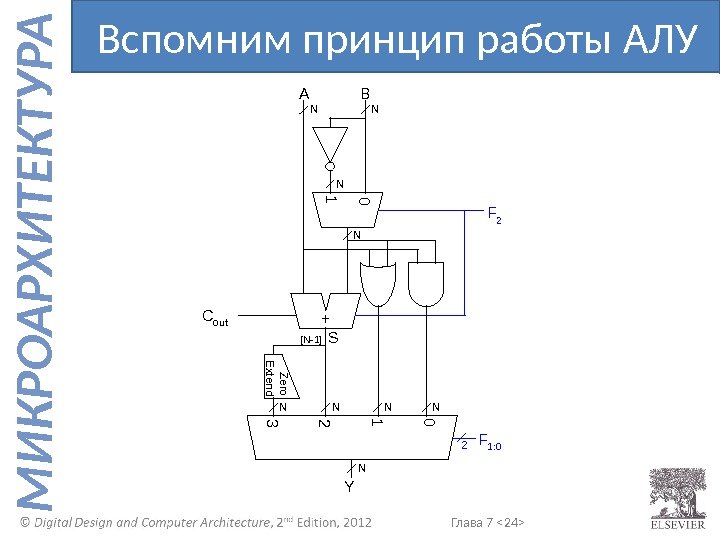

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АF 2: 0 Функция 000 A & B 001 A | B 010 A + B 011 Не исп. 100 A & ~B 101 A | ~B 110 A — B 111 SLTВспомним принцип работы АЛУ ALU NN N 3 AB Y

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АF 2: 0 Функция 000 A & B 001 A | B 010 A + B 011 Не исп. 100 A & ~B 101 A | ~B 110 A — B 111 SLTВспомним принцип работы АЛУ ALU NN N 3 AB Y

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АВспомним принцип работы АЛУ + 201 AB Cout Y 3 01 F 2 F 1: 0 [N-1]S NN N N NNNN N 2 Zero Extend

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АВспомним принцип работы АЛУ + 201 AB Cout Y 3 01 F 2 F 1: 0 [N-1]S NN N N NNNN N 2 Zero Extend

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АALUOp 1: 0 Действие 00 Сложение 01 Вычитание 10 Определяется полем Funct 11 Не используется ALUOp 1: 0 Funct ALUControl 2: 0 00 X 010 (Сложение) X 110 (Вычитание) 1 X 100000 ( add ) 010 (Сложение) 1 X 100010 ( sub ) 110 (Вычитание) 1 X 100100 ( and ) 000 (И) 1 X 100101 ( or ) 001 (ИЛИ) 1 X 101010 ( slt ) 111 (SLT)Управляющее устройство: Дешифратор АЛУ

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АALUOp 1: 0 Действие 00 Сложение 01 Вычитание 10 Определяется полем Funct 11 Не используется ALUOp 1: 0 Funct ALUControl 2: 0 00 X 010 (Сложение) X 110 (Вычитание) 1 X 100000 ( add ) 010 (Сложение) 1 X 100010 ( sub ) 110 (Вычитание) 1 X 100100 ( and ) 000 (И) 1 X 100101 ( or ) 001 (ИЛИ) 1 X 101010 ( slt ) 111 (SLT)Управляющее устройство: Дешифратор АЛУ

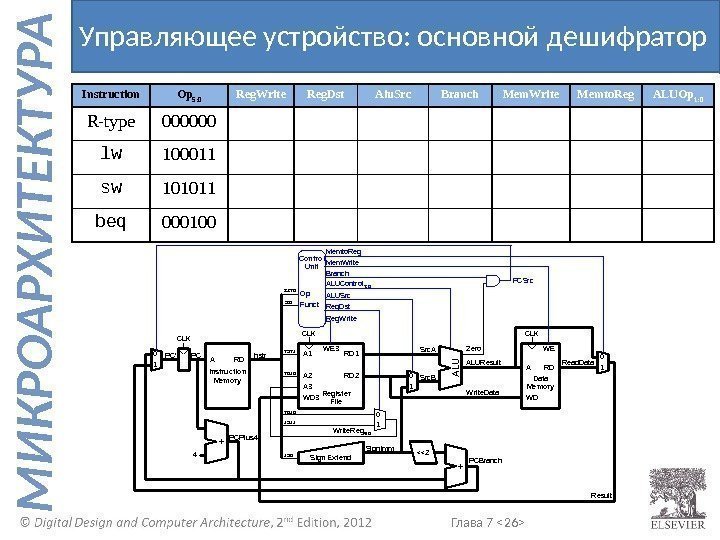

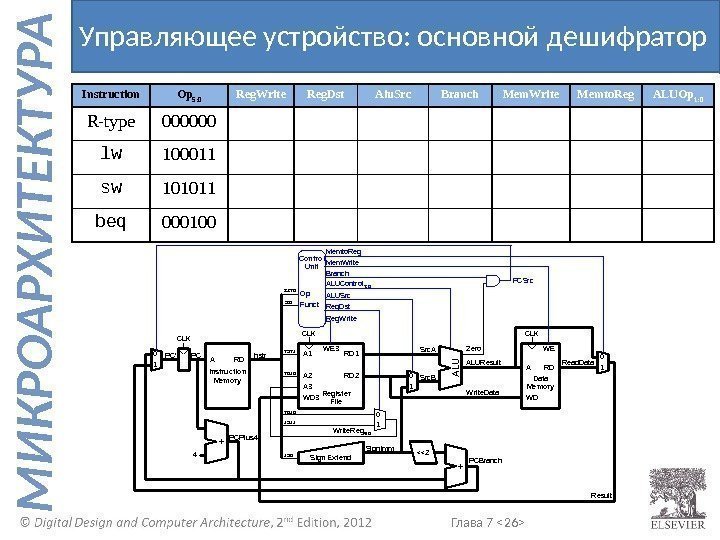

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Reg ALUOp 1: 0 R-type 000000 lw 100011 sw 101011 beq 000100 Управляющее устройство: основной дешифратор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Reg ALUOp 1: 0 R-type 000000 lw 100011 sw 101011 beq 000100 Управляющее устройство: основной дешифратор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstructio n Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Reg ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 0 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 Управляющее устройство: основной дешифратор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstructio n Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Reg ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 0 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 Управляющее устройство: основной дешифратор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

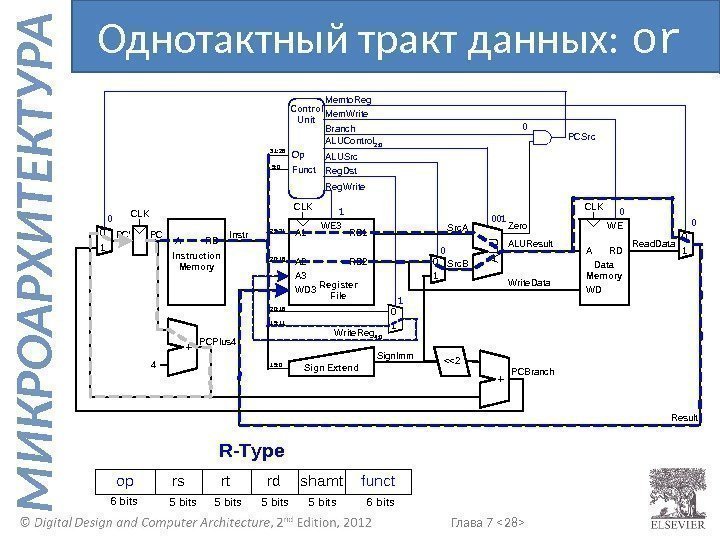

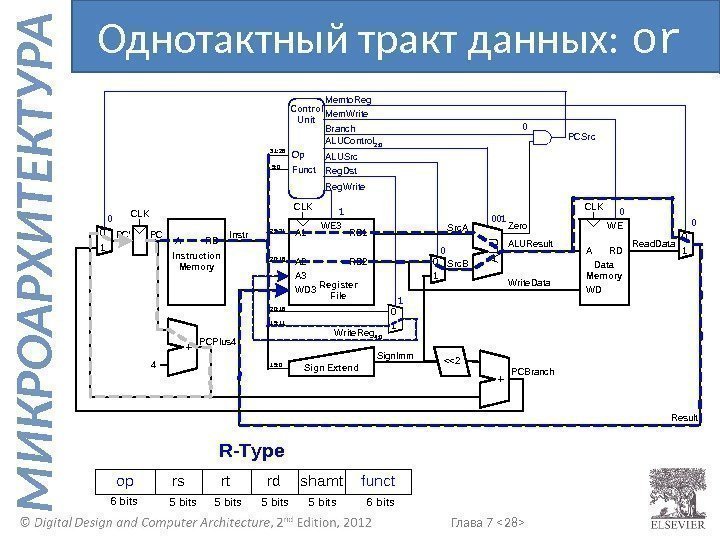

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный тракт данных: or Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD WE 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. Write. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 001 0 0 1 0 oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный тракт данных: or Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD WE 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. Write. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 001 0 0 1 0 oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

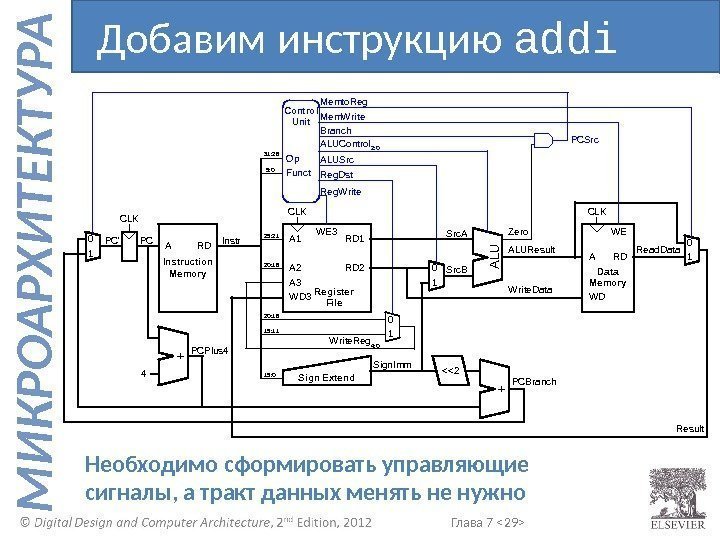

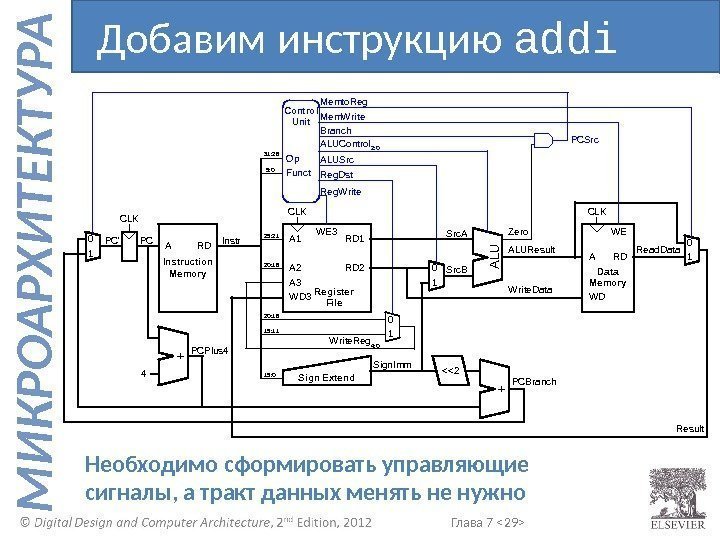

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АНеобходимо сформировать управляющие сигналы, а тракт данных менять не нужно Добавим инструкцию addi Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D WE 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АНеобходимо сформировать управляющие сигналы, а тракт данных менять не нужно Добавим инструкцию addi Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D WE 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

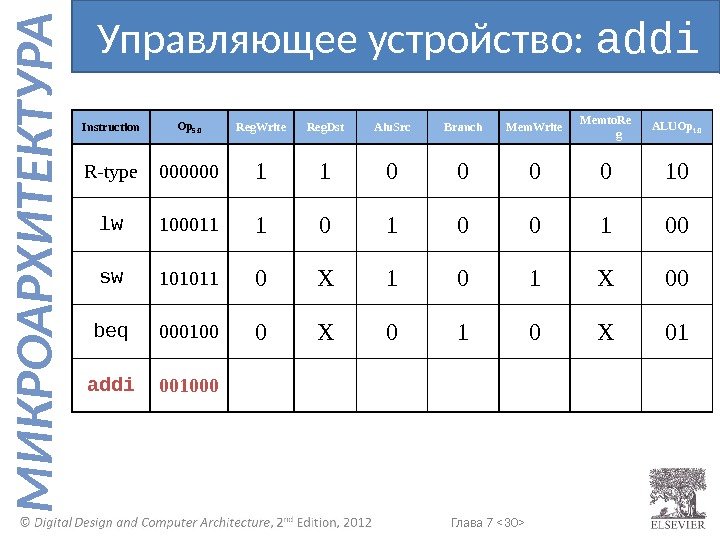

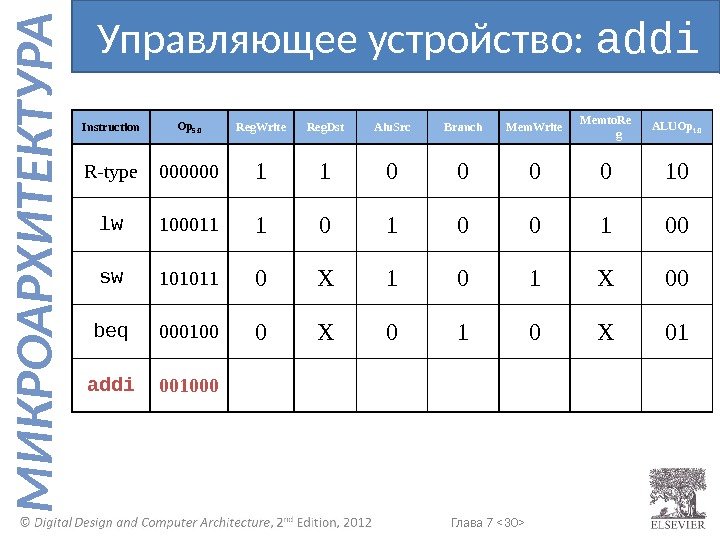

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 1 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 addi 001000 Управляющее устройство: addi

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 1 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 addi 001000 Управляющее устройство: addi

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 1 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 addi 001000 1 0 0 0 00 Управляющее устройство: addi

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 R-type 000000 1 1 0 0 10 lw 100011 1 0 0 1 00 sw 101011 0 X 1 0 1 X 00 beq 000100 0 X 0 1 0 X 01 addi 001000 1 0 0 0 00 Управляющее устройство: addi

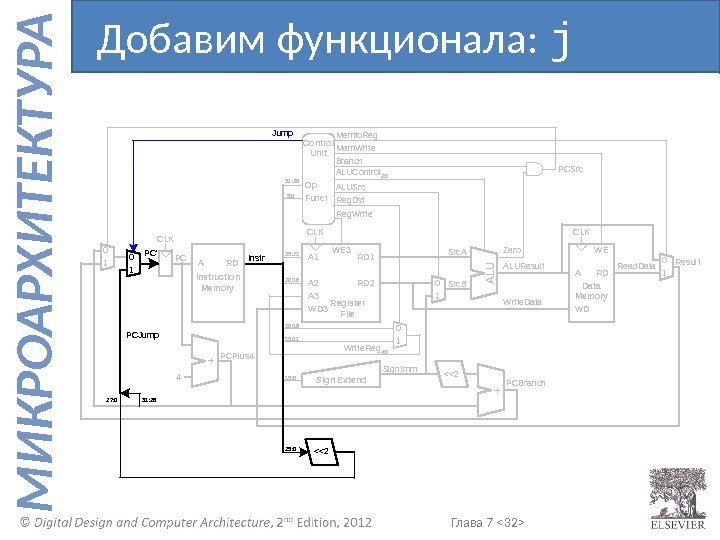

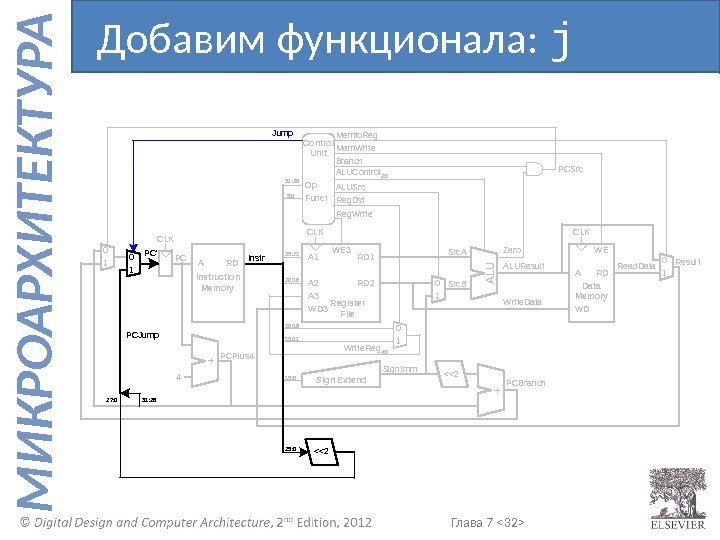

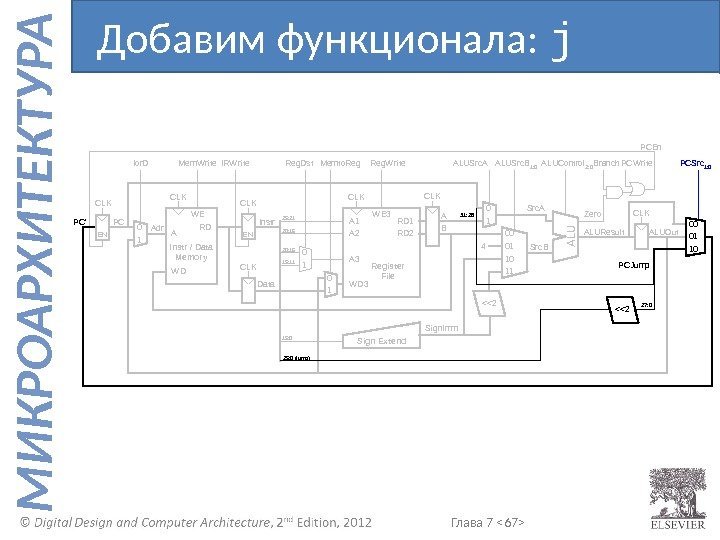

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: j Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 0 1 25: 0 <<227: 0 31: 28 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: j Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. W rite. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 0 1 25: 0 <<227: 0 31: 28 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 Jump R-type 000000 1 1 0 0 10 0 lw 100011 1 0 0 1 00 0 sw 101011 0 X 1 0 1 X 00 0 beq 000100 0 X 0 1 0 X 01 0 j 000100 Управляющее устройство: j

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 Jump R-type 000000 1 1 0 0 10 0 lw 100011 1 0 0 1 00 0 sw 101011 0 X 1 0 1 X 00 0 beq 000100 0 X 0 1 0 X 01 0 j 000100 Управляющее устройство: j

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 Jump R-type 000000 1 1 0 0 10 0 lw 100011 1 0 0 1 00 0 sw 101011 0 X 1 0 1 X 00 0 beq 000100 0 X 0 1 0 X 01 0 j 000100 0 X X X 0 X XX 1 Управляющее устройство: j

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АInstruction Op 5: 0 Reg. Write Reg. Dst Alu. Src Branch Mem. Write Memto. Re g ALUOp 1: 0 Jump R-type 000000 1 1 0 0 10 0 lw 100011 1 0 0 1 00 0 sw 101011 0 X 1 0 1 X 00 0 beq 000100 0 X 0 1 0 X 01 0 j 000100 0 X X X 0 X XX 1 Управляющее устройство: j

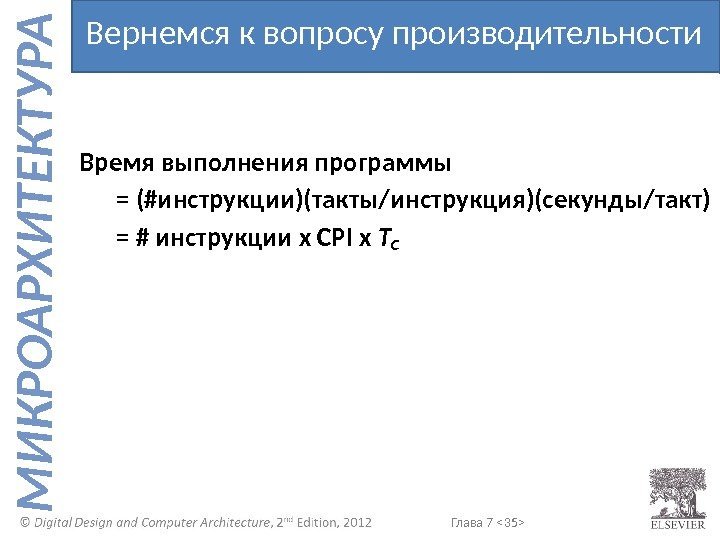

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АВремя выполнения программы = (#инструкции)(такты/инструкция)(секунды/такт) = # инструкции x CPI x T CВернемся к вопросу производительности

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АВремя выполнения программы = (#инструкции)(такты/инструкция)(секунды/такт) = # инструкции x CPI x T CВернемся к вопросу производительности

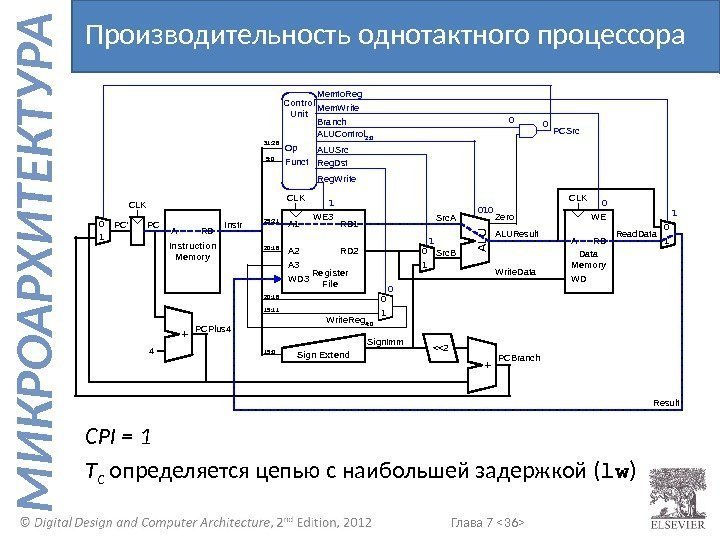

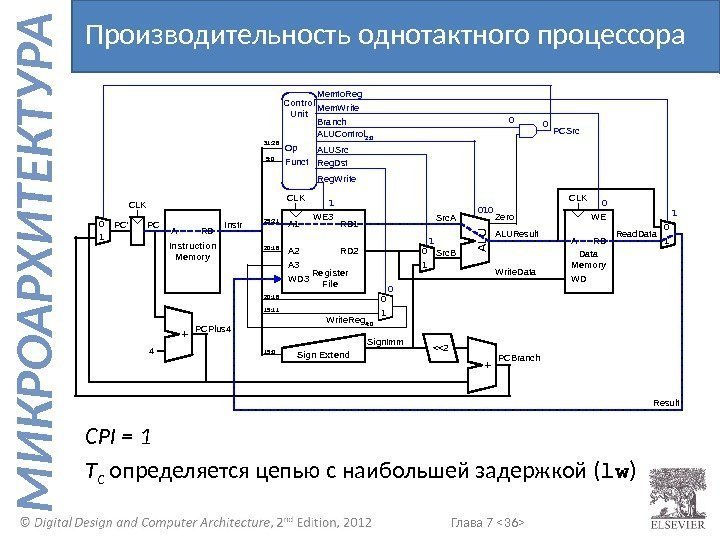

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT C определяется цепью с наибольшей задержкой ( lw ) Производительность однотактного процессора CPI = 1 Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT C определяется цепью с наибольшей задержкой ( lw ) Производительность однотактного процессора CPI = 1 Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU

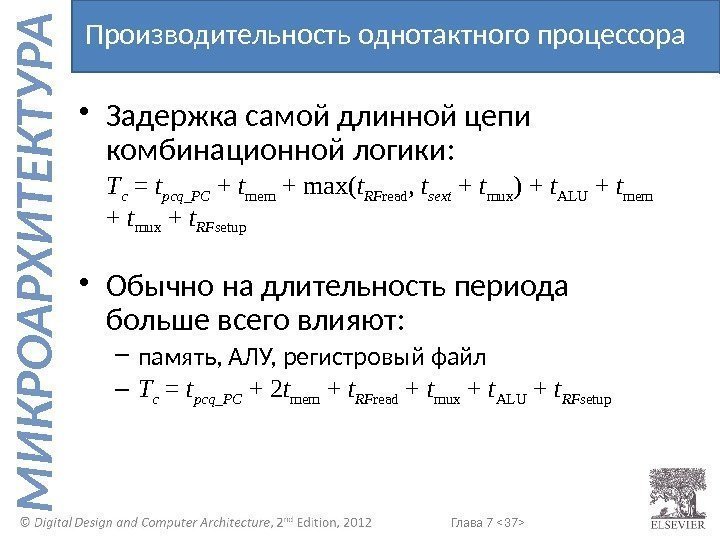

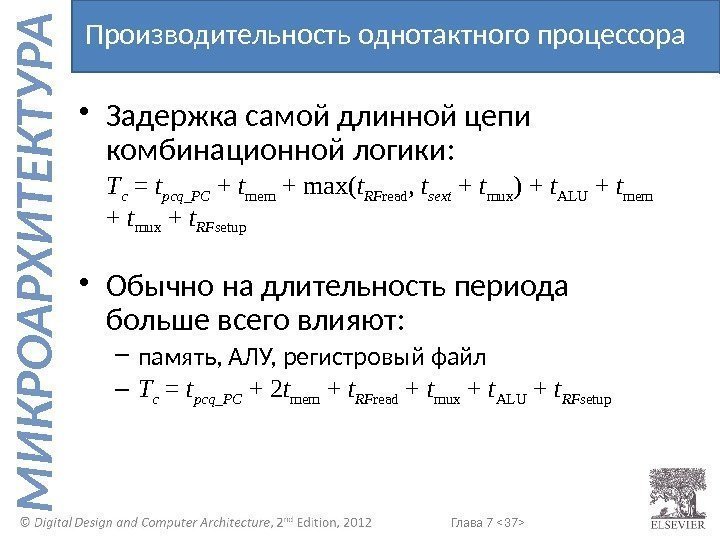

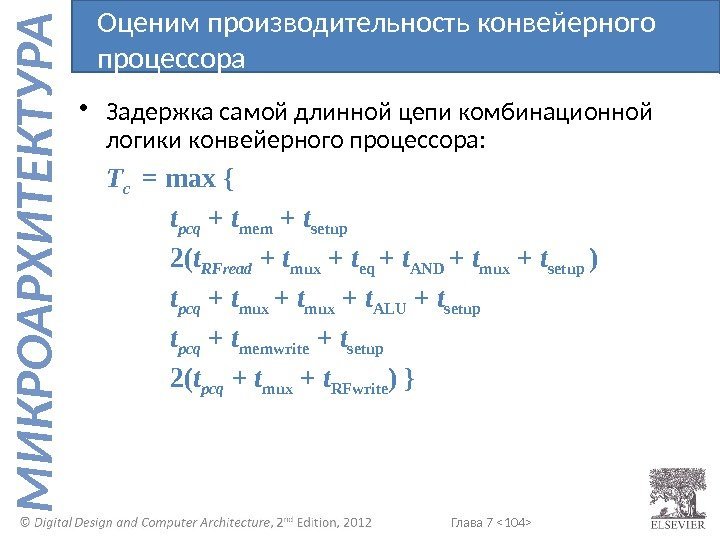

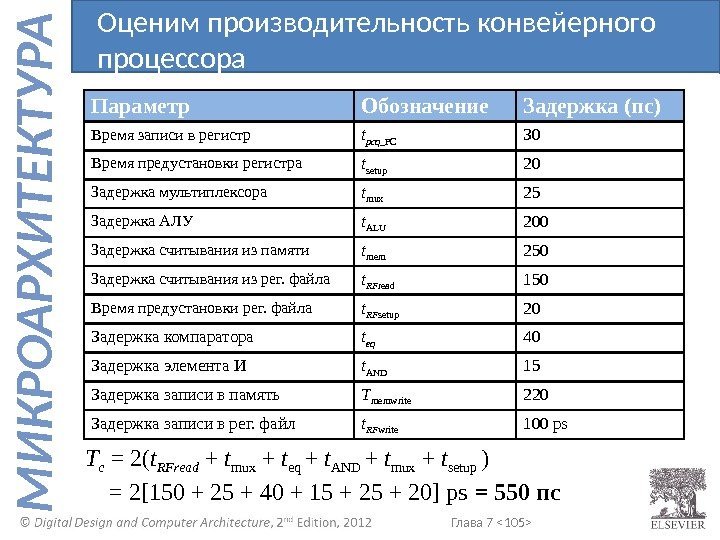

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Задержка самой длинной цепи комбинационной логики : T c = t pcq_PC + t mem + max( t RF read , t sext + t mux ) + t ALU + t mem + t mux + t RF setup • Обычно на длительность периода больше всего влияют : – память, АЛУ, регистровый файл – T c = t pcq_PC + 2 t mem + t RF read + t mux + t ALU + t RF setup. Производительность однотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Задержка самой длинной цепи комбинационной логики : T c = t pcq_PC + t mem + max( t RF read , t sext + t mux ) + t ALU + t mem + t mux + t RF setup • Обычно на длительность периода больше всего влияют : – память, АЛУ, регистровый файл – T c = t pcq_PC + 2 t mem + t RF read + t mux + t ALU + t RF setup. Производительность однотактного процессора

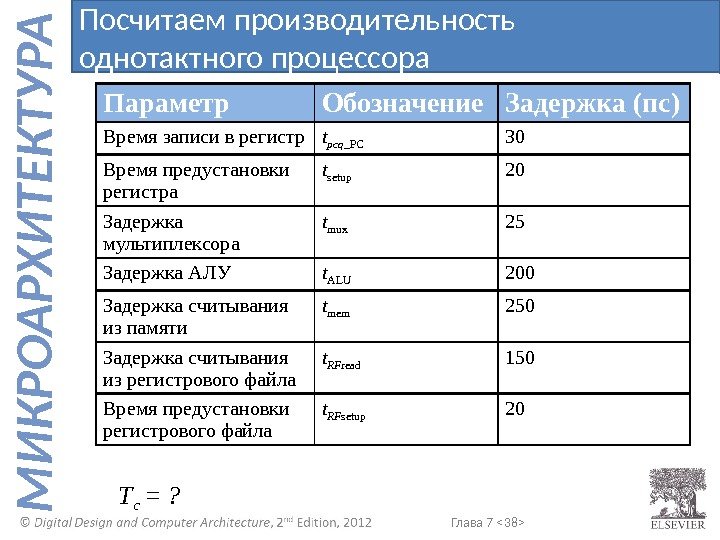

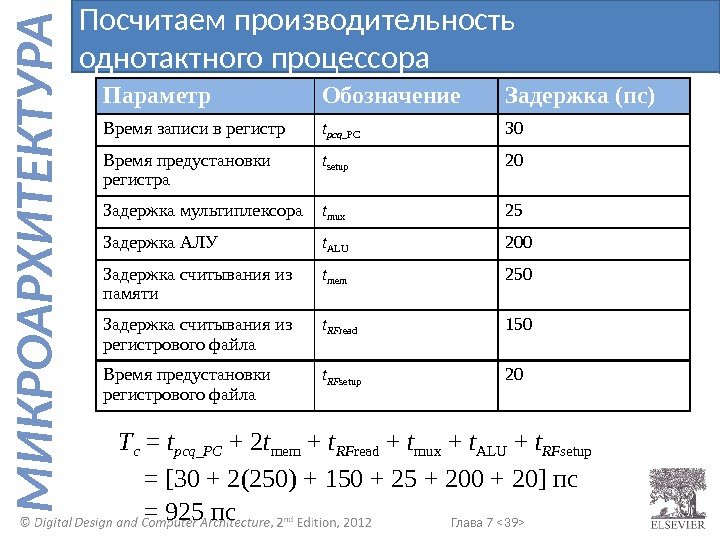

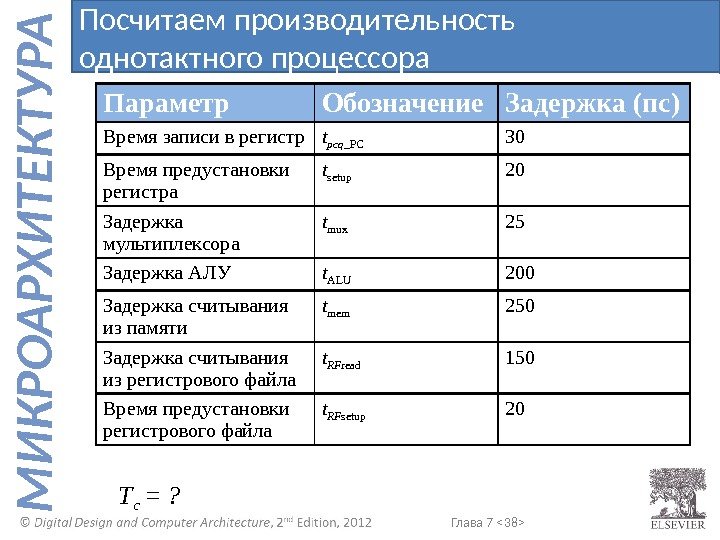

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПараметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup 20 T c = ? Посчитаем производительность однотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПараметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup 20 T c = ? Посчитаем производительность однотактного процессора

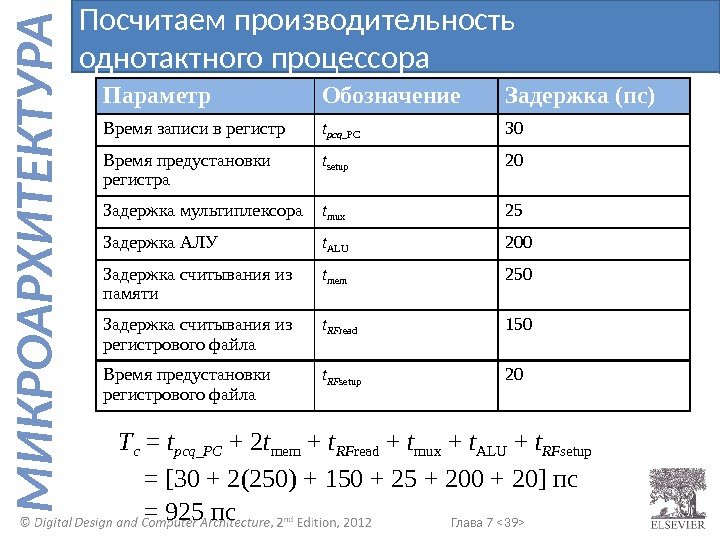

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = t pcq_PC + 2 t mem + t RF read + t mux + t ALU + t RF setup = [30 + 2(250) + 150 + 25 + 200 + 20] пс = 925 пс. Посчитаем производительность однотактного процессора Параметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = t pcq_PC + 2 t mem + t RF read + t mux + t ALU + t RF setup = [30 + 2(250) + 150 + 25 + 200 + 20] пс = 925 пс. Посчитаем производительность однотактного процессора Параметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup

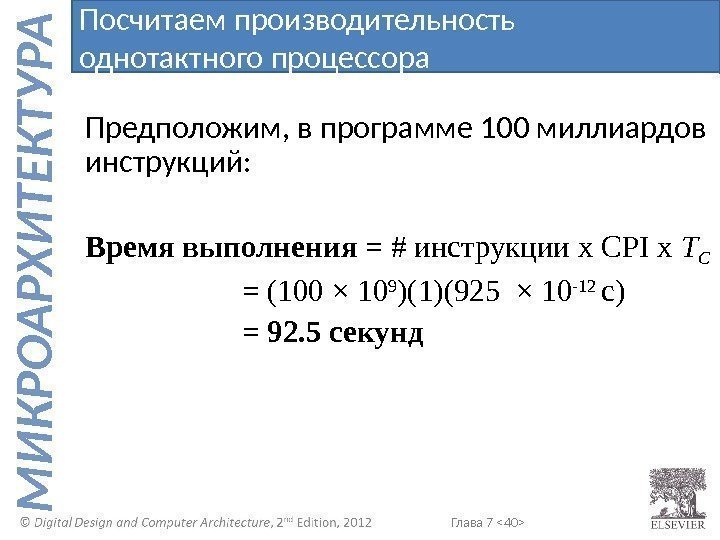

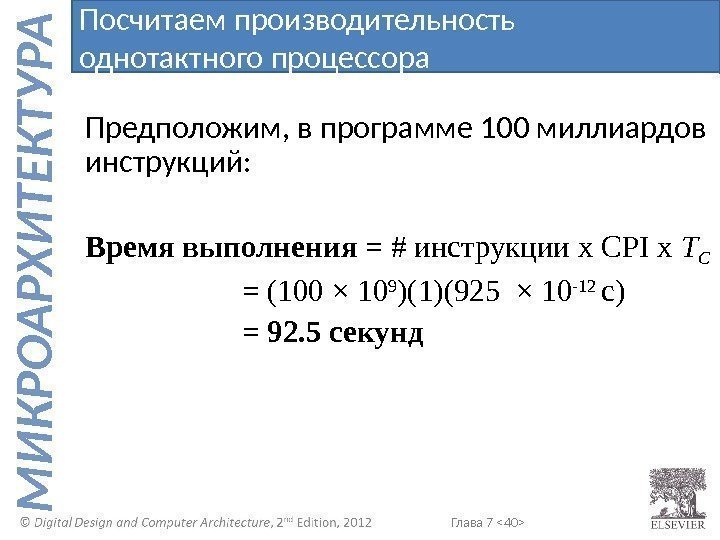

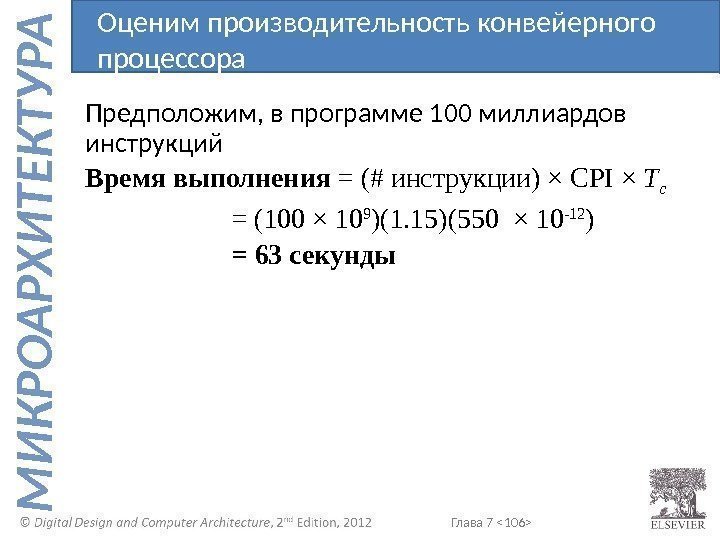

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПредположим, в программе 100 миллиардов инструкций: Время выполнения = # инструкции x CPI x T C = (100 × 10 9 )(1)(925 × 10 -12 с) = 92. 5 секунд. Посчитаем производительность однотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПредположим, в программе 100 миллиардов инструкций: Время выполнения = # инструкции x CPI x T C = (100 × 10 9 )(1)(925 × 10 -12 с) = 92. 5 секунд. Посчитаем производительность однотактного процессора

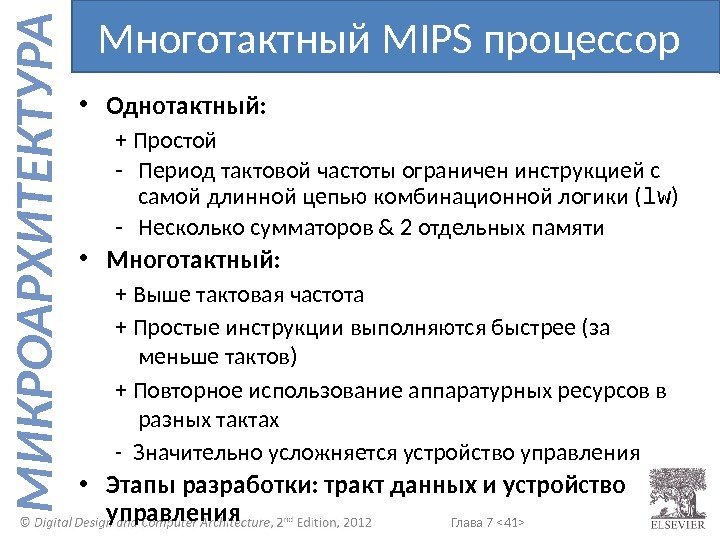

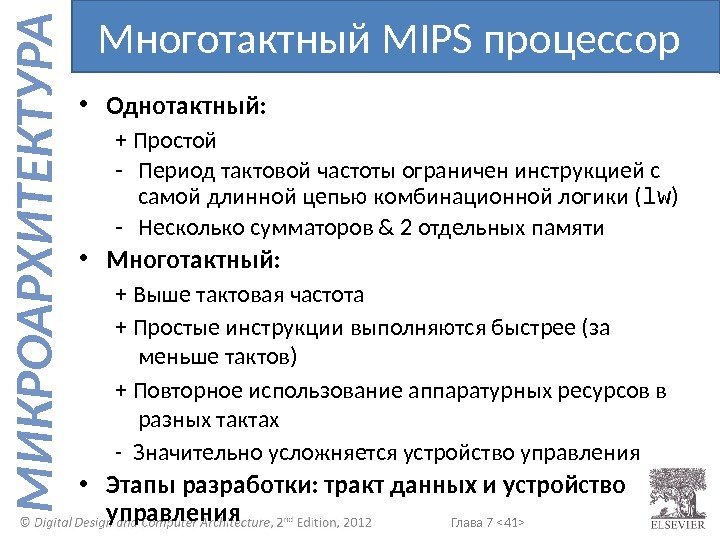

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Однотактный: + Простой — Период тактовой частоты ограничен инструкцией с самой длинной цепью комбинационной логики ( lw ) — Несколько сумматоров & 2 отдельных памяти • Многотактный: + Выше тактовая частота + Простые инструкции выполняются быстрее (за меньше тактов) + Повторное использование аппаратурных ресурсов в разных тактах — Значительно усложняется устройство управления • Этапы разработки: тракт данных и устройство управления. Многотактный MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Однотактный: + Простой — Период тактовой частоты ограничен инструкцией с самой длинной цепью комбинационной логики ( lw ) — Несколько сумматоров & 2 отдельных памяти • Многотактный: + Выше тактовая частота + Простые инструкции выполняются быстрее (за меньше тактов) + Повторное использование аппаратурных ресурсов в разных тактах — Значительно усложняется устройство управления • Этапы разработки: тракт данных и устройство управления. Многотактный MIPS процессор

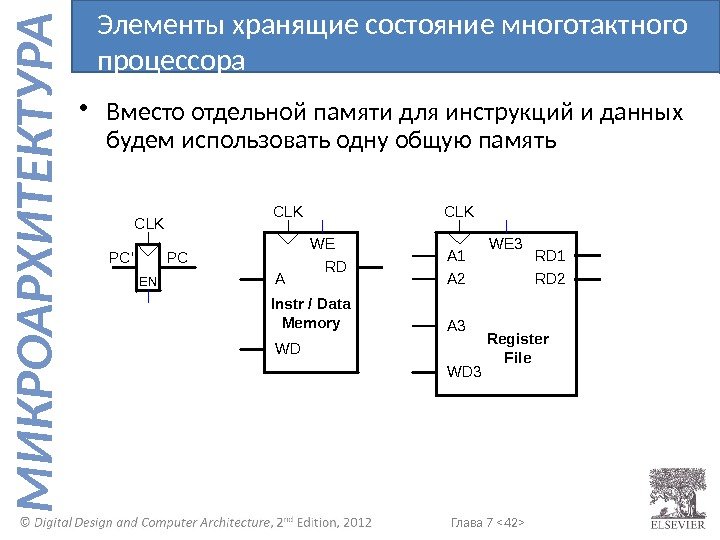

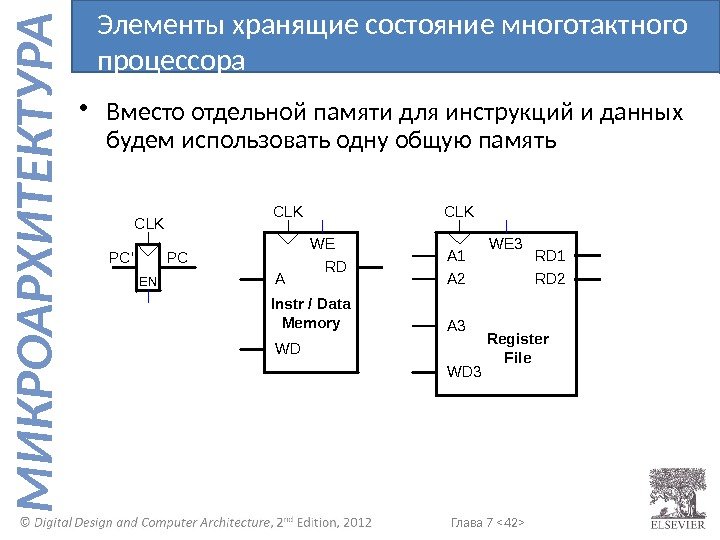

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Вместо отдельной памяти для инструкций и данных будем использовать одну общую память. Элементы хранящие состояние многотактного процессора CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’ W D WE CLK EN

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Вместо отдельной памяти для инструкций и данных будем использовать одну общую память. Элементы хранящие состояние многотактного процессора CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’ W D WE CLK EN

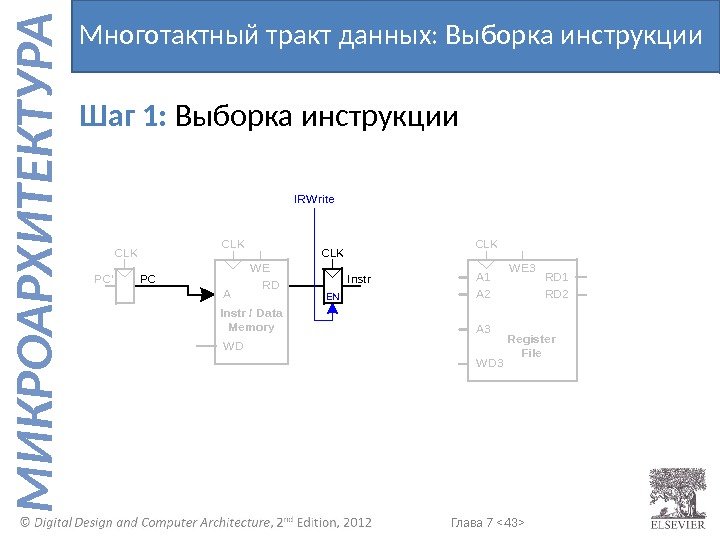

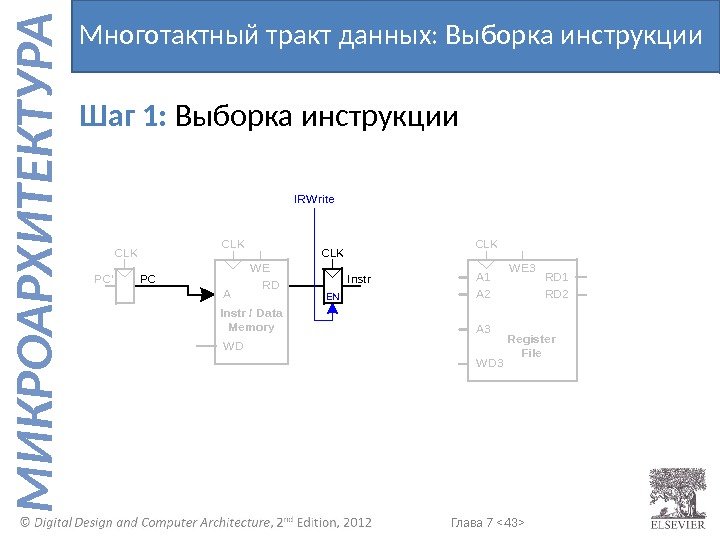

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 1: Выборка инструкции. Многотактный тракт данных: Выборка инструкции b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’Instr CLK W D WE CLK EN IRW rite

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АШаг 1: Выборка инструкции. Многотактный тракт данных: Выборка инструкции b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’Instr CLK W D WE CLK EN IRW rite

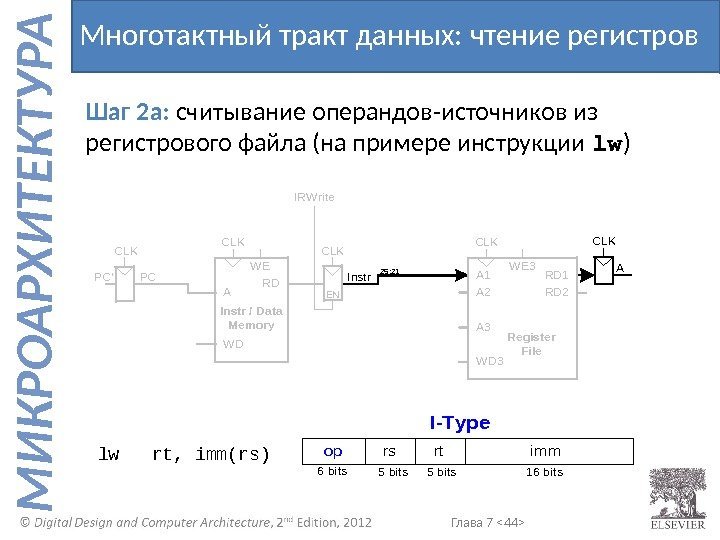

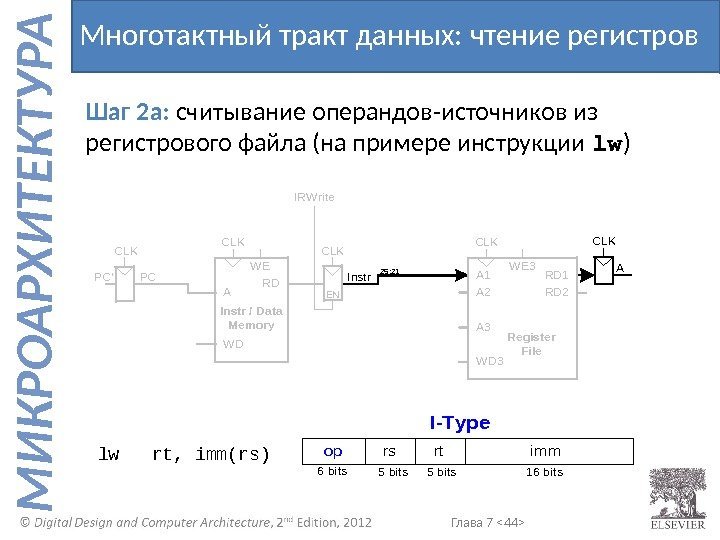

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: чтение регистров Шаг 2 a: считывание операндов-источников из регистрового файла (на примере инструкции lw ) lw rt, imm(rs) b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’Instr 25: 21 CLK W D WE CLKCLK A EN IRW rite oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: чтение регистров Шаг 2 a: считывание операндов-источников из регистрового файла (на примере инструкции lw ) lw rt, imm(rs) b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Register File PCPC’Instr 25: 21 CLK W D WE CLKCLK A EN IRW rite oprsrtimm 6 bits 5 bits 16 bits I-Type

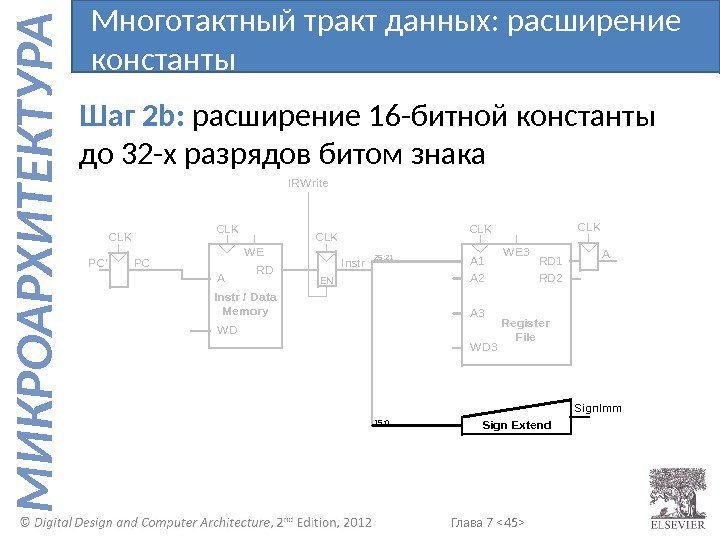

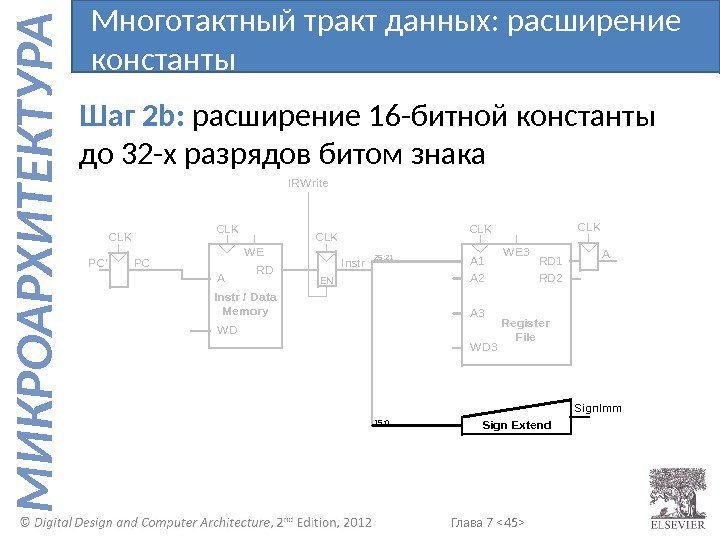

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: расширение константы Шаг 2 b: расширение 16 -битной константы до 32 -х разрядов битом знака Sign. Imm b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File PCPC’Instr 25: 21 15: 0 CLK W D WE CLKCLK A EN IRW rite

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: расширение константы Шаг 2 b: расширение 16 -битной константы до 32 -х разрядов битом знака Sign. Imm b CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File PCPC’Instr 25: 21 15: 0 CLK W D WE CLKCLK A EN IRW rite

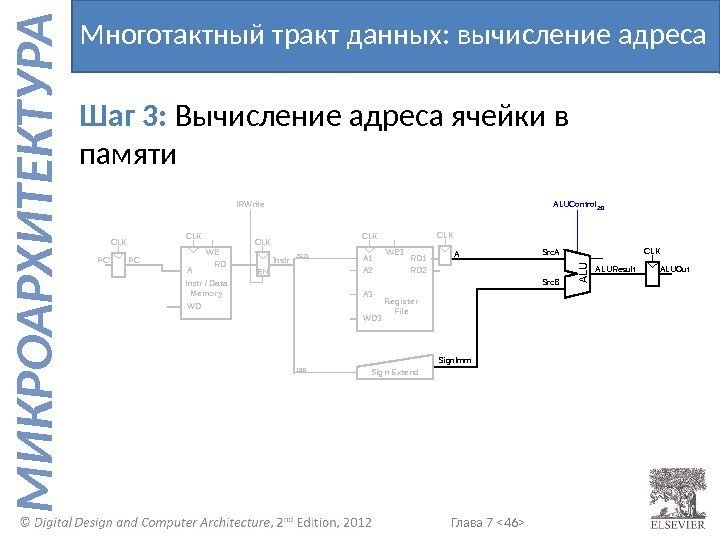

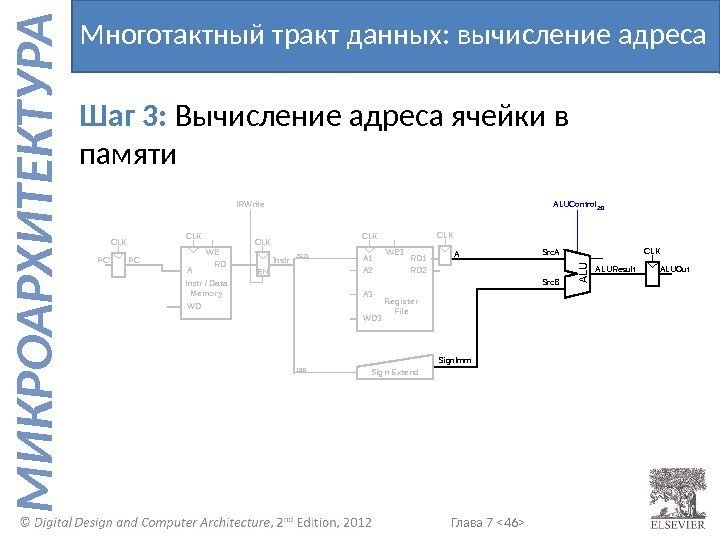

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: вычисление адреса Шаг 3: Вычисление адреса ячейки в памяти Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File PCPC’Instr 25: 21 15: 0 Src. B ALUResult Src. A ALUOut CLK ALUControl 2: 0 ALU WD W E CLKCLK ACLK EN IRW rite

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: вычисление адреса Шаг 3: Вычисление адреса ячейки в памяти Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File PCPC’Instr 25: 21 15: 0 Src. B ALUResult Src. A ALUOut CLK ALUControl 2: 0 ALU WD W E CLKCLK ACLK EN IRW rite

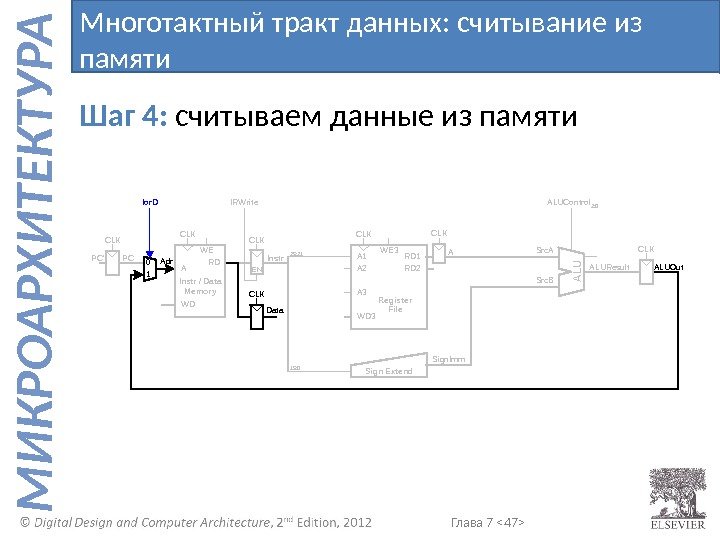

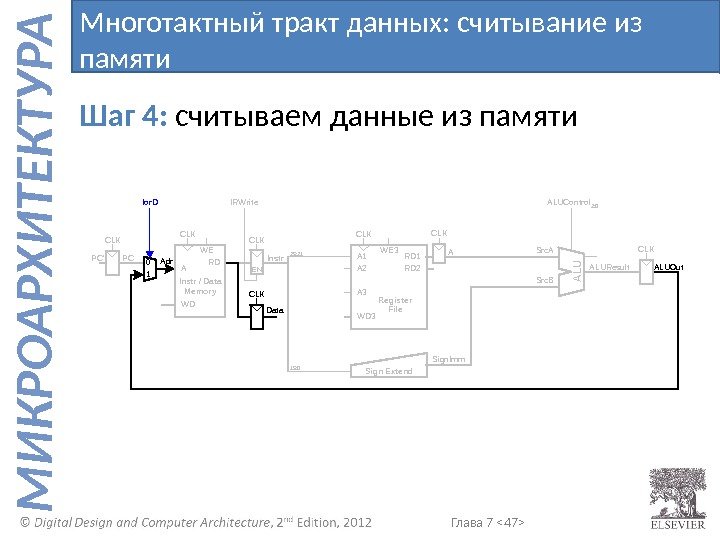

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: считывание из памяти Шаг 4: считываем данные из памяти Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File PCPC’Instr 25: 21 15: 0 Src. B ALUResult Src. A ALUOut CLK ALUControl 2: 0 ALU WD W E CLK Adr Data CLK ACLK EN IRW rite. Ior.

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: считывание из памяти Шаг 4: считываем данные из памяти Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File PCPC’Instr 25: 21 15: 0 Src. B ALUResult Src. A ALUOut CLK ALUControl 2: 0 ALU WD W E CLK Adr Data CLK ACLK EN IRW rite. Ior.

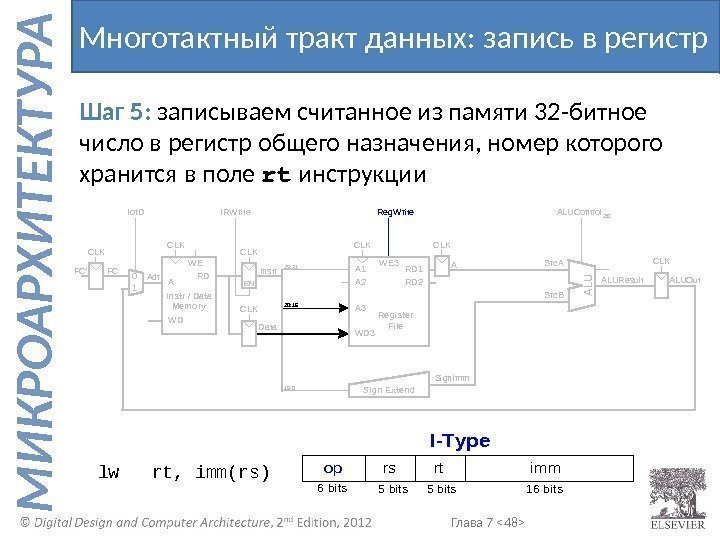

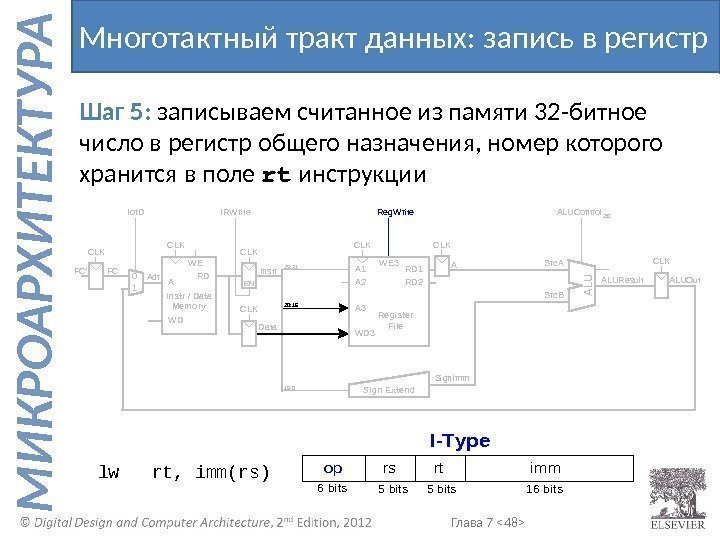

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: запись в регистр Шаг 5: записываем считанное из памяти 32 -битное число в регистр общего назначения, номер которого хранится в поле rt инструкции lw rt, imm(rs) Sign. Imm b CLK ARD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File PCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut Reg. W rite CLK ALUControl 2: 0 ALU W D WE CLK Adr Data CLK ACLK EN IRW rite. Ior. D 0 1 oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: запись в регистр Шаг 5: записываем считанное из памяти 32 -битное число в регистр общего назначения, номер которого хранится в поле rt инструкции lw rt, imm(rs) Sign. Imm b CLK ARD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File PCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut Reg. W rite CLK ALUControl 2: 0 ALU W D WE CLK Adr Data CLK ACLK EN IRW rite. Ior. D 0 1 oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: увеличиваем PC Шаг 6: вычисляем адрес следующей инструкции и записываем в PC PCWrite Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut ALUSrc. AReg. W rite CLK ALUControl 2: 0 ALU W D WE CLK Adr Data CLK A 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior.

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: увеличиваем PC Шаг 6: вычисляем адрес следующей инструкции и записываем в PC PCWrite Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 WD 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PCPC’Instr 25: 21 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut ALUSrc. AReg. W rite CLK ALUControl 2: 0 ALU W D WE CLK Adr Data CLK A 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior.

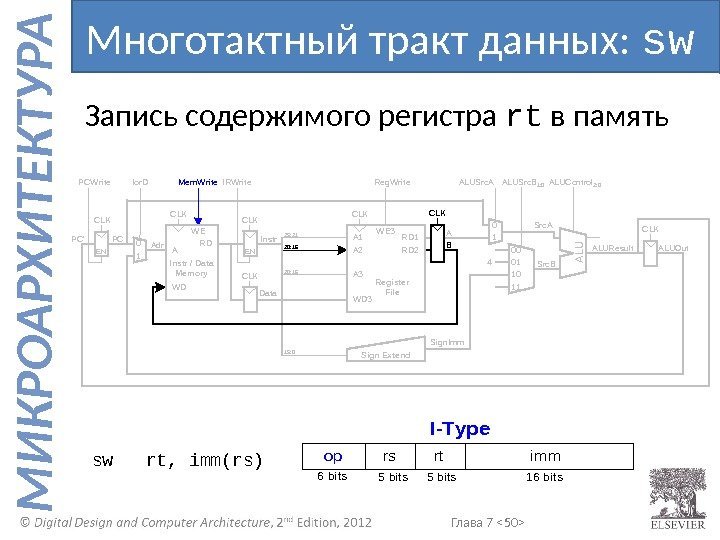

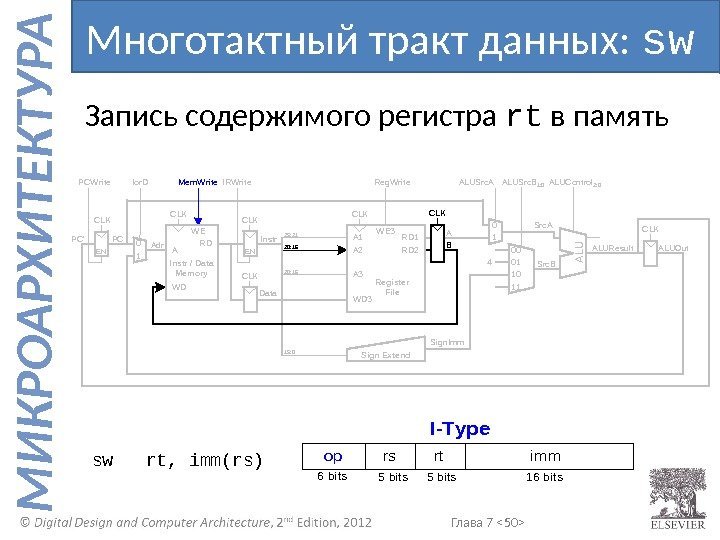

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: sw Запись содержимого регистра rt в память sw rt, imm(rs) Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut Mem. W rite. ALUSrc. AReg. Write CLK ALUControl 2: 0 ALU W D W E CLK Adr Data CLK A 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite B oprsrtimm 6 bits 5 bits 16 bits I-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: sw Запись содержимого регистра rt в память sw rt, imm(rs) Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 ALUResult Src. A ALUOut Mem. W rite. ALUSrc. AReg. Write CLK ALUControl 2: 0 ALU W D W E CLK Adr Data CLK A 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite B oprsrtimm 6 bits 5 bits 16 bits I-Type

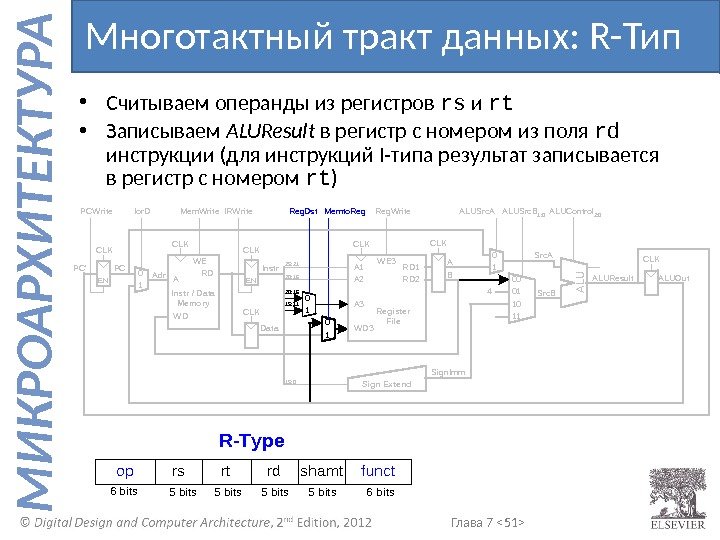

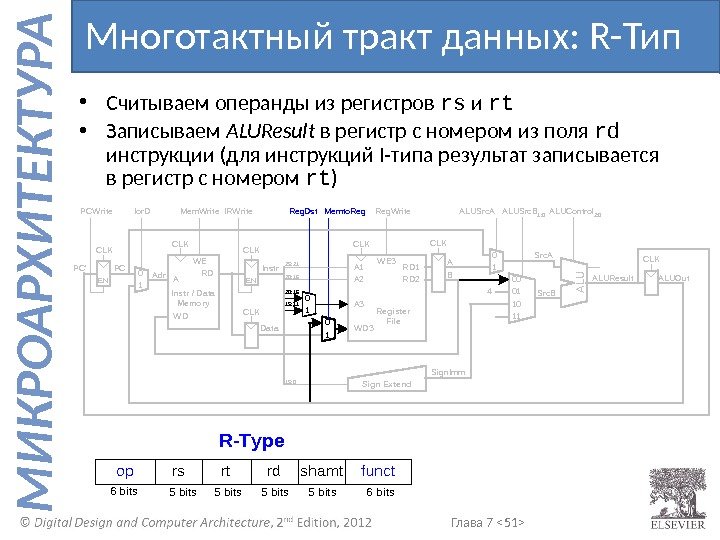

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: R-Тип • Считываем операнды из регистров rs и rt • Записываем ALUResult в регистр с номером из поля rd инструкции (для инструкций I-типа результат записывается в регистр с номером rt ) 0 1 Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 ALUResult Src. A ALUOut Reg. Dst. Mem. W rite. Memto. Reg. ALUSrc. AReg. W rite CLK ALUControl 2: 0 ALU WD WE CLK Adr Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCWrite oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный тракт данных: R-Тип • Считываем операнды из регистров rs и rt • Записываем ALUResult в регистр с номером из поля rd инструкции (для инструкций I-типа результат записывается в регистр с номером rt ) 0 1 Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 ALUResult Src. A ALUOut Reg. Dst. Mem. W rite. Memto. Reg. ALUSrc. AReg. W rite CLK ALUControl 2: 0 ALU WD WE CLK Adr Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCWrite oprsrtrdshamtfunct 6 bits 5 bits 6 bits R-Type

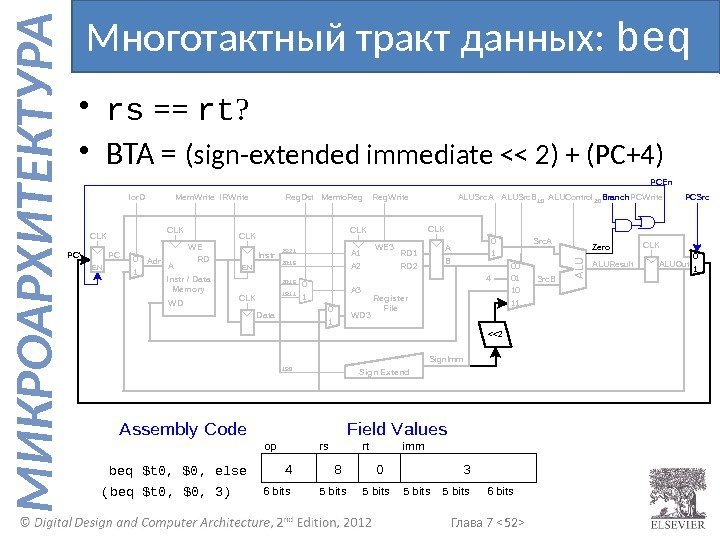

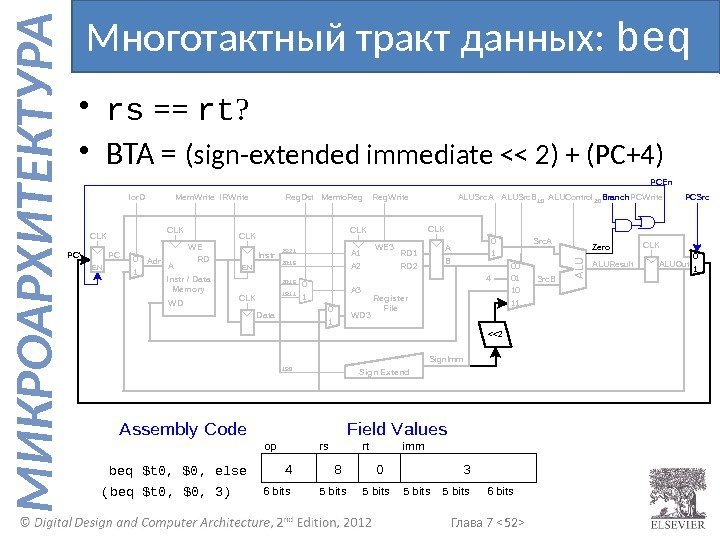

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • rs == rt ? • BTA = (sign-extended immediate << 2) + (PC+4)Многотактный тракт данных: beq Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 10 1 PC'Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut Reg. Dst. Branch. Mem. Write. Memto. Reg. ALUSrc. AReg. W rite Zero PCSrc CLK ALUControl 2: 0 ALU W D W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite PCEn beq $t 0, $0, else Assembly Code. Field Values 4 8 0 3 oprsrtimm 6 bits 5 bits 6 bits(beq $t 0, $0, 3)

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • rs == rt ? • BTA = (sign-extended immediate << 2) + (PC+4)Многотактный тракт данных: beq Sign. Imm b CLK ARD Instr / Data. Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register. File 0 10 1 PC'Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut Reg. Dst. Branch. Mem. Write. Memto. Reg. ALUSrc. AReg. W rite Zero PCSrc CLK ALUControl 2: 0 ALU W D W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite PCEn beq $t 0, $0, else Assembly Code. Field Values 4 8 0 3 oprsrtimm 6 bits 5 bits 6 bits(beq $t 0, $0, 3)

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный процессор Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst. Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCW rite PCEn

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактный процессор Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst. Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCW rite PCEn

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактное устройство управления ALUSrc. APCSrc Branch. ALUSrc. B 1: 0 Opcode 5: 0 Control Unit ALUControl 2: 0 Funct 5: 0 Main Controller (FSM) ALUOp 1: 0 ALU Decoder Reg. W rite. PCW rite Ior. D Mem. W rite. IRW rite Reg. Dst. Memto. Register Enables. Multiplexer Selects

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АМноготактное устройство управления ALUSrc. APCSrc Branch. ALUSrc. B 1: 0 Opcode 5: 0 Control Unit ALUControl 2: 0 Funct 5: 0 Main Controller (FSM) ALUOp 1: 0 ALU Decoder Reg. W rite. PCW rite Ior. D Mem. W rite. IRW rite Reg. Dst. Memto. Register Enables. Multiplexer Selects

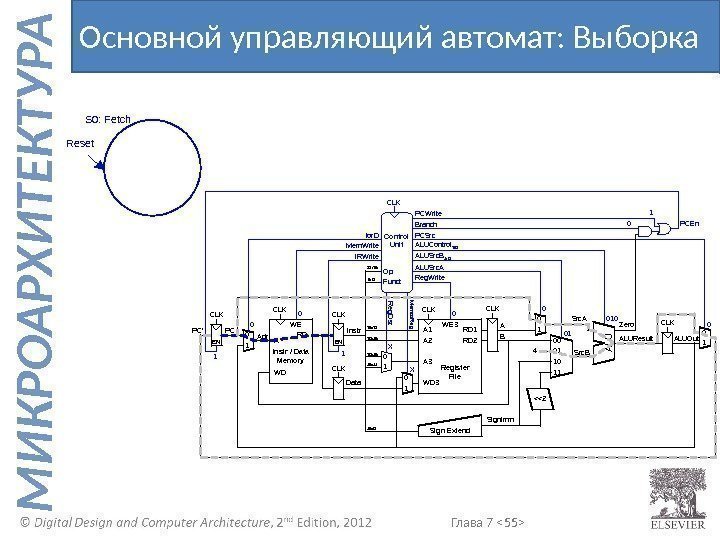

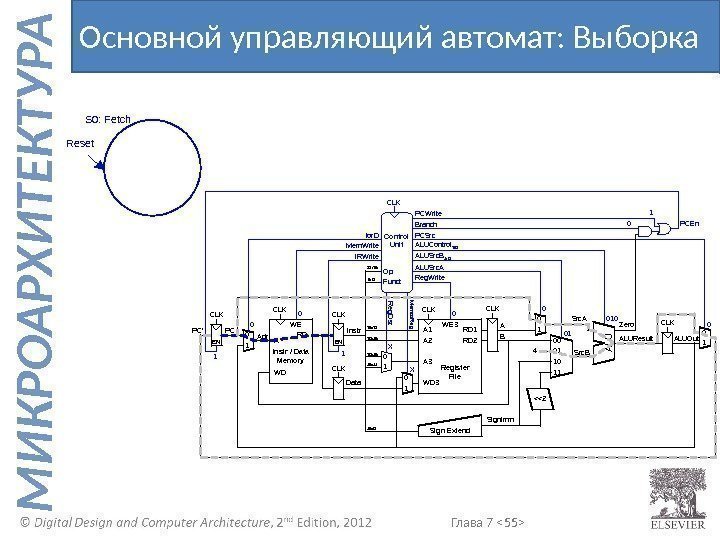

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Выборка Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn 0 1 10 X X 0 0 01 010 01 0 Reset S 0: Fetch

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Выборка Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn 0 1 10 X X 0 0 01 010 01 0 Reset S 0: Fetch

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Выборка • Сигналы разрешения записи будем показывать только если они не равны нулю • Одновременно со считыванием инструкции при помощи АЛУ увеличиваем на 4 содержимое PC Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU WD W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn 0 1 10 X X 0 0 01 010 01 0 Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRWrite PCW rite Reset S 0: Fetch

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Выборка • Сигналы разрешения записи будем показывать только если они не равны нулю • Одновременно со считыванием инструкции при помощи АЛУ увеличиваем на 4 содержимое PC Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU WD W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn 0 1 10 X X 0 0 01 010 01 0 Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRWrite PCW rite Reset S 0: Fetch

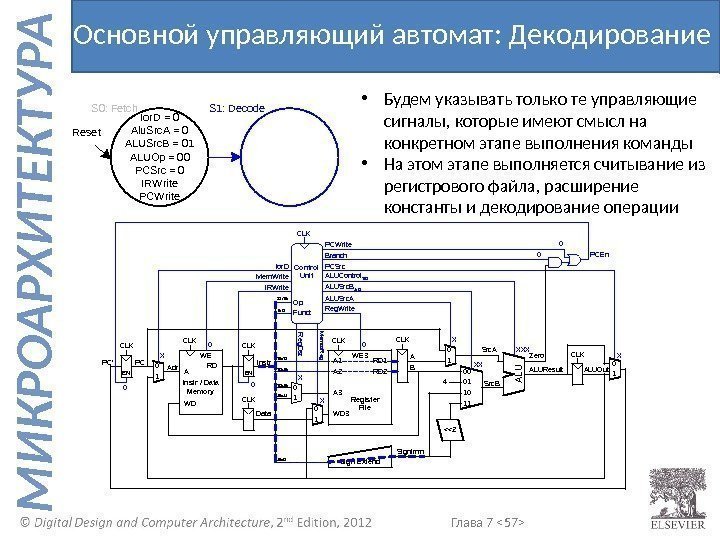

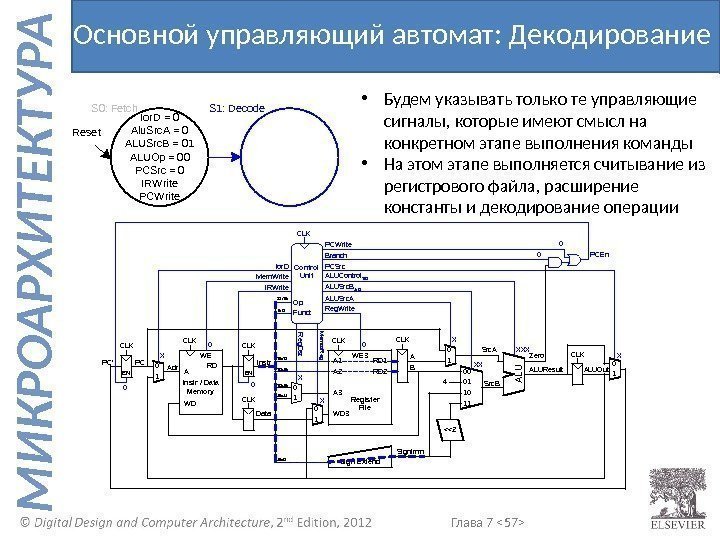

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Декодирование • Будем указывать только те управляющие сигналы, которые имеют смысл на конкретном этапе выполнения команды • На этом этапе выполняется считывание из регистрового файла, расширение константы и декодирование операции Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCWrite Reset S 0: Fetch. S 1: Decode Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X XX X

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Декодирование • Будем указывать только те управляющие сигналы, которые имеют смысл на конкретном этапе выполнения команды • На этом этапе выполняется считывание из регистрового файла, расширение константы и декодирование операции Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCWrite Reset S 0: Fetch. S 1: Decode Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLK ENEN ALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X XX X

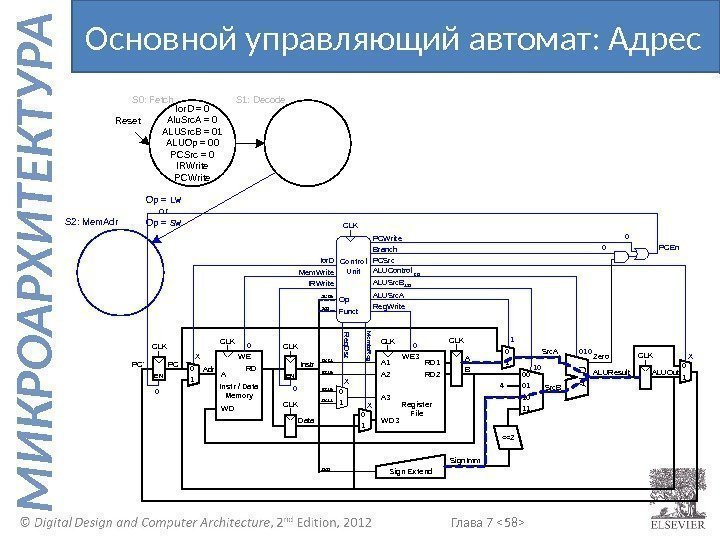

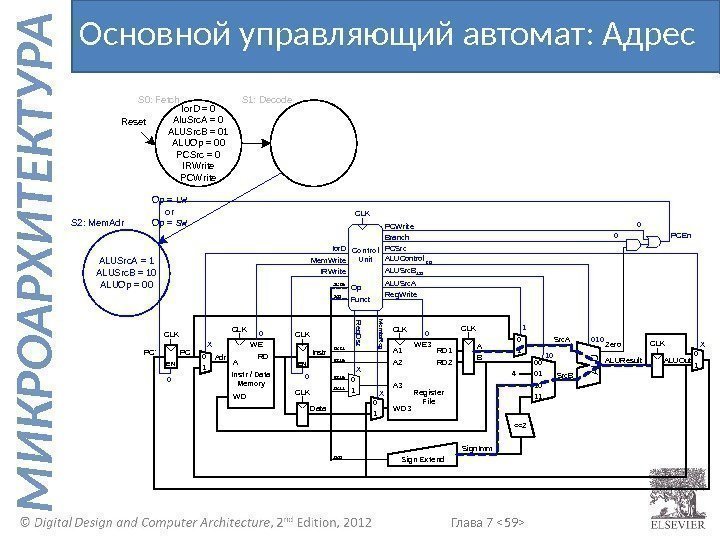

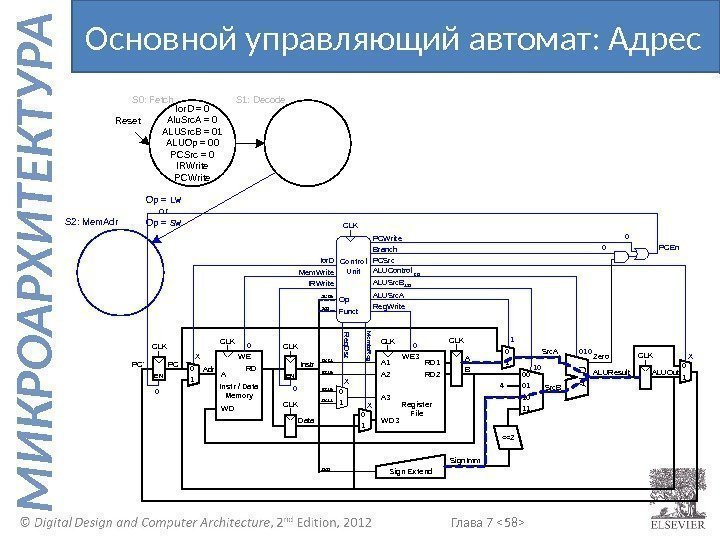

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Адрес Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite Reset S 0: Fetch S 2: Mem. Adr S 1: Decode Op = LW or Op = SW Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. Write. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D WECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X X 0 1 10 010 X

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Адрес Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite Reset S 0: Fetch S 2: Mem. Adr S 1: Decode Op = LW or Op = SW Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. Write. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU W D WECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X X 0 1 10 010 X

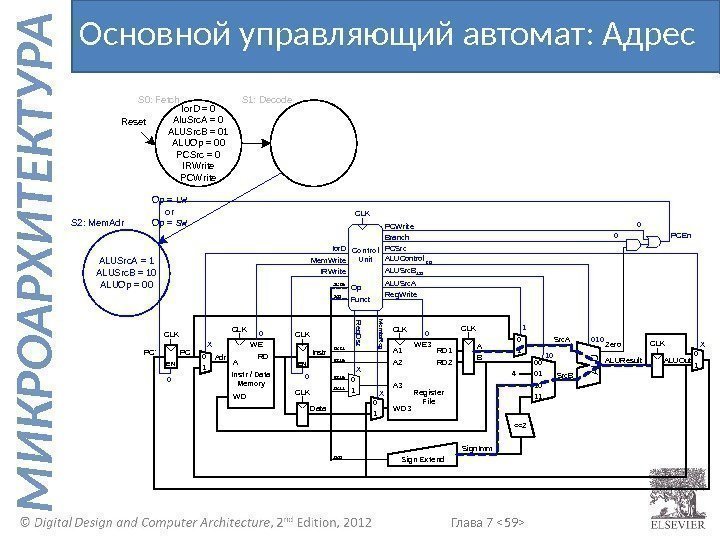

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Адрес Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode Op = LW or Op = SW Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU WD WECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X X 0 1 10 010 X

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: Адрес Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode Op = LW or Op = SW Sign. Imm. CLK A RD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control Unit Zero. PCSrc. CLK ALUControl 2: 0 ALU WD WECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENENALUSrc. B 1: 0 IRW rite Ior. D PCWrite PCEn X 0 00 X X 0 1 10 010 X

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: lw Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read Op = LW or Op = SW Op = LW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: lw Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read Op = LW or Op = SW Op = LW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: sw Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Mem. Write. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite. Op = LW or Op = SW Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: sw Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Mem. Write. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite. Op = LW or Op = SW Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: R-Тип Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback. Op = LW or Op = SW Op = R-type Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: R-Тип Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback. Op = LW or Op = SW Op = R-type Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : beq Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : beq Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: addi Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback Op = ADDI S 9: ADDI Execute S 10: ADDI W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: addi Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback Op = ADDI S 9: ADDI Execute S 10: ADDI W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: addi Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite. Op = ADDI S 9: ADDI Execute S 10: ADDI W riteback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат: addi Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 0 IRW rite PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. W rite ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 1 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU W riteback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem W riteback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite. Op = ADDI S 9: ADDI Execute S 10: ADDI W riteback

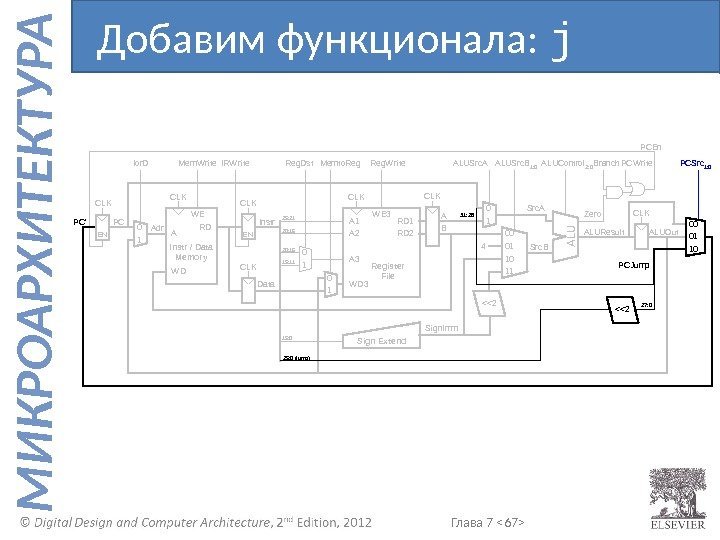

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: j Sign. Imm CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut Reg. Dst. Branch. Mem. Write. Memto. Reg. ALUSrc. AReg. Write Zero PCSrc 1: 0 CLK ALUControl 2: 0 ALU WD W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite PCEn 00 01 10 <<2 25: 0 (jump) 31: 28 27: 0 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АДобавим функционала: j Sign. Imm CLK ARD Instr / Data Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 PC 0 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut Reg. Dst. Branch. Mem. Write. Memto. Reg. ALUSrc. AReg. Write Zero PCSrc 1: 0 CLK ALUControl 2: 0 ALU WD W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRW rite. Ior. DPCW rite PCEn 00 01 10 <<2 25: 0 (jump) 31: 28 27: 0 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : j Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 00 IRW rite. PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 01 Branch Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read. S 5: Mem. W rite S 6: Execute S 7: ALUWriteback S 8: Branch Op = LWor. Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite S 4: Mem. Writeback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite Op = ADDI S 9: ADDIExecute S 10: ADDIW riteback Op = J S 11: Jump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : j Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 00 IRW rite. PCW rite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 01 Branch Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read. S 5: Mem. W rite S 6: Execute S 7: ALUWriteback S 8: Branch Op = LWor. Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite S 4: Mem. Writeback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite Op = ADDI S 9: ADDIExecute S 10: ADDIW riteback Op = J S 11: Jump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : j Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 00 IRW rite PCWrite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 01 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU Writeback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem Writeback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite. Op = ADDI S 9: ADDI Execute S 10: ADDI Writeback PCSrc = 10 PCWrite. Op = J S 11: Jump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОсновной управляющий автомат : j Ior. D = 0 Alu. Src. A = 0 ALUSrc. B = 01 ALUOp = 00 PCSrc = 00 IRW rite PCWrite ALUSrc. A = 0 ALUSrc. B = 11 ALUOp = 00 ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Ior. D = 1 Reg. Dst = 1 Memto. Reg = 0 Reg. W rite. Ior. D = 1 Mem. Write ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 10 ALUSrc. A = 1 ALUSrc. B = 00 ALUOp = 01 PCSrc = 01 Branch. Reset S 0: Fetch S 2: Mem. Adr S 1: Decode S 3: Mem. Read S 5: Mem. W rite S 6: Execute S 7: ALU Writeback S 8: Branch. Op = LW or Op = SW Op = R-type Op = BEQ Op = LW Op = SW Reg. Dst = 0 Memto. Reg = 1 Reg. W rite. S 4: Mem Writeback ALUSrc. A = 1 ALUSrc. B = 10 ALUOp = 00 Reg. Dst = 0 Memto. Reg = 0 Reg. W rite. Op = ADDI S 9: ADDI Execute S 10: ADDI Writeback PCSrc = 10 PCWrite. Op = J S 11: Jump

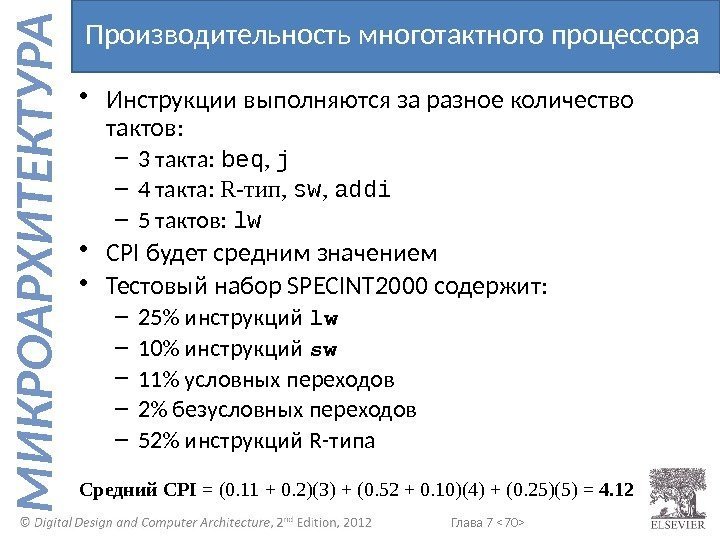

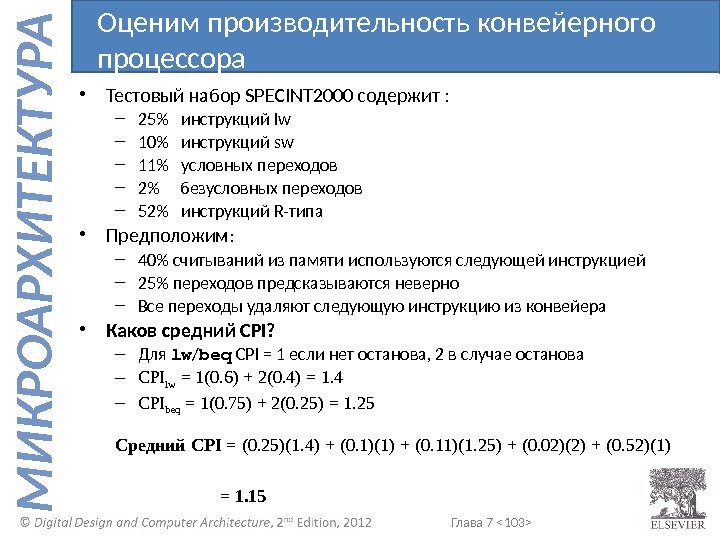

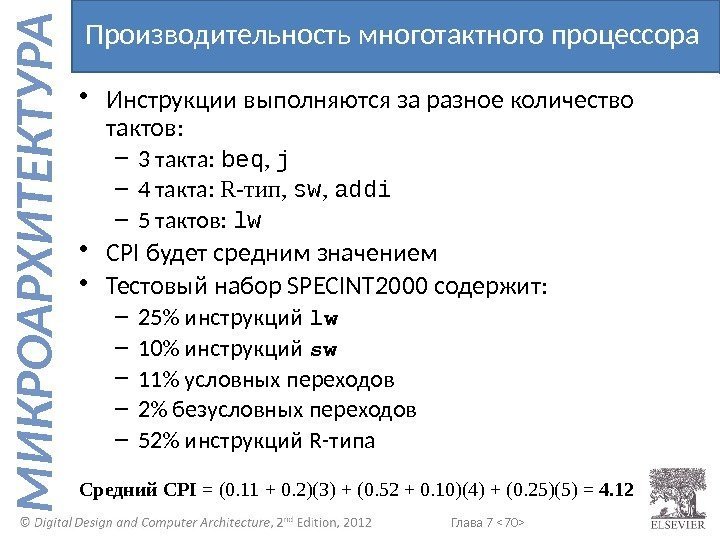

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Инструкции выполняются за разное количество тактов: – 3 такта : beq , j – 4 такта: R-тип, sw , addi – 5 тактов: lw • CPI будет средним значением • Тестовый набор SPECINT 2000 содержит: – 25% инструкций lw – 10% инструкций sw – 11% условных переходов – 2% безусловных переходов – 52% инструкций R-типа Средний CPI = (0. 11 + 0. 2)(3) + (0. 52 + 0. 10)(4) + (0. 25)(5) = 4. 12 Производительность многотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Инструкции выполняются за разное количество тактов: – 3 такта : beq , j – 4 такта: R-тип, sw , addi – 5 тактов: lw • CPI будет средним значением • Тестовый набор SPECINT 2000 содержит: – 25% инструкций lw – 10% инструкций sw – 11% условных переходов – 2% безусловных переходов – 52% инструкций R-типа Средний CPI = (0. 11 + 0. 2)(3) + (0. 52 + 0. 10)(4) + (0. 25)(5) = 4. 12 Производительность многотактного процессора

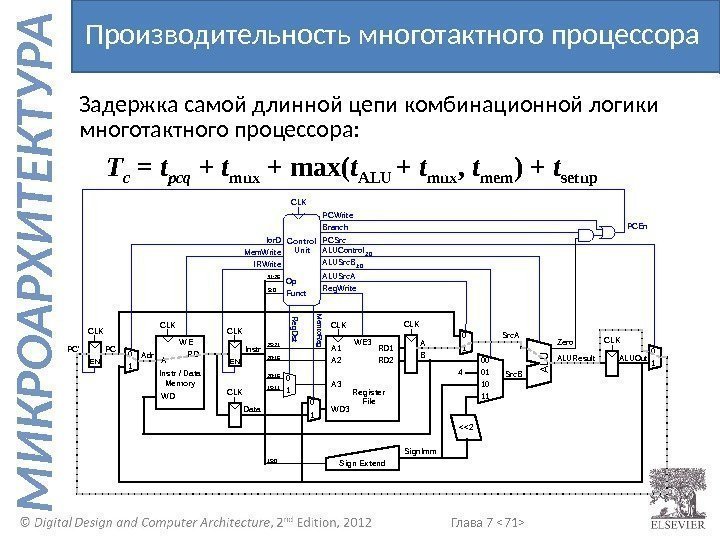

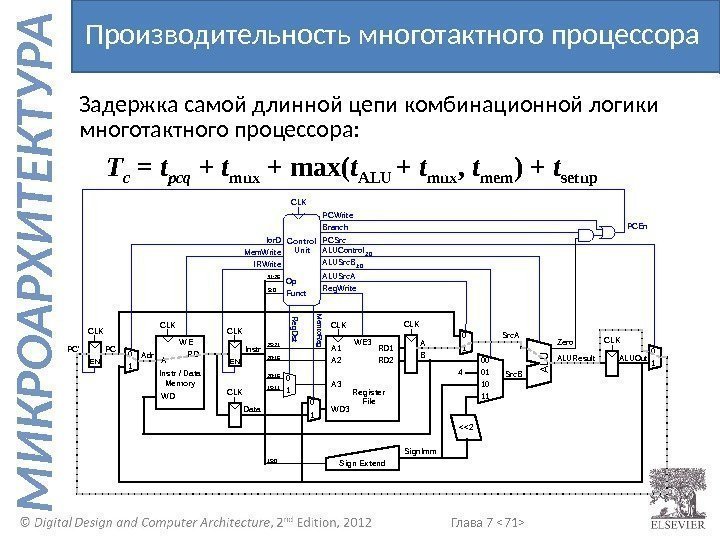

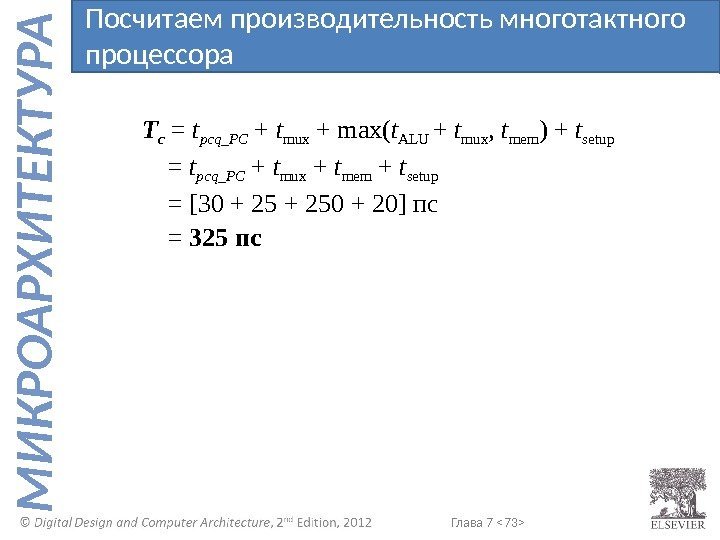

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЗадержка самой длинной цепи комбинационной логики многотактного процессора: T c = t pcq + t mux + max( t ALU + t mux , t mem ) + t setup. Производительность многотактного процессора Sign. Imm CLK ARD Instr / Data. Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File 0 10 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control. Unit Zero PCSrc CLK ALUControl 2: 0 ALU WD W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRWrite Ior. D PCWrite PCEn

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АЗадержка самой длинной цепи комбинационной логики многотактного процессора: T c = t pcq + t mux + max( t ALU + t mux , t mem ) + t setup. Производительность многотактного процессора Sign. Imm CLK ARD Instr / Data. Memory A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register. File 0 10 1 PC’Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult Src. A ALUOut 31: 26 Reg. Dst Branch Mem. W rite Memto. Reg ALUSrc. A Reg. W rite. Op Funct Control. Unit Zero PCSrc CLK ALUControl 2: 0 ALU WD W E CLK Adr 0 1 Data CLK A B 00 01 10 11 4 CLK ENEN ALUSrc. B 1: 0 IRWrite Ior. D PCWrite PCEn

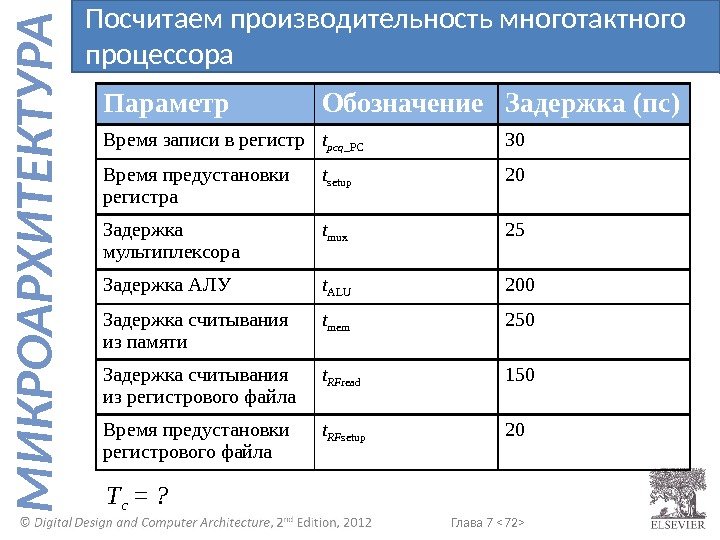

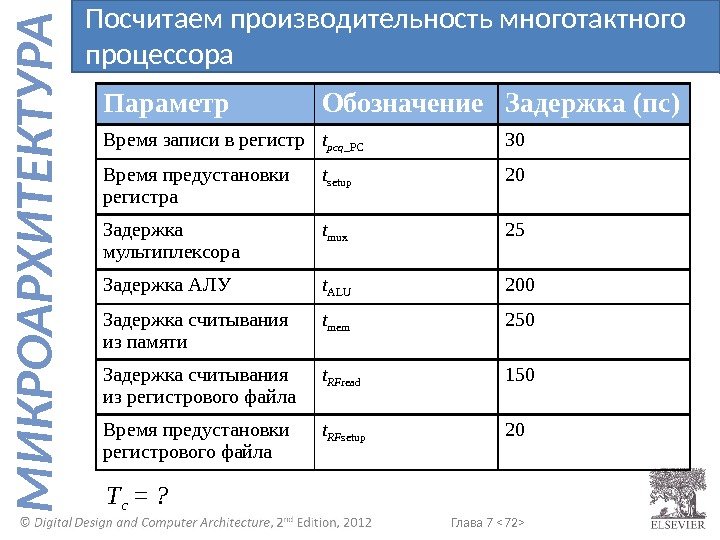

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = ? Посчитаем производительность многотактного процессора Параметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = ? Посчитаем производительность многотактного процессора Параметр Обозначение Задержка (пс) Время записи в регистр t pcq _PC 30 Время предустановки регистра t setup 20 Задержка мультиплексора t mux 25 Задержка АЛУ t ALU 200 Задержка считывания из памяти t mem 250 Задержка считывания из регистрового файла t RF read 150 Время предустановки регистрового файла t RF setup

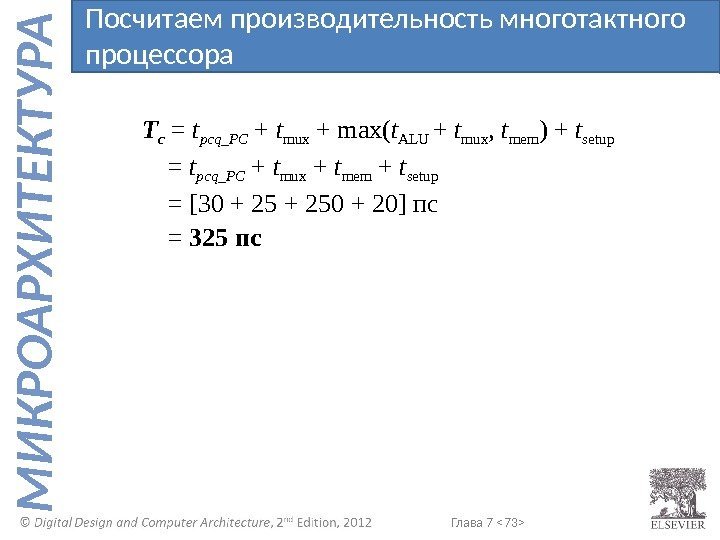

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = t pcq_PC + t mux + max( t ALU + t mux , t mem ) + t setup = t pcq_PC + t mux + t mem + t setup = [30 + 250 + 20] пс = 325 пс. Посчитаем производительность многотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АT c = t pcq_PC + t mux + max( t ALU + t mux , t mem ) + t setup = t pcq_PC + t mux + t mem + t setup = [30 + 250 + 20] пс = 325 пс. Посчитаем производительность многотактного процессора

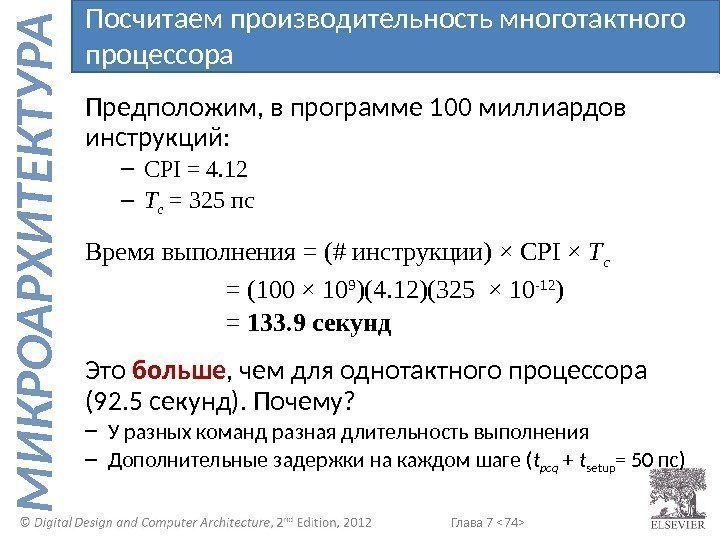

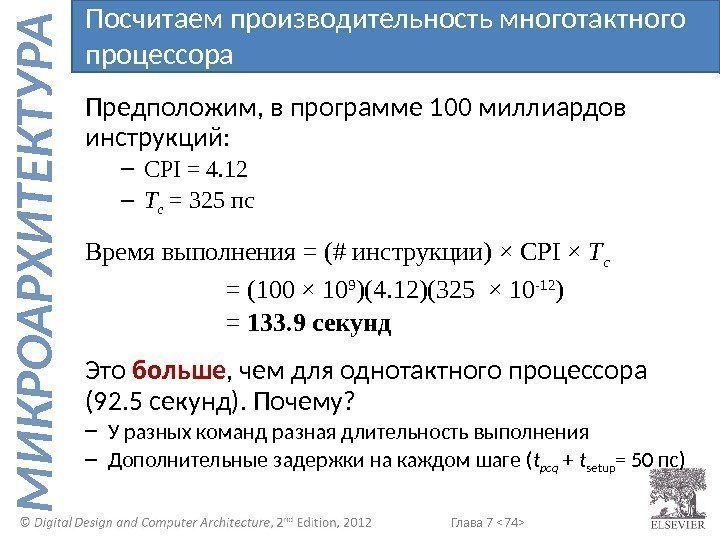

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПредположим, в программе 100 миллиардов инструкций: – CPI = 4. 12 – T c = 325 пс Время выполнения = (# инструкции) × CPI × T c = (100 × 10 9 )(4. 12)(325 × 10 -12 ) = 133. 9 секунд Это больше , чем для однотактного процессора (92. 5 секунд). Почему? – У разных команд разная длительность выполнения – Дополнительные задержки на каждом шаге ( t pcq + t setup = 50 пс)Посчитаем производительность многотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПредположим, в программе 100 миллиардов инструкций: – CPI = 4. 12 – T c = 325 пс Время выполнения = (# инструкции) × CPI × T c = (100 × 10 9 )(4. 12)(325 × 10 -12 ) = 133. 9 секунд Это больше , чем для однотактного процессора (92. 5 секунд). Почему? – У разных команд разная длительность выполнения – Дополнительные задержки на каждом шаге ( t pcq + t setup = 50 пс)Посчитаем производительность многотактного процессора

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПовторение: однотактный процессор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 0 1 25: 0 <<227: 0 31: 28 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПовторение: однотактный процессор Sign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data Write. Data. Src. A PCPlus 4 PCBranch. Write. Reg 4: 0 Result 31: 26 Reg. Dst. Branch. Mem. Write. Memto. Reg ALUSrc Reg. W rite. Op Funct. Control Unit Zero PCSrc CLKALUControl 2: 0 ALU 0 1 25: 0 <<227: 0 31: 28 PCJump

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПовторение: многотактный процессор Imm. Ext. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut. Zero. CLK ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENEN 00 01 10 <<2 25: 0 (Addr) 31: 28 27: 0 PCJump 5: 0 31: 26 Branch Mem. W rite ALUSrc. A Reg. W rite. Op Funct Control Unit PCSrc. CLK ALUControl 2: 0 ALUSrc. B 1: 0 IRW rite Ior. D PCW rite PCEn Reg. Dst Memto. Reg

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АПовторение: многотактный процессор Imm. Ext. CLK A RD Instr / Data Memory A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 PC 0 1 PC’ Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 ALUResult. Src. A ALUOut. Zero. CLK ALU W D W ECLK Adr 0 1 Data. CLK A B 00 01 10 114 CLKENEN 00 01 10 <<2 25: 0 (Addr) 31: 28 27: 0 PCJump 5: 0 31: 26 Branch Mem. W rite ALUSrc. A Reg. W rite. Op Funct Control Unit PCSrc. CLK ALUControl 2: 0 ALUSrc. B 1: 0 IRW rite Ior. D PCW rite PCEn Reg. Dst Memto. Reg

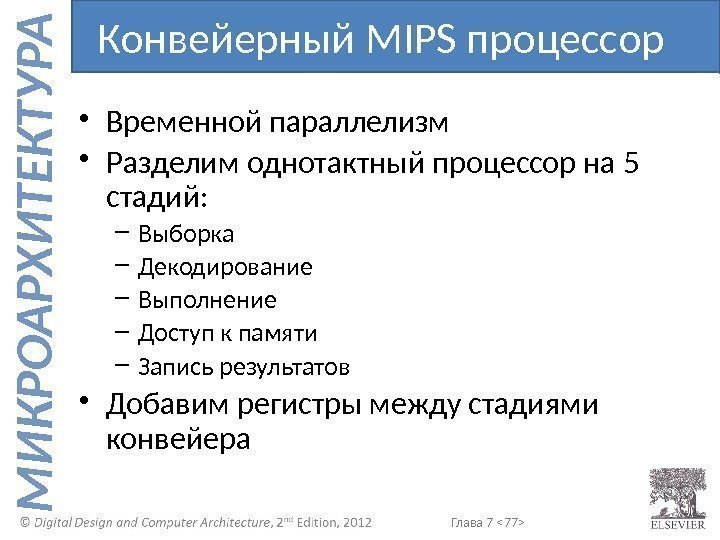

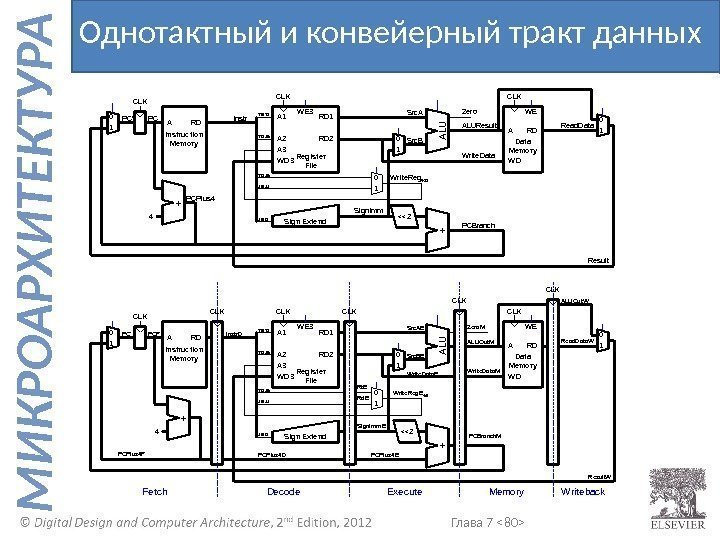

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Временной параллелизм • Разделим однотактный процессор на 5 стадий: – Выборка – Декодирование – Выполнение – Доступ к памяти – Запись результатов • Добавим регистры между стадиями конвейера. Конвейерный MIPS процессор

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • Временной параллелизм • Разделим однотактный процессор на 5 стадий: – Выборка – Декодирование – Выполнение – Доступ к памяти – Запись результатов • Добавим регистры между стадиями конвейера. Конвейерный MIPS процессор

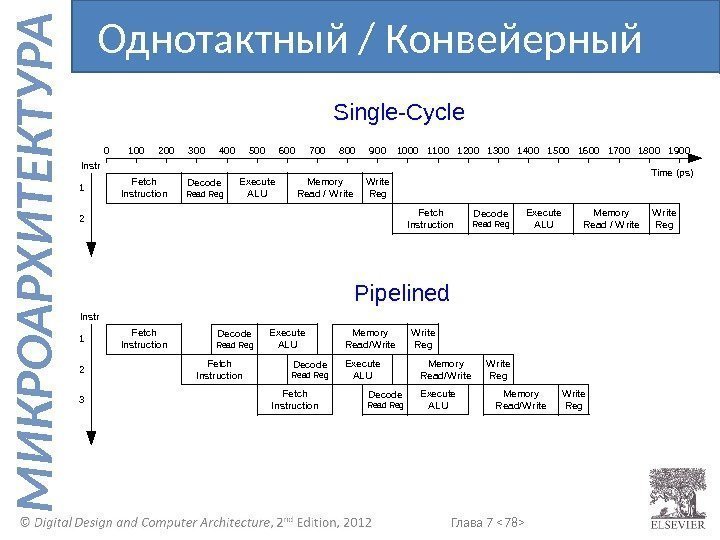

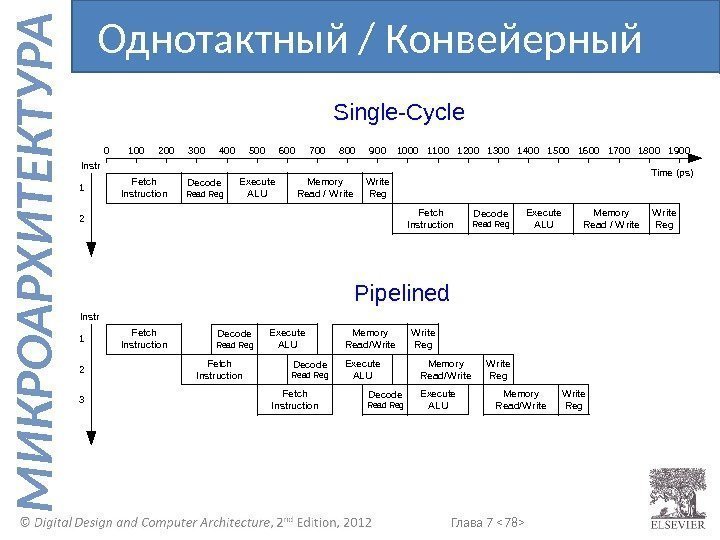

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный / Конвейерный Time (ps)Instr Fetch Instruction Decode Read Reg Execute ALU Memory Read / W rite Write Reg 1 2 0 100 200 300 400 500 600 700 800 900 1100 1200 1300 1400 1500 1600 1700 1800 19001000 Instr 1 2 3 Fetch Instruction Decode Read Reg Execute ALU Memory Read / W rite Reg Fetch Instruction Decode Read Reg Execute ALU Memory Read/Write Write Reg Single-Cycle Pipelined

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный / Конвейерный Time (ps)Instr Fetch Instruction Decode Read Reg Execute ALU Memory Read / W rite Write Reg 1 2 0 100 200 300 400 500 600 700 800 900 1100 1200 1300 1400 1500 1600 1700 1800 19001000 Instr 1 2 3 Fetch Instruction Decode Read Reg Execute ALU Memory Read / W rite Reg Fetch Instruction Decode Read Reg Execute ALU Memory Read/Write Write Reg Single-Cycle Pipelined

Глава 7 М И К Р О А Р Х И Т Е К Т У Р ААбстрактное представление конвейера Time (cycles) lw $s 2, 40($0) RF 40$0 RF$s 2 + DM RF $t 2$t 1 RF$s 3 + DM RF $s 5$s 1 RF$s 4 — DM RF $t 6$t 5 RF$s 5 & DM RF 20$s 1 RF$s 6 + DM RF $t 4$t 3 RF$s 7 | DMadd $s 3, $t 1, $t 2 sub $s 4, $s 1, $s 5 and $s 5, $t 6 sw $s 6, 20($s 1) or $s 7, $t 3, $t 4 1 2 3 4 5 6 7 8 9 10 add IMIMIM lw sub and sw or

Глава 7 М И К Р О А Р Х И Т Е К Т У Р ААбстрактное представление конвейера Time (cycles) lw $s 2, 40($0) RF 40$0 RF$s 2 + DM RF $t 2$t 1 RF$s 3 + DM RF $s 5$s 1 RF$s 4 — DM RF $t 6$t 5 RF$s 5 & DM RF 20$s 1 RF$s 6 + DM RF $t 4$t 3 RF$s 7 | DMadd $s 3, $t 1, $t 2 sub $s 4, $s 1, $s 5 and $s 5, $t 6 sw $s 6, 20($s 1) or $s 7, $t 3, $t 4 1 2 3 4 5 6 7 8 9 10 add IMIMIM lw sub and sw or

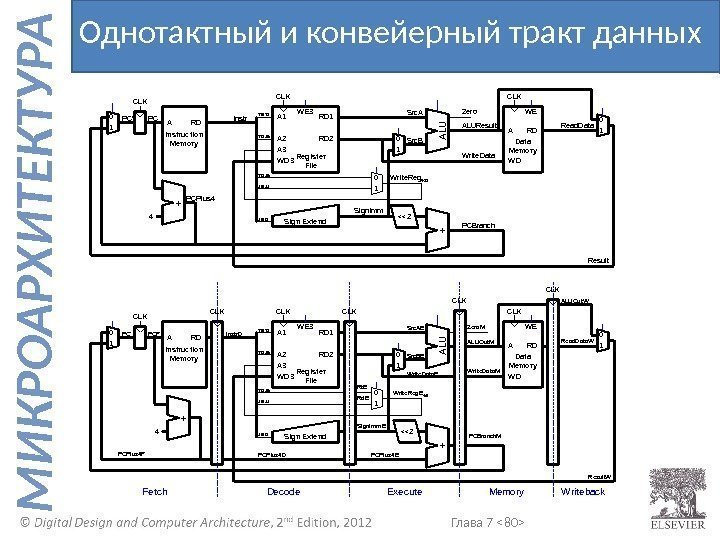

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный и конвейерный тракт данных Sign. Imm. ECLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E Write. Data. MSrc. AE PCPlus 4 D PCBranch. M Result. WPCPlus 4 EPCPlus 4 F Zero. MCLK ALU W rite. Reg. E 4: 0 CLK CLKSign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC' Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result. Zero CLK ALU Fetch Decode Execute Memory Writeback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АОднотактный и конвейерный тракт данных Sign. Imm. ECLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E Write. Data. MSrc. AE PCPlus 4 D PCBranch. M Result. WPCPlus 4 EPCPlus 4 F Zero. MCLK ALU W rite. Reg. E 4: 0 CLK CLKSign. Imm. CLK A RD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 W E 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory W D W E 0 1 PC 0 1 PC' Instr 25: 21 20: 16 15: 0 Src. B 20: 16 15: 11 <<2 + ALUResult Read. Data W rite. Data. Src. A PCPlus 4 PCBranch. W rite. Reg 4: 0 Result. Zero CLK ALU Fetch Decode Execute Memory Writeback

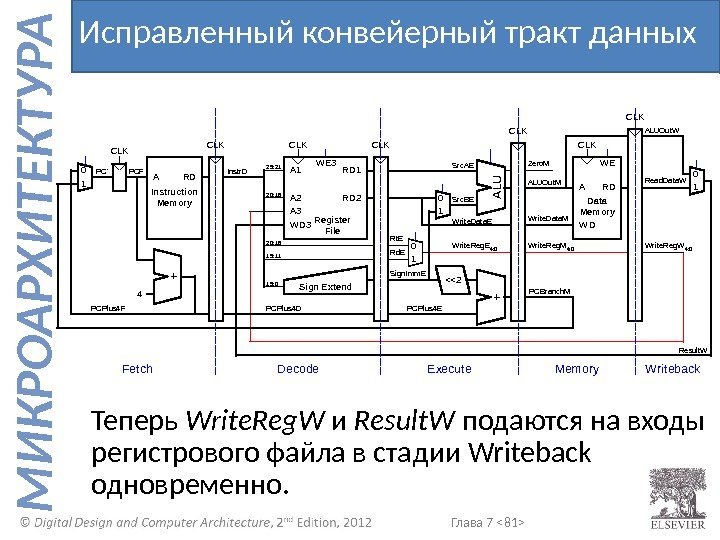

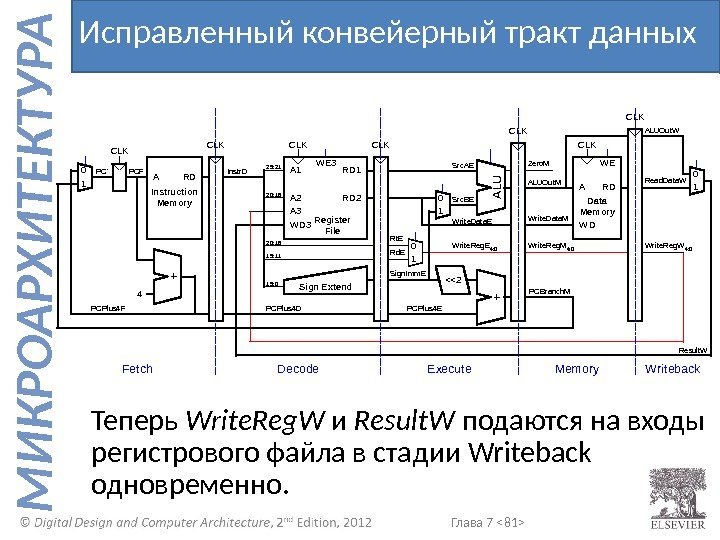

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АТеперь Write. Reg. W и Result. W подаются на входы регистрового файла в стадии Writeback одновременно. Исправленный конвейерный тракт данных Sign. Imm. E CLK ARD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 ARD Data Memory W D W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E W rite. Data. MSrc. AE PCPlus 4 D PCBranch. MW rite. Reg. M 4: 0 Result. WPCPlus 4 EPCPlus 4 F Zero. M CLKCLK W rite. Reg. W 4: 0 ALUW rite. Reg. E 4: 0 CLK CLK Fetch. Decode. Execute. Memory. Writeback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р АТеперь Write. Reg. W и Result. W подаются на входы регистрового файла в стадии Writeback одновременно. Исправленный конвейерный тракт данных Sign. Imm. E CLK ARD Instruction Memory + 4 A 1 A 3 W D 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 ARD Data Memory W D W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E W rite. Data. MSrc. AE PCPlus 4 D PCBranch. MW rite. Reg. M 4: 0 Result. WPCPlus 4 EPCPlus 4 F Zero. M CLKCLK W rite. Reg. W 4: 0 ALUW rite. Reg. E 4: 0 CLK CLK Fetch. Decode. Execute. Memory. Writeback

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • То же устройство управления, что и в однотактном процессоре • Сигналы управления доходят до соответствующей стадии с задержкой (сигналы управления тоже конвейеризируются)Управление конвейерным процессором Sign. Imm. ECLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E W rite. Data. MSrc. AE PCPlus 4 D PCBranch. MWrite. Reg. M 4: 0 Result. WPCPlus 4 EPCPlus 4 F 31: 26 Reg. Dst. DBranch. DMem. Write. DMemto. Reg. D ALUControl. D ALUSrc. DReg. W rite. D Op Funct. Control Unit Zero. M PCSrc. MCLK CLK CLK W rite. Reg. W 4: 0 ALUControl. E 2: 0 ALUReg. W rite. E Reg. Write. M Reg. Write. W Memto. Reg. E Memto. Reg. M Memto. Reg. W Mem. Write. E Mem. W rite. M Branch. E Branch. M Reg. Dst. EALUSrc. E Write. Reg. E 4:

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • То же устройство управления, что и в однотактном процессоре • Сигналы управления доходят до соответствующей стадии с задержкой (сигналы управления тоже конвейеризируются)Управление конвейерным процессором Sign. Imm. ECLK A RD Instruction Memory + 4 A 1 A 3 WD 3 RD 2 RD 1 WE 3 A 2 CLK Sign Extend Register File 0 1 A RD Data Memory WD W E 0 1 PCF 0 1 PC’ Instr. D 25: 21 20: 16 15: 0 Src. BE 20: 16 15: 11 Rt. E Rd. E <<2 + ALUOut. M ALUOut. W Read. Data. W W rite. Data. E W rite. Data. MSrc. AE PCPlus 4 D PCBranch. MWrite. Reg. M 4: 0 Result. WPCPlus 4 EPCPlus 4 F 31: 26 Reg. Dst. DBranch. DMem. Write. DMemto. Reg. D ALUControl. D ALUSrc. DReg. W rite. D Op Funct. Control Unit Zero. M PCSrc. MCLK CLK CLK W rite. Reg. W 4: 0 ALUControl. E 2: 0 ALUReg. W rite. E Reg. Write. M Reg. Write. W Memto. Reg. E Memto. Reg. M Memto. Reg. W Mem. Write. E Mem. W rite. M Branch. E Branch. M Reg. Dst. EALUSrc. E Write. Reg. E 4:

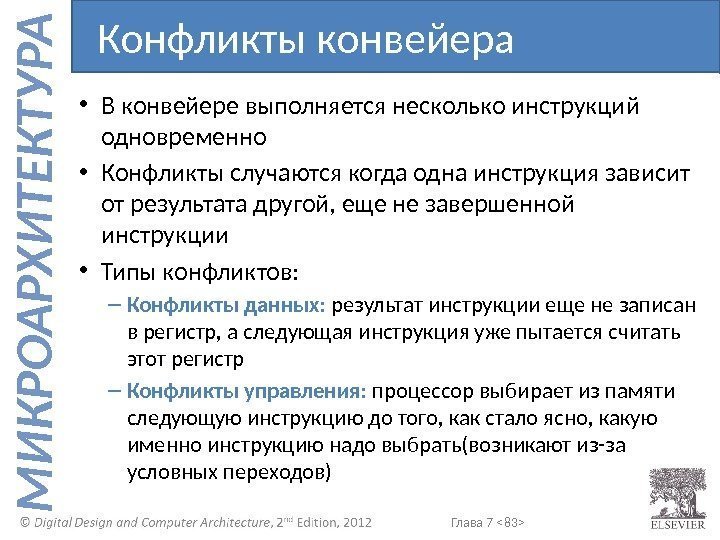

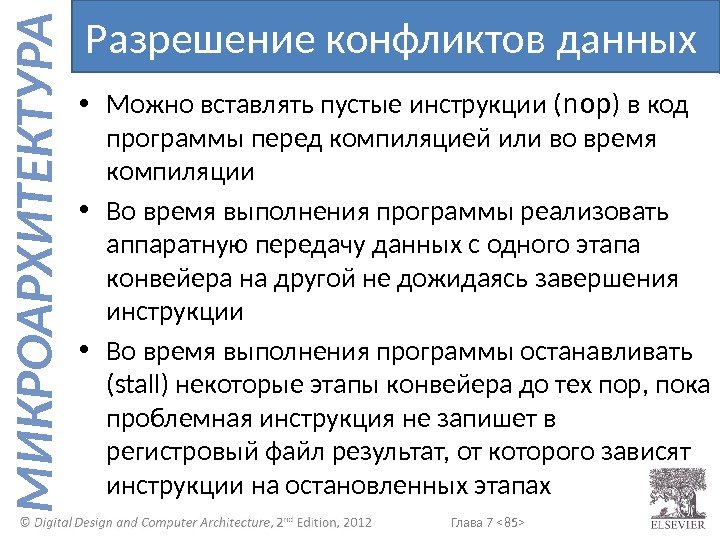

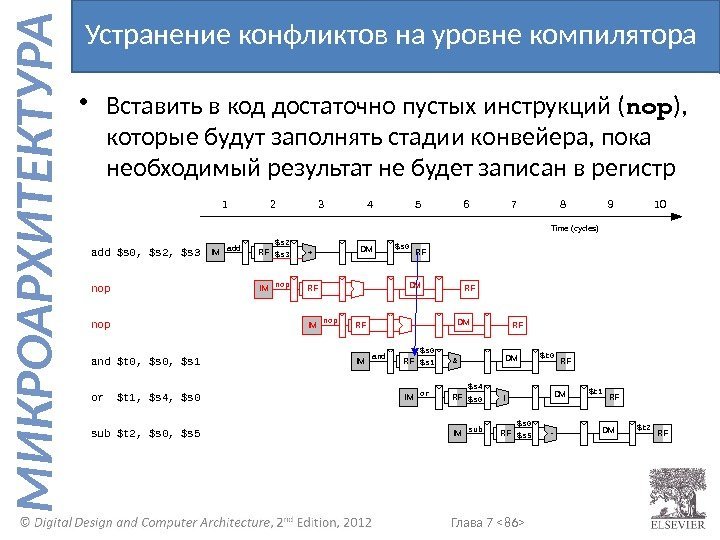

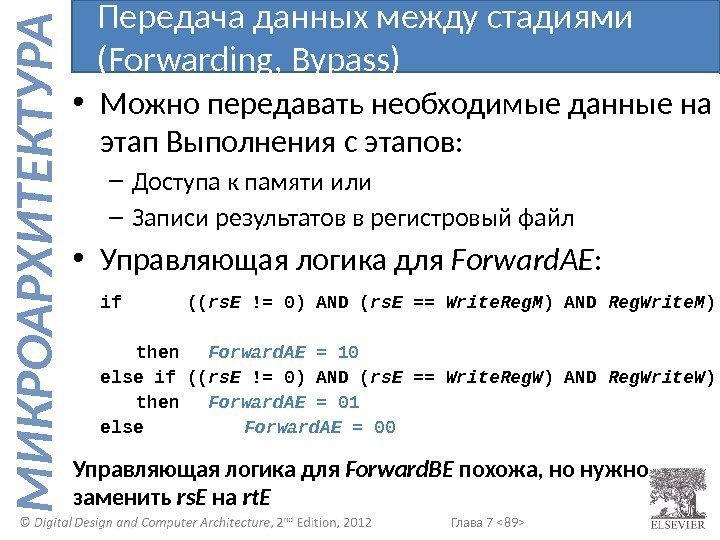

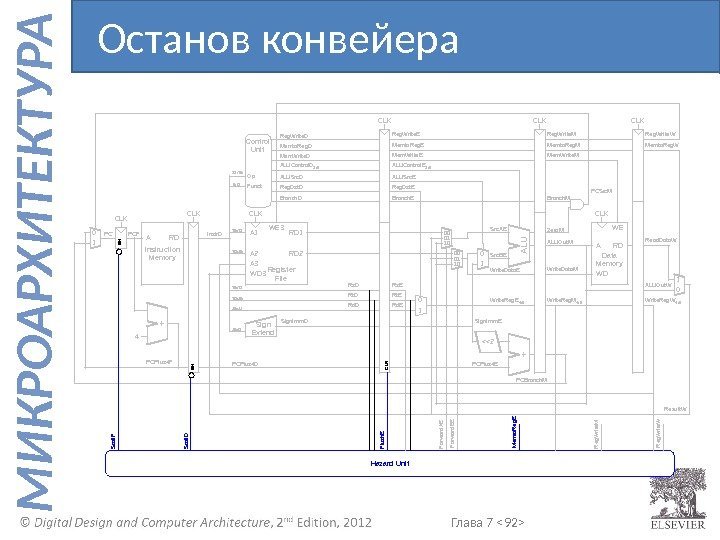

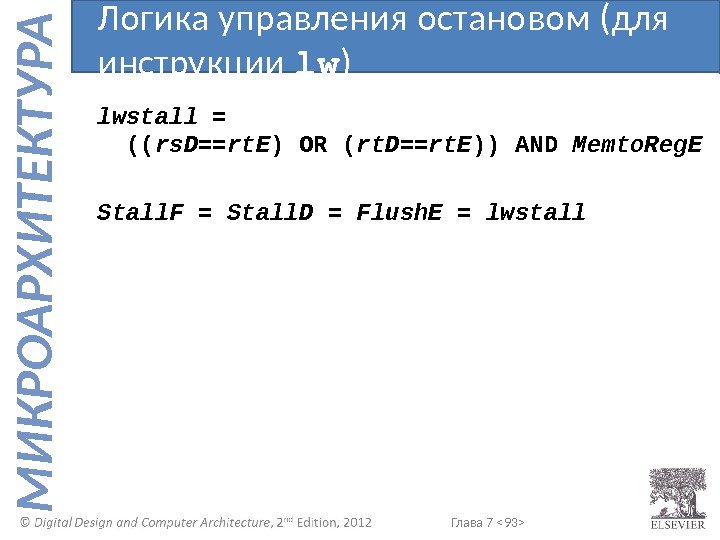

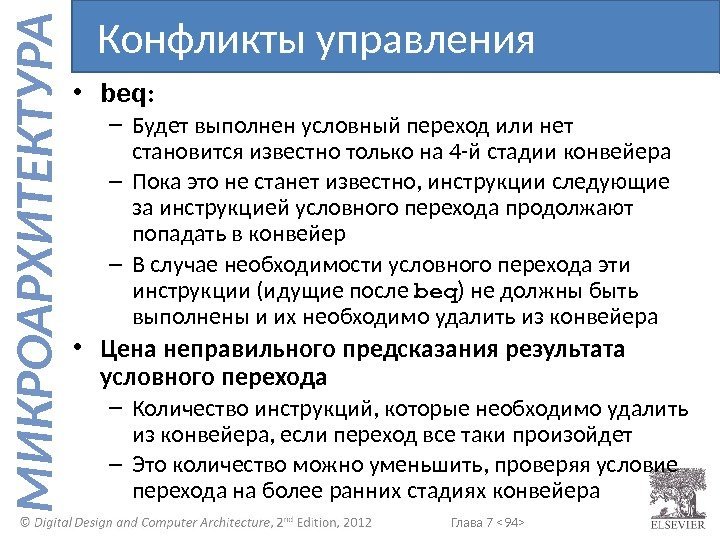

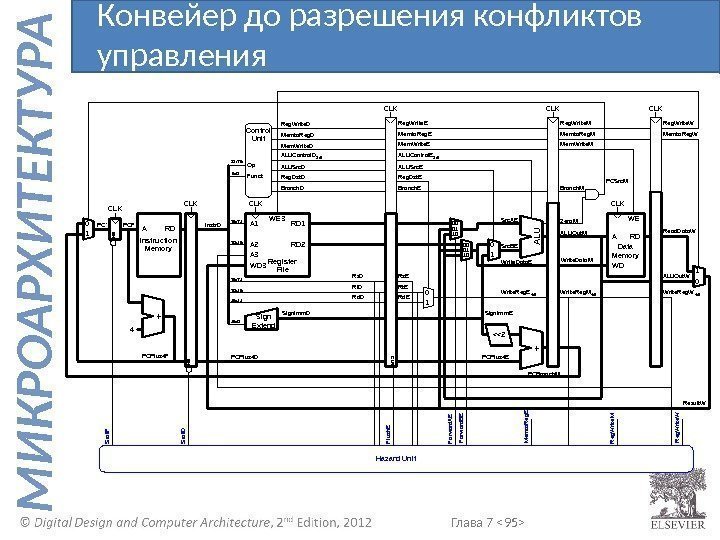

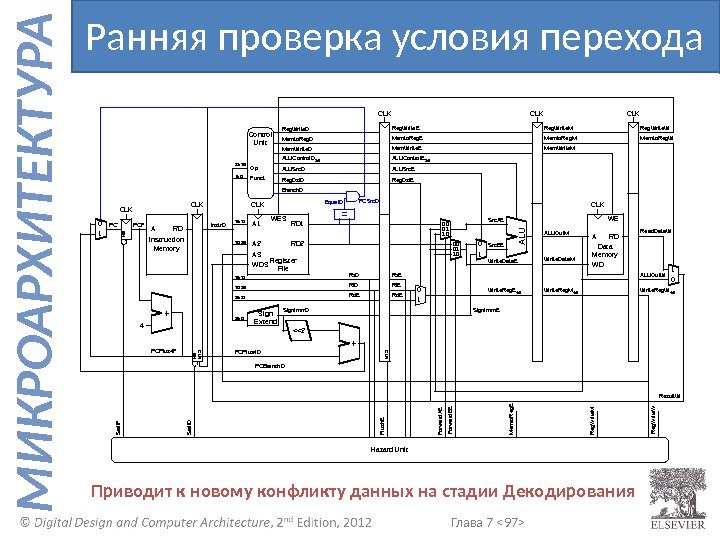

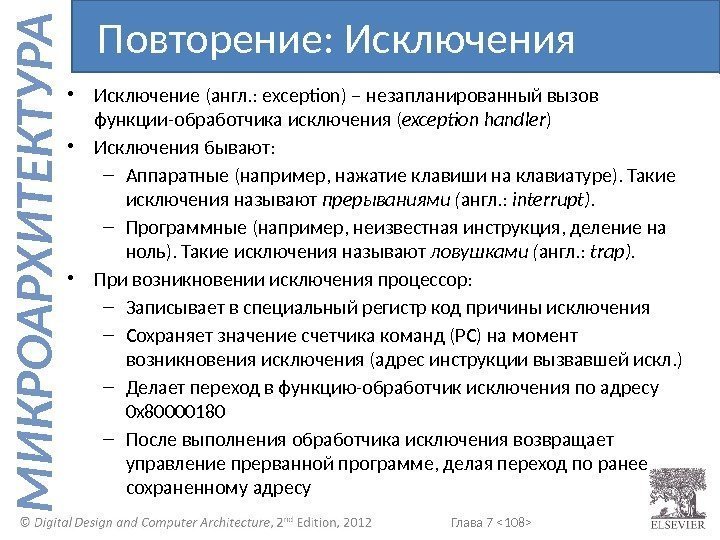

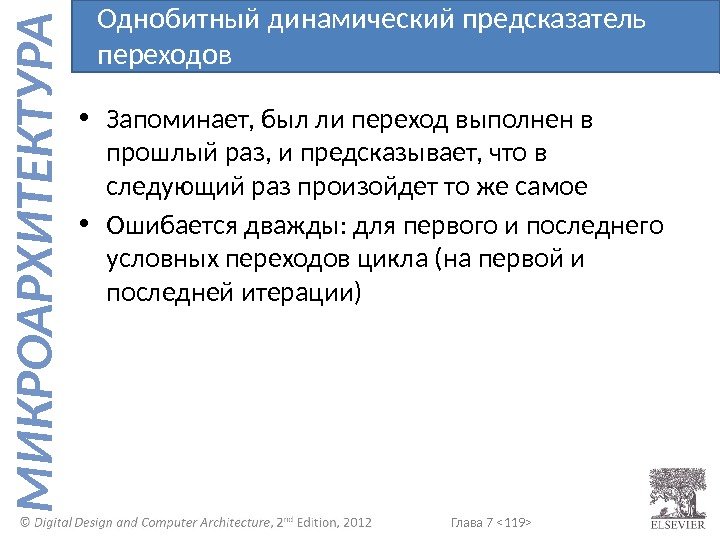

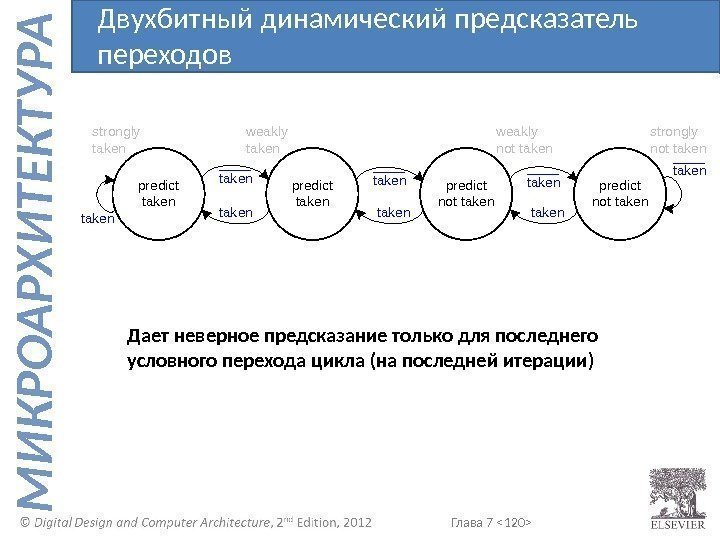

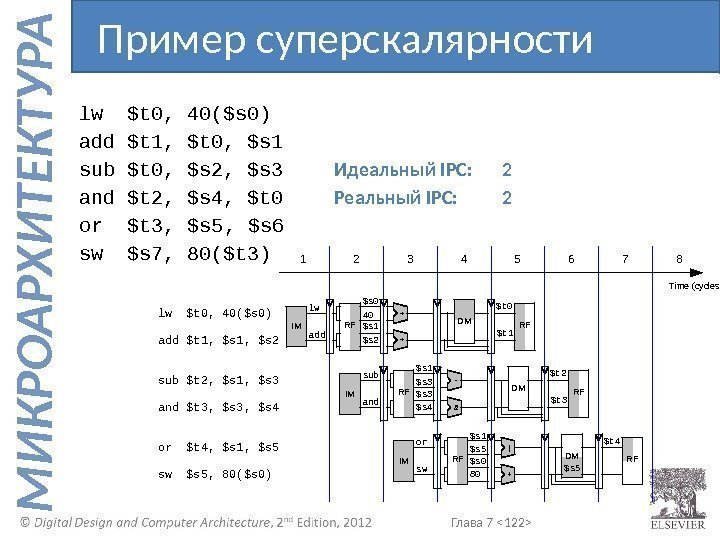

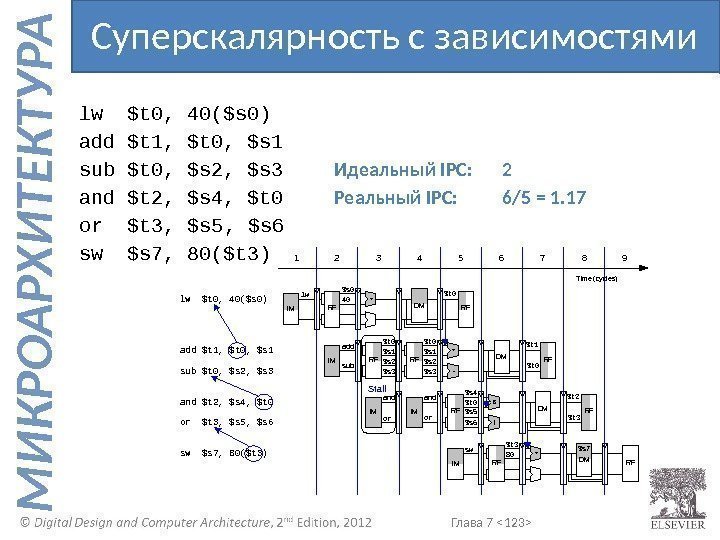

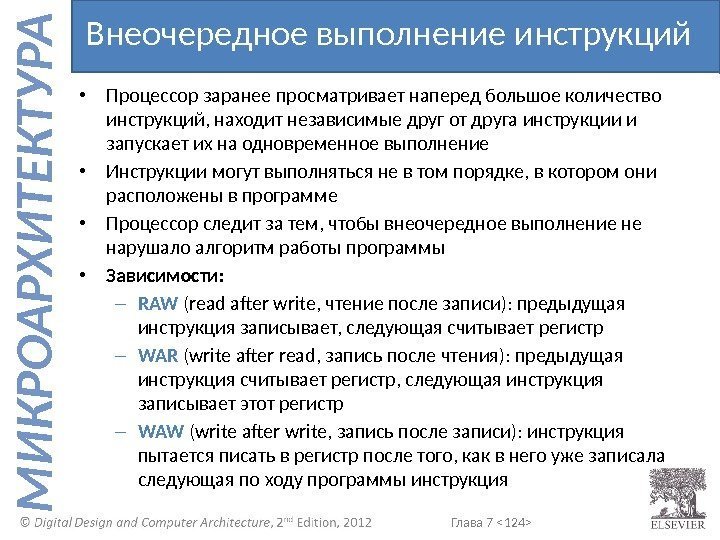

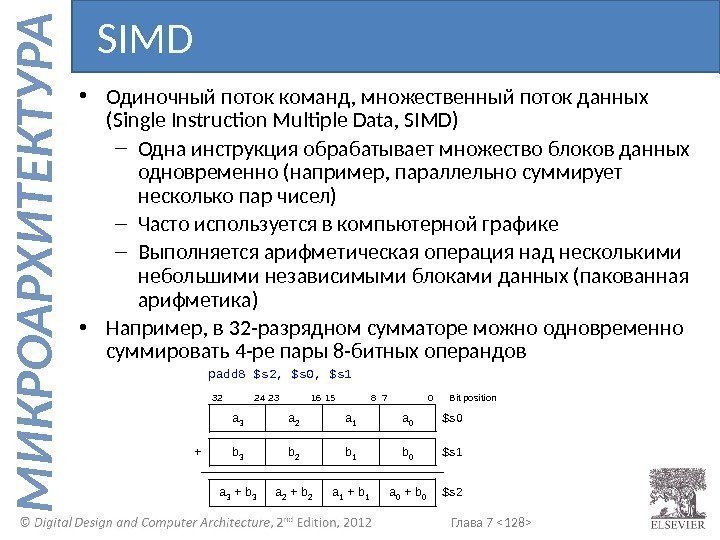

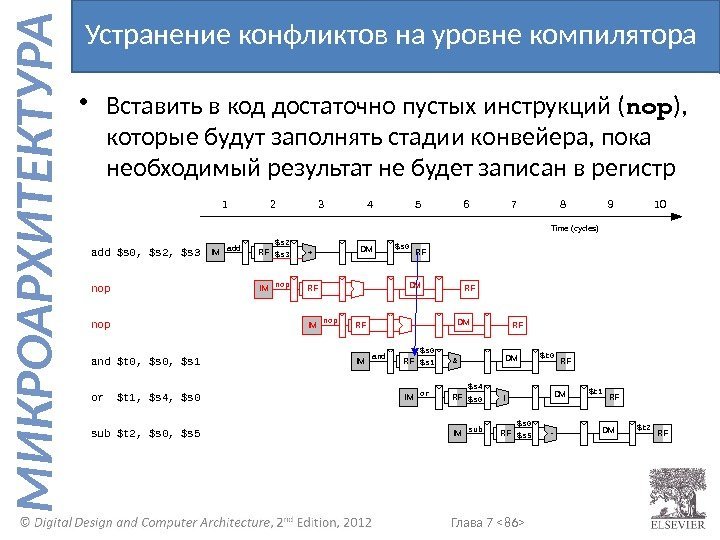

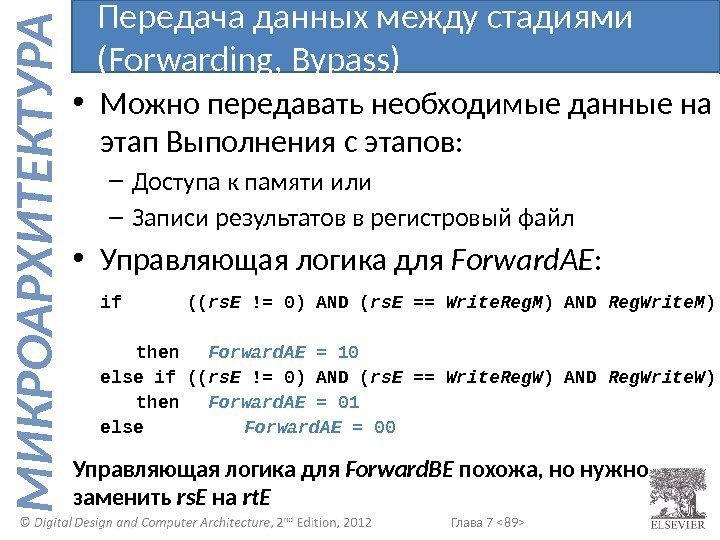

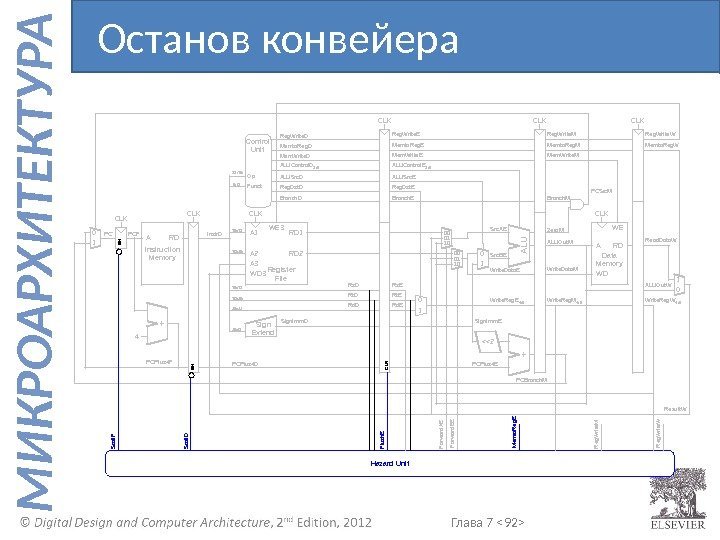

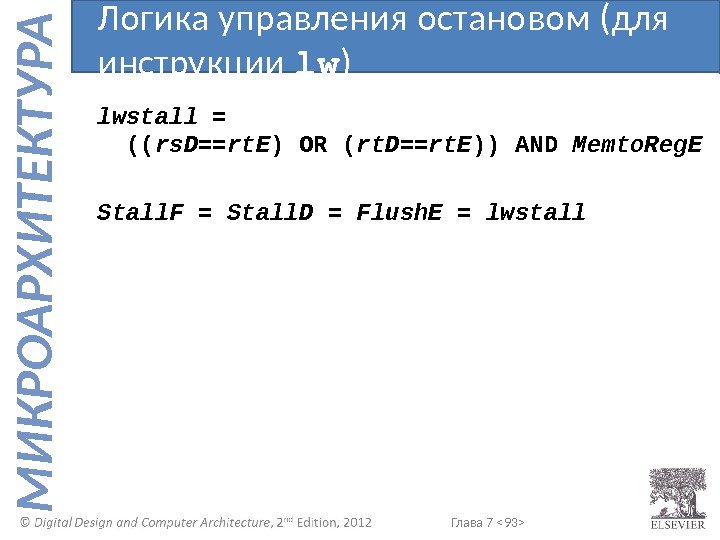

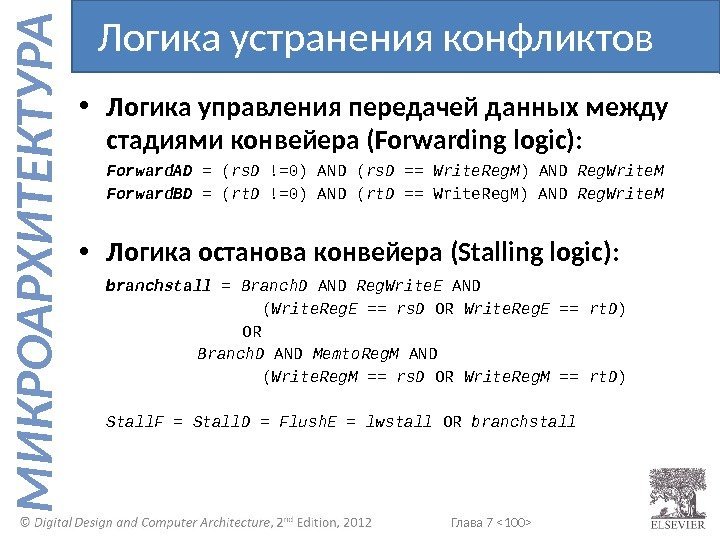

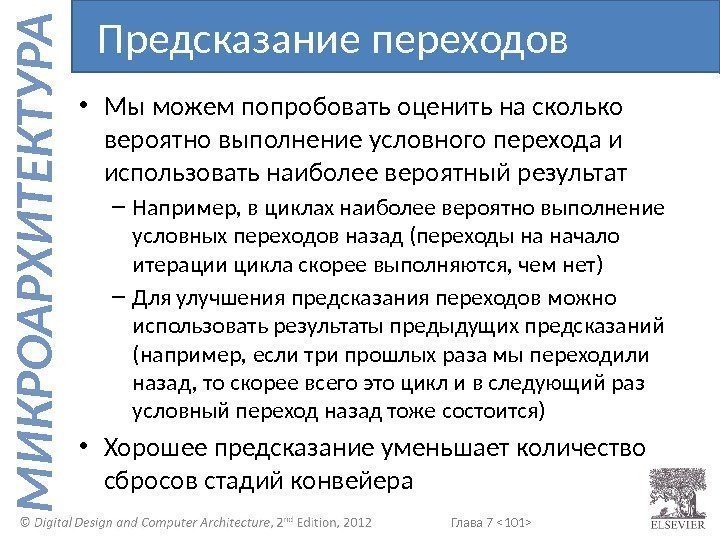

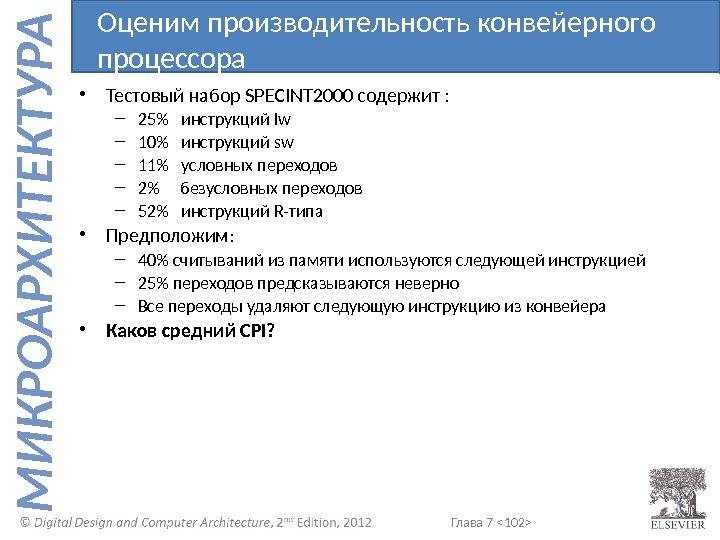

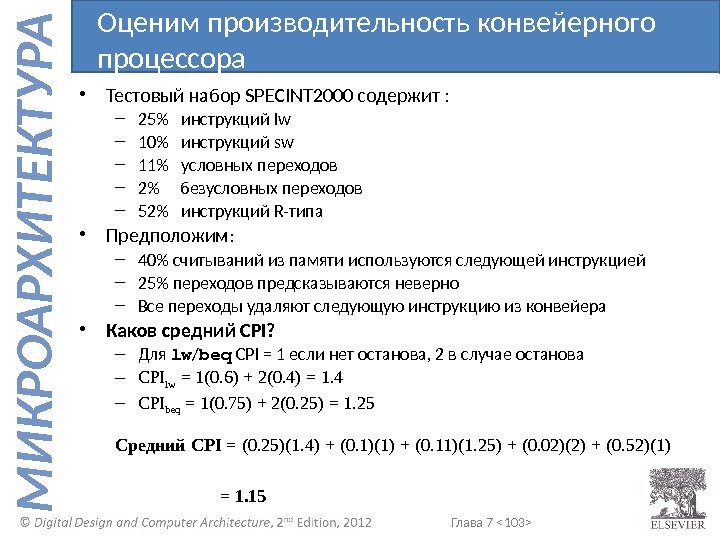

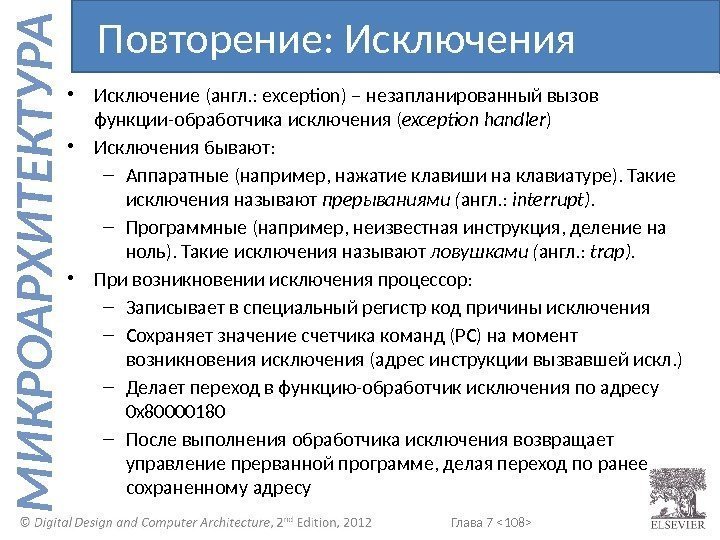

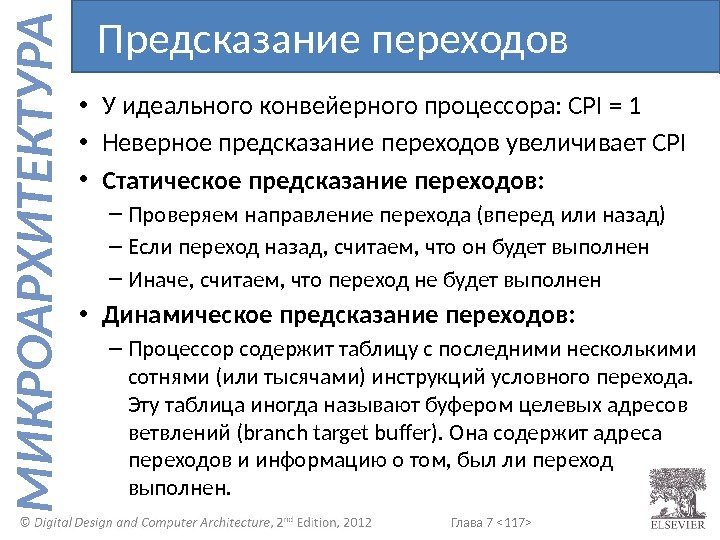

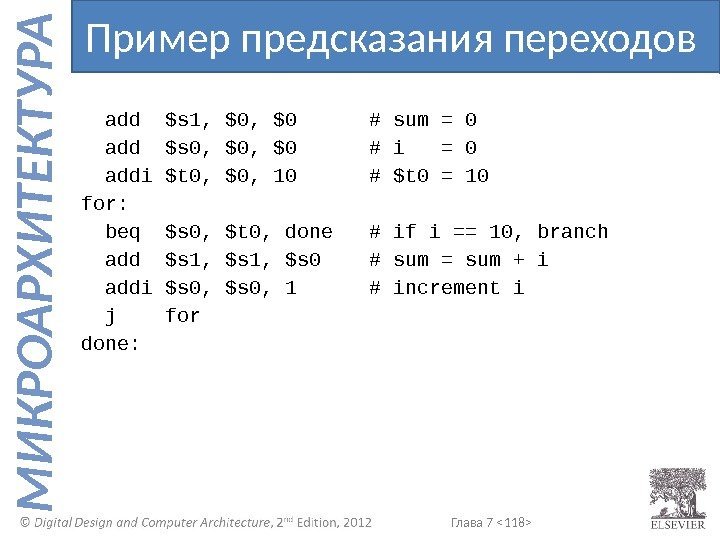

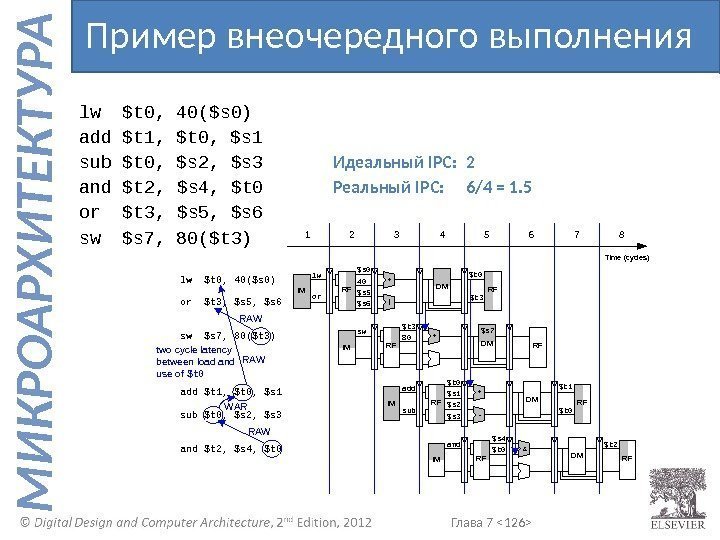

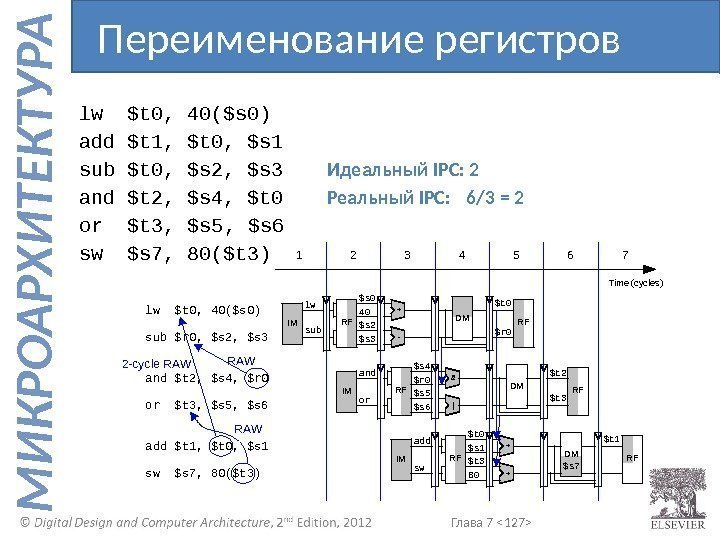

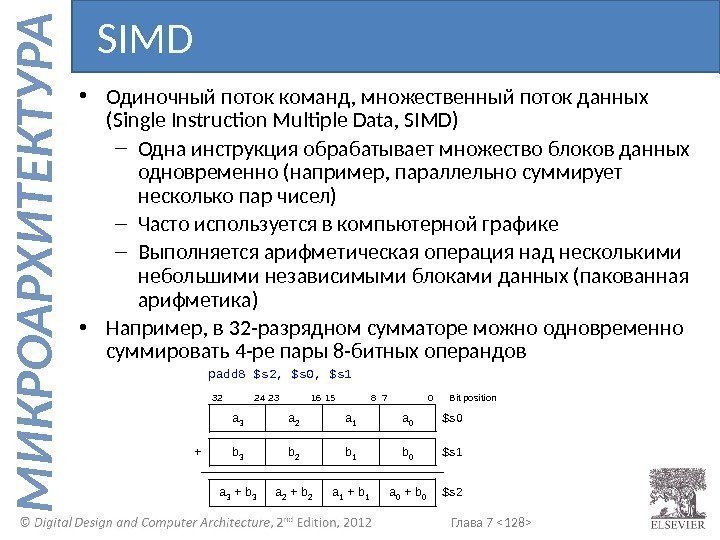

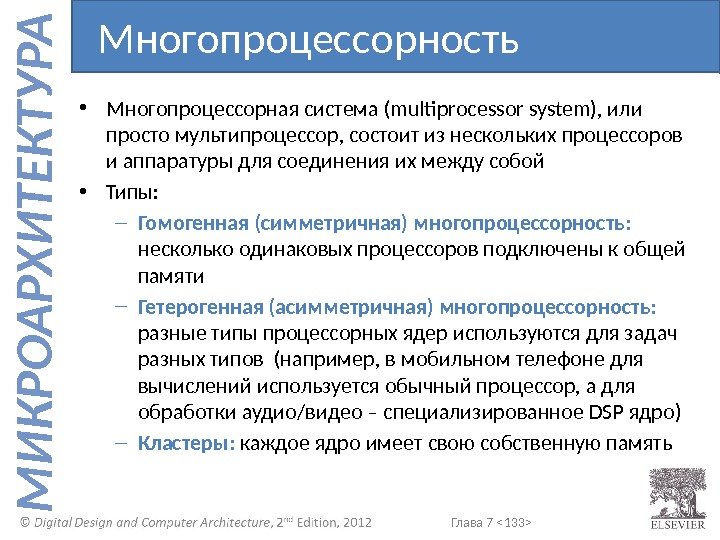

Глава 7 М И К Р О А Р Х И Т Е К Т У Р А • В конвейере выполняется несколько инструкций одновременно • Конфликты случаются когда одна инструкция зависит от результата другой, еще не завершенной инструкции • Типы конфликтов: – Конфликты данных: результат инструкции еще не записан в регистр, а следующая инструкция уже пытается считать этот регистр – Конфликты управления: процессор выбирает из памяти следующую инструкцию до того, как стало ясно, какую именно инструкцию надо выбрать(возникают из-за условных переходов)Конфликты конвейера