233327127df923315bf0abe907dfbb4f.ppt

- Количество слайдов: 35

Get the total Coverage ! ID 311 C: Utilizing JTAG / boundary scan and JTAG emulation for board and system level test and design verification GOEPEL Electronics Heiko Ehrenberg Managing Director NA Operations 12 October 2010 Version 1. 3

Get the total Coverage ! ID 311 C: Utilizing JTAG / boundary scan and JTAG emulation for board and system level test and design verification GOEPEL Electronics Heiko Ehrenberg Managing Director NA Operations 12 October 2010 Version 1. 3

Heiko Ehrenberg n Managing Director of North American Operations at GOEPEL Electronics LLC at Austin, TX l responsible for GOEPEL's operations in the USA, Canada, and Mexico l providing support and consulting services to North American clients l GOEPEL was founded in 1991 and has ~160 employees worldwide, active in JTAG/boundary scan, AOI, AXI, and Functional Test n Prior Experience: l Field Application Engineer for JTAG/boundary scan supporting GOEPEL customers in Germany and then Europe l BSEE from the University of Applied Sciences at Mittweida, Germany 2

Heiko Ehrenberg n Managing Director of North American Operations at GOEPEL Electronics LLC at Austin, TX l responsible for GOEPEL's operations in the USA, Canada, and Mexico l providing support and consulting services to North American clients l GOEPEL was founded in 1991 and has ~160 employees worldwide, active in JTAG/boundary scan, AOI, AXI, and Functional Test n Prior Experience: l Field Application Engineer for JTAG/boundary scan supporting GOEPEL customers in Germany and then Europe l BSEE from the University of Applied Sciences at Mittweida, Germany 2

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 3

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 3

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 4

Renesas Technology and Solution Portfolio Microcontrollers & Microprocessors #1 Market share worldwide * ASIC, ASSP & Memory Advanced and proven technologies Solutions for Innovation Analog and Power Devices #1 Market share in low-voltage MOSFET** * MCU: 31% revenue basis from Gartner "Semiconductor Applications Worldwide Annual Market Share: Database" 25 March 2010 ** Power MOSFET: 17. 1% on unit basis from Marketing Eye 2009 (17. 1% on unit basis). 4

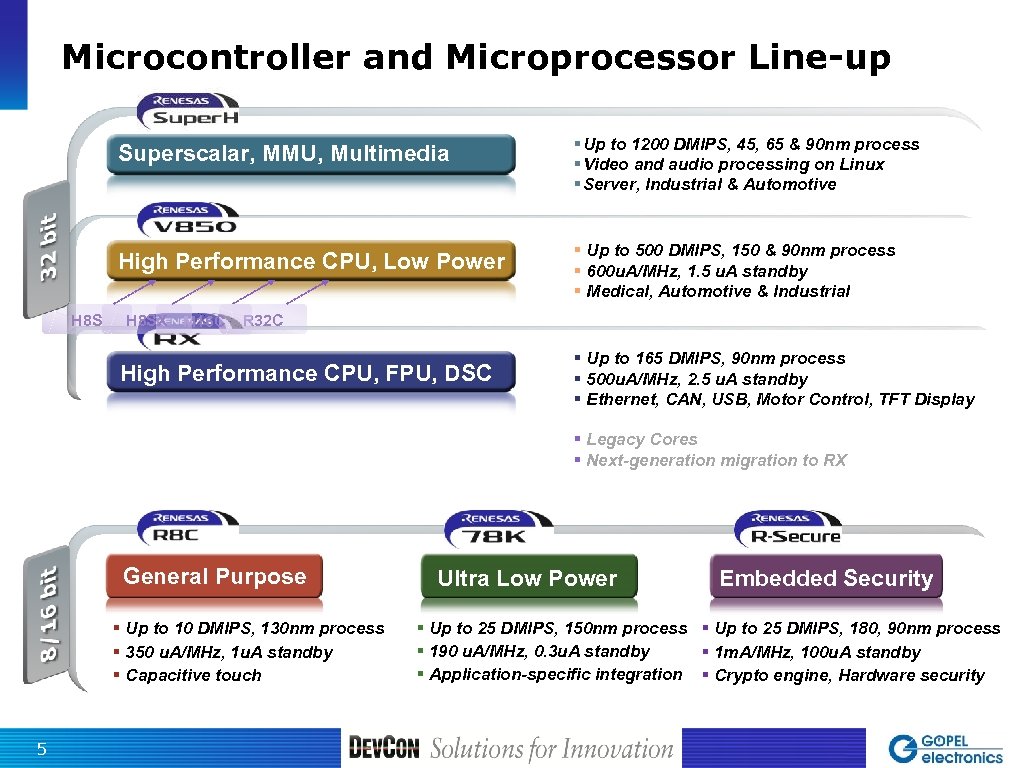

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia High Performance CPU, Low Power H 8 S § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial H 8 SX M 16 C R 32 C High Performance CPU, FPU, DSC § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX General Purpose § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 5 Ultra Low Power Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia High Performance CPU, Low Power H 8 S § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial H 8 SX M 16 C R 32 C High Performance CPU, FPU, DSC § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX General Purpose § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 5 Ultra Low Power Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia High Performance CPU, Low Power H 8 S § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial H 8 SX M 16 C High Performance CPU, FPU, DSC § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX JTAG / boundary scan and JTAG emulation for board and system level Generaltest and design verification Power Purpose Ultra Low § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 7 Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Microcontroller and Microprocessor Line-up Superscalar, MMU, Multimedia High Performance CPU, Low Power H 8 S § Up to 1200 DMIPS, 45, 65 & 90 nm process § Video and audio processing on Linux § Server, Industrial & Automotive § Up to 500 DMIPS, 150 & 90 nm process § 600 u. A/MHz, 1. 5 u. A standby § Medical, Automotive & Industrial H 8 SX M 16 C High Performance CPU, FPU, DSC § Up to 165 DMIPS, 90 nm process § 500 u. A/MHz, 2. 5 u. A standby § Ethernet, CAN, USB, Motor Control, TFT Display § Legacy Cores § Next-generation migration to RX JTAG / boundary scan and JTAG emulation for board and system level Generaltest and design verification Power Purpose Ultra Low § Up to 10 DMIPS, 130 nm process § 350 u. A/MHz, 1 u. A standby § Capacitive touch 7 Embedded Security § Up to 25 DMIPS, 150 nm process § Up to 25 DMIPS, 180, 90 nm process § 190 u. A/MHz, 0. 3 u. A standby § 1 m. A/MHz, 100 u. A standby § Application-specific integration § Crypto engine, Hardware security

Innovation Design verification and prototyping Manufacturing test and debug End of line (system) test Field service / warranty/repair On-Chip / In-Circuit Emulation IEEE 1149. x JTAG / boundary scan IEEE 1149. x Functional test IEEE 1149. x (JTAG / boundary scan) + On-Chip Emulation Functional test 8

Innovation Design verification and prototyping Manufacturing test and debug End of line (system) test Field service / warranty/repair On-Chip / In-Circuit Emulation IEEE 1149. x JTAG / boundary scan IEEE 1149. x Functional test IEEE 1149. x (JTAG / boundary scan) + On-Chip Emulation Functional test 8

Intelligent boundary scan solutions GOEPEL is a technology leader in JTAG / boundary scan – creating new, innovative ways to extend the reach of boundary scan beyond pure structural test applications. 9

Intelligent boundary scan solutions GOEPEL is a technology leader in JTAG / boundary scan – creating new, innovative ways to extend the reach of boundary scan beyond pure structural test applications. 9

Agenda n Benefits and limitations of IEEE Std. 1149. 1 for board level debug and test n Overview of board and system level JTAG/boundary scan applications n Utilization of On-Chip Emulation resources for board level connectivity test applications n Interlaced JTAG Emulation and boundary scan testing n Summary of fault coverage improvements and other benefits 10

Agenda n Benefits and limitations of IEEE Std. 1149. 1 for board level debug and test n Overview of board and system level JTAG/boundary scan applications n Utilization of On-Chip Emulation resources for board level connectivity test applications n Interlaced JTAG Emulation and boundary scan testing n Summary of fault coverage improvements and other benefits 10

Key Takeaways n By the end of this session you will be able to: l Identify potential board and system level test applications supported by JTAG/boundary scan on specific board/system designs; l Discuss potential test strategies involving JTAG/boundary scan with test engineering / production test groups 11

Key Takeaways n By the end of this session you will be able to: l Identify potential board and system level test applications supported by JTAG/boundary scan on specific board/system designs; l Discuss potential test strategies involving JTAG/boundary scan with test engineering / production test groups 11

JTAG / boundary scan in a nutshell 12

JTAG / boundary scan in a nutshell 12

Boundary scan test applications R AND Gates Bi-Dir Buffer R SRAM Digital Core Logic /TRST TDI TCK TMS TDO 13 R ID Reg R IR B P TAP Controller Digital Core Logic /TRST TDI TDO TCK TMS ID Reg IR B P TAP Controller TDO

Boundary scan test applications R AND Gates Bi-Dir Buffer R SRAM Digital Core Logic /TRST TDI TCK TMS TDO 13 R ID Reg R IR B P TAP Controller Digital Core Logic /TRST TDI TDO TCK TMS ID Reg IR B P TAP Controller TDO

JTAG / boundary scan limitations. . . n Strictly digital test access (exception: IEEE 1149. 4) n Quasi-static tests (low I/O toggle rate), limited dynamic test capabilities (exception: BIST) n Test access determined by BScan capabilities implemented in devices on the UUT n BScan test coverage could be improved: l if test points or connector pins are accessed with Tester I/O l by accessing analog circuitry with Tester resources l by utilizing On-Chip Emulation and Tester resources for dynamic, quasi-functional tests 14

JTAG / boundary scan limitations. . . n Strictly digital test access (exception: IEEE 1149. 4) n Quasi-static tests (low I/O toggle rate), limited dynamic test capabilities (exception: BIST) n Test access determined by BScan capabilities implemented in devices on the UUT n BScan test coverage could be improved: l if test points or connector pins are accessed with Tester I/O l by accessing analog circuitry with Tester resources l by utilizing On-Chip Emulation and Tester resources for dynamic, quasi-functional tests 14

Boundary scan vs. ✓ Structural Test ✓ Efficient ATPG tools ✓ Pin Level Diagnostics ✓ In-System Test / - Programming Flash programming inefficiencies Limits in dynamic test Complexity of cluster tests Need for BScan Register Emulation ✓ Functional Test ✓ Fault Coverage ✓ At-Speed Test ✓ FLASH programming speed - µP/µC specific pods - Limited ATPG - Quality of diagnostics - Limited In-System Test / Programming How to get the best of both worlds? 15

Boundary scan vs. ✓ Structural Test ✓ Efficient ATPG tools ✓ Pin Level Diagnostics ✓ In-System Test / - Programming Flash programming inefficiencies Limits in dynamic test Complexity of cluster tests Need for BScan Register Emulation ✓ Functional Test ✓ Fault Coverage ✓ At-Speed Test ✓ FLASH programming speed - µP/µC specific pods - Limited ATPG - Quality of diagnostics - Limited In-System Test / Programming How to get the best of both worlds? 15

Vario. TAP ✓ Structural Test ✓ Efficient ATPG tools ✓ Pin Level Diagnostics ✓ In-System Test / - Programming Flash programming inefficiencies Limits in dynamic test Complexity of cluster tests Need for BScan Register ✓ Functional Test ✓ Fault Coverage ✓ At-Speed Test ✓ FLASH programming speed - µP/µC specific pods - Limited ATPG - Quality of diagnostics - Limited In-System Test / Programming On-Chip Programming + Interlaced Emulation Test 16

Vario. TAP ✓ Structural Test ✓ Efficient ATPG tools ✓ Pin Level Diagnostics ✓ In-System Test / - Programming Flash programming inefficiencies Limits in dynamic test Complexity of cluster tests Need for BScan Register ✓ Functional Test ✓ Fault Coverage ✓ At-Speed Test ✓ FLASH programming speed - µP/µC specific pods - Limited ATPG - Quality of diagnostics - Limited In-System Test / Programming On-Chip Programming + Interlaced Emulation Test 16

Classification of boundary scan applications 17

Classification of boundary scan applications 17

Utilization of On-Chip Emulation resources for board level connectivity test applications 18

Utilization of On-Chip Emulation resources for board level connectivity test applications 18

Emulation Test Generic μP / MCU / CPU model (On-Chip Resources) JTAG PCI Express, CAN, LIN, Flexray, Blue. Tooth, WLAN, USB, LAN, RS 232, . . . Bus IF Type A Flash Analog I/O Bus IF Type X Core Digital I/O Internal Circuits System Bus IF Audio, Video, Legacy analog, Legacy digital, PWM signals, I 2 C, SPI, μW, . . . Mixed I/O On-Board Resources: DRAM, External Periphery, Bridges, etc. Application Type A: Programming Functions for On-Chip or external Flash 19 Application Type B: Bus Control Functions for Bus Emulation Test Application Type C: Test Functions for On-Chip Resources

Emulation Test Generic μP / MCU / CPU model (On-Chip Resources) JTAG PCI Express, CAN, LIN, Flexray, Blue. Tooth, WLAN, USB, LAN, RS 232, . . . Bus IF Type A Flash Analog I/O Bus IF Type X Core Digital I/O Internal Circuits System Bus IF Audio, Video, Legacy analog, Legacy digital, PWM signals, I 2 C, SPI, μW, . . . Mixed I/O On-Board Resources: DRAM, External Periphery, Bridges, etc. Application Type A: Programming Functions for On-Chip or external Flash 19 Application Type B: Bus Control Functions for Bus Emulation Test Application Type C: Test Functions for On-Chip Resources

Flash ISP TAP JTAG Bus IF Type A PHY Bus IF Type X Core Digital I/O Internal Circuits System Bus IF Mixed I/O Analog I/O JTAG Flash Signal Conditioning PHY Standard I/O 20 Bridge Standard I/FLASH Flash Standard I/RAM RAM Standard I/I/O I/O

Flash ISP TAP JTAG Bus IF Type A PHY Bus IF Type X Core Digital I/O Internal Circuits System Bus IF Mixed I/O Analog I/O JTAG Flash Signal Conditioning PHY Standard I/O 20 Bridge Standard I/FLASH Flash Standard I/RAM RAM Standard I/I/O I/O

Bus Emulation Test TAP JTAG Analog I/O Digital I/O System Bus IF Mixed I/O JTAG Signal Conditioning Core Flash Standard I/O Bridge Standard I/FLASH Flash Standard I/RAM RAM Standard I/I/O I/O External Tester Channels Bus IF Type X Internal Circuits 21 Bus IF Type A PHY TAP PHY

Bus Emulation Test TAP JTAG Analog I/O Digital I/O System Bus IF Mixed I/O JTAG Signal Conditioning Core Flash Standard I/O Bridge Standard I/FLASH Flash Standard I/RAM RAM Standard I/I/O I/O External Tester Channels Bus IF Type X Internal Circuits 21 Bus IF Type A PHY TAP PHY

System Emulation Test TAP JTAG Analog I/O Bus IF Type X Core Digital I/O System Bus IF Mixed I/O External Tester Channels PHY FLASH Standard I/O Bridge Standard I/FLASH Standard I/RAM RAM Standard I/I/O I/O External Tester Channels JTAG TAP External Tester Channels Bus IF Type A Internal Circuits 22 PHY Signal Conditioning External Tester Channels JTAG

System Emulation Test TAP JTAG Analog I/O Bus IF Type X Core Digital I/O System Bus IF Mixed I/O External Tester Channels PHY FLASH Standard I/O Bridge Standard I/FLASH Standard I/RAM RAM Standard I/I/O I/O External Tester Channels JTAG TAP External Tester Channels Bus IF Type A Internal Circuits 22 PHY Signal Conditioning External Tester Channels JTAG

Vario. TAP application development Emulation Tool suite for Flash ISP and Testing CASLAN Source code Bscan instruction Vario. TAP Instruction Bscan Instruction Compiler Available Vario. TAP Commands Device Model #1 -- Register descriptions -- Port descriptions Device -- ……. Model #2 -- Register descriptions -- Port descriptions Device Model #n (µP) -- ……. -- Register descriptions -- Vario. TAP Model -- Port descriptions -- … -- Vario. TAP Model(s) Selected Device Library Executable SYSTEM CASCON™ Environment n µP/µC specific models are the key for Vario. TAP n Access to Vario. TAP functions via CASLAN (high-level commands) 23

Vario. TAP application development Emulation Tool suite for Flash ISP and Testing CASLAN Source code Bscan instruction Vario. TAP Instruction Bscan Instruction Compiler Available Vario. TAP Commands Device Model #1 -- Register descriptions -- Port descriptions Device -- ……. Model #2 -- Register descriptions -- Port descriptions Device Model #n (µP) -- ……. -- Register descriptions -- Vario. TAP Model -- Port descriptions -- … -- Vario. TAP Model(s) Selected Device Library Executable SYSTEM CASCON™ Environment n µP/µC specific models are the key for Vario. TAP n Access to Vario. TAP functions via CASLAN (high-level commands) 23

Vario. TAP applications n n n n Test of Digital I/O Test of Analog / Mixed-Signal I/O Fast external Flash Programming On-Chip Flash Programming Test of Bus Interfaces Test of Peripheral Circuitry Dynamic Memory Access Tests Customer specific Tests n Unique: Interlaced utilization of emulation resources and boundary scan resources 24

Vario. TAP applications n n n n Test of Digital I/O Test of Analog / Mixed-Signal I/O Fast external Flash Programming On-Chip Flash Programming Test of Bus Interfaces Test of Peripheral Circuitry Dynamic Memory Access Tests Customer specific Tests n Unique: Interlaced utilization of emulation resources and boundary scan resources 24

Fault coverage improvements and other benefits n Boundary scan provides: l Embedded test access l Deterministic test coverage l Very good diagnostics n JTAG (on-chip) emulation provides: l Dynamic fault coverage l Verification of circuit functions 25

Fault coverage improvements and other benefits n Boundary scan provides: l Embedded test access l Deterministic test coverage l Very good diagnostics n JTAG (on-chip) emulation provides: l Dynamic fault coverage l Verification of circuit functions 25

Fault coverage improvements and other benefits n Vario. TAP combines boundary scan and on-chip emulation to provide: l JTAG controlled functional tests l Interlaced boundary scan and on-chip emulation tests for extended connectivity tests l Automated test generation and deterministic test coverage for (functional) on-chip emulation tests 26

Fault coverage improvements and other benefits n Vario. TAP combines boundary scan and on-chip emulation to provide: l JTAG controlled functional tests l Interlaced boundary scan and on-chip emulation tests for extended connectivity tests l Automated test generation and deterministic test coverage for (functional) on-chip emulation tests 26

Questions? 27

Questions? 27

Question 1 n Is there a standard defining JTAG / boundary scan resources? If so, which standard? l Yes: IEEE 1149. 1 l Also: IEEE 1149. 4, IEEE 1149. 6, IEEE 1149. 7 28

Question 1 n Is there a standard defining JTAG / boundary scan resources? If so, which standard? l Yes: IEEE 1149. 1 l Also: IEEE 1149. 4, IEEE 1149. 6, IEEE 1149. 7 28

Question 2 n Name potential board and system level test applications supported by JTAG / boundary scan. l Infrastructure test l Interconnect test l Memory access (cluster) test l Logic cluster test l In-system programming for Flash, s. EEPROM, CPLD l … 29

Question 2 n Name potential board and system level test applications supported by JTAG / boundary scan. l Infrastructure test l Interconnect test l Memory access (cluster) test l Logic cluster test l In-system programming for Flash, s. EEPROM, CPLD l … 29

Question 3 n What is one of the most important printed circuit board level “design for test” requirements enabling the utilization of boundary scan capabilities implemented in integrated circuits? l Implement a boundary scan chain ! Make the TAP accessible. l Allow Compliance enable pattern to be satisfied to enable JTAG / boundary scan compliance. 30

Question 3 n What is one of the most important printed circuit board level “design for test” requirements enabling the utilization of boundary scan capabilities implemented in integrated circuits? l Implement a boundary scan chain ! Make the TAP accessible. l Allow Compliance enable pattern to be satisfied to enable JTAG / boundary scan compliance. 30

Feedback Form n Please fill out the feedback form! l. If you do not have one, please raise your hand 31

Feedback Form n Please fill out the feedback form! l. If you do not have one, please raise your hand 31

Thank You! 32

Thank You! 32

Contact information n. For further information, please: Visit our website at www. goepelusa. com Contact your local sales representative Call us at 1 -888 -4 GOEPEL Email us at sales@goepelusa. com 33

Contact information n. For further information, please: Visit our website at www. goepelusa. com Contact your local sales representative Call us at 1 -888 -4 GOEPEL Email us at sales@goepelusa. com 33

Appendix 34

Appendix 34

References and tools n White Paper: “Combining Boundary Scan and JTAG Emulation for advanced structural Test and Diagnostics” n Boundary Scan Coach: l software tool demonstrating the key principles of JTAG / boundary scan as defined in IEEE 1149. 1 n BSDL Syntax Checker: l software for verification of BSDL syntax and semantics n TAP Checker: l software for validation of JTAG / boundary scan implementations in integrated circuits n CASCON GALAXY: l software for device, board, and system level JTAG / boundary scan test and emulation applications 35

References and tools n White Paper: “Combining Boundary Scan and JTAG Emulation for advanced structural Test and Diagnostics” n Boundary Scan Coach: l software tool demonstrating the key principles of JTAG / boundary scan as defined in IEEE 1149. 1 n BSDL Syntax Checker: l software for verification of BSDL syntax and semantics n TAP Checker: l software for validation of JTAG / boundary scan implementations in integrated circuits n CASCON GALAXY: l software for device, board, and system level JTAG / boundary scan test and emulation applications 35