f0465aa1b0526b496ebb6abd8a6364c7.ppt

- Количество слайдов: 42

FUNDAMENTOS DA COMPUTAÇÃO Aula 3 – Parte 2 Instrutor. : Frank S. Fernandes Bastos (frank. bastos@gmail. com) Foco. : Adiquirir conhecimento preparatório para Concurso referente itens complementares sobre fundamentos Público. : Estudantes de concurso específico Local. : Sala de aula - Obcursos Número Slides. : 20 (incluindo este)

FUNDAMENTOS DA COMPUTAÇÃO Aula 3 – Parte 2 Instrutor. : Frank S. Fernandes Bastos (frank. bastos@gmail. com) Foco. : Adiquirir conhecimento preparatório para Concurso referente itens complementares sobre fundamentos Público. : Estudantes de concurso específico Local. : Sala de aula - Obcursos Número Slides. : 20 (incluindo este)

OBJETIVOS Adquirir conhecimentos complementares sobre os fundamentos relativo a arquitetura de computadores.

OBJETIVOS Adquirir conhecimentos complementares sobre os fundamentos relativo a arquitetura de computadores.

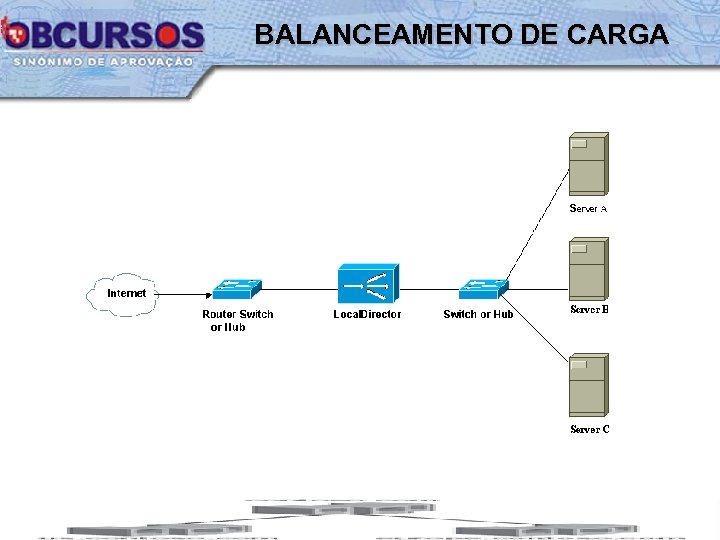

BALANCEAMENTO DE CARGA

BALANCEAMENTO DE CARGA

PERSISTÊNCIA Sessão 1 Sessão 2 Sessão 3 Cliente INTERNET Sessão 4

PERSISTÊNCIA Sessão 1 Sessão 2 Sessão 3 Cliente INTERNET Sessão 4

Formas de acesso ao Cache ■ Hit - dado encontrado no nível procurado. ■ Miss - dado não encontrado no nível procurado. ■ Hit-rate (ratio) - percentual de hits no nível. ■ Miss-rate (ratio) – percentual de misses no nível. É complementar ao hit-rate. ■ Hit-time – tempo de acesso ao nível incluindo tempo de ver se é hit ou miss. ■ Miss-penalty – tempo médio gasto para que o dado não encontrado no nível desejado seja transferido dos níveis mais baixos.

Formas de acesso ao Cache ■ Hit - dado encontrado no nível procurado. ■ Miss - dado não encontrado no nível procurado. ■ Hit-rate (ratio) - percentual de hits no nível. ■ Miss-rate (ratio) – percentual de misses no nível. É complementar ao hit-rate. ■ Hit-time – tempo de acesso ao nível incluindo tempo de ver se é hit ou miss. ■ Miss-penalty – tempo médio gasto para que o dado não encontrado no nível desejado seja transferido dos níveis mais baixos.

Formas de acesso ao Cache ■ Cálculo do tempo médio (tme) efetivo de acesso a uma memória cache considerando: Hit-ratio = 80% Hit-time = 2 ns Miss-penalty = 10 ns ■ Tme = hit-time + (1 – hit-rate) * miss-penalty

Formas de acesso ao Cache ■ Cálculo do tempo médio (tme) efetivo de acesso a uma memória cache considerando: Hit-ratio = 80% Hit-time = 2 ns Miss-penalty = 10 ns ■ Tme = hit-time + (1 – hit-rate) * miss-penalty

Problemas no acesso ao Cache Como a cache só pode conter parte dos dados por causa de seu tamanho, tem-se dois problemas: Como identificar se o dado procurado está na cache; ele estiver na cache, como acessá-lo de forma rápida. Se ■ A solução é fazer o mapaemento de endereços

Problemas no acesso ao Cache Como a cache só pode conter parte dos dados por causa de seu tamanho, tem-se dois problemas: Como identificar se o dado procurado está na cache; ele estiver na cache, como acessá-lo de forma rápida. Se ■ A solução é fazer o mapaemento de endereços

Mapeamento do Cache O termo mapeamento é usado para indicar o relacionamento dos dados do nível inferior com as posições da memória cache ■ Existem três tipos de mapeamento. : Direto Associativo Conjuntivo associativo

Mapeamento do Cache O termo mapeamento é usado para indicar o relacionamento dos dados do nível inferior com as posições da memória cache ■ Existem três tipos de mapeamento. : Direto Associativo Conjuntivo associativo

Mapeamento direto É a forma mais simples de mapeamento; Cada bloco na memória principal é mapeado em uma linha da cache; Este mapeamento é dado diretamente através de uma operação no endereço que se está procurando; Exemplo: Para uma cache de 8 posições e uma memória de 32 endereços teríamos palavras de 4 bits. Cada posição da cache pode ter 4 posições da memória 3 bits menos significativos são usados para indexar os Os blocos (log 2(8))

Mapeamento direto É a forma mais simples de mapeamento; Cada bloco na memória principal é mapeado em uma linha da cache; Este mapeamento é dado diretamente através de uma operação no endereço que se está procurando; Exemplo: Para uma cache de 8 posições e uma memória de 32 endereços teríamos palavras de 4 bits. Cada posição da cache pode ter 4 posições da memória 3 bits menos significativos são usados para indexar os Os blocos (log 2(8))

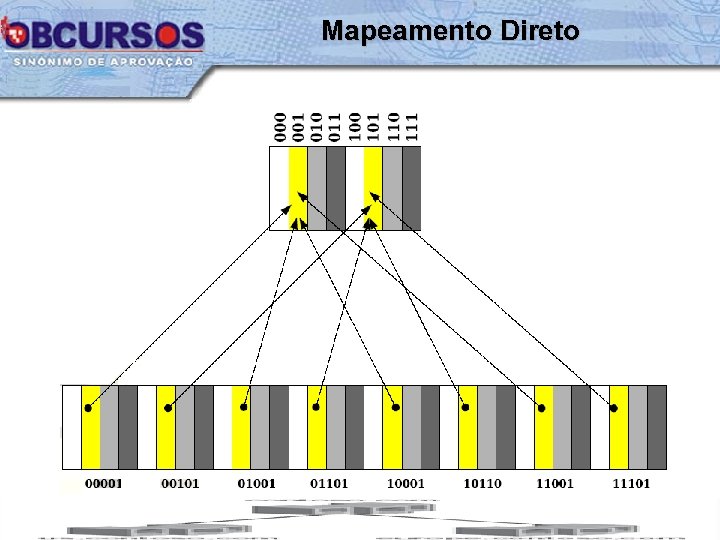

Mapeamento Direto

Mapeamento Direto

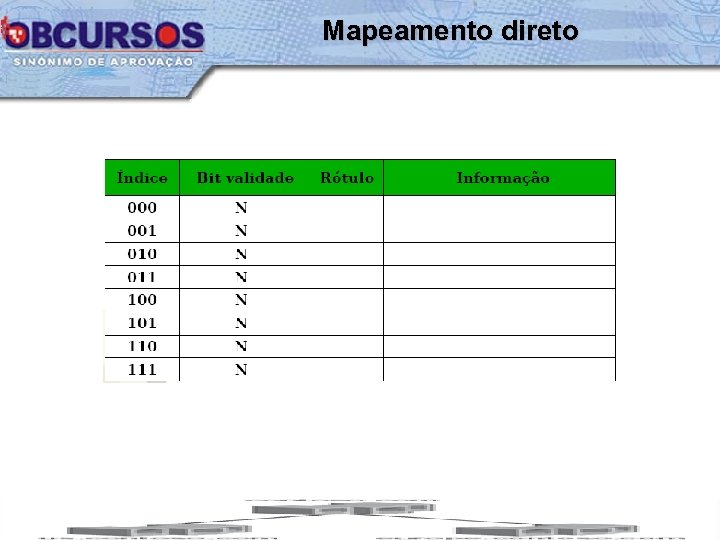

Mapeamento direto Etapas do reconhecimento e recebimento do dato. • Identificação por rótulos, contidos nos bits que não estão sendo utilizados nos índices da cache, possui 2 bits já que dos 5 bits totais, 3 bits são usados para o índice. • Saber se o dado do bloco, realmente corresponde ao dado solicitado e também se ele existe. Nesse caso utiliza-se um bit de validade. • Se o bit for zero, não há necessidade de comparação de rotulos.

Mapeamento direto Etapas do reconhecimento e recebimento do dato. • Identificação por rótulos, contidos nos bits que não estão sendo utilizados nos índices da cache, possui 2 bits já que dos 5 bits totais, 3 bits são usados para o índice. • Saber se o dado do bloco, realmente corresponde ao dado solicitado e também se ele existe. Nesse caso utiliza-se um bit de validade. • Se o bit for zero, não há necessidade de comparação de rotulos.

Mapeamento direto

Mapeamento direto

Mapeamento associativo Caracteriza-se por um bloco da memória principal poder ser colocado em qualquer posição da cache, ou seja, um bloco de memória pode ser associado a qualquer entrada da cache. produz 100% de aproveitamento da cache; Isso Consequentemente é preciso: ➔ Pesquisar todas as entradas da cache para encontrar um determinado bloco, uma vez que tal bloco pode estar em qualquer lugar da cache. ➔ Política de substituição, quando se tem falta (miss), a cache está cheia e é preciso tirar alguém.

Mapeamento associativo Caracteriza-se por um bloco da memória principal poder ser colocado em qualquer posição da cache, ou seja, um bloco de memória pode ser associado a qualquer entrada da cache. produz 100% de aproveitamento da cache; Isso Consequentemente é preciso: ➔ Pesquisar todas as entradas da cache para encontrar um determinado bloco, uma vez que tal bloco pode estar em qualquer lugar da cache. ➔ Política de substituição, quando se tem falta (miss), a cache está cheia e é preciso tirar alguém.

Desvantagem do Mapeamento associativo A solução para tornar a pesquisa rápida, é fazê-la em paralelo com um comparador associado (hardware) a cada uma das entradas da cache. comparadores aumentam o custo de hardware, o que torna o Tais mapeamento associativo idéal somente para pequenas caches, com capacidade para armazenar um pequeno número de blocos.

Desvantagem do Mapeamento associativo A solução para tornar a pesquisa rápida, é fazê-la em paralelo com um comparador associado (hardware) a cada uma das entradas da cache. comparadores aumentam o custo de hardware, o que torna o Tais mapeamento associativo idéal somente para pequenas caches, com capacidade para armazenar um pequeno número de blocos.

Mapeamento associativo Já a solução para substituição pode ser: ➔ Randômica: escolher aleatoriamente uma posição a ser substituída ➔ LFU (Least Frequent Used): a posição da cache que foi usada menos vezes será substituída. É preciso incrementa um contador a cada acesso e comparação para escolha; ➔ LRU (Least Recent Used): a posição da cache que foi usada a mais tempo será substituída. É preciso incrementar um contador a cada acesso e comparação para escolha.

Mapeamento associativo Já a solução para substituição pode ser: ➔ Randômica: escolher aleatoriamente uma posição a ser substituída ➔ LFU (Least Frequent Used): a posição da cache que foi usada menos vezes será substituída. É preciso incrementa um contador a cada acesso e comparação para escolha; ➔ LRU (Least Recent Used): a posição da cache que foi usada a mais tempo será substituída. É preciso incrementar um contador a cada acesso e comparação para escolha.

Mapeamento associativo Já a solução para substituição pode ser: ➔ Randômica: escolher aleatoriamente uma posição a ser substituída ➔ LFU (Least Frequent Used): a posição da cache que foi usada menos vezes será substituída. É preciso incrementa um contador a cada acesso e comparação para escolha; ➔ LRU (Least Recent Used): a posição da cache que foi usada a mais tempo será substituída. É preciso incrementar um contador a cada acesso e comparação para escolha.

Mapeamento associativo Já a solução para substituição pode ser: ➔ Randômica: escolher aleatoriamente uma posição a ser substituída ➔ LFU (Least Frequent Used): a posição da cache que foi usada menos vezes será substituída. É preciso incrementa um contador a cada acesso e comparação para escolha; ➔ LRU (Least Recent Used): a posição da cache que foi usada a mais tempo será substituída. É preciso incrementar um contador a cada acesso e comparação para escolha.

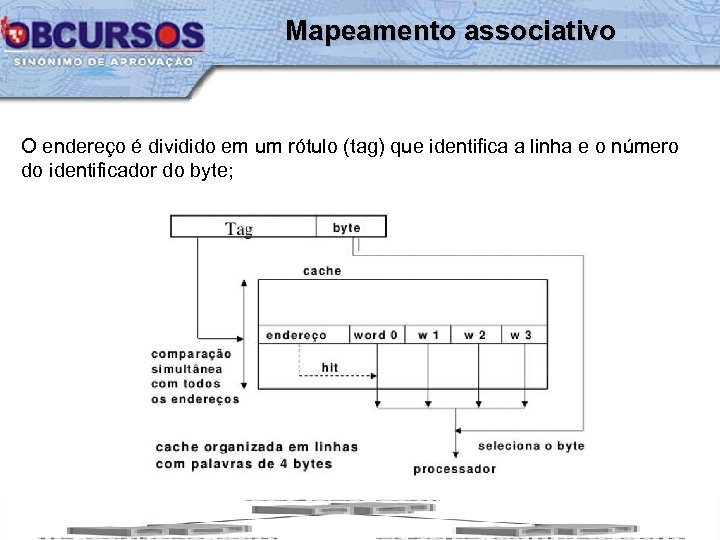

Mapeamento associativo O endereço é dividido em um rótulo (tag) que identifica a linha e o número do identificador do byte;

Mapeamento associativo O endereço é dividido em um rótulo (tag) que identifica a linha e o número do identificador do byte;

Passos do Mapeamento associativo 1. Alimentar a memória associativa com o tag procurado. 2. Se o tag procurado não está na cache acontece miss. Ir para 4. 3. Se acontece hit, acessar a memória cache com o índice fornecido e efeturar leitura. FIM. 4. Se não existir posição livre na cache, escolher um endereço para substituir (LRU). 5. Buscar o endereço procurado no nível mais baixo e colocar a posição livre (ou escolhida) da cache cadastrando essa posição e a tag na memória e efeturar leitura. FIM.

Passos do Mapeamento associativo 1. Alimentar a memória associativa com o tag procurado. 2. Se o tag procurado não está na cache acontece miss. Ir para 4. 3. Se acontece hit, acessar a memória cache com o índice fornecido e efeturar leitura. FIM. 4. Se não existir posição livre na cache, escolher um endereço para substituir (LRU). 5. Buscar o endereço procurado no nível mais baixo e colocar a posição livre (ou escolhida) da cache cadastrando essa posição e a tag na memória e efeturar leitura. FIM.

Mapeamento associativo Vantagens ➔ Melhor aproveitamento das posições da cache, pois de cheia se tem 100% de aproveitamento ➔ Dados de controle não ficam na cache Desvantangens ➔ Memória associativa tem alto custo e tamanho limitado ➔ Limita o número de linhas da cache ➔ Necessita de política de substituição, que custa tempo e ainda pode-se escolher mal.

Mapeamento associativo Vantagens ➔ Melhor aproveitamento das posições da cache, pois de cheia se tem 100% de aproveitamento ➔ Dados de controle não ficam na cache Desvantangens ➔ Memória associativa tem alto custo e tamanho limitado ➔ Limita o número de linhas da cache ➔ Necessita de política de substituição, que custa tempo e ainda pode-se escolher mal.

Mapeamento associativo conjuntivo Meio termo entre mapeamento direto e associativo. Uma cache associativa conjuntiva é dividida em S conjuntos (set) de N blocos ➔ Se S =1, mapaeamento associativo; ➔ Se S =N, mapeamento direto endereço da memória principal pode ser mapeado para qualquer Um endereço no conjunto da cache. preciso fazer procura dentro do conjunto. É Também faz uso de política para substituição.

Mapeamento associativo conjuntivo Meio termo entre mapeamento direto e associativo. Uma cache associativa conjuntiva é dividida em S conjuntos (set) de N blocos ➔ Se S =1, mapaeamento associativo; ➔ Se S =N, mapeamento direto endereço da memória principal pode ser mapeado para qualquer Um endereço no conjunto da cache. preciso fazer procura dentro do conjunto. É Também faz uso de política para substituição.

Passos para o mapeamento associativo conjuntivo 1. Calcular o módulo do endereço procurado pelo número de conjuntos S da cache. 2. Alimentar a memória associativa deste conjunto com o tag procurado. 3. Se o tag procurado não está na cache acontece miss. Ir para 5. 4. Se acontece hit, acessar a memória cache com o índice fornecido e efeturar leitura. FIM. 5. Se não existir posição livre na cache, escolher um endereço para substituir (LRU). 6. Buscar o endereço procurado no nível mais baixo e colocar a posição livre (ou escolhida) da cache cadastrando essa posição e a tag na memória e efeturar leitura. FIM.

Passos para o mapeamento associativo conjuntivo 1. Calcular o módulo do endereço procurado pelo número de conjuntos S da cache. 2. Alimentar a memória associativa deste conjunto com o tag procurado. 3. Se o tag procurado não está na cache acontece miss. Ir para 5. 4. Se acontece hit, acessar a memória cache com o índice fornecido e efeturar leitura. FIM. 5. Se não existir posição livre na cache, escolher um endereço para substituir (LRU). 6. Buscar o endereço procurado no nível mais baixo e colocar a posição livre (ou escolhida) da cache cadastrando essa posição e a tag na memória e efeturar leitura. FIM.

mapeamento associativo conjuntivo Vantagens ➔ Aumenta o tamanho da cache mantendo o tamanho da memória associativa ➔ Bastante flexível ➔ Usa a totalidade da área da cache para dados Desvantagens ➔ Tem alto custo e tamanho limitado ➔ Necessita de política de substituição ➔ Tempo acesso maior devido ao cálculo ➔ Dependendo da geração de endereços não se aproveita a totalidade das posições da cache

mapeamento associativo conjuntivo Vantagens ➔ Aumenta o tamanho da cache mantendo o tamanho da memória associativa ➔ Bastante flexível ➔ Usa a totalidade da área da cache para dados Desvantagens ➔ Tem alto custo e tamanho limitado ➔ Necessita de política de substituição ➔ Tempo acesso maior devido ao cálculo ➔ Dependendo da geração de endereços não se aproveita a totalidade das posições da cache

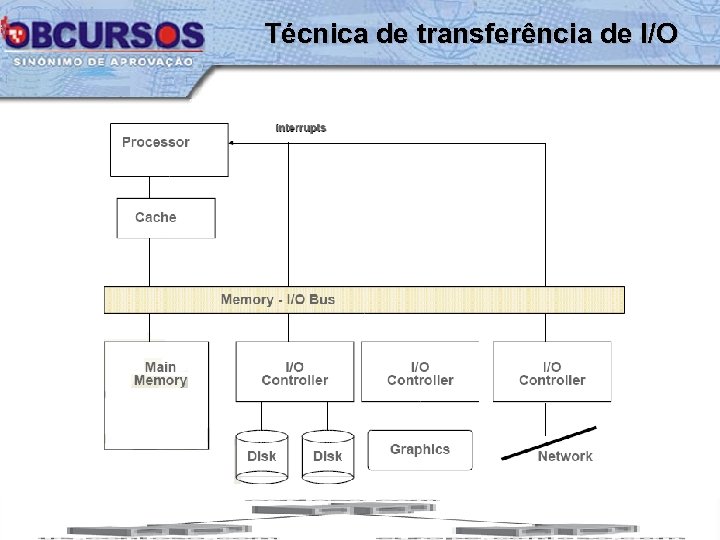

Técnica de transferência de I/O

Técnica de transferência de I/O

Porque estudar I/O? desempenho de CPUs aumenta de 50% a 100% por ano; O desempenho Supercomputadores com multiprocessadores aumenta O 150% por ano; o desempenho de subsistemas de I/O é limitado por atrasos mecânicos; Já ➔ Em média o crescimento é de 5% por ano (I/O por seg ou MB por seg); prática, o gargalo é I/O: Na ➔ CPU estão ficando mais rápidas ➔ Velocidade de CPUs está fazendo menos diferença

Porque estudar I/O? desempenho de CPUs aumenta de 50% a 100% por ano; O desempenho Supercomputadores com multiprocessadores aumenta O 150% por ano; o desempenho de subsistemas de I/O é limitado por atrasos mecânicos; Já ➔ Em média o crescimento é de 5% por ano (I/O por seg ou MB por seg); prática, o gargalo é I/O: Na ➔ CPU estão ficando mais rápidas ➔ Velocidade de CPUs está fazendo menos diferença

Porque estudar I/O? Hoje: ➔ O poder de processamento dobra a cada 18 meses ➔ Tamanho de memória dobra a cada 18 meses (? ) ➔ Capacidade de disco dobra a cada 18 meses ➔ Velocidade de posicionamento dos discos (Seek + Rotate) dobra a cada 10 anos!

Porque estudar I/O? Hoje: ➔ O poder de processamento dobra a cada 18 meses ➔ Tamanho de memória dobra a cada 18 meses (? ) ➔ Capacidade de disco dobra a cada 18 meses ➔ Velocidade de posicionamento dos discos (Seek + Rotate) dobra a cada 10 anos!

Tipos de barramentos Arquitetura de barramento único Arquitetura de barramento em dois níveis Arquitetura de barramento hierarquica

Tipos de barramentos Arquitetura de barramento único Arquitetura de barramento em dois níveis Arquitetura de barramento hierarquica

Barramento único Memória e dispositivos de I/O estão ligados a CPU atráves de um único barramento Forma mais simples de interconexão Barramento tem que acomodar dispositivos com características e velocidades bem diferentes e o desempenho da comunicação cai

Barramento único Memória e dispositivos de I/O estão ligados a CPU atráves de um único barramento Forma mais simples de interconexão Barramento tem que acomodar dispositivos com características e velocidades bem diferentes e o desempenho da comunicação cai

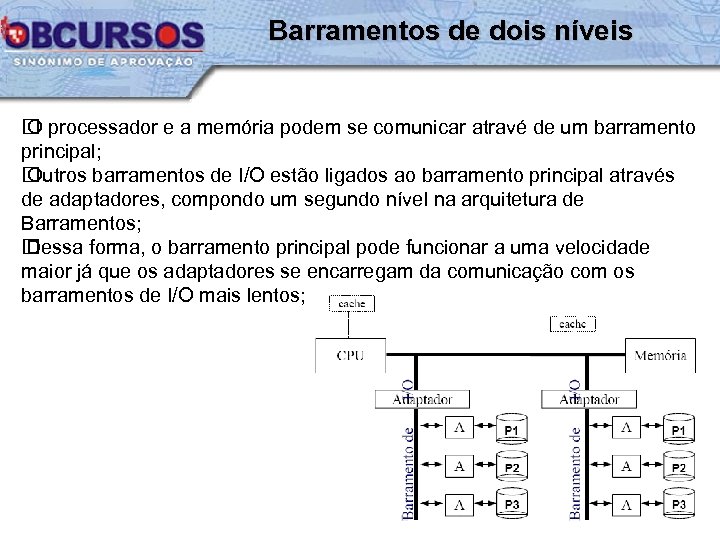

Barramentos de dois níveis processador e a memória podem se comunicar atravé de um barramento O principal; Outros barramentos de I/O estão ligados ao barramento principal através de adaptadores, compondo um segundo nível na arquitetura de Barramentos; Dessa forma, o barramento principal pode funcionar a uma velocidade maior já que os adaptadores se encarregam da comunicação com os barramentos de I/O mais lentos;

Barramentos de dois níveis processador e a memória podem se comunicar atravé de um barramento O principal; Outros barramentos de I/O estão ligados ao barramento principal através de adaptadores, compondo um segundo nível na arquitetura de Barramentos; Dessa forma, o barramento principal pode funcionar a uma velocidade maior já que os adaptadores se encarregam da comunicação com os barramentos de I/O mais lentos;

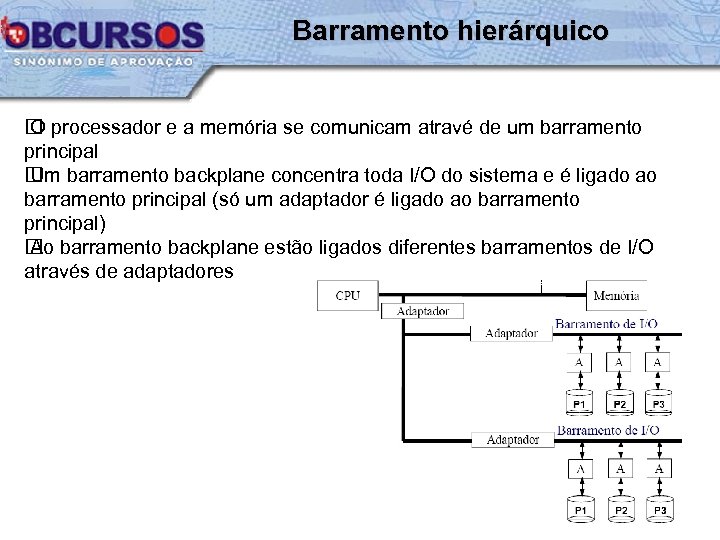

Barramento hierárquico processador e a memória se comunicam atravé de um barramento O principal barramento backplane concentra toda I/O do sistema e é ligado ao Um barramento principal (só um adaptador é ligado ao barramento principal) barramento backplane estão ligados diferentes barramentos de I/O Ao através de adaptadores

Barramento hierárquico processador e a memória se comunicam atravé de um barramento O principal barramento backplane concentra toda I/O do sistema e é ligado ao Um barramento principal (só um adaptador é ligado ao barramento principal) barramento backplane estão ligados diferentes barramentos de I/O Ao através de adaptadores

Mapeamento de I/O é o que faz um barramento é definir regras do que deve-se fazer para tranferir um bloco ou palavra. ■ Duas formas: Memory mapped; portas de I/O

Mapeamento de I/O é o que faz um barramento é definir regras do que deve-se fazer para tranferir um bloco ou palavra. ■ Duas formas: Memory mapped; portas de I/O

Mapeamento de I/O – Memory Mapped único espaço de endereçamento Um Destina-se um conjunto de endereços aos periféricos Instruções à memória pode ser tanto memória quanto operações de I/O mapeamento em memória tem a vantagem de permitir uma maior O proteção ao acesso direto a dispositivos, pois os endereços de I/O podem ser controlados pelo S. O. processadores da Motorola Ex:

Mapeamento de I/O – Memory Mapped único espaço de endereçamento Um Destina-se um conjunto de endereços aos periféricos Instruções à memória pode ser tanto memória quanto operações de I/O mapeamento em memória tem a vantagem de permitir uma maior O proteção ao acesso direto a dispositivos, pois os endereços de I/O podem ser controlados pelo S. O. processadores da Motorola Ex:

Mapeamento de I/O – portas de I/O Dois espaços distintos de endereçamento Entrada e saída acessadas por instruções específicas (IN, OUT) Microprocessador da INTEL Ex:

Mapeamento de I/O – portas de I/O Dois espaços distintos de endereçamento Entrada e saída acessadas por instruções específicas (IN, OUT) Microprocessador da INTEL Ex:

Modos de transferência de I/O ■ O que se deseja é: Rapidez na resposta a eventos criticos sobrecarga da CPU com atividades como acesso a disco e Não refresh de memória ■ Três modos de implementar: Programado Interrupção DMA

Modos de transferência de I/O ■ O que se deseja é: Rapidez na resposta a eventos criticos sobrecarga da CPU com atividades como acesso a disco e Não refresh de memória ■ Três modos de implementar: Programado Interrupção DMA

I/O Programada controlada pela CPU (registradores e instruções específicas) É processador pergunta para cada dispositivo se está apto a receber O ou transmitir uma unidade de informação e em caso afirmativo realiza a transferência; Existem dois tipos: ➔ Bloqueado (busy way); ➔ Polling (inquisição).

I/O Programada controlada pela CPU (registradores e instruções específicas) É processador pergunta para cada dispositivo se está apto a receber O ou transmitir uma unidade de informação e em caso afirmativo realiza a transferência; Existem dois tipos: ➔ Bloqueado (busy way); ➔ Polling (inquisição).

I/O Programada - Bloqueado ■ Bloqueado (busy way) Uma vez iniciada a comunicação, a CPU fica ocupada (escrava) até o término da operação CPU é subutilizada, pois os periféricos são muito mais lentos que a CPU balança eletrônica Ex:

I/O Programada - Bloqueado ■ Bloqueado (busy way) Uma vez iniciada a comunicação, a CPU fica ocupada (escrava) até o término da operação CPU é subutilizada, pois os periféricos são muito mais lentos que a CPU balança eletrônica Ex:

I/O Programada - Polling ■ Polling CPU periodicamente testa o conteúdo dos bits do(s) registrador(es) A de estado existente(s) nos controladores de I/O cada controlador há registradores que indicam tranferência a ser Em realizada (status) modo polling a CPU possui controle total, realizando todo o No trabalho

I/O Programada - Polling ■ Polling CPU periodicamente testa o conteúdo dos bits do(s) registrador(es) A de estado existente(s) nos controladores de I/O cada controlador há registradores que indicam tranferência a ser Em realizada (status) modo polling a CPU possui controle total, realizando todo o No trabalho

I/O por interrupção Criada para solucionar o problema do tempo desperdiçado com múltiplos testes que é inerente do polling; Controladora é avisada pelo dispositivo que está pronto para transmitir/receber dados; Principais características: ➔ Assincronismo em relação a qualquer instrução, ocorrendo a qualquer instante ➔ Na ocorrência de uma interrupção, a mesma é atendida após o término da instrução corrente. O teste de interrupção é feito depois da execução da instrução ➔ Diferenciar interrupção de hardware de excessões ➔ Dispositivos podem ter diferentes prioridades

I/O por interrupção Criada para solucionar o problema do tempo desperdiçado com múltiplos testes que é inerente do polling; Controladora é avisada pelo dispositivo que está pronto para transmitir/receber dados; Principais características: ➔ Assincronismo em relação a qualquer instrução, ocorrendo a qualquer instante ➔ Na ocorrência de uma interrupção, a mesma é atendida após o término da instrução corrente. O teste de interrupção é feito depois da execução da instrução ➔ Diferenciar interrupção de hardware de excessões ➔ Dispositivos podem ter diferentes prioridades

I/O com utilização de DMA ■ DMA (Transferência direta à memória) idéia de interrupção, a CPU é liberada da tarefa de aguardar por Na ocorrência de eventos de I/O, mas continua sendo o elemente ativo solução é usar DMA. Dispositivo controlador é o responsável pela A tranferência de dados, ficando a CPU livre para realizar outras operações. Mecanismos de interrupção continuam sendo utilizados pelo controlador para comunicação com o processador, mas apenas no término de um evento de I/O ou na ocorrência de erros Durante a operação o controlador DMA se torna o mestre do barramento e controla a transferência I/O <-> memória

I/O com utilização de DMA ■ DMA (Transferência direta à memória) idéia de interrupção, a CPU é liberada da tarefa de aguardar por Na ocorrência de eventos de I/O, mas continua sendo o elemente ativo solução é usar DMA. Dispositivo controlador é o responsável pela A tranferência de dados, ficando a CPU livre para realizar outras operações. Mecanismos de interrupção continuam sendo utilizados pelo controlador para comunicação com o processador, mas apenas no término de um evento de I/O ou na ocorrência de erros Durante a operação o controlador DMA se torna o mestre do barramento e controla a transferência I/O <-> memória

PROTOCOLOS – Parte 1 TCP - Transmission Control Protocol (Comunicação) FTP – File Transfer Protocol (Transferência de Arquivos) SMTP – Simple Mail Transport Protocol (Informações) LDAP - Lightweight Directory Access Protocol (Serviço de diretório) SNMP – Simple Network Management Protocol (Gerenciamento)

PROTOCOLOS – Parte 1 TCP - Transmission Control Protocol (Comunicação) FTP – File Transfer Protocol (Transferência de Arquivos) SMTP – Simple Mail Transport Protocol (Informações) LDAP - Lightweight Directory Access Protocol (Serviço de diretório) SNMP – Simple Network Management Protocol (Gerenciamento)

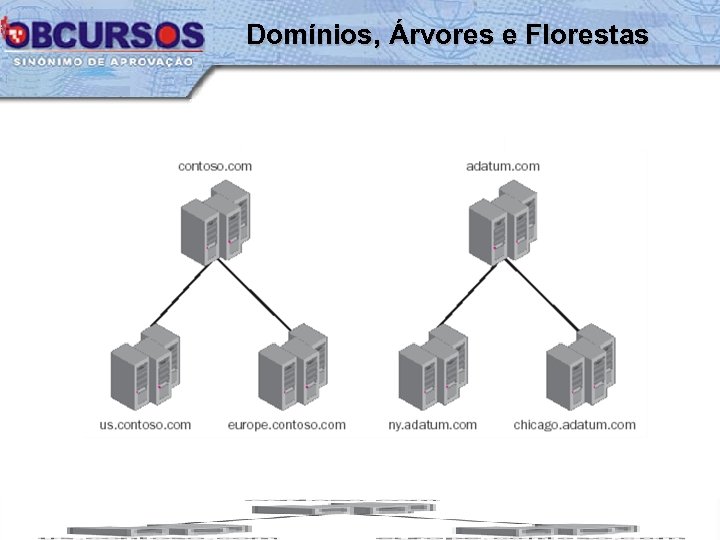

Domínios, Árvores e Florestas

Domínios, Árvores e Florestas

Objetos e atributos • Domain – Contém um agrupamento de todos os demais objetos • Organizational Unit – Consiste em uma espécie de container • User – Objeto de usuário • Computer – Objeto de associação a computadores • Group – Representação gráfica de grupos de usuários, computadores e/ou árvores de replicação • Shared Folders – Associação à compartilhamentos de arquivos • Printer – Objeto relacionado à impressoras locais ou de rede.

Objetos e atributos • Domain – Contém um agrupamento de todos os demais objetos • Organizational Unit – Consiste em uma espécie de container • User – Objeto de usuário • Computer – Objeto de associação a computadores • Group – Representação gráfica de grupos de usuários, computadores e/ou árvores de replicação • Shared Folders – Associação à compartilhamentos de arquivos • Printer – Objeto relacionado à impressoras locais ou de rede.

Contato Frank S. F. Bastos E-MAIL. : Frank. bastos@gmail. com MSN. : frankbastos@hotmail. com Skype. : frankbastos

Contato Frank S. F. Bastos E-MAIL. : Frank. bastos@gmail. com MSN. : frankbastos@hotmail. com Skype. : frankbastos