786c181995ba116e64ffa5839094bde1.ppt

- Количество слайдов: 198

From ESL to Implementation: Reinventing Hardware Design using Bluespec System. Verilog™ © 2006, Bluespec, Inc. Copyright © Bluespec Inc. 2006 Confidential and Proprietary

From ESL to Implementation: Reinventing Hardware Design using Bluespec System. Verilog™ © 2006, Bluespec, Inc. Copyright © Bluespec Inc. 2006 Confidential and Proprietary

Joe Stoy Founder and Principal Engineer Bluespec Inc. 14 -16 Spring Street Waltham MA 02451, USA +1 781 250 2206 stoy@bluespec. com www. bluespec. com Copyright © Bluespec Inc. 2006 Confidential and Proprietary 2

Joe Stoy Founder and Principal Engineer Bluespec Inc. 14 -16 Spring Street Waltham MA 02451, USA +1 781 250 2206 stoy@bluespec. com www. bluespec. com Copyright © Bluespec Inc. 2006 Confidential and Proprietary 2

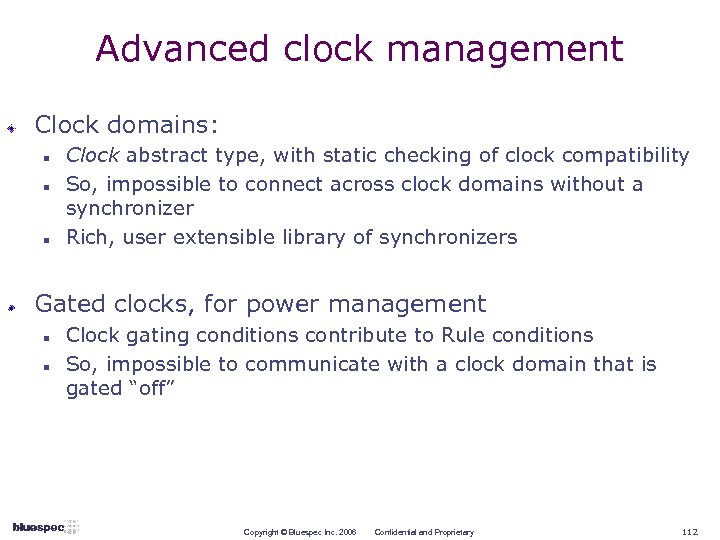

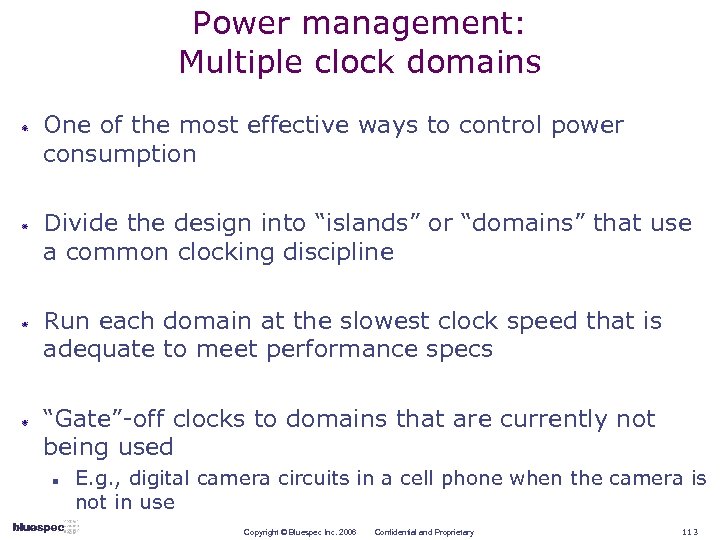

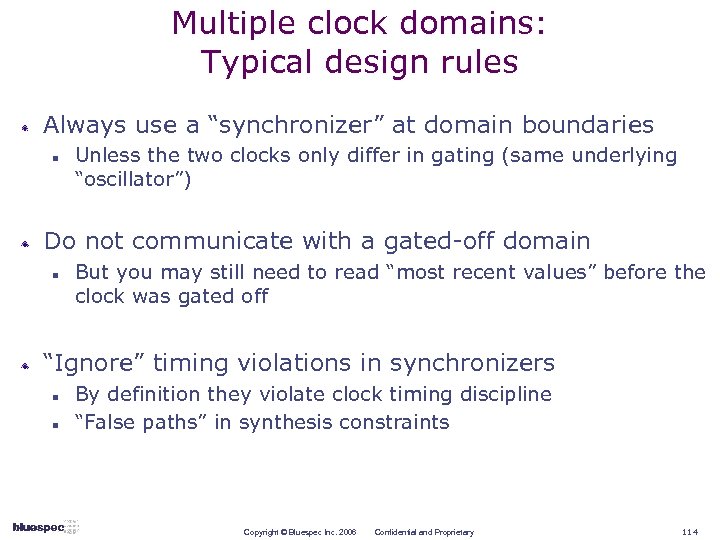

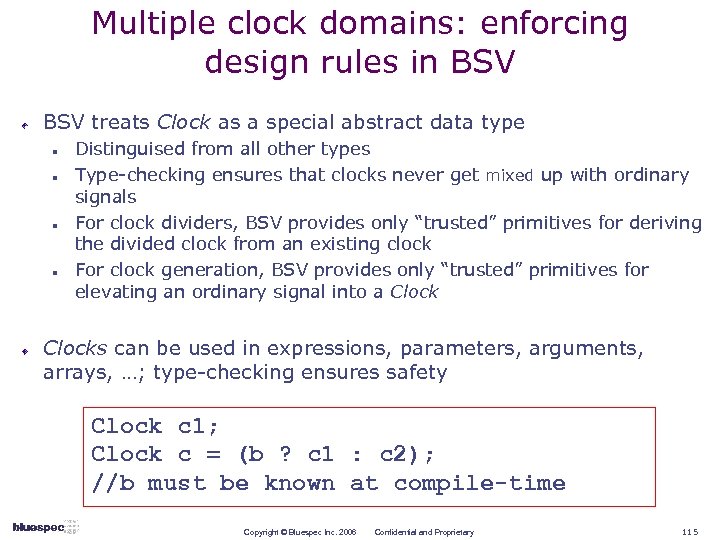

Bluespec System. Verilog Workshop Agenda Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm Synthesis quality: as good as hand-coded RTL Tool flows Futures: n Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 3

Bluespec System. Verilog Workshop Agenda Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm Synthesis quality: as good as hand-coded RTL Tool flows Futures: n Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 3

Intro: why an improved HDL is a central need to address today’s chip design complexities Copyright © Bluespec Inc. 2006 Confidential and Proprietary 4

Intro: why an improved HDL is a central need to address today’s chip design complexities Copyright © Bluespec Inc. 2006 Confidential and Proprietary 4

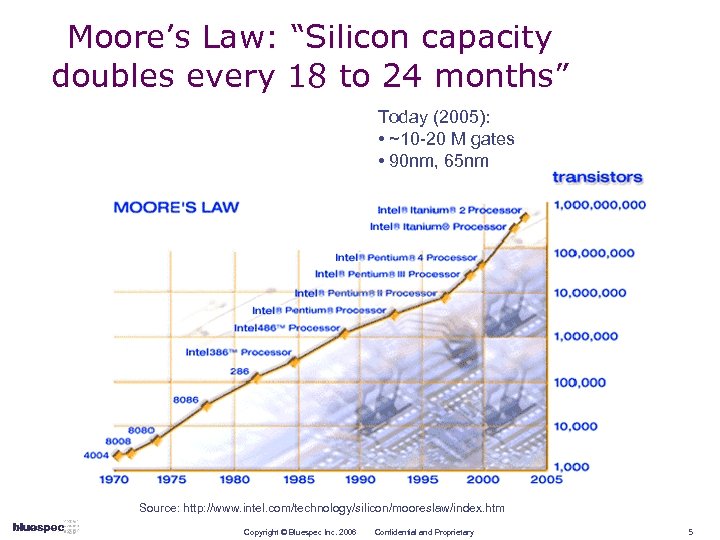

Moore’s Law: “Silicon capacity doubles every 18 to 24 months” Today (2005): • ~10 -20 M gates • 90 nm, 65 nm Source: http: //www. intel. com/technology/silicon/mooreslaw/index. htm Copyright © Bluespec Inc. 2006 Confidential and Proprietary 5

Moore’s Law: “Silicon capacity doubles every 18 to 24 months” Today (2005): • ~10 -20 M gates • 90 nm, 65 nm Source: http: //www. intel. com/technology/silicon/mooreslaw/index. htm Copyright © Bluespec Inc. 2006 Confidential and Proprietary 5

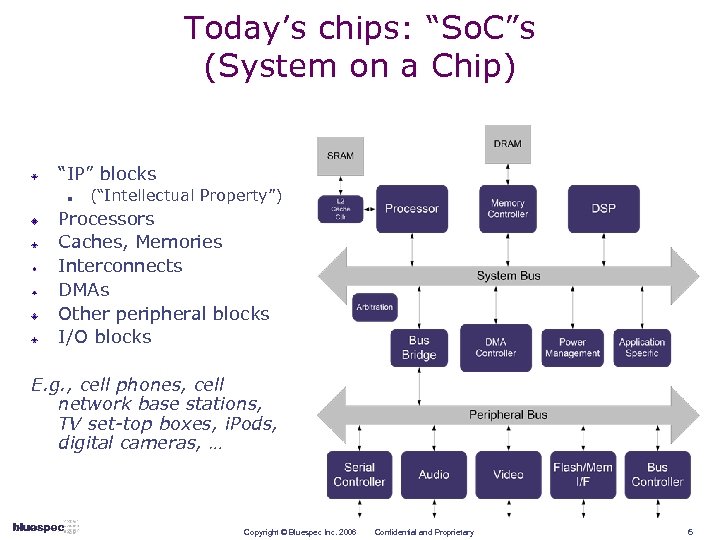

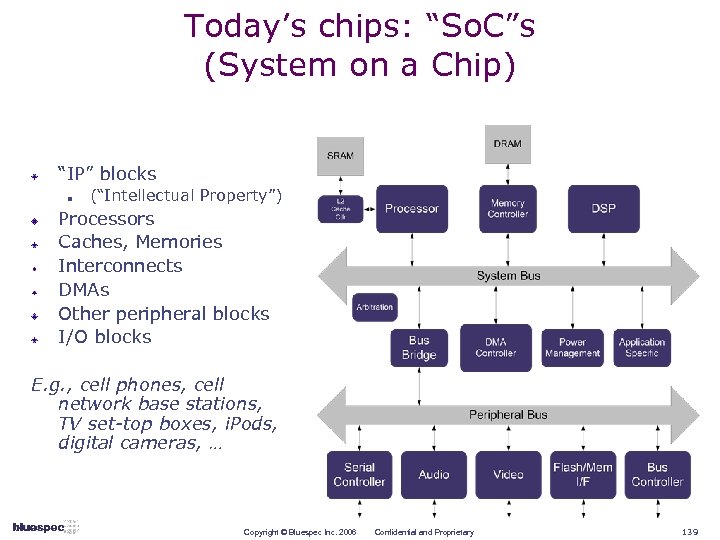

Today’s chips: “So. C”s (System on a Chip) “IP” blocks n (“Intellectual Property”) Processors Caches, Memories Interconnects DMAs Other peripheral blocks I/O blocks E. g. , cell phones, cell network base stations, TV set-top boxes, i. Pods, digital cameras, … Copyright © Bluespec Inc. 2006 Confidential and Proprietary 6

Today’s chips: “So. C”s (System on a Chip) “IP” blocks n (“Intellectual Property”) Processors Caches, Memories Interconnects DMAs Other peripheral blocks I/O blocks E. g. , cell phones, cell network base stations, TV set-top boxes, i. Pods, digital cameras, … Copyright © Bluespec Inc. 2006 Confidential and Proprietary 6

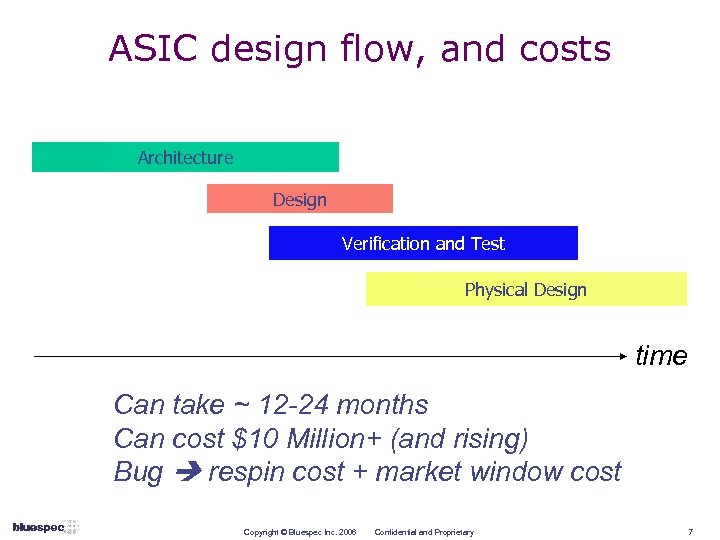

ASIC design flow, and costs Architecture Design Verification and Test Physical Design time Can take ~ 12 -24 months Can cost $10 Million+ (and rising) Bug respin cost + market window cost Copyright © Bluespec Inc. 2006 Confidential and Proprietary 7

ASIC design flow, and costs Architecture Design Verification and Test Physical Design time Can take ~ 12 -24 months Can cost $10 Million+ (and rising) Bug respin cost + market window cost Copyright © Bluespec Inc. 2006 Confidential and Proprietary 7

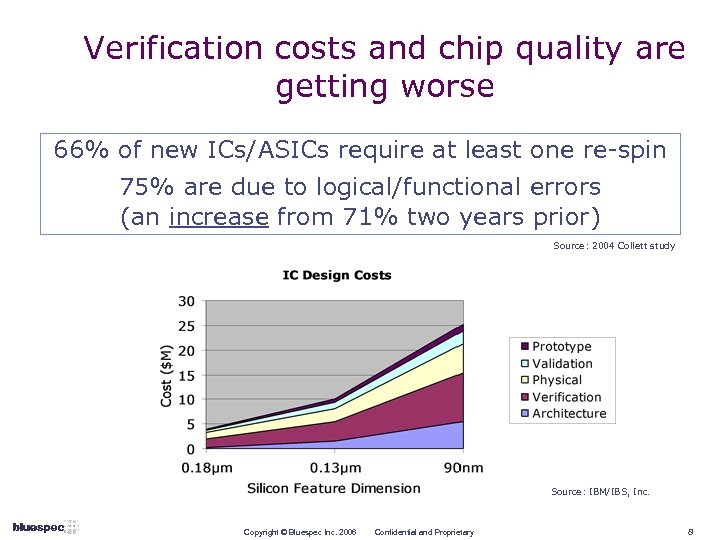

Verification costs and chip quality are getting worse 66% of new ICs/ASICs require at least one re-spin 75% are due to logical/functional errors (an increase from 71% two years prior) Source: 2004 Collett study Source: IBM/IBS, Inc. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 8

Verification costs and chip quality are getting worse 66% of new ICs/ASICs require at least one re-spin 75% are due to logical/functional errors (an increase from 71% two years prior) Source: 2004 Collett study Source: IBM/IBS, Inc. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 8

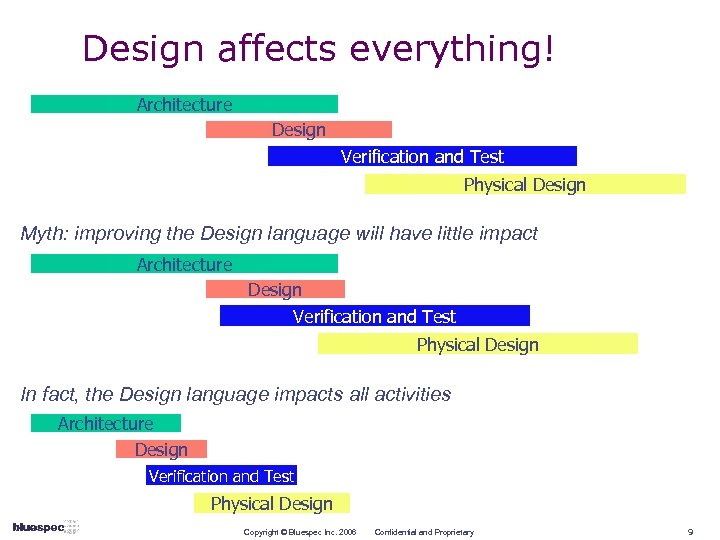

Design affects everything! Architecture Design Verification and Test Physical Design Myth: improving the Design language will have little impact Architecture Design Verification and Test Physical Design In fact, the Design language impacts all activities Architecture Design Verification and Test Physical Design Copyright © Bluespec Inc. 2006 Confidential and Proprietary 9

Design affects everything! Architecture Design Verification and Test Physical Design Myth: improving the Design language will have little impact Architecture Design Verification and Test Physical Design In fact, the Design language impacts all activities Architecture Design Verification and Test Physical Design Copyright © Bluespec Inc. 2006 Confidential and Proprietary 9

How to improve productivity? “It is a profoundly erroneous truism, repeated by all copybooks and by eminent people when they are making speeches, that we should cultivate the habit of thinking of what we are doing. The precise opposite is the case. Civilization advances by extending the number of important operations which we can perform without thinking about them. …” [ Example: long division used to be an advanced subject in the days of Roman numerals; Arabic numerals changed that ] Alfred North Whitehead Mathematician and philosopher (1861 -1947) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 10

How to improve productivity? “It is a profoundly erroneous truism, repeated by all copybooks and by eminent people when they are making speeches, that we should cultivate the habit of thinking of what we are doing. The precise opposite is the case. Civilization advances by extending the number of important operations which we can perform without thinking about them. …” [ Example: long division used to be an advanced subject in the days of Roman numerals; Arabic numerals changed that ] Alfred North Whitehead Mathematician and philosopher (1861 -1947) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 10

The language of design is crucial! Software analogy: Assembler Fortran C C++ Java No theoretical difference (all Turing-complete) n “I can produce better code by writing it in Assembler” w w Maybe, if you are given enough time! “Better” = more efficient, but not more readable, maintainable, or reusable You can still write incorrect code; you still need to debug; you still need to verify. But the probabilities of certain bugs decrease and the kinds of bugs change, as you go to higher levels: n n n Register protocol, argument/result-passing protocol, stack protocol, byte/word-alignment issues Reentrancy and recursion protocols Memory layout of complex data Memory allocation/deallocation Type-misinterpretation Code reuse (parameterization and polymorphism) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 11

The language of design is crucial! Software analogy: Assembler Fortran C C++ Java No theoretical difference (all Turing-complete) n “I can produce better code by writing it in Assembler” w w Maybe, if you are given enough time! “Better” = more efficient, but not more readable, maintainable, or reusable You can still write incorrect code; you still need to debug; you still need to verify. But the probabilities of certain bugs decrease and the kinds of bugs change, as you go to higher levels: n n n Register protocol, argument/result-passing protocol, stack protocol, byte/word-alignment issues Reentrancy and recursion protocols Memory layout of complex data Memory allocation/deallocation Type-misinterpretation Code reuse (parameterization and polymorphism) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 11

Some lessons from SW language history The size/complexity of the system that you can build, correctly, within a short time, improves with higher levels of abstraction But also, crucially, people will not/ cannot use your new higher level language for serious work n n if it sacrifices efficiency if it is unpredictable/uncontrollable Copyright © Bluespec Inc. 2006 Confidential and Proprietary 12

Some lessons from SW language history The size/complexity of the system that you can build, correctly, within a short time, improves with higher levels of abstraction But also, crucially, people will not/ cannot use your new higher level language for serious work n n if it sacrifices efficiency if it is unpredictable/uncontrollable Copyright © Bluespec Inc. 2006 Confidential and Proprietary 12

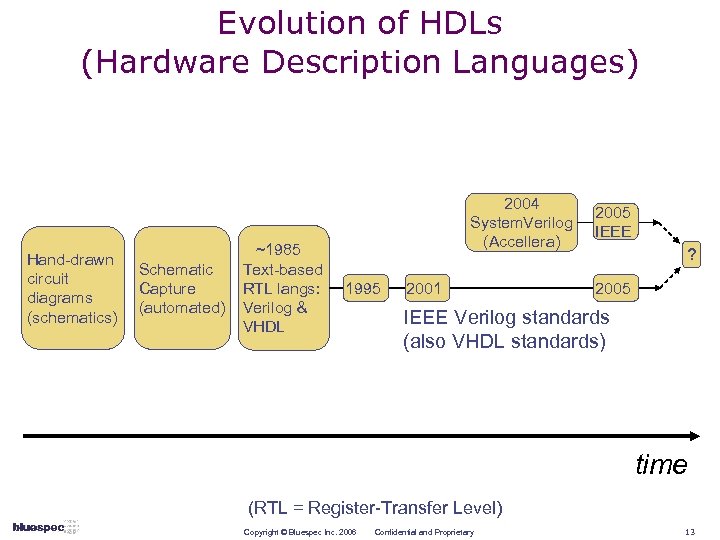

Evolution of HDLs (Hardware Description Languages) Hand-drawn circuit diagrams (schematics) Schematic Capture (automated) ~1985 Text-based RTL langs: Verilog & VHDL 2004 System. Verilog (Accellera) 1995 2001 2005 IEEE ? 2005 IEEE Verilog standards (also VHDL standards) time (RTL = Register-Transfer Level) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 13

Evolution of HDLs (Hardware Description Languages) Hand-drawn circuit diagrams (schematics) Schematic Capture (automated) ~1985 Text-based RTL langs: Verilog & VHDL 2004 System. Verilog (Accellera) 1995 2001 2005 IEEE ? 2005 IEEE Verilog standards (also VHDL standards) time (RTL = Register-Transfer Level) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 13

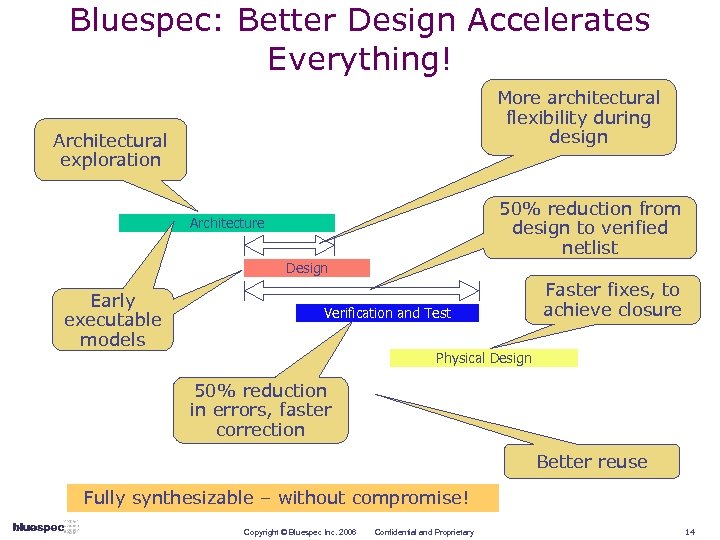

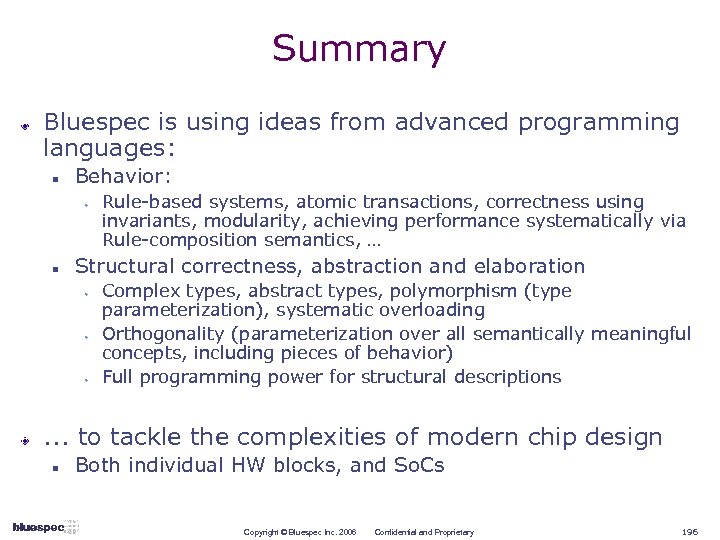

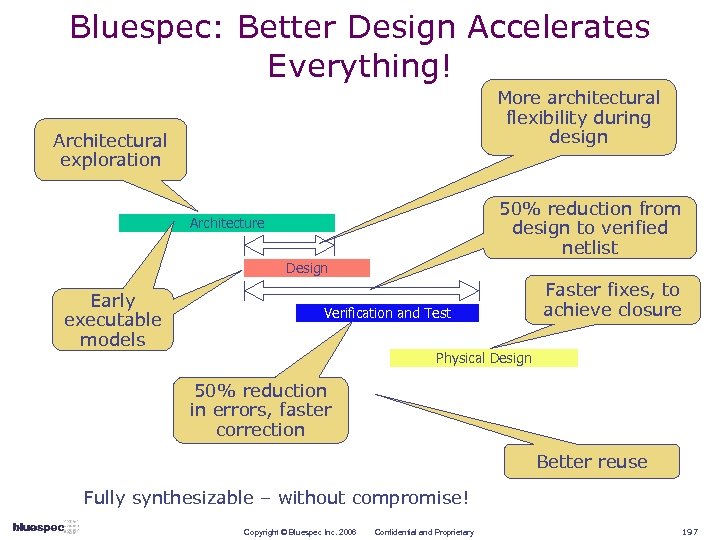

Bluespec: Better Design Accelerates Everything! More architectural flexibility during design Architectural exploration 50% reduction from design to verified netlist Architecture Design Early executable models Verification and Test Faster fixes, to achieve closure Physical Design 50% reduction in errors, faster correction Better reuse Fully synthesizable – without compromise! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 14

Bluespec: Better Design Accelerates Everything! More architectural flexibility during design Architectural exploration 50% reduction from design to verified netlist Architecture Design Early executable models Verification and Test Faster fixes, to achieve closure Physical Design 50% reduction in errors, faster correction Better reuse Fully synthesizable – without compromise! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 14

Bluespec, Inc. company and technology background Copyright © Bluespec Inc. 2006 Confidential and Proprietary 15

Bluespec, Inc. company and technology background Copyright © Bluespec Inc. 2006 Confidential and Proprietary 15

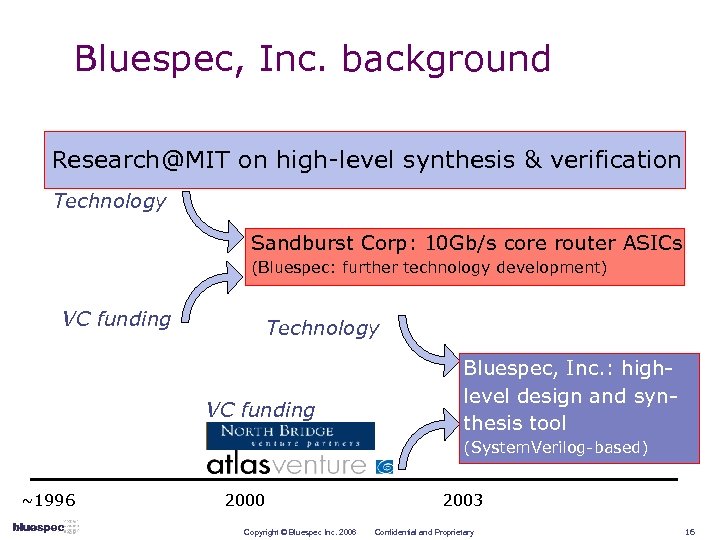

Bluespec, Inc. background Research@MIT on high-level synthesis & verification Technology Sandburst Corp: 10 Gb/s core router ASICs (Bluespec: further technology development) VC funding Technology VC funding Bluespec, Inc. : highlevel design and synthesis tool (System. Verilog-based) ~1996 2000 Copyright © Bluespec Inc. 2006 2003 Confidential and Proprietary 16

Bluespec, Inc. background Research@MIT on high-level synthesis & verification Technology Sandburst Corp: 10 Gb/s core router ASICs (Bluespec: further technology development) VC funding Technology VC funding Bluespec, Inc. : highlevel design and synthesis tool (System. Verilog-based) ~1996 2000 Copyright © Bluespec Inc. 2006 2003 Confidential and Proprietary 16

Bluespec, Inc. Headquartered in Waltham, MA n ~45 people (MA, CA, Europe, Armenia, India) Technology, 1997 -present n n MIT research: Professor Arvind, students & colleagues Patented: HW synthesis from Rules Active IEEE P 1800/Accellera member; SV language contributor, System C language contributor Copyright © Bluespec Inc. 2006 Confidential and Proprietary 17

Bluespec, Inc. Headquartered in Waltham, MA n ~45 people (MA, CA, Europe, Armenia, India) Technology, 1997 -present n n MIT research: Professor Arvind, students & colleagues Patented: HW synthesis from Rules Active IEEE P 1800/Accellera member; SV language contributor, System C language contributor Copyright © Bluespec Inc. 2006 Confidential and Proprietary 17

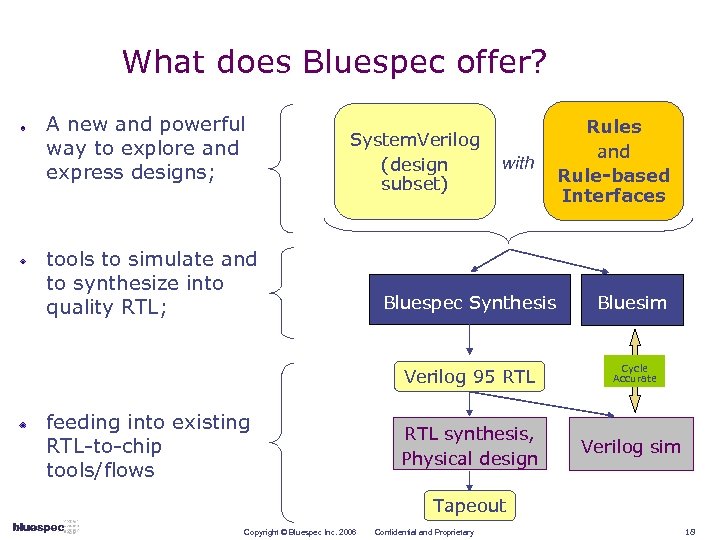

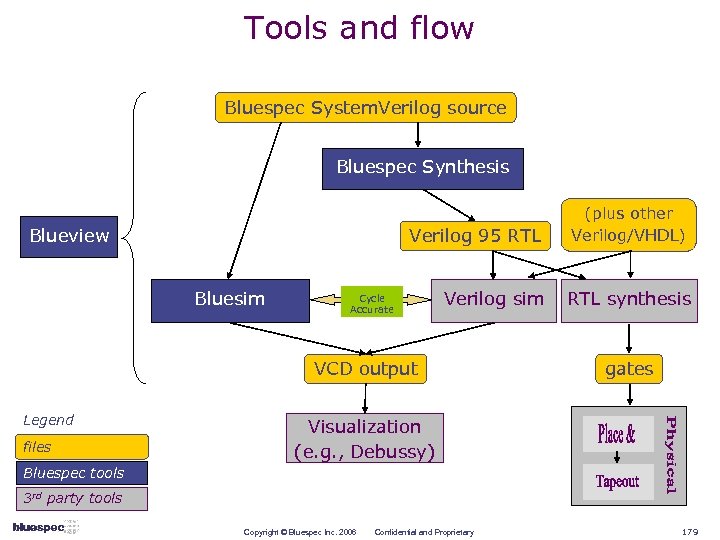

What does Bluespec offer? A new and powerful way to explore and express designs; System. Verilog (design subset) tools to simulate and to synthesize into quality RTL; with Rules and Rule-based Interfaces Bluesim Verilog 95 RTL feeding into existing RTL-to-chip tools/flows Bluespec Synthesis Cycle Accurate RTL synthesis, Physical design Verilog sim Tapeout Copyright © Bluespec Inc. 2006 Confidential and Proprietary 18

What does Bluespec offer? A new and powerful way to explore and express designs; System. Verilog (design subset) tools to simulate and to synthesize into quality RTL; with Rules and Rule-based Interfaces Bluesim Verilog 95 RTL feeding into existing RTL-to-chip tools/flows Bluespec Synthesis Cycle Accurate RTL synthesis, Physical design Verilog sim Tapeout Copyright © Bluespec Inc. 2006 Confidential and Proprietary 18

Bluespec Solutions Copyright © Bluespec Inc. 2006 Confidential and Proprietary 19

Bluespec Solutions Copyright © Bluespec Inc. 2006 Confidential and Proprietary 19

Bluespec core technologies Design – executable specifications n n Synthesizable, high-level concurrency semantics Transactional interfaces for design with self-documenting protocol Verification – static and formal n n n Strong type checking Interface connectivity and protocol checking Race condition identification and management Multiple-domain clock and interface checking Rapid simulation with C/C++ functions Copyright © Bluespec Inc. 2006 Confidential and Proprietary 20

Bluespec core technologies Design – executable specifications n n Synthesizable, high-level concurrency semantics Transactional interfaces for design with self-documenting protocol Verification – static and formal n n n Strong type checking Interface connectivity and protocol checking Race condition identification and management Multiple-domain clock and interface checking Rapid simulation with C/C++ functions Copyright © Bluespec Inc. 2006 Confidential and Proprietary 20

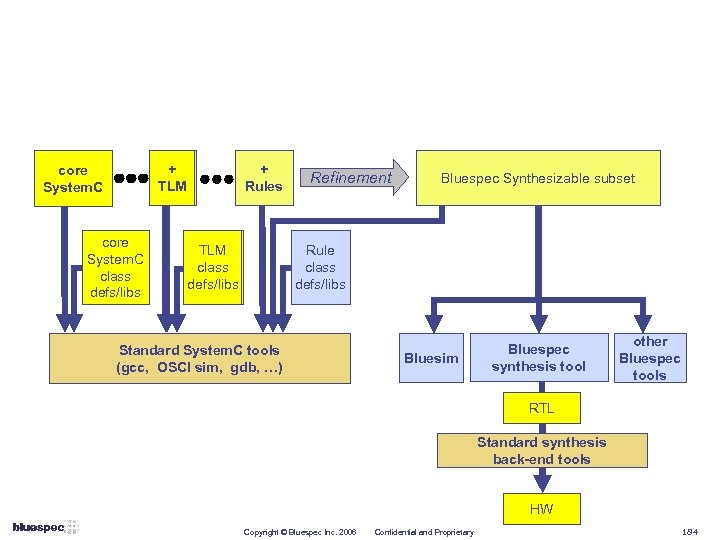

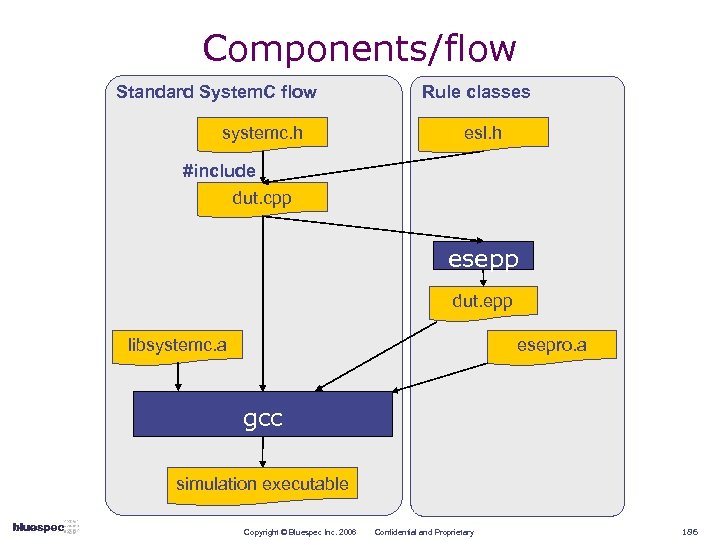

![Bluespec tools System. C [ESE] BSV TRANSLATE Parsing Static Checking Optimization gcc Scheduling Common Bluespec tools System. C [ESE] BSV TRANSLATE Parsing Static Checking Optimization gcc Scheduling Common](https://present5.com/presentation/786c181995ba116e64ffa5839094bde1/image-21.jpg) Bluespec tools System. C [ESE] BSV TRANSLATE Parsing Static Checking Optimization gcc Scheduling Common Synthesis Engine Power Optimization. exe Rapid, Source-Level Simulation and Interactive Debug of BSV Blueview Debug Parsing libsystemc. h RTL Generation System. C Simulation Bluespec Synthesis Cycle-Accurate w/Verilog sim Bluesim w/Verilog sim RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 21

Bluespec tools System. C [ESE] BSV TRANSLATE Parsing Static Checking Optimization gcc Scheduling Common Synthesis Engine Power Optimization. exe Rapid, Source-Level Simulation and Interactive Debug of BSV Blueview Debug Parsing libsystemc. h RTL Generation System. C Simulation Bluespec Synthesis Cycle-Accurate w/Verilog sim Bluesim w/Verilog sim RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 21

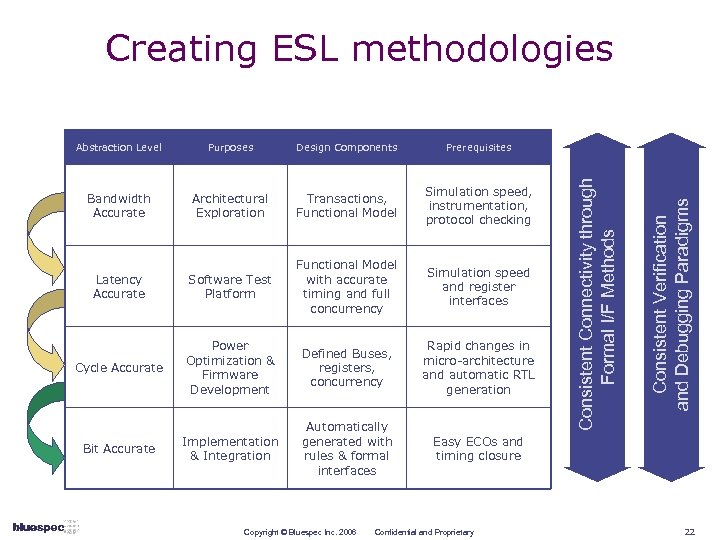

Creating ESL methodologies Design Components Prerequisites Bandwidth Accurate Architectural Exploration Transactions, Functional Model Simulation speed, instrumentation, protocol checking Latency Accurate Software Test Platform Functional Model with accurate timing and full concurrency Simulation speed and register interfaces Cycle Accurate Power Optimization & Firmware Development Defined Buses, registers, concurrency Rapid changes in micro-architecture and automatic RTL generation Implementation & Integration Automatically generated with rules & formal interfaces Easy ECOs and timing closure Bit Accurate Copyright © Bluespec Inc. 2006 Confidential and Proprietary Consistent Verification and Debugging Paradigms Purposes Consistent Connectivity through Formal I/F Methods Abstraction Level 22

Creating ESL methodologies Design Components Prerequisites Bandwidth Accurate Architectural Exploration Transactions, Functional Model Simulation speed, instrumentation, protocol checking Latency Accurate Software Test Platform Functional Model with accurate timing and full concurrency Simulation speed and register interfaces Cycle Accurate Power Optimization & Firmware Development Defined Buses, registers, concurrency Rapid changes in micro-architecture and automatic RTL generation Implementation & Integration Automatically generated with rules & formal interfaces Easy ECOs and timing closure Bit Accurate Copyright © Bluespec Inc. 2006 Confidential and Proprietary Consistent Verification and Debugging Paradigms Purposes Consistent Connectivity through Formal I/F Methods Abstraction Level 22

![ESL to Implementation Technologies Tools System. C [ESE] Methodologies BSV TRANSLATE Concurrency Semantics Bandwidth ESL to Implementation Technologies Tools System. C [ESE] Methodologies BSV TRANSLATE Concurrency Semantics Bandwidth](https://present5.com/presentation/786c181995ba116e64ffa5839094bde1/image-23.jpg) ESL to Implementation Technologies Tools System. C [ESE] Methodologies BSV TRANSLATE Concurrency Semantics Bandwidth Accurate Formal Interfaces gcc Bluespec Synthesis Bluesim Static, Formal Checking. exe Low Power Optimization Blueview libsystemc. h Latency Accurate Cycle Accurate System. C Simulation Bit Accurate RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 23

ESL to Implementation Technologies Tools System. C [ESE] Methodologies BSV TRANSLATE Concurrency Semantics Bandwidth Accurate Formal Interfaces gcc Bluespec Synthesis Bluesim Static, Formal Checking. exe Low Power Optimization Blueview libsystemc. h Latency Accurate Cycle Accurate System. C Simulation Bit Accurate RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 23

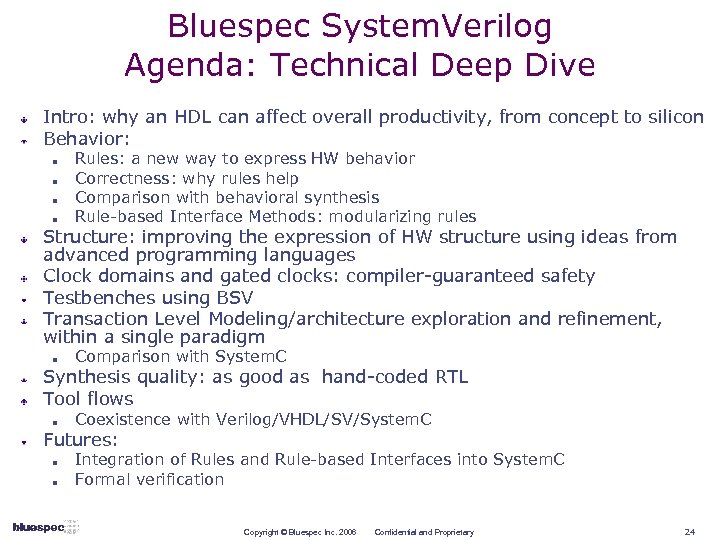

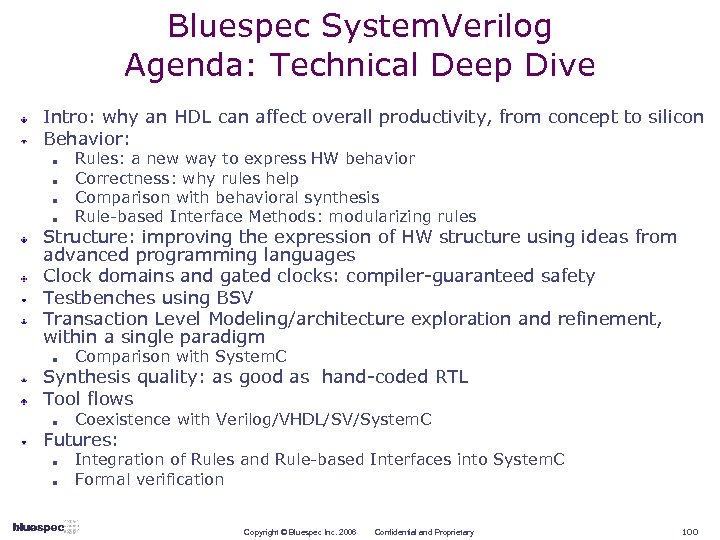

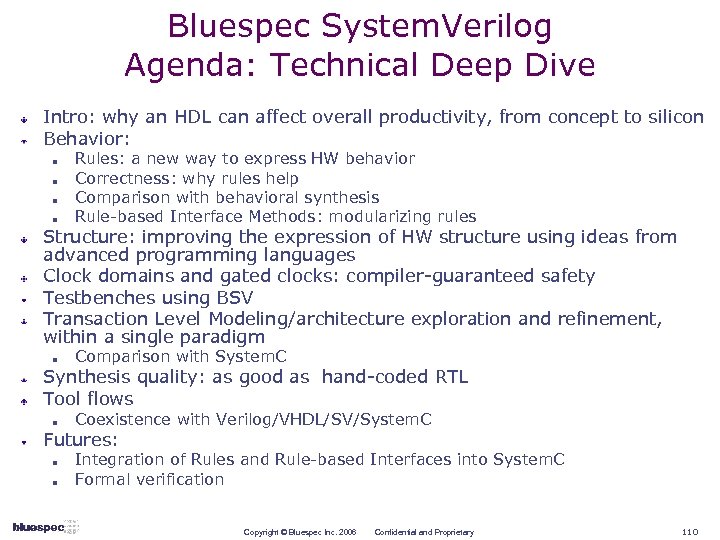

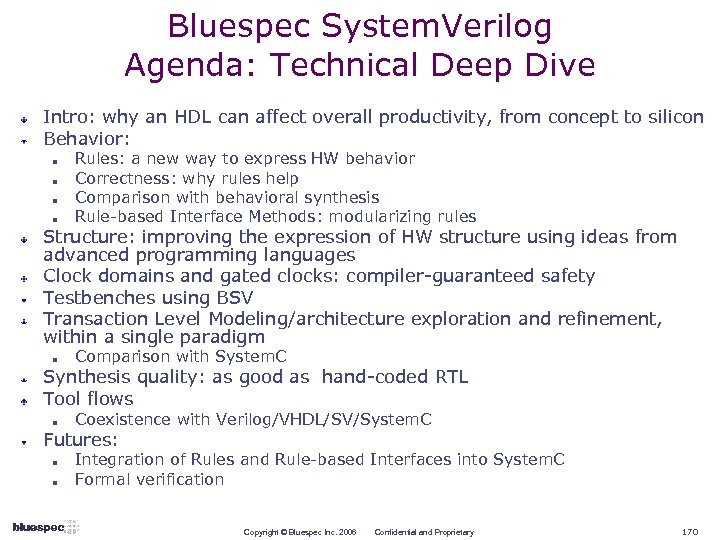

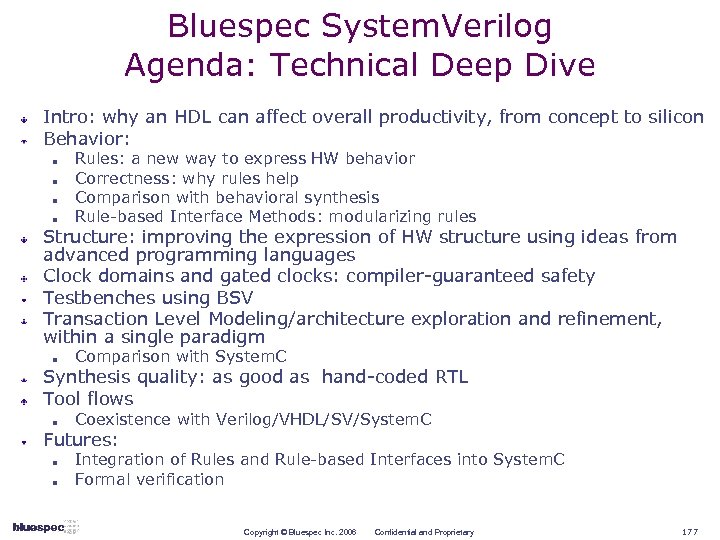

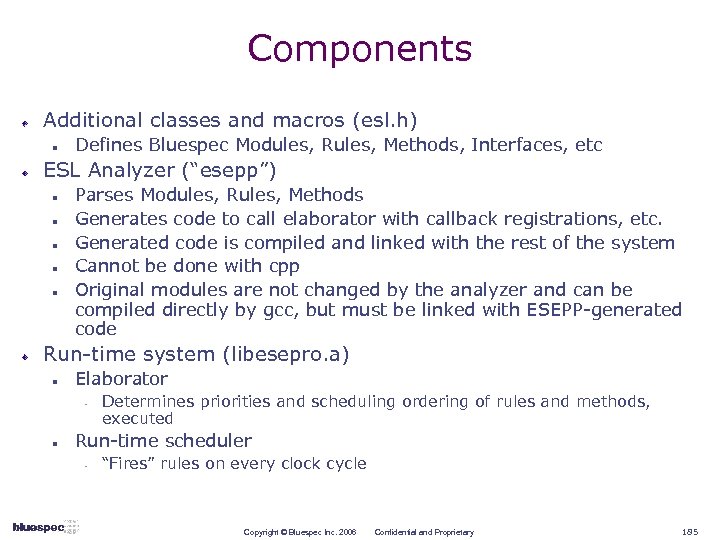

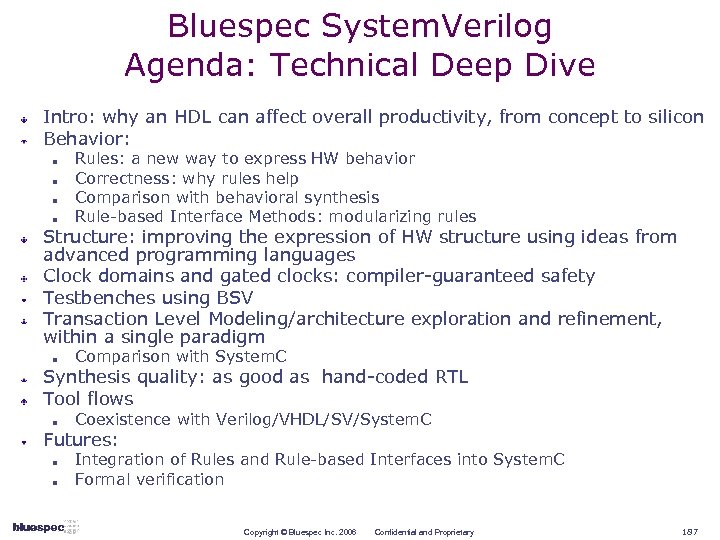

Bluespec System. Verilog Agenda: Technical Deep Dive Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm n Comparison with System. C Synthesis quality: as good as hand-coded RTL Tool flows n Coexistence with Verilog/VHDL/SV/System. C Futures: n n Integration of Rules and Rule-based Interfaces into System. C Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 24

Bluespec System. Verilog Agenda: Technical Deep Dive Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm n Comparison with System. C Synthesis quality: as good as hand-coded RTL Tool flows n Coexistence with Verilog/VHDL/SV/System. C Futures: n n Integration of Rules and Rule-based Interfaces into System. C Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 24

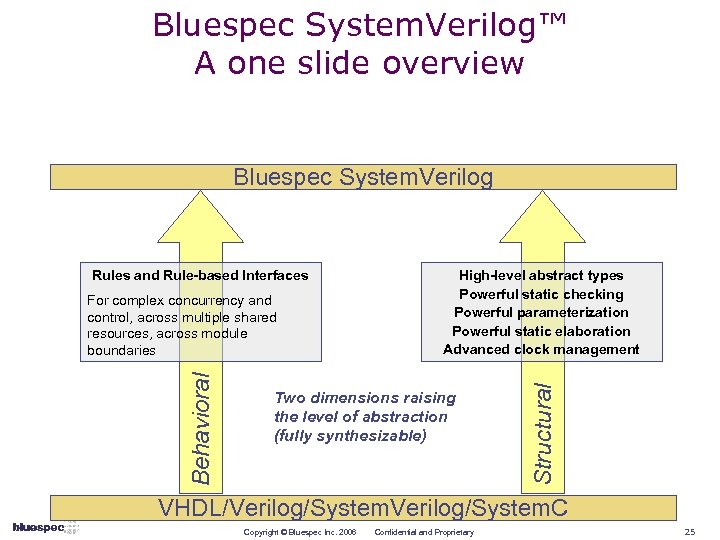

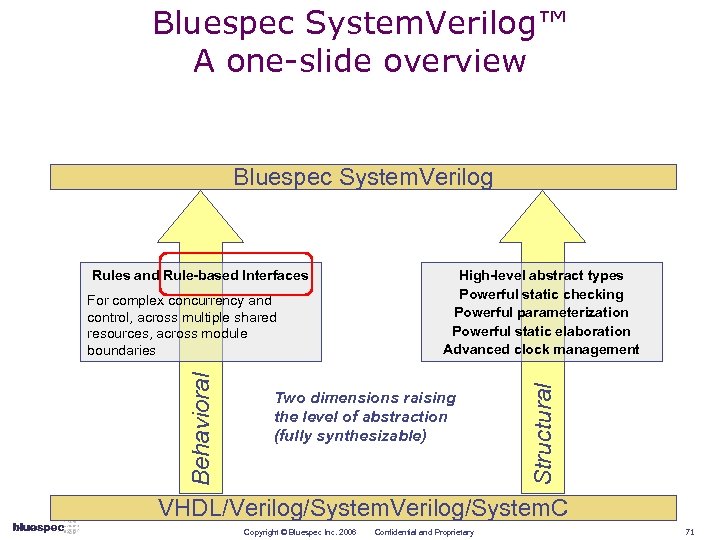

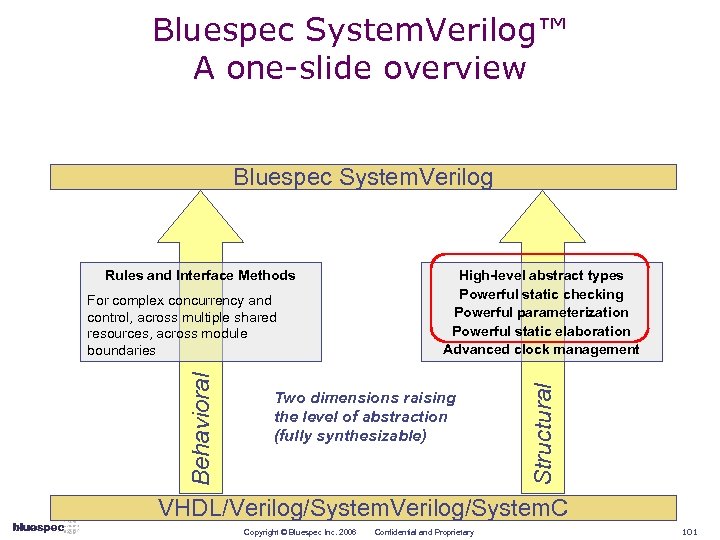

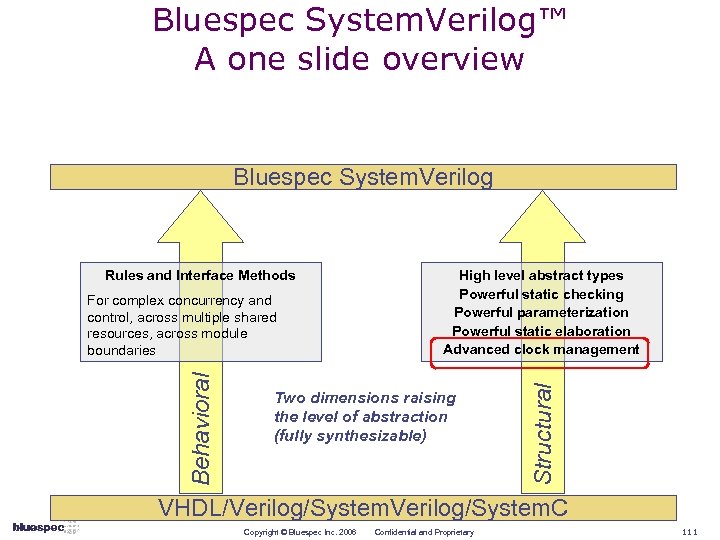

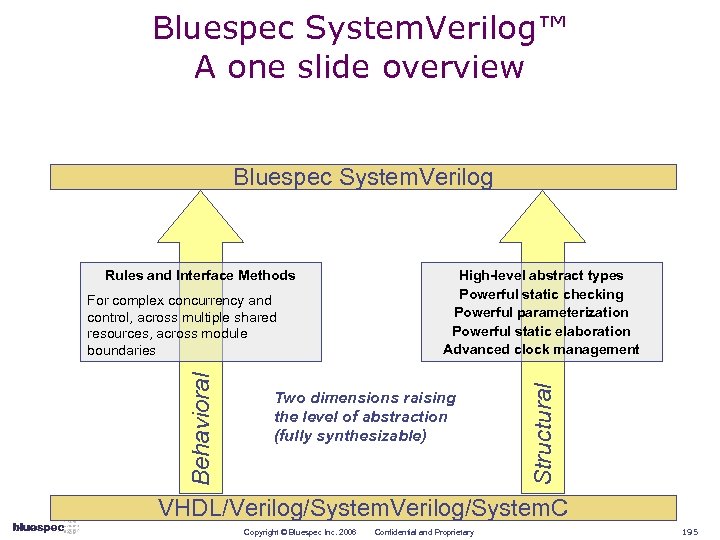

Bluespec System. Verilog™ A one slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 25

Bluespec System. Verilog™ A one slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 25

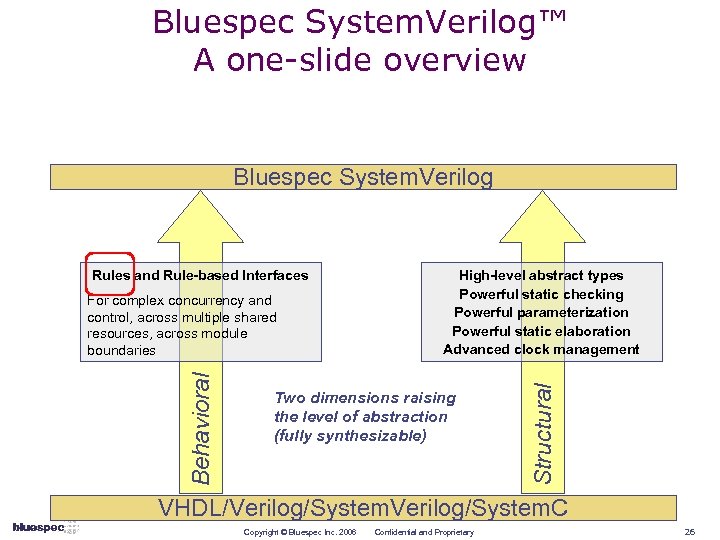

Bluespec System. Verilog™ A one-slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 26

Bluespec System. Verilog™ A one-slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 26

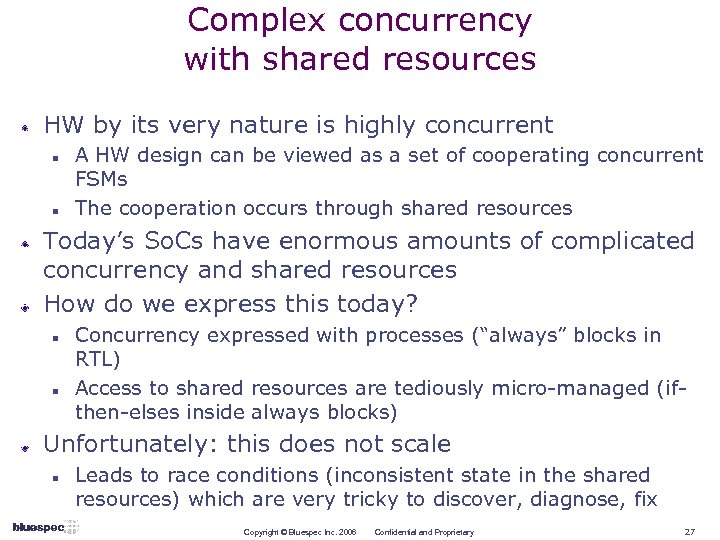

Complex concurrency with shared resources HW by its very nature is highly concurrent n n A HW design can be viewed as a set of cooperating concurrent FSMs The cooperation occurs through shared resources Today’s So. Cs have enormous amounts of complicated concurrency and shared resources How do we express this today? n n Concurrency expressed with processes (“always” blocks in RTL) Access to shared resources are tediously micro-managed (ifthen-elses inside always blocks) Unfortunately: this does not scale n Leads to race conditions (inconsistent state in the shared resources) which are very tricky to discover, diagnose, fix Copyright © Bluespec Inc. 2006 Confidential and Proprietary 27

Complex concurrency with shared resources HW by its very nature is highly concurrent n n A HW design can be viewed as a set of cooperating concurrent FSMs The cooperation occurs through shared resources Today’s So. Cs have enormous amounts of complicated concurrency and shared resources How do we express this today? n n Concurrency expressed with processes (“always” blocks in RTL) Access to shared resources are tediously micro-managed (ifthen-elses inside always blocks) Unfortunately: this does not scale n Leads to race conditions (inconsistent state in the shared resources) which are very tricky to discover, diagnose, fix Copyright © Bluespec Inc. 2006 Confidential and Proprietary 27

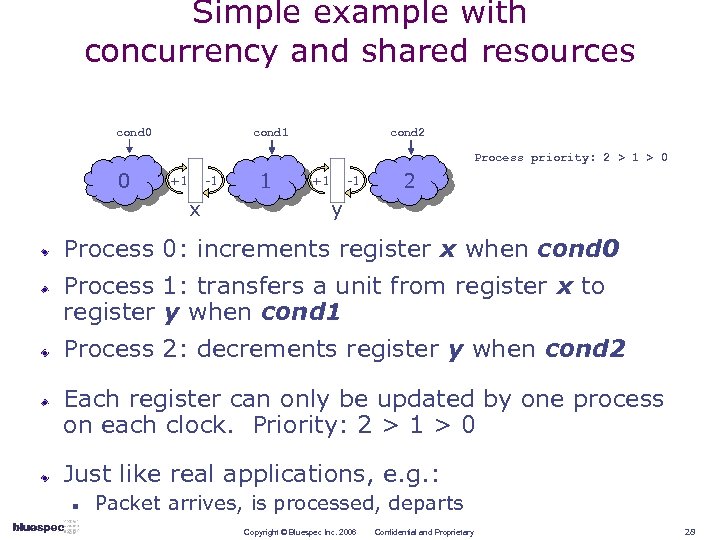

Simple example with concurrency and shared resources cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 x 1 +1 -1 2 y Process 0: increments register x when cond 0 Process 1: transfers a unit from register x to register y when cond 1 Process 2: decrements register y when cond 2 Each register can only be updated by one process on each clock. Priority: 2 > 1 > 0 Just like real applications, e. g. : n Packet arrives, is processed, departs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 28

Simple example with concurrency and shared resources cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 x 1 +1 -1 2 y Process 0: increments register x when cond 0 Process 1: transfers a unit from register x to register y when cond 1 Process 2: decrements register y when cond 2 Each register can only be updated by one process on each clock. Priority: 2 > 1 > 0 Just like real applications, e. g. : n Packet arrives, is processed, departs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 28

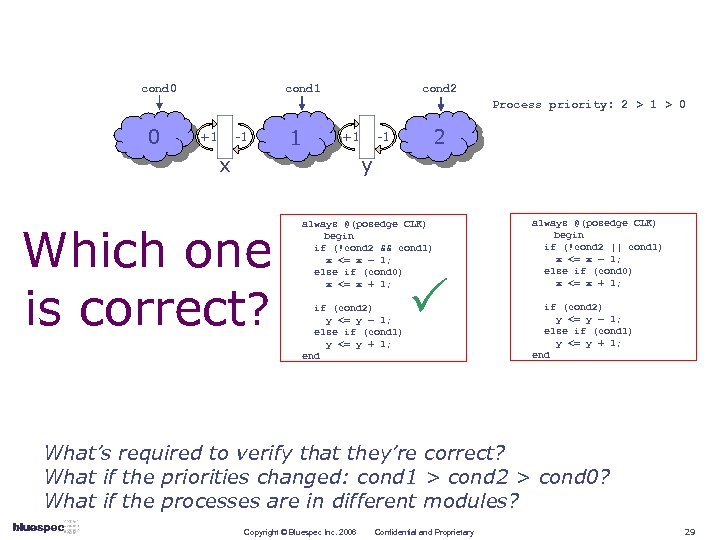

cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 1 +1 x -1 2 y Which one is correct? always @(posedge CLK) begin if (!cond 2 && cond 1) x <= x – 1; else if (cond 0) x <= x + 1; always @(posedge CLK) begin if (!cond 2 || cond 1) x <= x – 1; else if (cond 0) x <= x + 1; if (cond 2) y <= y – 1; else if (cond 1) y <= y + 1; end What’s required to verify that they’re correct? What if the priorities changed: cond 1 > cond 2 > cond 0? What if the processes are in different modules? Copyright © Bluespec Inc. 2006 Confidential and Proprietary 29

cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 1 +1 x -1 2 y Which one is correct? always @(posedge CLK) begin if (!cond 2 && cond 1) x <= x – 1; else if (cond 0) x <= x + 1; always @(posedge CLK) begin if (!cond 2 || cond 1) x <= x – 1; else if (cond 0) x <= x + 1; if (cond 2) y <= y – 1; else if (cond 1) y <= y + 1; end What’s required to verify that they’re correct? What if the priorities changed: cond 1 > cond 2 > cond 0? What if the processes are in different modules? Copyright © Bluespec Inc. 2006 Confidential and Proprietary 29

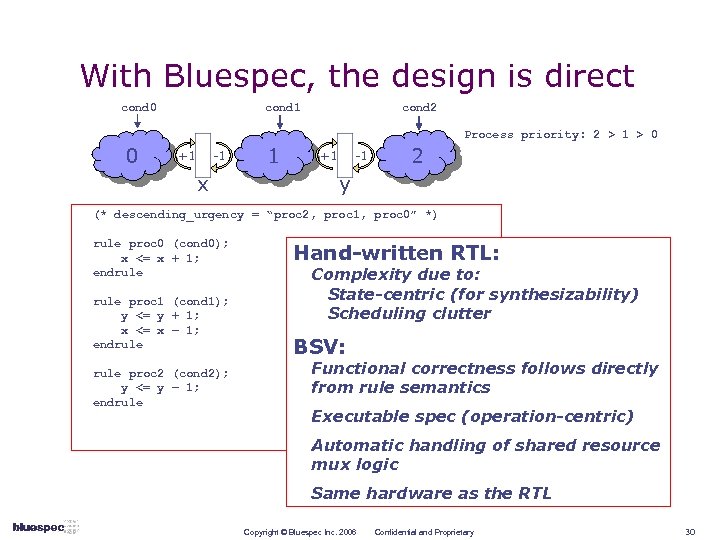

With Bluespec, the design is direct cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 x 1 +1 -1 2 y (* descending_urgency = “proc 2, proc 1, proc 0” *) rule proc 0 (cond 0); x <= x + 1; endrule proc 1 (cond 1); y <= y + 1; x <= x – 1; endrule proc 2 (cond 2); y <= y – 1; endrule Hand-written RTL: Complexity due to: State-centric (for synthesizability) Scheduling clutter BSV: Functional correctness follows directly from rule semantics Executable spec (operation-centric) Automatic handling of shared resource mux logic Same hardware as the RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 30

With Bluespec, the design is direct cond 0 cond 1 cond 2 Process priority: 2 > 1 > 0 0 +1 -1 x 1 +1 -1 2 y (* descending_urgency = “proc 2, proc 1, proc 0” *) rule proc 0 (cond 0); x <= x + 1; endrule proc 1 (cond 1); y <= y + 1; x <= x – 1; endrule proc 2 (cond 2); y <= y – 1; endrule Hand-written RTL: Complexity due to: State-centric (for synthesizability) Scheduling clutter BSV: Functional correctness follows directly from rule semantics Executable spec (operation-centric) Automatic handling of shared resource mux logic Same hardware as the RTL Copyright © Bluespec Inc. 2006 Confidential and Proprietary 30

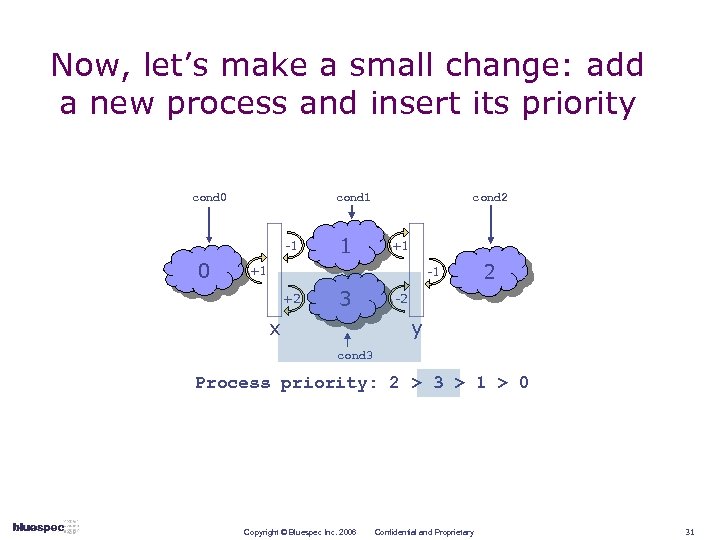

Now, let’s make a small change: add a new process and insert its priority cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 x 2 -2 y cond 3 Process priority: 2 > 3 > 1 > 0 Copyright © Bluespec Inc. 2006 Confidential and Proprietary 31

Now, let’s make a small change: add a new process and insert its priority cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 x 2 -2 y cond 3 Process priority: 2 > 3 > 1 > 0 Copyright © Bluespec Inc. 2006 Confidential and Proprietary 31

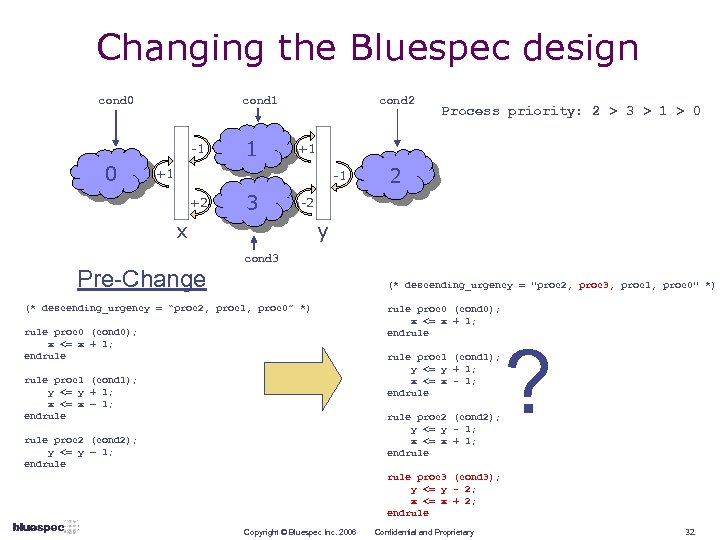

Changing the Bluespec design cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 2 -2 x Pre-Change Process priority: 2 > 3 > 1 > 0 y cond 3 (* descending_urgency = "proc 2, proc 3, proc 1, proc 0" *) (* descending_urgency = “proc 2, proc 1, proc 0” *) rule proc 0 (cond 0); x <= x + 1; endrule proc 1 (cond 1); y <= y + 1; x <= x - 1; endrule proc 1 (cond 1); y <= y + 1; x <= x – 1; endrule proc 2 (cond 2); y <= y - 1; x <= x + 1; endrule proc 2 (cond 2); y <= y – 1; endrule ? rule proc 3 (cond 3); y <= y - 2; x <= x + 2; endrule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 32

Changing the Bluespec design cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 2 -2 x Pre-Change Process priority: 2 > 3 > 1 > 0 y cond 3 (* descending_urgency = "proc 2, proc 3, proc 1, proc 0" *) (* descending_urgency = “proc 2, proc 1, proc 0” *) rule proc 0 (cond 0); x <= x + 1; endrule proc 1 (cond 1); y <= y + 1; x <= x - 1; endrule proc 1 (cond 1); y <= y + 1; x <= x – 1; endrule proc 2 (cond 2); y <= y - 1; x <= x + 1; endrule proc 2 (cond 2); y <= y – 1; endrule ? rule proc 3 (cond 3); y <= y - 2; x <= x + 2; endrule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 32

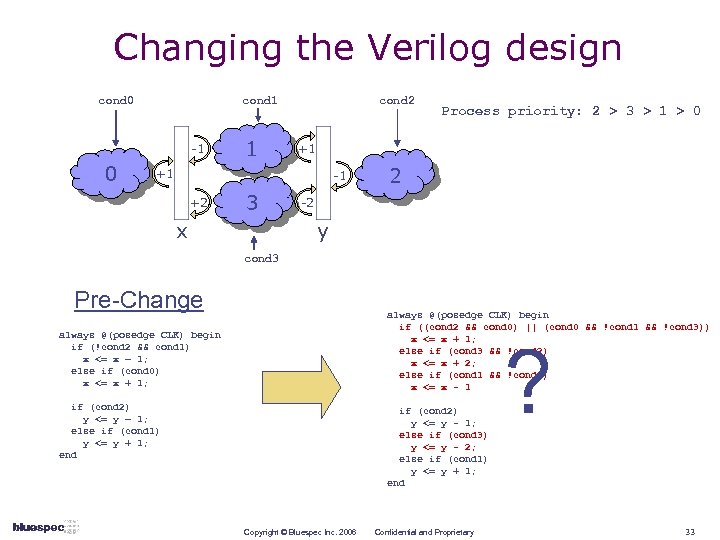

Changing the Verilog design cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 x Process priority: 2 > 3 > 1 > 0 2 -2 y cond 3 Pre-Change always @(posedge CLK) begin if ((cond 2 && cond 0) || (cond 0 && !cond 1 && !cond 3)) x <= x + 1; else if (cond 3 && !cond 2) x <= x + 2; else if (cond 1 && !cond 2) x <= x - 1 always @(posedge CLK) begin if (!cond 2 && cond 1) x <= x – 1; else if (cond 0) x <= x + 1; if (cond 2) y <= y – 1; else if (cond 1) y <= y + 1; end if (cond 2) y <= y - 1; else if (cond 3) y <= y - 2; else if (cond 1) y <= y + 1; end Copyright © Bluespec Inc. 2006 Confidential and Proprietary ? 33

Changing the Verilog design cond 0 cond 1 -1 0 1 cond 2 +1 +1 -1 +2 3 x Process priority: 2 > 3 > 1 > 0 2 -2 y cond 3 Pre-Change always @(posedge CLK) begin if ((cond 2 && cond 0) || (cond 0 && !cond 1 && !cond 3)) x <= x + 1; else if (cond 3 && !cond 2) x <= x + 2; else if (cond 1 && !cond 2) x <= x - 1 always @(posedge CLK) begin if (!cond 2 && cond 1) x <= x – 1; else if (cond 0) x <= x + 1; if (cond 2) y <= y – 1; else if (cond 1) y <= y + 1; end if (cond 2) y <= y - 1; else if (cond 3) y <= y - 2; else if (cond 1) y <= y + 1; end Copyright © Bluespec Inc. 2006 Confidential and Proprietary ? 33

Key Benefits Executable specifications Rapid changes But, with fine-grained control of RTL: n n n Define the optimal architecture/microarchitecture Debug at the source OR RTL level – designer understands both The Quality of Results (Qo. R) of RTL! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 34

Key Benefits Executable specifications Rapid changes But, with fine-grained control of RTL: n n n Define the optimal architecture/microarchitecture Debug at the source OR RTL level – designer understands both The Quality of Results (Qo. R) of RTL! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 34

The concurrency complexities illustrated in the simple example are greatly magnified in real designs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 35

The concurrency complexities illustrated in the simple example are greatly magnified in real designs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 35

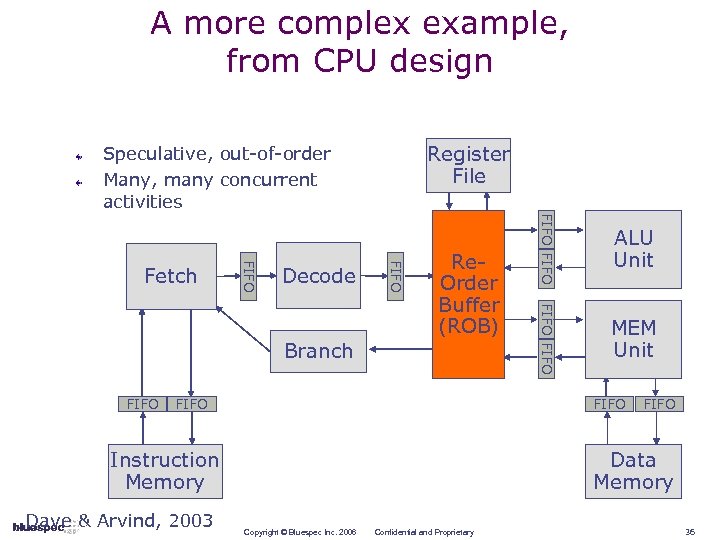

A more complex example, from CPU design Register File Speculative, out-of-order Many, many concurrent activities Branch FIFO MEM Unit FIFO Instruction Memory Dave & Arvind, 2003 FIFO Re. Order Buffer (ROB) FIFO Decode FIFO Fetch ALU Unit FIFO Data Memory Copyright © Bluespec Inc. 2006 Confidential and Proprietary 36

A more complex example, from CPU design Register File Speculative, out-of-order Many, many concurrent activities Branch FIFO MEM Unit FIFO Instruction Memory Dave & Arvind, 2003 FIFO Re. Order Buffer (ROB) FIFO Decode FIFO Fetch ALU Unit FIFO Data Memory Copyright © Bluespec Inc. 2006 Confidential and Proprietary 36

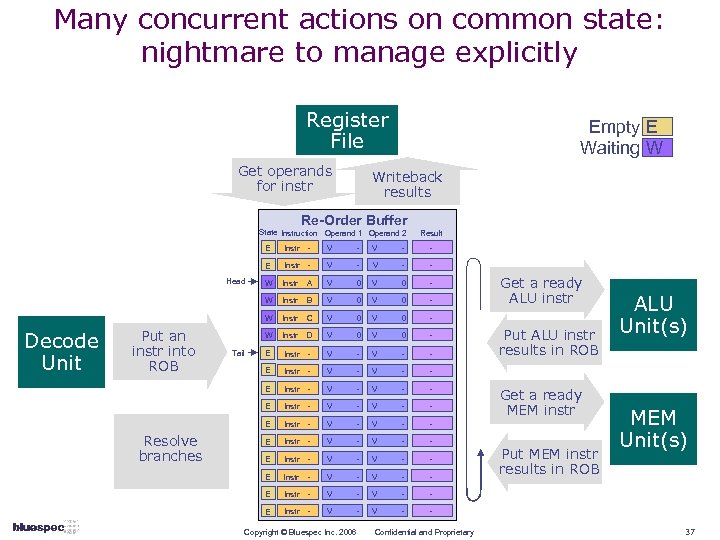

Many concurrent actions on common state: nightmare to manage explicitly Register File Get operands for instr Empty E Waiting W Writeback results Re-Order Buffer State Instruction Operand 1 Operand 2 Result E - - Instr - V - - W Instr A V 0 - Instr B V 0 - Instr C V 0 - Instr D V 0 - E Instr - V - V - - E Resolve branches V W Instr - V - V - - E Instr - V - - E Tail - W Put an instr into ROB V W Decode Unit - E Head Instr - V - - Copyright © Bluespec Inc. 2006 Confidential and Proprietary Get a ready ALU instr Put ALU instr results in ROB Get a ready MEM instr Put MEM instr results in ROB ALU Unit(s) MEM Unit(s) 37

Many concurrent actions on common state: nightmare to manage explicitly Register File Get operands for instr Empty E Waiting W Writeback results Re-Order Buffer State Instruction Operand 1 Operand 2 Result E - - Instr - V - - W Instr A V 0 - Instr B V 0 - Instr C V 0 - Instr D V 0 - E Instr - V - V - - E Resolve branches V W Instr - V - V - - E Instr - V - - E Tail - W Put an instr into ROB V W Decode Unit - E Head Instr - V - - Copyright © Bluespec Inc. 2006 Confidential and Proprietary Get a ready ALU instr Put ALU instr results in ROB Get a ready MEM instr Put MEM instr results in ROB ALU Unit(s) MEM Unit(s) 37

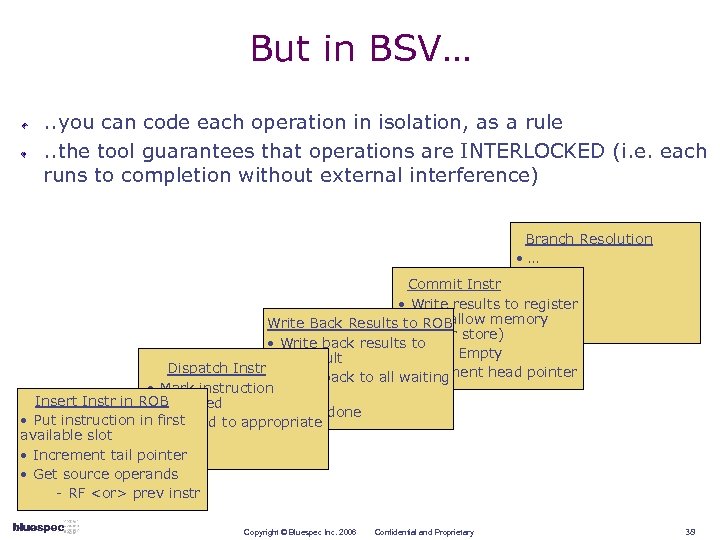

But in BSV…. . you can code each operation in isolation, as a rule. . the tool guarantees that operations are INTERLOCKED (i. e. each runs to completion without external interference) Branch Resolution • … Commit Instr • … • Write results to register Write Back Resultsfile ROB to (or allow memory write for store) • Write back results to • Set to Empty instr result Dispatch Instr • Write back to all • Increment head pointer waiting • Mark instruction tags Insert Instr in ROB dispatched • Set to done • Put instruction in first • Forward to appropriate available slot unit • Increment tail pointer • Get source operands - RF

But in BSV…. . you can code each operation in isolation, as a rule. . the tool guarantees that operations are INTERLOCKED (i. e. each runs to completion without external interference) Branch Resolution • … Commit Instr • … • Write results to register Write Back Resultsfile ROB to (or allow memory write for store) • Write back results to • Set to Empty instr result Dispatch Instr • Write back to all • Increment head pointer waiting • Mark instruction tags Insert Instr in ROB dispatched • Set to done • Put instruction in first • Forward to appropriate available slot unit • Increment tail pointer • Get source operands - RF

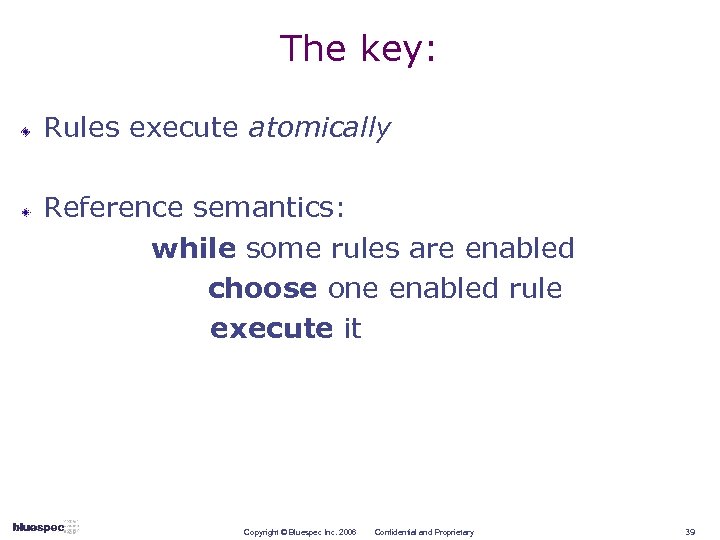

The key: Rules execute atomically Reference semantics: while some rules are enabled choose one enabled rule execute it Copyright © Bluespec Inc. 2006 Confidential and Proprietary 39

The key: Rules execute atomically Reference semantics: while some rules are enabled choose one enabled rule execute it Copyright © Bluespec Inc. 2006 Confidential and Proprietary 39

Atomicity atomic Copyright © Bluespec Inc. 2006 Confidential and Proprietary 40

Atomicity atomic Copyright © Bluespec Inc. 2006 Confidential and Proprietary 40

Atomicity ατομος Copyright © Bluespec Inc. 2006 Confidential and Proprietary 41

Atomicity ατομος Copyright © Bluespec Inc. 2006 Confidential and Proprietary 41

Atomicity a_tomic n not w w w asymmetric atypical amoral Copyright © Bluespec Inc. 2006 Confidential and Proprietary 42

Atomicity a_tomic n not w w w asymmetric atypical amoral Copyright © Bluespec Inc. 2006 Confidential and Proprietary 42

Atomicity a_tomic n not w w w n asymmetric atypical amoral cut w w microtome Tomography appendectomy tome (of a multi_volume book) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 43

Atomicity a_tomic n not w w w n asymmetric atypical amoral cut w w microtome Tomography appendectomy tome (of a multi_volume book) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 43

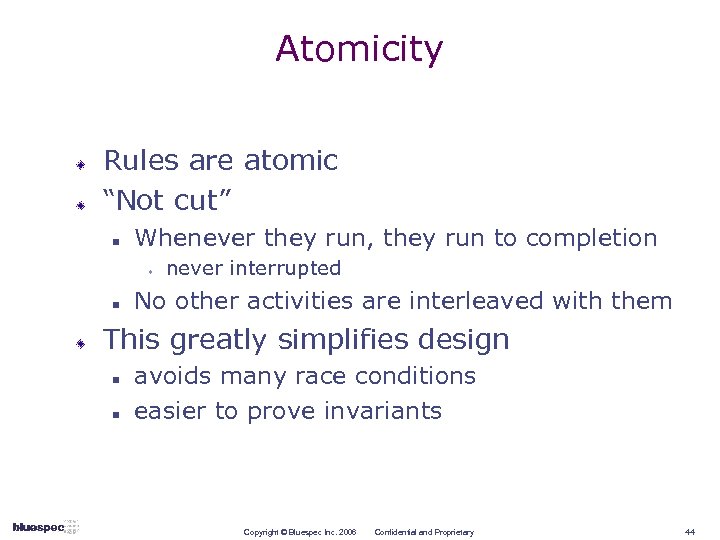

Atomicity Rules are atomic “Not cut” n Whenever they run, they run to completion w n never interrupted No other activities are interleaved with them This greatly simplifies design n n avoids many race conditions easier to prove invariants Copyright © Bluespec Inc. 2006 Confidential and Proprietary 44

Atomicity Rules are atomic “Not cut” n Whenever they run, they run to completion w n never interrupted No other activities are interleaved with them This greatly simplifies design n n avoids many race conditions easier to prove invariants Copyright © Bluespec Inc. 2006 Confidential and Proprietary 44

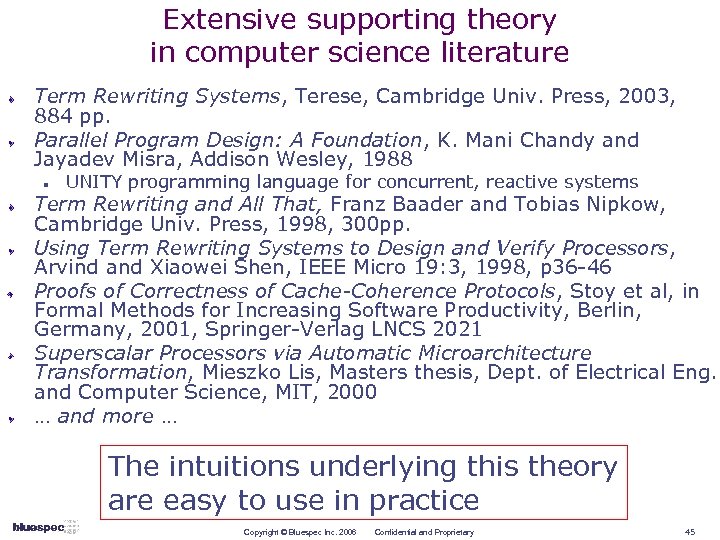

Extensive supporting theory in computer science literature Term Rewriting Systems, Terese, Cambridge Univ. Press, 2003, 884 pp. Parallel Program Design: A Foundation, K. Mani Chandy and Jayadev Misra, Addison Wesley, 1988 n UNITY programming language for concurrent, reactive systems Term Rewriting and All That, Franz Baader and Tobias Nipkow, Cambridge Univ. Press, 1998, 300 pp. Using Term Rewriting Systems to Design and Verify Processors, Arvind and Xiaowei Shen, IEEE Micro 19: 3, 1998, p 36 -46 Proofs of Correctness of Cache-Coherence Protocols, Stoy et al, in Formal Methods for Increasing Software Productivity, Berlin, Germany, 2001, Springer-Verlag LNCS 2021 Superscalar Processors via Automatic Microarchitecture Transformation, Mieszko Lis, Masters thesis, Dept. of Electrical Eng. and Computer Science, MIT, 2000 … and more … The intuitions underlying this theory are easy to use in practice Copyright © Bluespec Inc. 2006 Confidential and Proprietary 45

Extensive supporting theory in computer science literature Term Rewriting Systems, Terese, Cambridge Univ. Press, 2003, 884 pp. Parallel Program Design: A Foundation, K. Mani Chandy and Jayadev Misra, Addison Wesley, 1988 n UNITY programming language for concurrent, reactive systems Term Rewriting and All That, Franz Baader and Tobias Nipkow, Cambridge Univ. Press, 1998, 300 pp. Using Term Rewriting Systems to Design and Verify Processors, Arvind and Xiaowei Shen, IEEE Micro 19: 3, 1998, p 36 -46 Proofs of Correctness of Cache-Coherence Protocols, Stoy et al, in Formal Methods for Increasing Software Productivity, Berlin, Germany, 2001, Springer-Verlag LNCS 2021 Superscalar Processors via Automatic Microarchitecture Transformation, Mieszko Lis, Masters thesis, Dept. of Electrical Eng. and Computer Science, MIT, 2000 … and more … The intuitions underlying this theory are easy to use in practice Copyright © Bluespec Inc. 2006 Confidential and Proprietary 45

Synthesizing Rules into efficient clocked synchronous HW - Automatically generates correct HW for the most error-prone parts of hand-written RTL - While retaining transparency, predictability and designer control Copyright © Bluespec Inc. 2006 Confidential and Proprietary 46

Synthesizing Rules into efficient clocked synchronous HW - Automatically generates correct HW for the most error-prone parts of hand-written RTL - While retaining transparency, predictability and designer control Copyright © Bluespec Inc. 2006 Confidential and Proprietary 46

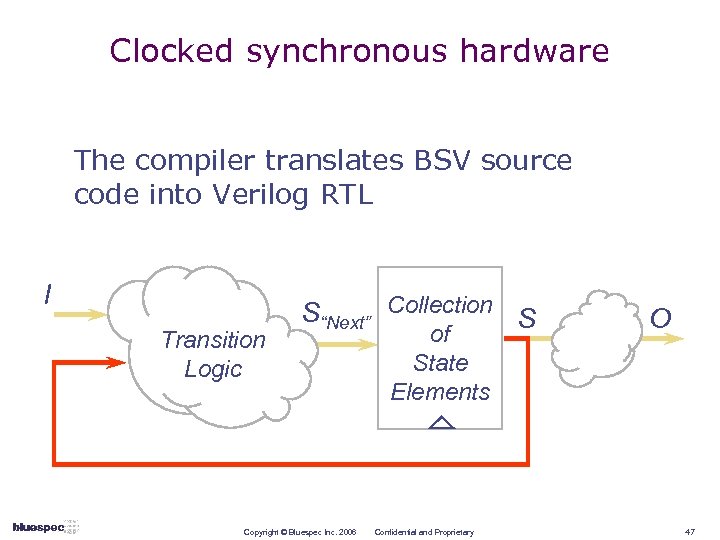

Clocked synchronous hardware The compiler translates BSV source code into Verilog RTL I Transition Logic S“Next” Collection S Copyright © Bluespec Inc. 2006 of State Elements Confidential and Proprietary O 47

Clocked synchronous hardware The compiler translates BSV source code into Verilog RTL I Transition Logic S“Next” Collection S Copyright © Bluespec Inc. 2006 of State Elements Confidential and Proprietary O 47

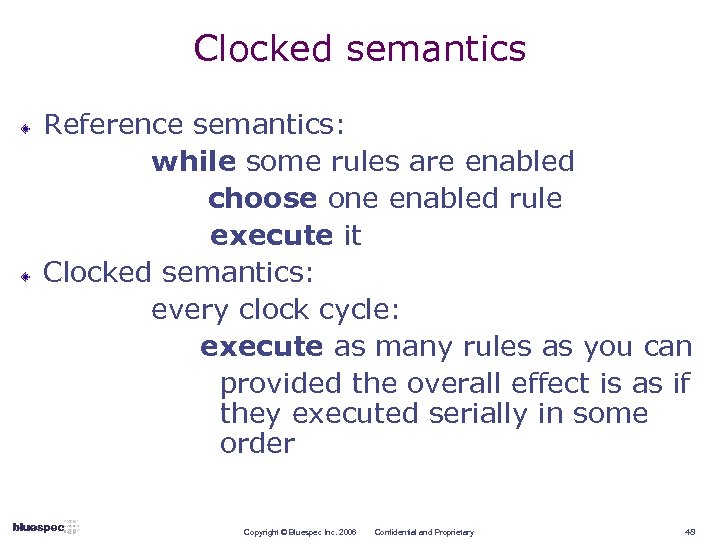

Clocked semantics Reference semantics: while some rules are enabled choose one enabled rule execute it Clocked semantics: every clock cycle: execute as many rules as you can provided the overall effect is as if they executed serially in some order Copyright © Bluespec Inc. 2006 Confidential and Proprietary 48

Clocked semantics Reference semantics: while some rules are enabled choose one enabled rule execute it Clocked semantics: every clock cycle: execute as many rules as you can provided the overall effect is as if they executed serially in some order Copyright © Bluespec Inc. 2006 Confidential and Proprietary 48

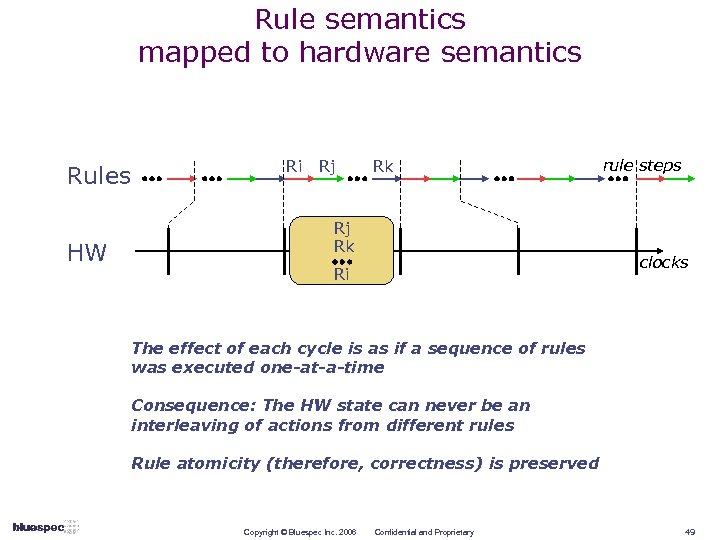

Rule semantics mapped to hardware semantics Rules HW Ri Rj Rk rule steps clocks Ri The effect of each cycle is as if a sequence of rules was executed one-at-a-time Consequence: The HW state can never be an interleaving of actions from different rules Rule atomicity (therefore, correctness) is preserved Copyright © Bluespec Inc. 2006 Confidential and Proprietary 49

Rule semantics mapped to hardware semantics Rules HW Ri Rj Rk rule steps clocks Ri The effect of each cycle is as if a sequence of rules was executed one-at-a-time Consequence: The HW state can never be an interleaving of actions from different rules Rule atomicity (therefore, correctness) is preserved Copyright © Bluespec Inc. 2006 Confidential and Proprietary 49

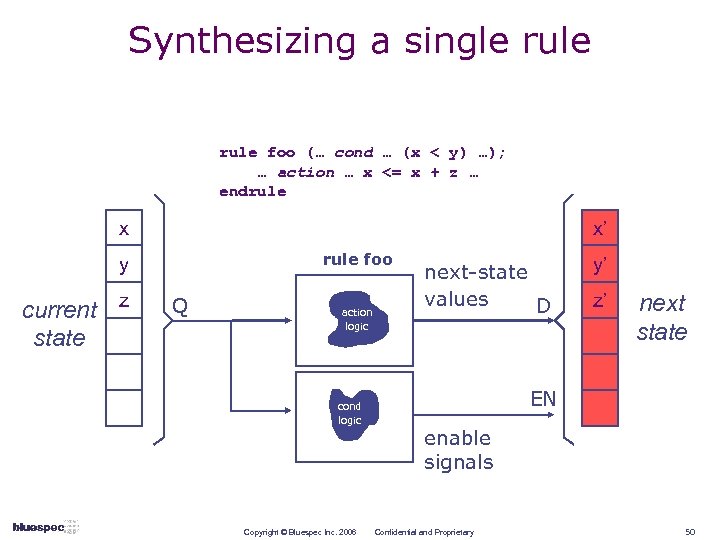

Synthesizing a single rule foo (… cond … (x < y) …); … action … x <= x + z … endrule x x’ rule foo y current z state Q action logic cond logic Copyright © Bluespec Inc. 2006 next-state values D y’ z’ next state EN enable signals Confidential and Proprietary 50

Synthesizing a single rule foo (… cond … (x < y) …); … action … x <= x + z … endrule x x’ rule foo y current z state Q action logic cond logic Copyright © Bluespec Inc. 2006 next-state values D y’ z’ next state EN enable signals Confidential and Proprietary 50

Synthesizing multiple rules Different rules can read/write common state. Therefore, n n Need multiplexing of next state values into shared state element inputs Need control of which rules get to update next state elements w w Control of next state “enables” Control of next state data multiplexers Copyright © Bluespec Inc. 2006 Confidential and Proprietary 51

Synthesizing multiple rules Different rules can read/write common state. Therefore, n n Need multiplexing of next state values into shared state element inputs Need control of which rules get to update next state elements w w Control of next state “enables” Control of next state data multiplexers Copyright © Bluespec Inc. 2006 Confidential and Proprietary 51

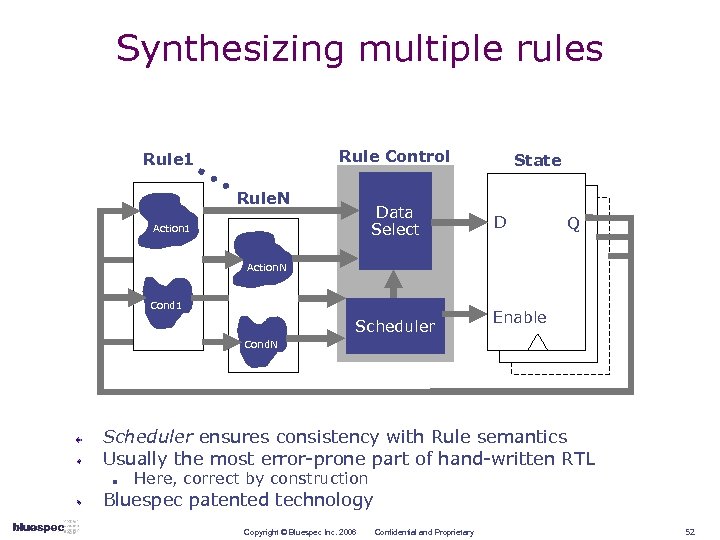

Synthesizing multiple rules Rule Control Rule 1 Rule. N Data Select Action 1 State D Q Action. N Cond 1 Scheduler Enable Cond. N Scheduler ensures consistency with Rule semantics Usually the most error-prone part of hand-written RTL n Here, correct by construction Bluespec patented technology Copyright © Bluespec Inc. 2006 Confidential and Proprietary 52

Synthesizing multiple rules Rule Control Rule 1 Rule. N Data Select Action 1 State D Q Action. N Cond 1 Scheduler Enable Cond. N Scheduler ensures consistency with Rule semantics Usually the most error-prone part of hand-written RTL n Here, correct by construction Bluespec patented technology Copyright © Bluespec Inc. 2006 Confidential and Proprietary 52

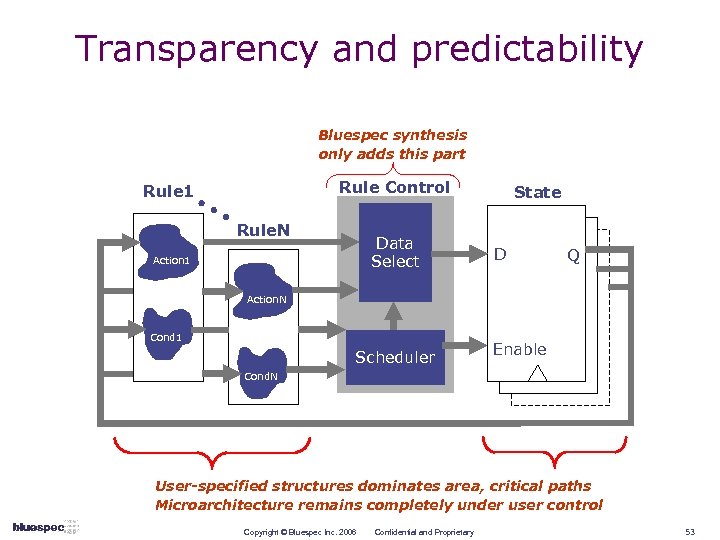

Transparency and predictability Bluespec synthesis only adds this part Rule Control Rule 1 Rule. N Data Select Action 1 State D Q Action. N Cond 1 Scheduler Enable Cond. N User-specified structures dominates area, critical paths Microarchitecture remains completely under user control Copyright © Bluespec Inc. 2006 Confidential and Proprietary 53

Transparency and predictability Bluespec synthesis only adds this part Rule Control Rule 1 Rule. N Data Select Action 1 State D Q Action. N Cond 1 Scheduler Enable Cond. N User-specified structures dominates area, critical paths Microarchitecture remains completely under user control Copyright © Bluespec Inc. 2006 Confidential and Proprietary 53

Comparing BSV to traditional “Behavioral Synthesis” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 54

Comparing BSV to traditional “Behavioral Synthesis” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 54

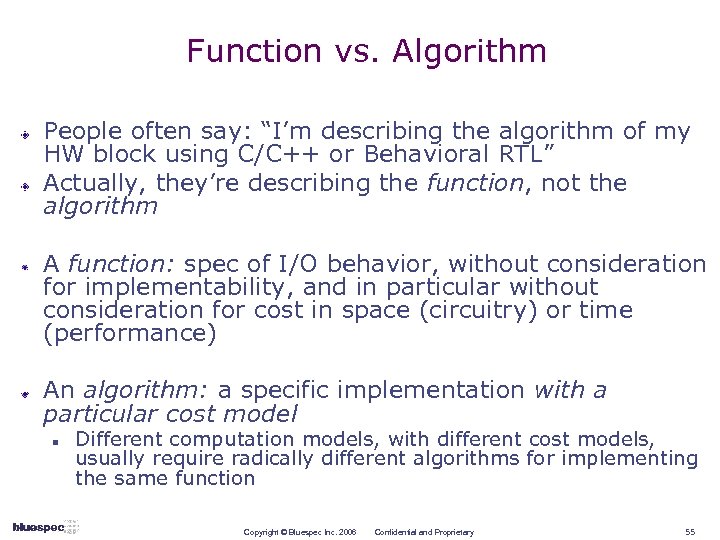

Function vs. Algorithm People often say: “I’m describing the algorithm of my HW block using C/C++ or Behavioral RTL” Actually, they’re describing the function, not the algorithm A function: spec of I/O behavior, without consideration for implementability, and in particular without consideration for cost in space (circuitry) or time (performance) An algorithm: a specific implementation with a particular cost model n Different computation models, with different cost models, usually require radically different algorithms for implementing the same function Copyright © Bluespec Inc. 2006 Confidential and Proprietary 55

Function vs. Algorithm People often say: “I’m describing the algorithm of my HW block using C/C++ or Behavioral RTL” Actually, they’re describing the function, not the algorithm A function: spec of I/O behavior, without consideration for implementability, and in particular without consideration for cost in space (circuitry) or time (performance) An algorithm: a specific implementation with a particular cost model n Different computation models, with different cost models, usually require radically different algorithms for implementing the same function Copyright © Bluespec Inc. 2006 Confidential and Proprietary 55

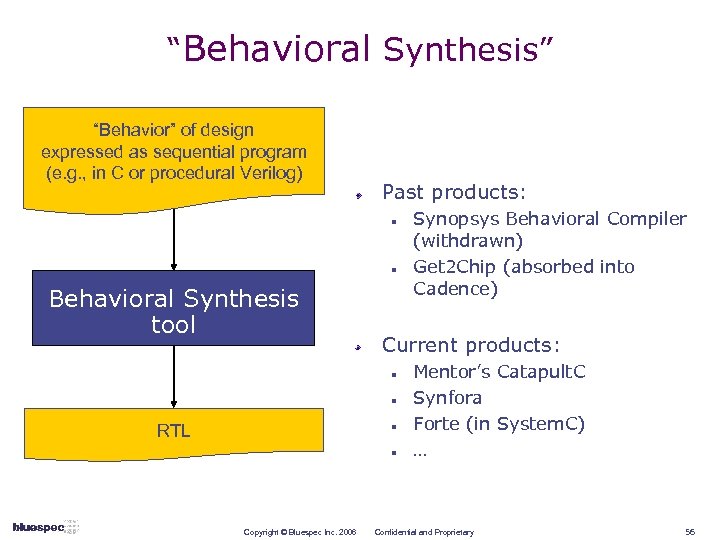

“Behavioral Synthesis” “Behavior” of design expressed as sequential program (e. g. , in C or procedural Verilog) Past products: n n Behavioral Synthesis tool Current products: n n RTL n n Copyright © Bluespec Inc. 2006 Synopsys Behavioral Compiler (withdrawn) Get 2 Chip (absorbed into Cadence) Mentor’s Catapult. C Synfora Forte (in System. C) … Confidential and Proprietary 56

“Behavioral Synthesis” “Behavior” of design expressed as sequential program (e. g. , in C or procedural Verilog) Past products: n n Behavioral Synthesis tool Current products: n n RTL n n Copyright © Bluespec Inc. 2006 Synopsys Behavioral Compiler (withdrawn) Get 2 Chip (absorbed into Cadence) Mentor’s Catapult. C Synfora Forte (in System. C) … Confidential and Proprietary 56

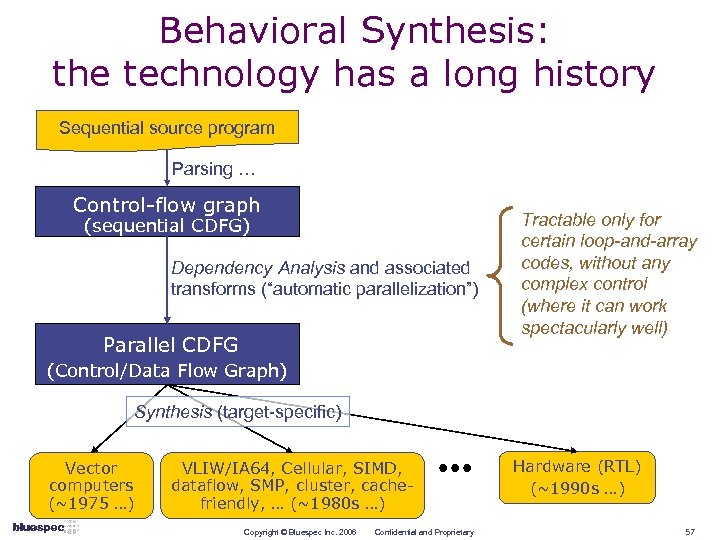

Behavioral Synthesis: the technology has a long history Sequential source program Parsing … Control-flow graph (sequential CDFG) Dependency Analysis and associated transforms (“automatic parallelization”) Parallel CDFG Tractable only for certain loop-and-array codes, without any complex control (where it can work spectacularly well) (Control/Data Flow Graph) Synthesis (target-specific) Vector computers (~1975 …) VLIW/IA 64, Cellular, SIMD, dataflow, SMP, cluster, cachefriendly, … (~1980 s …) Copyright © Bluespec Inc. 2006 Confidential and Proprietary Hardware (RTL) (~1990 s …) 57

Behavioral Synthesis: the technology has a long history Sequential source program Parsing … Control-flow graph (sequential CDFG) Dependency Analysis and associated transforms (“automatic parallelization”) Parallel CDFG Tractable only for certain loop-and-array codes, without any complex control (where it can work spectacularly well) (Control/Data Flow Graph) Synthesis (target-specific) Vector computers (~1975 …) VLIW/IA 64, Cellular, SIMD, dataflow, SMP, cluster, cachefriendly, … (~1980 s …) Copyright © Bluespec Inc. 2006 Confidential and Proprietary Hardware (RTL) (~1990 s …) 57

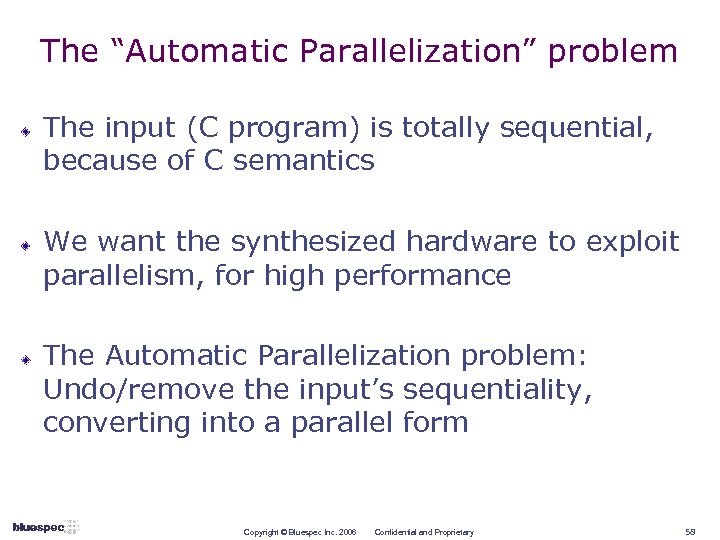

The “Automatic Parallelization” problem The input (C program) is totally sequential, because of C semantics We want the synthesized hardware to exploit parallelism, for high performance The Automatic Parallelization problem: Undo/remove the input’s sequentiality, converting into a parallel form Copyright © Bluespec Inc. 2006 Confidential and Proprietary 58

The “Automatic Parallelization” problem The input (C program) is totally sequential, because of C semantics We want the synthesized hardware to exploit parallelism, for high performance The Automatic Parallelization problem: Undo/remove the input’s sequentiality, converting into a parallel form Copyright © Bluespec Inc. 2006 Confidential and Proprietary 58

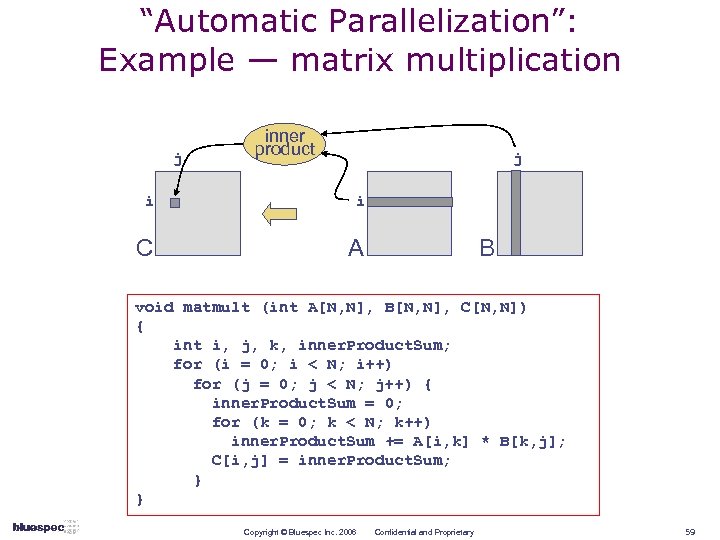

“Automatic Parallelization”: Example — matrix multiplication j inner product j i i C A B void matmult (int A[N, N], B[N, N], C[N, N]) { int i, j, k, inner. Product. Sum; for (i = 0; i < N; i++) for (j = 0; j < N; j++) { inner. Product. Sum = 0; for (k = 0; k < N; k++) inner. Product. Sum += A[i, k] * B[k, j]; C[i, j] = inner. Product. Sum; } } Copyright © Bluespec Inc. 2006 Confidential and Proprietary 59

“Automatic Parallelization”: Example — matrix multiplication j inner product j i i C A B void matmult (int A[N, N], B[N, N], C[N, N]) { int i, j, k, inner. Product. Sum; for (i = 0; i < N; i++) for (j = 0; j < N; j++) { inner. Product. Sum = 0; for (k = 0; k < N; k++) inner. Product. Sum += A[i, k] * B[k, j]; C[i, j] = inner. Product. Sum; } } Copyright © Bluespec Inc. 2006 Confidential and Proprietary 59

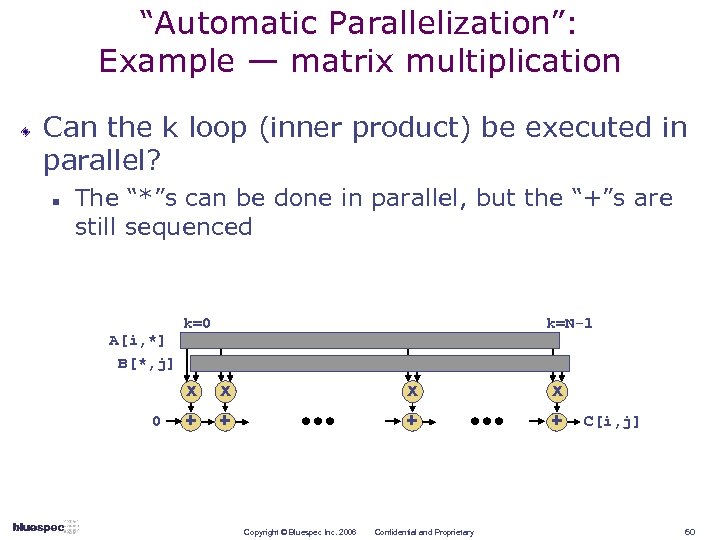

“Automatic Parallelization”: Example — matrix multiplication Can the k loop (inner product) be executed in parallel? n The “*”s can be done in parallel, but the “+”s are still sequenced A[i, *] B[*, j] k=0 k=N-1 x 0 x x x + + Copyright © Bluespec Inc. 2006 Confidential and Proprietary C[i, j] 60

“Automatic Parallelization”: Example — matrix multiplication Can the k loop (inner product) be executed in parallel? n The “*”s can be done in parallel, but the “+”s are still sequenced A[i, *] B[*, j] k=0 k=N-1 x 0 x x x + + Copyright © Bluespec Inc. 2006 Confidential and Proprietary C[i, j] 60

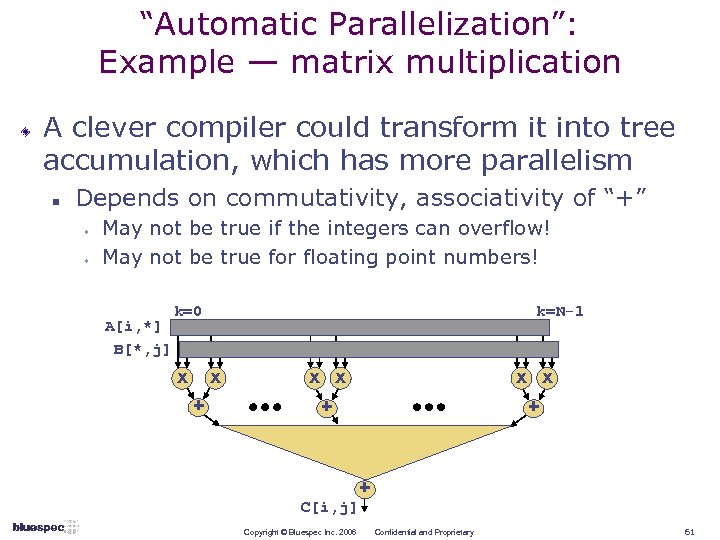

“Automatic Parallelization”: Example — matrix multiplication A clever compiler could transform it into tree accumulation, which has more parallelism n Depends on commutativity, associativity of “+” w w May not be true if the integers can overflow! May not be true for floating point numbers! A[i, *] B[*, j] k=0 x k=N-1 x + x x + + + C[i, j] Copyright © Bluespec Inc. 2006 Confidential and Proprietary 61

“Automatic Parallelization”: Example — matrix multiplication A clever compiler could transform it into tree accumulation, which has more parallelism n Depends on commutativity, associativity of “+” w w May not be true if the integers can overflow! May not be true for floating point numbers! A[i, *] B[*, j] k=0 x k=N-1 x + x x + + + C[i, j] Copyright © Bluespec Inc. 2006 Confidential and Proprietary 61

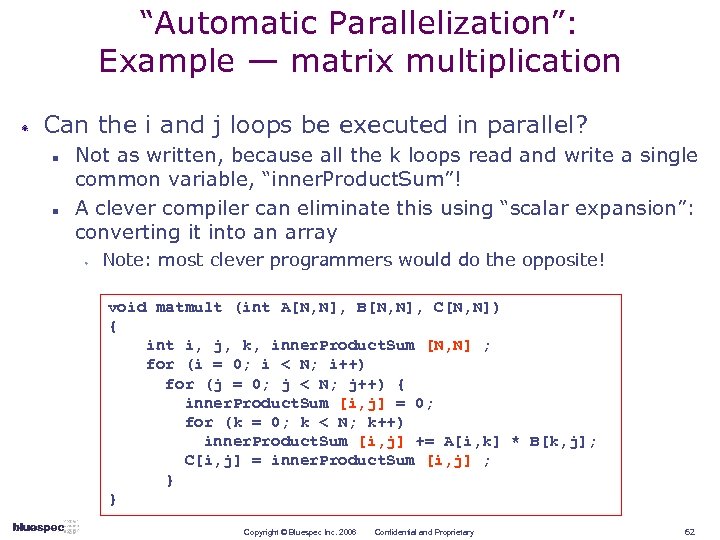

“Automatic Parallelization”: Example — matrix multiplication Can the i and j loops be executed in parallel? n n Not as written, because all the k loops read and write a single common variable, “inner. Product. Sum”! A clever compiler can eliminate this using “scalar expansion”: converting it into an array w Note: most clever programmers would do the opposite! void matmult (int A[N, N], B[N, N], C[N, N]) { int i, j, k, inner. Product. Sum [N, N] ; for (i = 0; i < N; i++) for (j = 0; j < N; j++) { inner. Product. Sum [i, j] = 0; for (k = 0; k < N; k++) inner. Product. Sum [i, j] += A[i, k] * B[k, j]; C[i, j] = inner. Product. Sum [i, j] ; } } Copyright © Bluespec Inc. 2006 Confidential and Proprietary 62

“Automatic Parallelization”: Example — matrix multiplication Can the i and j loops be executed in parallel? n n Not as written, because all the k loops read and write a single common variable, “inner. Product. Sum”! A clever compiler can eliminate this using “scalar expansion”: converting it into an array w Note: most clever programmers would do the opposite! void matmult (int A[N, N], B[N, N], C[N, N]) { int i, j, k, inner. Product. Sum [N, N] ; for (i = 0; i < N; i++) for (j = 0; j < N; j++) { inner. Product. Sum [i, j] = 0; for (k = 0; k < N; k++) inner. Product. Sum [i, j] += A[i, k] * B[k, j]; C[i, j] = inner. Product. Sum [i, j] ; } } Copyright © Bluespec Inc. 2006 Confidential and Proprietary 62

Automatic Parallelization: history Studied extensively since the 1960 s (vectorizing/ parallelizing/ VLIW/ EPIC software compilers) Fundamental problems: n n Complex control structures, pointers and aliasing (memory indirection), dynamic data allocation, … are all difficult/ impossible to parallelize automatically C is often a bad starting point: best parallel algorithm for a given function can be quite different from best sequential algorithm w Parallel algorithm designers prefer to start with a clean slate from a functional specification, not a C algorithm with unnecessary sequential baggage Has succeeded only in limited domain: simple array-based loop nests n SW community has abandoned automatic parallelization of generalpurpose programs; is mostly used only for scientific/ technical computing, linear algebra, … Copyright © Bluespec Inc. 2006 Confidential and Proprietary 63

Automatic Parallelization: history Studied extensively since the 1960 s (vectorizing/ parallelizing/ VLIW/ EPIC software compilers) Fundamental problems: n n Complex control structures, pointers and aliasing (memory indirection), dynamic data allocation, … are all difficult/ impossible to parallelize automatically C is often a bad starting point: best parallel algorithm for a given function can be quite different from best sequential algorithm w Parallel algorithm designers prefer to start with a clean slate from a functional specification, not a C algorithm with unnecessary sequential baggage Has succeeded only in limited domain: simple array-based loop nests n SW community has abandoned automatic parallelization of generalpurpose programs; is mostly used only for scientific/ technical computing, linear algebra, … Copyright © Bluespec Inc. 2006 Confidential and Proprietary 63

Automatic Parallelization: transparency, predictability, controllability Another common issue with automatic parallelization and behavioral synthesis n n Designer loses intuition and precise control over generated output Behavioral synthesis: tool decides microarchitecture based on complex optimization criteria w w w “What HW will result, with this input C program? ” “What will be the effect on the resulting HW, if I make this change to the input C program? ” “What change should I make to the input C program, to improve the HW in this way? ” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 64

Automatic Parallelization: transparency, predictability, controllability Another common issue with automatic parallelization and behavioral synthesis n n Designer loses intuition and precise control over generated output Behavioral synthesis: tool decides microarchitecture based on complex optimization criteria w w w “What HW will result, with this input C program? ” “What will be the effect on the resulting HW, if I make this change to the input C program? ” “What change should I make to the input C program, to improve the HW in this way? ” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 64

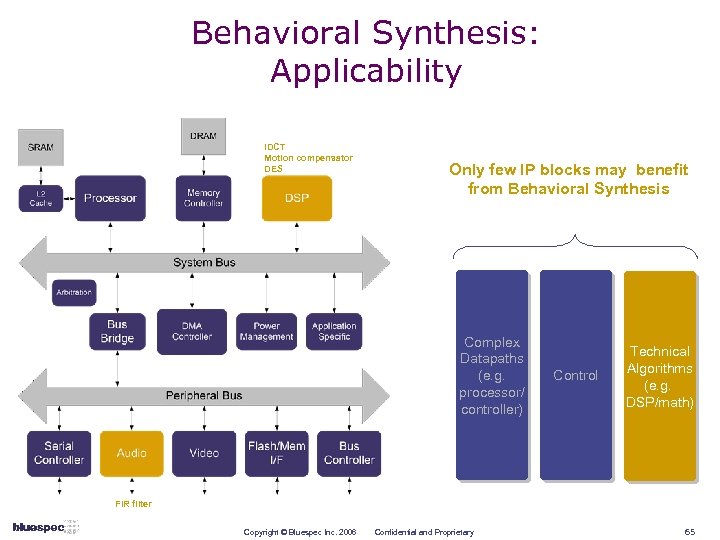

Behavioral Synthesis: Applicability IDCT Motion compensator DES Only few IP blocks may benefit from Behavioral Synthesis Complex Datapaths (e. g. processor/ controller) Control Technical Algorithms (e. g. DSP/math) FIR filter Copyright © Bluespec Inc. 2006 Confidential and Proprietary 65

Behavioral Synthesis: Applicability IDCT Motion compensator DES Only few IP blocks may benefit from Behavioral Synthesis Complex Datapaths (e. g. processor/ controller) Control Technical Algorithms (e. g. DSP/math) FIR filter Copyright © Bluespec Inc. 2006 Confidential and Proprietary 65

Comparing “Model of Time” in BSV vs. Automatic Synthesis from C/C++: completely untimed n No relationship between source model of time (sequential C code execution) and target model of time (HW clocks) BSV: untimed to timed n n n Initially, designer writes arbitrarily complex rules, i. e. , any amount of functional computation per rule Designer refines this (splitting rules, if necessary) so that the functional computation per rule is feasible in HW in a target clock speed/ technology BSV tool schedules multiple rules per clock Copyright © Bluespec Inc. 2006 Confidential and Proprietary 66

Comparing “Model of Time” in BSV vs. Automatic Synthesis from C/C++: completely untimed n No relationship between source model of time (sequential C code execution) and target model of time (HW clocks) BSV: untimed to timed n n n Initially, designer writes arbitrarily complex rules, i. e. , any amount of functional computation per rule Designer refines this (splitting rules, if necessary) so that the functional computation per rule is feasible in HW in a target clock speed/ technology BSV tool schedules multiple rules per clock Copyright © Bluespec Inc. 2006 Confidential and Proprietary 66

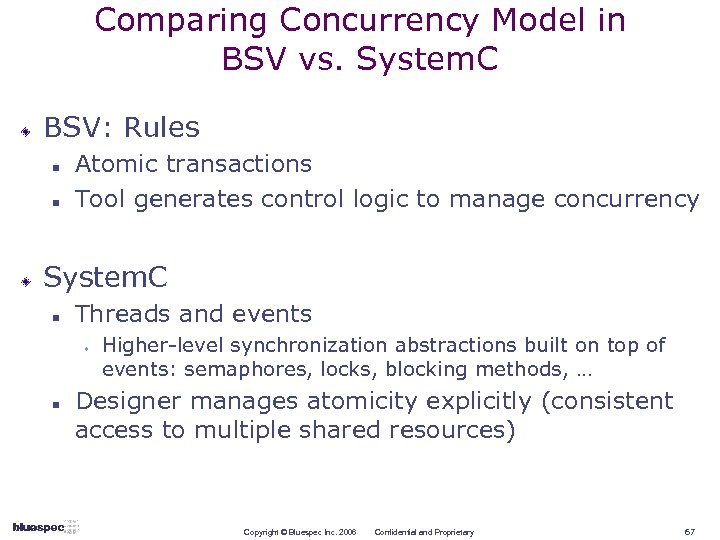

Comparing Concurrency Model in BSV vs. System. C BSV: Rules n n Atomic transactions Tool generates control logic to manage concurrency System. C n Threads and events w n Higher-level synchronization abstractions built on top of events: semaphores, locks, blocking methods, … Designer manages atomicity explicitly (consistent access to multiple shared resources) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 67

Comparing Concurrency Model in BSV vs. System. C BSV: Rules n n Atomic transactions Tool generates control logic to manage concurrency System. C n Threads and events w n Higher-level synchronization abstractions built on top of events: semaphores, locks, blocking methods, … Designer manages atomicity explicitly (consistent access to multiple shared resources) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 67

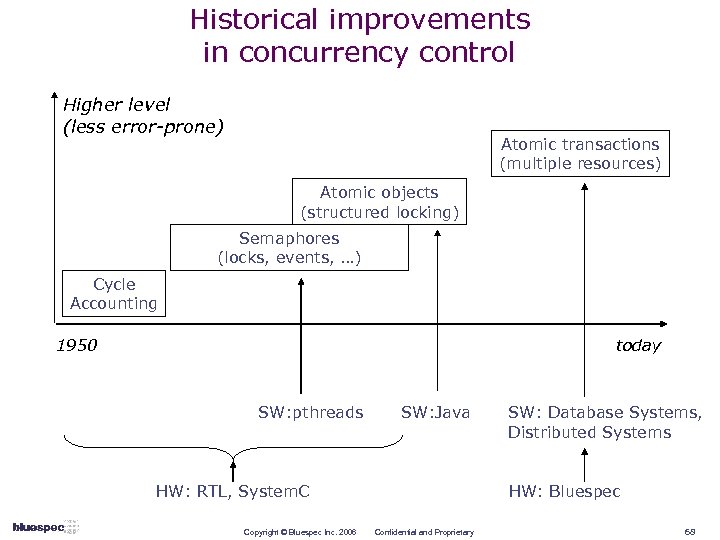

Historical improvements in concurrency control Higher level (less error-prone) Atomic transactions (multiple resources) Atomic objects (structured locking) Semaphores (locks, events, …) Cycle Accounting 1950 today SW: pthreads SW: Java HW: RTL, System. C Copyright © Bluespec Inc. 2006 SW: Database Systems, Distributed Systems HW: Bluespec Confidential and Proprietary 68

Historical improvements in concurrency control Higher level (less error-prone) Atomic transactions (multiple resources) Atomic objects (structured locking) Semaphores (locks, events, …) Cycle Accounting 1950 today SW: pthreads SW: Java HW: RTL, System. C Copyright © Bluespec Inc. 2006 SW: Database Systems, Distributed Systems HW: Bluespec Confidential and Proprietary 68

Elevating design above RTL Bluespec System. C C/C++ Rules with Methods Explicit

Elevating design above RTL Bluespec System. C C/C++ Rules with Methods Explicit

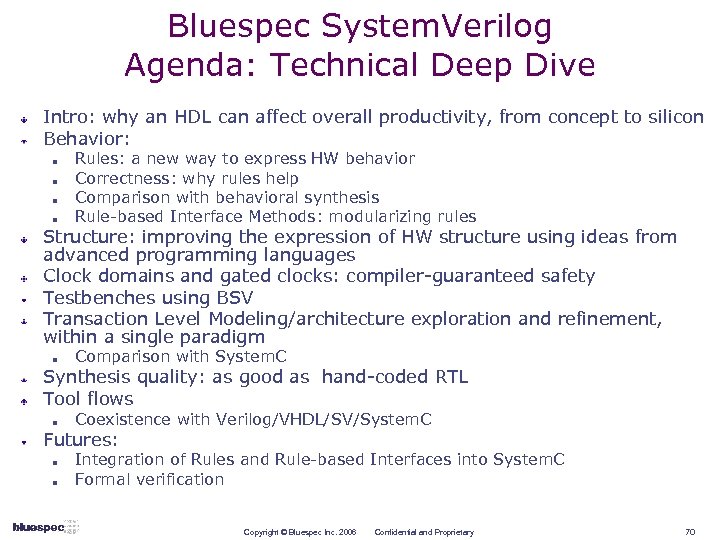

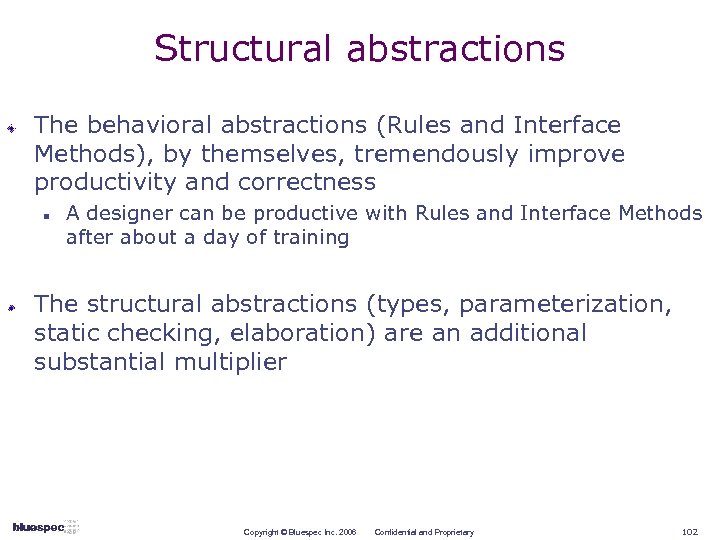

Bluespec System. Verilog Agenda: Technical Deep Dive Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm n Comparison with System. C Synthesis quality: as good as hand-coded RTL Tool flows n Coexistence with Verilog/VHDL/SV/System. C Futures: n n Integration of Rules and Rule-based Interfaces into System. C Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 70

Bluespec System. Verilog Agenda: Technical Deep Dive Intro: why an HDL can affect overall productivity, from concept to silicon Behavior: n n Rules: a new way to express HW behavior Correctness: why rules help Comparison with behavioral synthesis Rule-based Interface Methods: modularizing rules Structure: improving the expression of HW structure using ideas from advanced programming languages Clock domains and gated clocks: compiler-guaranteed safety Testbenches using BSV Transaction Level Modeling/architecture exploration and refinement, within a single paradigm n Comparison with System. C Synthesis quality: as good as hand-coded RTL Tool flows n Coexistence with Verilog/VHDL/SV/System. C Futures: n n Integration of Rules and Rule-based Interfaces into System. C Formal verification Copyright © Bluespec Inc. 2006 Confidential and Proprietary 70

Bluespec System. Verilog™ A one-slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 71

Bluespec System. Verilog™ A one-slide overview Bluespec System. Verilog Behavioral For complex concurrency and control, across multiple shared resources, across module boundaries High-level abstract types Powerful static checking Powerful parameterization Powerful static elaboration Advanced clock management Two dimensions raising the level of abstraction (fully synthesizable) Structural Rules and Rule-based Interfaces VHDL/Verilog/System. C Copyright © Bluespec Inc. 2006 Confidential and Proprietary 71

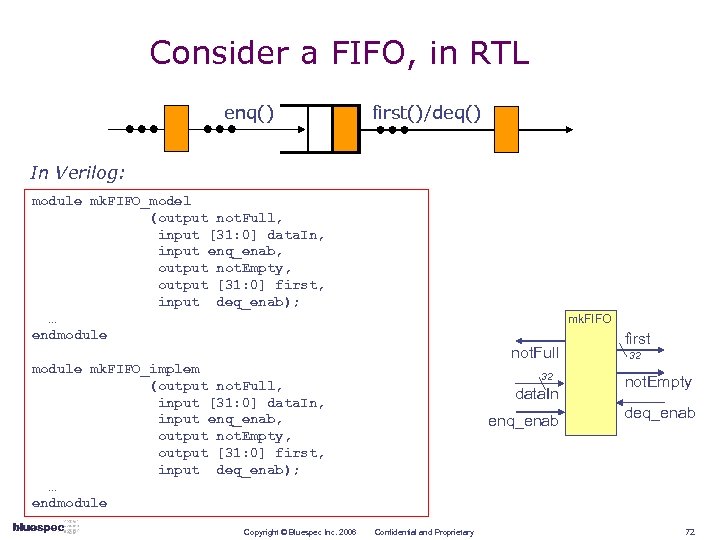

Consider a FIFO, in RTL enq() first()/deq() In Verilog: module mk. FIFO_model (output not. Full, input [31: 0] data. In, input enq_enab, output not. Empty, output [31: 0] first, input deq_enab); … endmodule mk. FIFO not. Full module mk. FIFO_implem (output not. Full, input [31: 0] data. In, input enq_enab, output not. Empty, output [31: 0] first, input deq_enab); … endmodule Copyright © Bluespec Inc. 2006 32 data. In enq_enab Confidential and Proprietary first 32 not. Empty deq_enab 72

Consider a FIFO, in RTL enq() first()/deq() In Verilog: module mk. FIFO_model (output not. Full, input [31: 0] data. In, input enq_enab, output not. Empty, output [31: 0] first, input deq_enab); … endmodule mk. FIFO not. Full module mk. FIFO_implem (output not. Full, input [31: 0] data. In, input enq_enab, output not. Empty, output [31: 0] first, input deq_enab); … endmodule Copyright © Bluespec Inc. 2006 32 data. In enq_enab Confidential and Proprietary first 32 not. Empty deq_enab 72

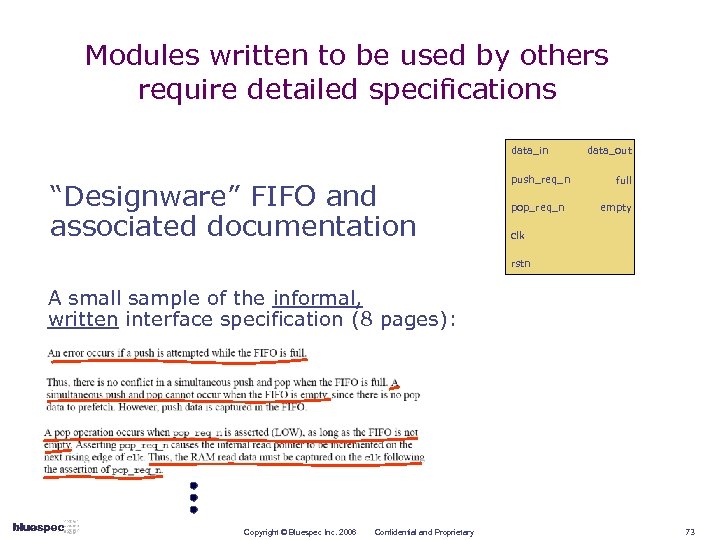

Modules written to be used by others require detailed specifications data_in “Designware” FIFO and associated documentation push_req_n pop_req_n data_out full empty clk rstn A small sample of the informal, written interface specification (8 pages): Copyright © Bluespec Inc. 2006 Confidential and Proprietary 73

Modules written to be used by others require detailed specifications data_in “Designware” FIFO and associated documentation push_req_n pop_req_n data_out full empty clk rstn A small sample of the informal, written interface specification (8 pages): Copyright © Bluespec Inc. 2006 Confidential and Proprietary 73

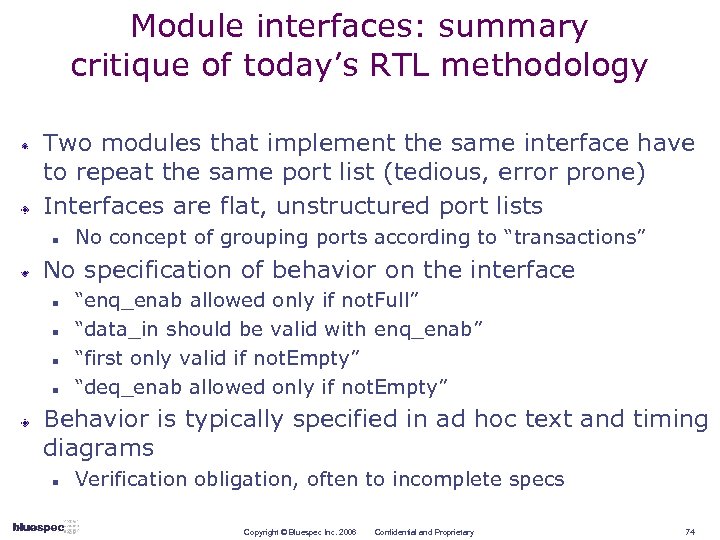

Module interfaces: summary critique of today’s RTL methodology Two modules that implement the same interface have to repeat the same port list (tedious, error prone) Interfaces are flat, unstructured port lists n No concept of grouping ports according to “transactions” No specification of behavior on the interface n n “enq_enab allowed only if not. Full” “data_in should be valid with enq_enab” “first only valid if not. Empty” “deq_enab allowed only if not. Empty” Behavior is typically specified in ad hoc text and timing diagrams n Verification obligation, often to incomplete specs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 74

Module interfaces: summary critique of today’s RTL methodology Two modules that implement the same interface have to repeat the same port list (tedious, error prone) Interfaces are flat, unstructured port lists n No concept of grouping ports according to “transactions” No specification of behavior on the interface n n “enq_enab allowed only if not. Full” “data_in should be valid with enq_enab” “first only valid if not. Empty” “deq_enab allowed only if not. Empty” Behavior is typically specified in ad hoc text and timing diagrams n Verification obligation, often to incomplete specs Copyright © Bluespec Inc. 2006 Confidential and Proprietary 74

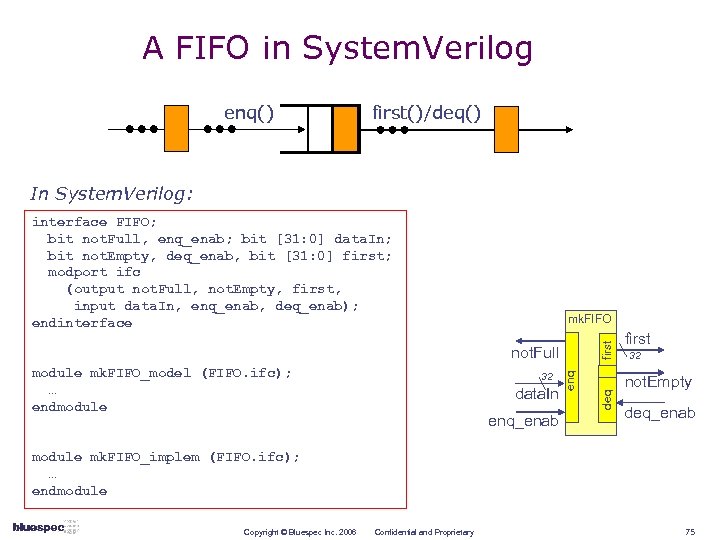

A FIFO in System. Verilog enq() first()/deq() In System. Verilog: interface FIFO; bit not. Full, enq_enab; bit [31: 0] data. In; bit not. Empty, deq_enab, bit [31: 0] first; modport ifc (output not. Full, not. Empty, first, input data. In, enq_enab, deq_enab); endinterface module mk. FIFO_model (FIFO. ifc); … endmodule 32 data. In enq_enab enq not. Full deq first mk. FIFO first 32 not. Empty deq_enab module mk. FIFO_implem (FIFO. ifc); … endmodule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 75

A FIFO in System. Verilog enq() first()/deq() In System. Verilog: interface FIFO; bit not. Full, enq_enab; bit [31: 0] data. In; bit not. Empty, deq_enab, bit [31: 0] first; modport ifc (output not. Full, not. Empty, first, input data. In, enq_enab, deq_enab); endinterface module mk. FIFO_model (FIFO. ifc); … endmodule 32 data. In enq_enab enq not. Full deq first mk. FIFO first 32 not. Empty deq_enab module mk. FIFO_implem (FIFO. ifc); … endmodule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 75

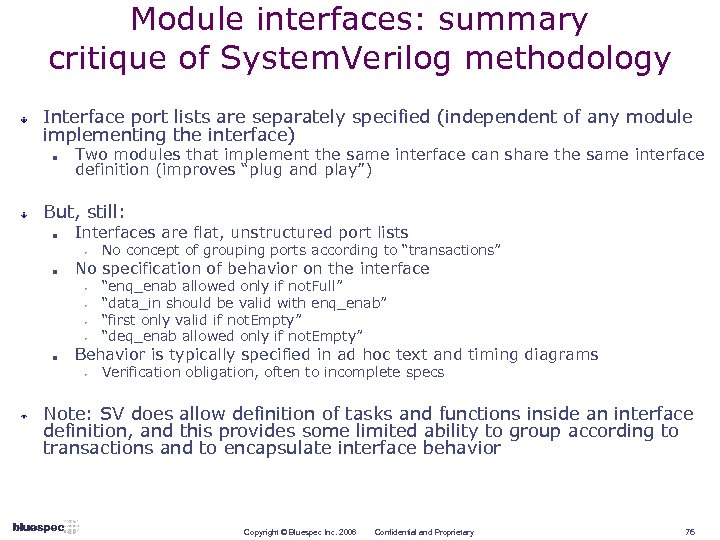

Module interfaces: summary critique of System. Verilog methodology Interface port lists are separately specified (independent of any module implementing the interface) n Two modules that implement the same interface can share the same interface definition (improves “plug and play”) But, still: n Interfaces are flat, unstructured port lists w n No specification of behavior on the interface w w n No concept of grouping ports according to “transactions” “enq_enab allowed only if not. Full” “data_in should be valid with enq_enab” “first only valid if not. Empty” “deq_enab allowed only if not. Empty” Behavior is typically specified in ad hoc text and timing diagrams w Verification obligation, often to incomplete specs Note: SV does allow definition of tasks and functions inside an interface definition, and this provides some limited ability to group according to transactions and to encapsulate interface behavior Copyright © Bluespec Inc. 2006 Confidential and Proprietary 76

Module interfaces: summary critique of System. Verilog methodology Interface port lists are separately specified (independent of any module implementing the interface) n Two modules that implement the same interface can share the same interface definition (improves “plug and play”) But, still: n Interfaces are flat, unstructured port lists w n No specification of behavior on the interface w w n No concept of grouping ports according to “transactions” “enq_enab allowed only if not. Full” “data_in should be valid with enq_enab” “first only valid if not. Empty” “deq_enab allowed only if not. Empty” Behavior is typically specified in ad hoc text and timing diagrams w Verification obligation, often to incomplete specs Note: SV does allow definition of tasks and functions inside an interface definition, and this provides some limited ability to group according to transactions and to encapsulate interface behavior Copyright © Bluespec Inc. 2006 Confidential and Proprietary 76

Rule-based Interfaces Robust, parameterizable, correct-by-construction way to express interactions with a module Extend Rule Semantics across module boundaries Capture the protocol of a complete “transaction” with a module Capture inter-transaction scheduling constraints Copyright © Bluespec Inc. 2006 Confidential and Proprietary 77

Rule-based Interfaces Robust, parameterizable, correct-by-construction way to express interactions with a module Extend Rule Semantics across module boundaries Capture the protocol of a complete “transaction” with a module Capture inter-transaction scheduling constraints Copyright © Bluespec Inc. 2006 Confidential and Proprietary 77

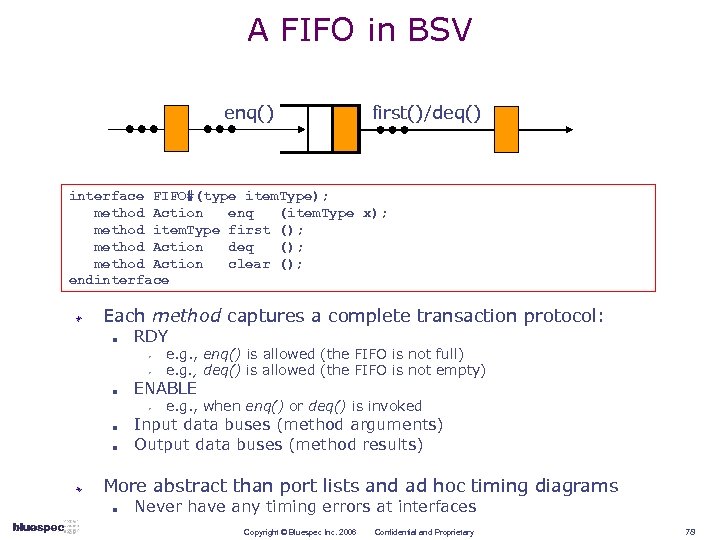

A FIFO in BSV enq() first()/deq() interface FIFO#(type item. Type); method Action enq (item. Type x); method item. Type first (); method Action deq (); method Action clear (); endinterface Each method captures a complete transaction protocol: n RDY w w n ENABLE w n n e. g. , enq() is allowed (the FIFO is not full) e. g. , deq() is allowed (the FIFO is not empty) e. g. , when enq() or deq() is invoked Input data buses (method arguments) Output data buses (method results) More abstract than port lists and ad hoc timing diagrams n Never have any timing errors at interfaces Copyright © Bluespec Inc. 2006 Confidential and Proprietary 78

A FIFO in BSV enq() first()/deq() interface FIFO#(type item. Type); method Action enq (item. Type x); method item. Type first (); method Action deq (); method Action clear (); endinterface Each method captures a complete transaction protocol: n RDY w w n ENABLE w n n e. g. , enq() is allowed (the FIFO is not full) e. g. , deq() is allowed (the FIFO is not empty) e. g. , when enq() or deq() is invoked Input data buses (method arguments) Output data buses (method results) More abstract than port lists and ad hoc timing diagrams n Never have any timing errors at interfaces Copyright © Bluespec Inc. 2006 Confidential and Proprietary 78

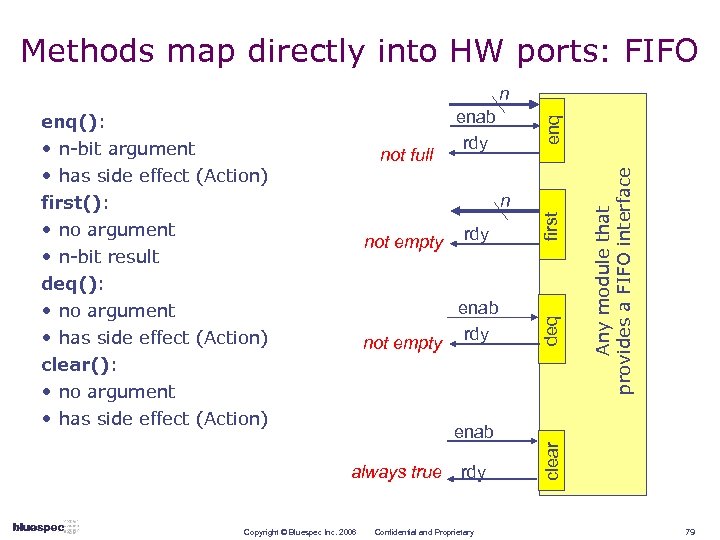

Methods map directly into HW ports: FIFO n not full enab not empty rdy enab always true Copyright © Bluespec Inc. 2006 rdy Confidential and Proprietary deq rdy clear not empty first n Any module that provides a FIFO interface • n-bit argument • has side effect (Action) first(): • no argument • n-bit result deq(): • no argument • has side effect (Action) clear(): • no argument • has side effect (Action) enab rdy enq(): 79

Methods map directly into HW ports: FIFO n not full enab not empty rdy enab always true Copyright © Bluespec Inc. 2006 rdy Confidential and Proprietary deq rdy clear not empty first n Any module that provides a FIFO interface • n-bit argument • has side effect (Action) first(): • no argument • n-bit result deq(): • no argument • has side effect (Action) clear(): • no argument • has side effect (Action) enab rdy enq(): 79

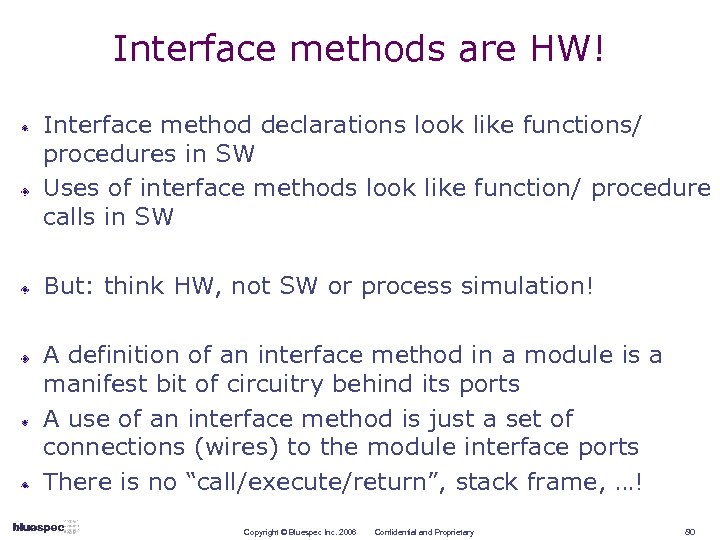

Interface methods are HW! Interface method declarations look like functions/ procedures in SW Uses of interface methods look like function/ procedure calls in SW But: think HW, not SW or process simulation! A definition of an interface method in a module is a manifest bit of circuitry behind its ports A use of an interface method is just a set of connections (wires) to the module interface ports There is no “call/execute/return”, stack frame, …! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 80

Interface methods are HW! Interface method declarations look like functions/ procedures in SW Uses of interface methods look like function/ procedure calls in SW But: think HW, not SW or process simulation! A definition of an interface method in a module is a manifest bit of circuitry behind its ports A use of an interface method is just a set of connections (wires) to the module interface ports There is no “call/execute/return”, stack frame, …! Copyright © Bluespec Inc. 2006 Confidential and Proprietary 80

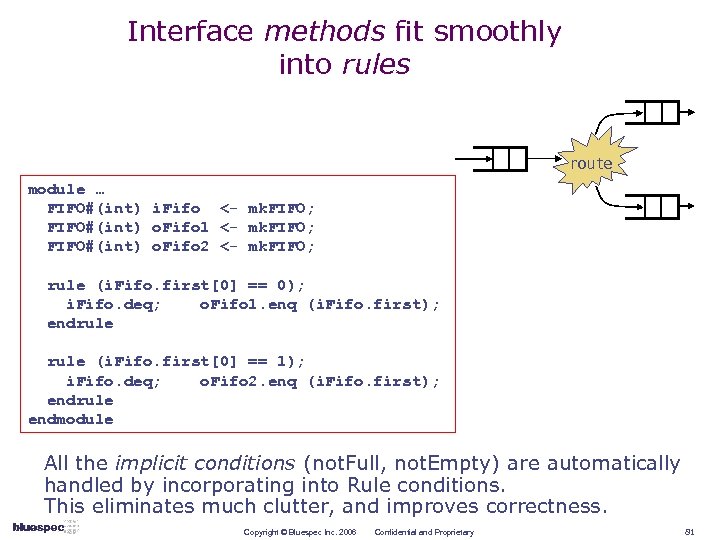

Interface methods fit smoothly into rules route module … FIFO#(int) i. Fifo <- mk. FIFO; FIFO#(int) o. Fifo 1 <- mk. FIFO; FIFO#(int) o. Fifo 2 <- mk. FIFO; rule (i. Fifo. first[0] == 0); i. Fifo. deq; o. Fifo 1. enq (i. Fifo. first); endrule (i. Fifo. first[0] == 1); i. Fifo. deq; o. Fifo 2. enq (i. Fifo. first); endrule endmodule All the implicit conditions (not. Full, not. Empty) are automatically handled by incorporating into Rule conditions. This eliminates much clutter, and improves correctness. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 81

Interface methods fit smoothly into rules route module … FIFO#(int) i. Fifo <- mk. FIFO; FIFO#(int) o. Fifo 1 <- mk. FIFO; FIFO#(int) o. Fifo 2 <- mk. FIFO; rule (i. Fifo. first[0] == 0); i. Fifo. deq; o. Fifo 1. enq (i. Fifo. first); endrule (i. Fifo. first[0] == 1); i. Fifo. deq; o. Fifo 2. enq (i. Fifo. first); endrule endmodule All the implicit conditions (not. Full, not. Empty) are automatically handled by incorporating into Rule conditions. This eliminates much clutter, and improves correctness. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 81

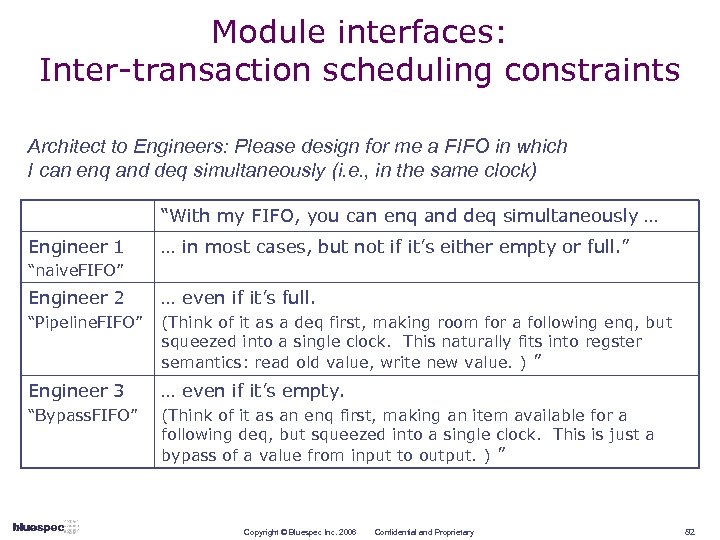

Module interfaces: Inter-transaction scheduling constraints Architect to Engineers: Please design for me a FIFO in which I can enq and deq simultaneously (i. e. , in the same clock) “With my FIFO, you can enq and deq simultaneously … Engineer 1 … in most cases, but not if it’s either empty or full. ” “naive. FIFO” Engineer 2 … even if it’s full. “Pipeline. FIFO” (Think of it as a deq first, making room for a following enq, but squeezed into a single clock. This naturally fits into regster semantics: read old value, write new value. ) ” Engineer 3 … even if it’s empty. “Bypass. FIFO” (Think of it as an enq first, making an item available for a following deq, but squeezed into a single clock. This is just a bypass of a value from input to output. ) ” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 82

Module interfaces: Inter-transaction scheduling constraints Architect to Engineers: Please design for me a FIFO in which I can enq and deq simultaneously (i. e. , in the same clock) “With my FIFO, you can enq and deq simultaneously … Engineer 1 … in most cases, but not if it’s either empty or full. ” “naive. FIFO” Engineer 2 … even if it’s full. “Pipeline. FIFO” (Think of it as a deq first, making room for a following enq, but squeezed into a single clock. This naturally fits into regster semantics: read old value, write new value. ) ” Engineer 3 … even if it’s empty. “Bypass. FIFO” (Think of it as an enq first, making an item available for a following deq, but squeezed into a single clock. This is just a bypass of a value from input to output. ) ” Copyright © Bluespec Inc. 2006 Confidential and Proprietary 82

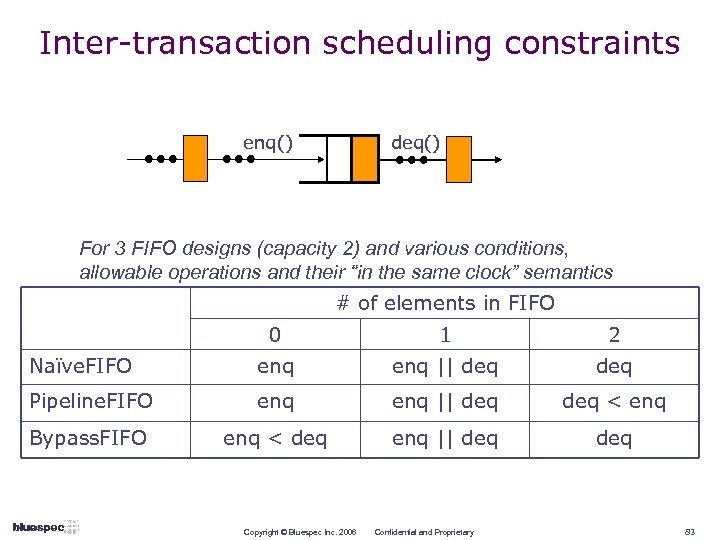

Inter-transaction scheduling constraints enq() deq() For 3 FIFO designs (capacity 2) and various conditions, allowable operations and their “in the same clock” semantics # of elements in FIFO 0 1 2 Naïve. FIFO enq || deq Pipeline. FIFO enq || deq < enq Bypass. FIFO enq < deq enq || deq Copyright © Bluespec Inc. 2006 Confidential and Proprietary 83

Inter-transaction scheduling constraints enq() deq() For 3 FIFO designs (capacity 2) and various conditions, allowable operations and their “in the same clock” semantics # of elements in FIFO 0 1 2 Naïve. FIFO enq || deq Pipeline. FIFO enq || deq < enq Bypass. FIFO enq < deq enq || deq Copyright © Bluespec Inc. 2006 Confidential and Proprietary 83

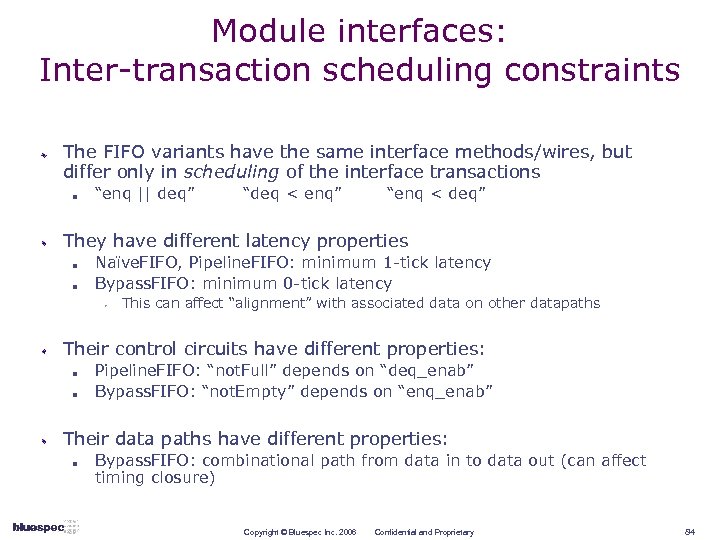

Module interfaces: Inter-transaction scheduling constraints The FIFO variants have the same interface methods/wires, but differ only in scheduling of the interface transactions n “enq || deq” “deq < enq” “enq < deq” They have different latency properties n n Naïve. FIFO, Pipeline. FIFO: minimum 1 -tick latency Bypass. FIFO: minimum 0 -tick latency w This can affect “alignment” with associated data on other datapaths Their control circuits have different properties: n n Pipeline. FIFO: “not. Full” depends on “deq_enab” Bypass. FIFO: “not. Empty” depends on “enq_enab” Their data paths have different properties: n Bypass. FIFO: combinational path from data in to data out (can affect timing closure) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 84

Module interfaces: Inter-transaction scheduling constraints The FIFO variants have the same interface methods/wires, but differ only in scheduling of the interface transactions n “enq || deq” “deq < enq” “enq < deq” They have different latency properties n n Naïve. FIFO, Pipeline. FIFO: minimum 1 -tick latency Bypass. FIFO: minimum 0 -tick latency w This can affect “alignment” with associated data on other datapaths Their control circuits have different properties: n n Pipeline. FIFO: “not. Full” depends on “deq_enab” Bypass. FIFO: “not. Empty” depends on “enq_enab” Their data paths have different properties: n Bypass. FIFO: combinational path from data in to data out (can affect timing closure) Copyright © Bluespec Inc. 2006 Confidential and Proprietary 84

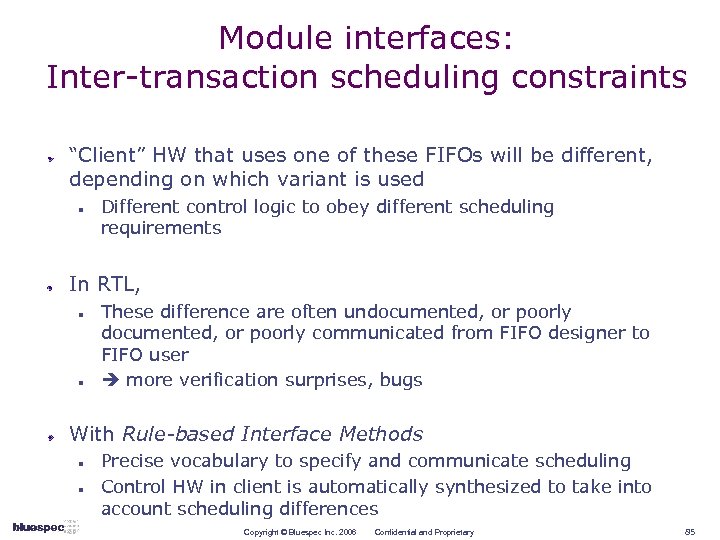

Module interfaces: Inter-transaction scheduling constraints “Client” HW that uses one of these FIFOs will be different, depending on which variant is used n Different control logic to obey different scheduling requirements In RTL, n n These difference are often undocumented, or poorly communicated from FIFO designer to FIFO user more verification surprises, bugs With Rule-based Interface Methods n n Precise vocabulary to specify and communicate scheduling Control HW in client is automatically synthesized to take into account scheduling differences Copyright © Bluespec Inc. 2006 Confidential and Proprietary 85

Module interfaces: Inter-transaction scheduling constraints “Client” HW that uses one of these FIFOs will be different, depending on which variant is used n Different control logic to obey different scheduling requirements In RTL, n n These difference are often undocumented, or poorly communicated from FIFO designer to FIFO user more verification surprises, bugs With Rule-based Interface Methods n n Precise vocabulary to specify and communicate scheduling Control HW in client is automatically synthesized to take into account scheduling differences Copyright © Bluespec Inc. 2006 Confidential and Proprietary 85

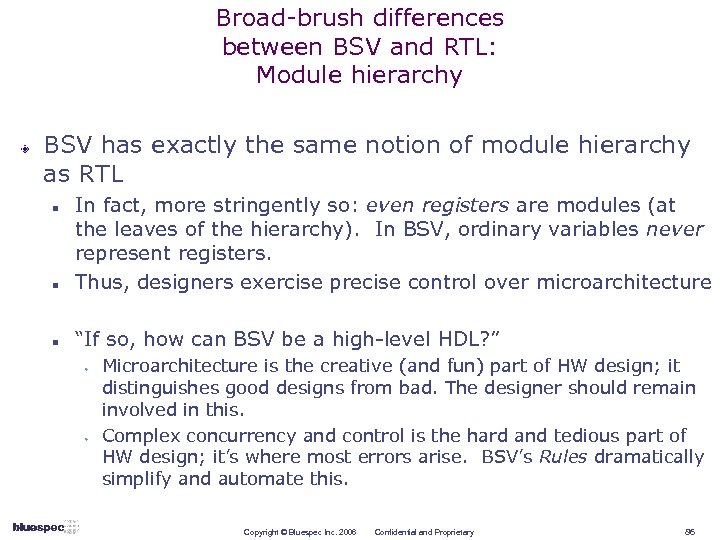

Broad-brush differences between BSV and RTL: Module hierarchy BSV has exactly the same notion of module hierarchy as RTL n In fact, more stringently so: even registers are modules (at the leaves of the hierarchy). In BSV, ordinary variables never represent registers. Thus, designers exercise precise control over microarchitecture n “If so, how can BSV be a high-level HDL? ” n w w Microarchitecture is the creative (and fun) part of HW design; it distinguishes good designs from bad. The designer should remain involved in this. Complex concurrency and control is the hard and tedious part of HW design; it’s where most errors arise. BSV’s Rules dramatically simplify and automate this. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 86

Broad-brush differences between BSV and RTL: Module hierarchy BSV has exactly the same notion of module hierarchy as RTL n In fact, more stringently so: even registers are modules (at the leaves of the hierarchy). In BSV, ordinary variables never represent registers. Thus, designers exercise precise control over microarchitecture n “If so, how can BSV be a high-level HDL? ” n w w Microarchitecture is the creative (and fun) part of HW design; it distinguishes good designs from bad. The designer should remain involved in this. Complex concurrency and control is the hard and tedious part of HW design; it’s where most errors arise. BSV’s Rules dramatically simplify and automate this. Copyright © Bluespec Inc. 2006 Confidential and Proprietary 86

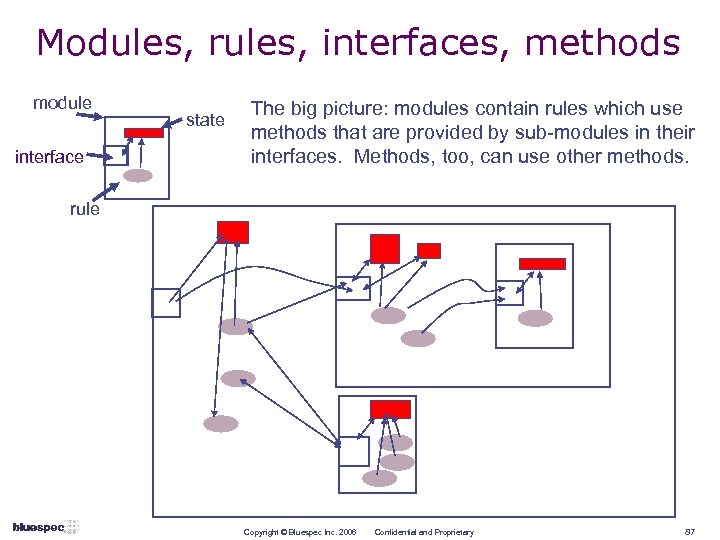

Modules, rules, interfaces, methods module interface state The big picture: modules contain rules which use methods that are provided by sub-modules in their interfaces. Methods, too, can use other methods. rule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 87

Modules, rules, interfaces, methods module interface state The big picture: modules contain rules which use methods that are provided by sub-modules in their interfaces. Methods, too, can use other methods. rule Copyright © Bluespec Inc. 2006 Confidential and Proprietary 87

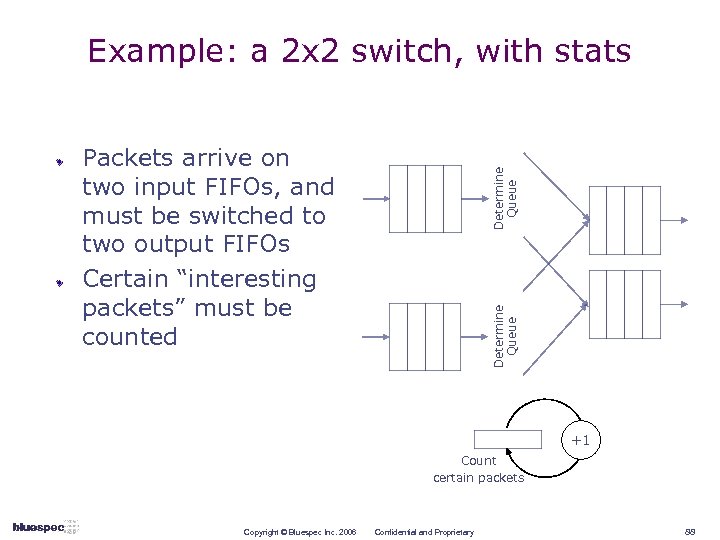

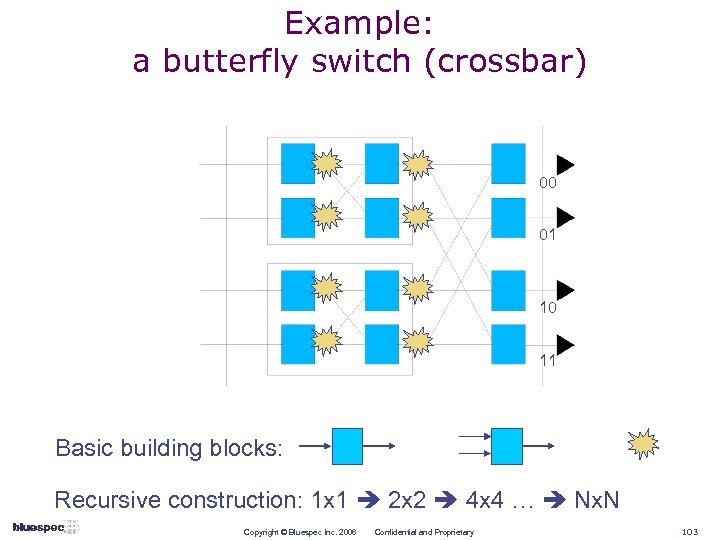

Example: a 2 x 2 switch, with stats Determine Queue Packets arrive on two input FIFOs, and must be switched to two output FIFOs Certain “interesting packets” must be counted +1 Count certain packets Copyright © Bluespec Inc. 2006 Confidential and Proprietary 88

Example: a 2 x 2 switch, with stats Determine Queue Packets arrive on two input FIFOs, and must be switched to two output FIFOs Certain “interesting packets” must be counted +1 Count certain packets Copyright © Bluespec Inc. 2006 Confidential and Proprietary 88

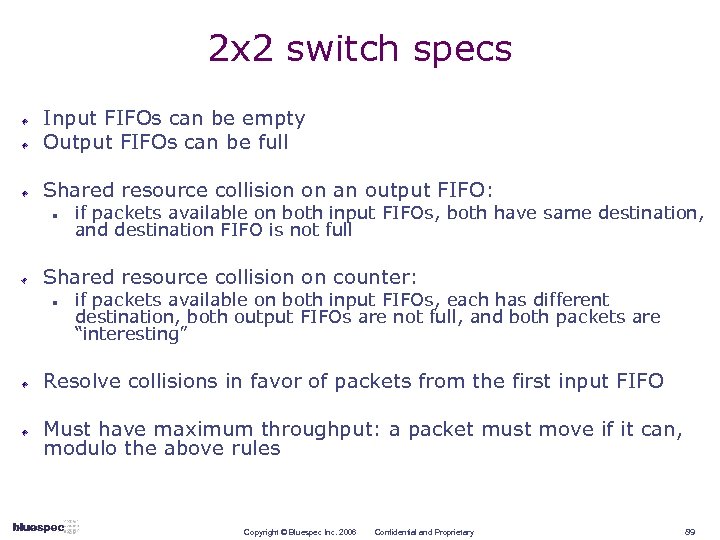

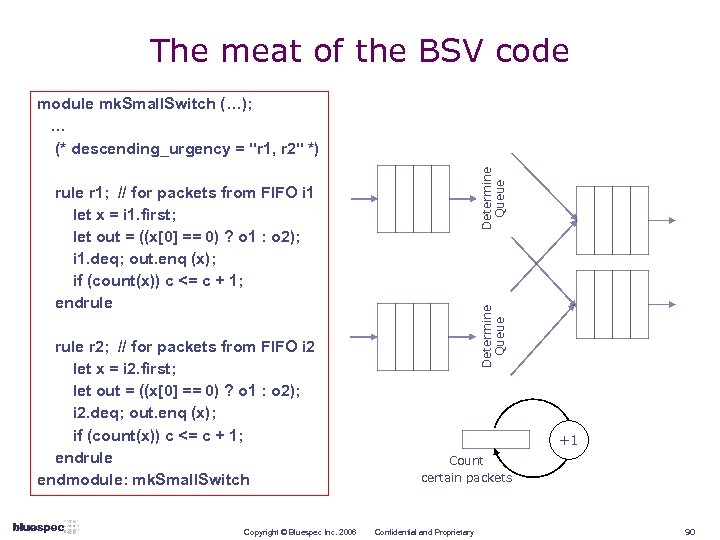

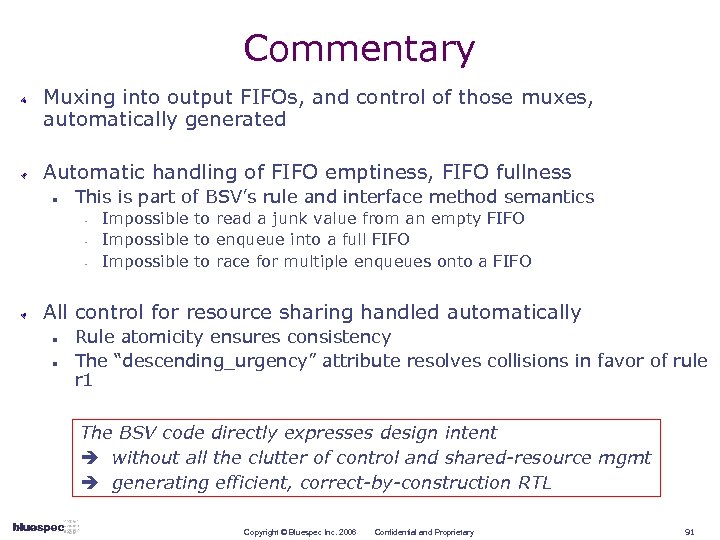

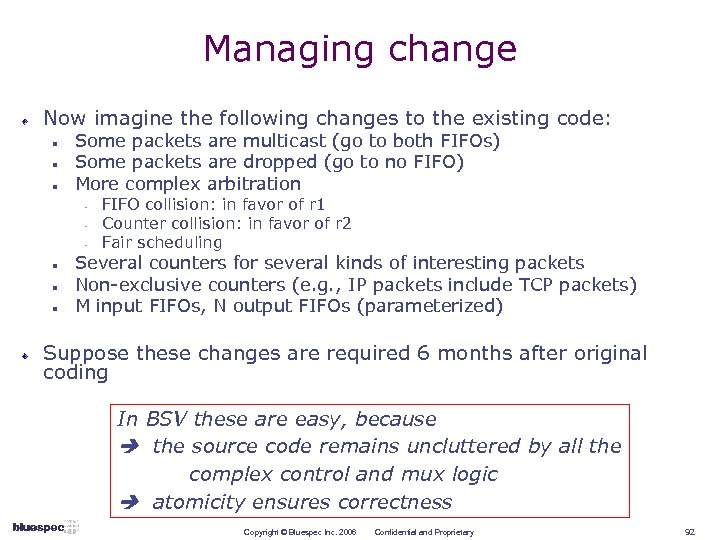

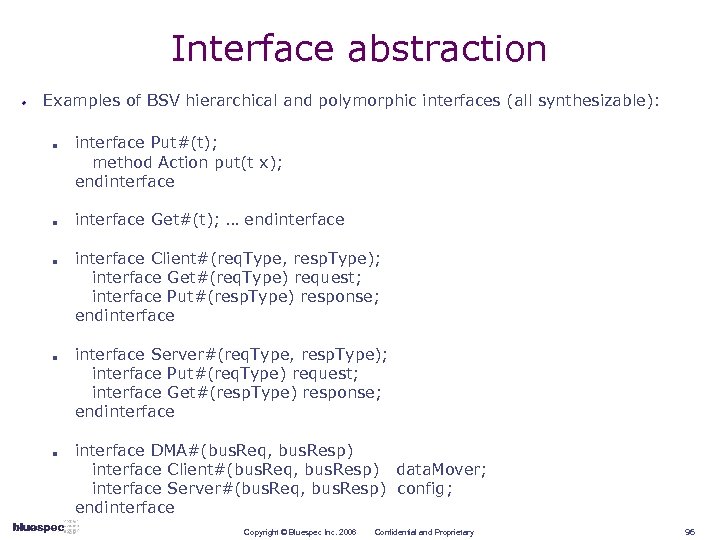

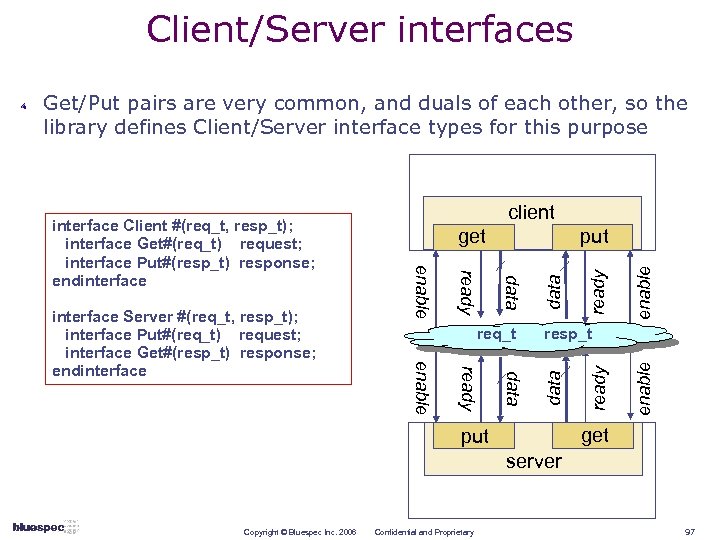

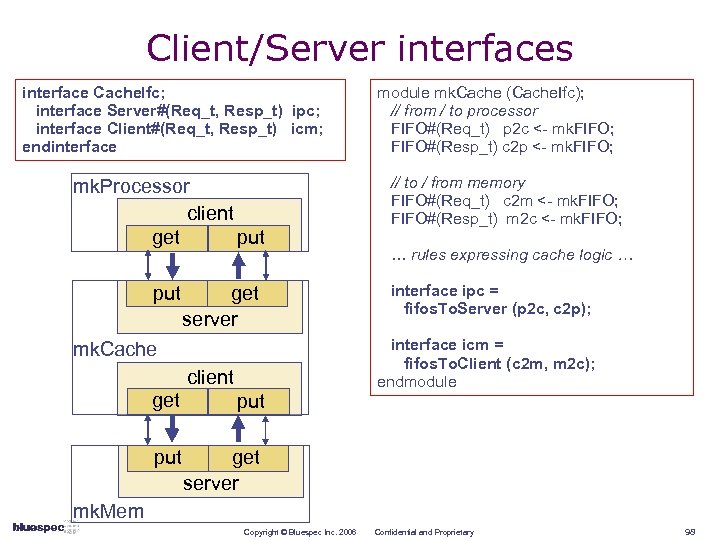

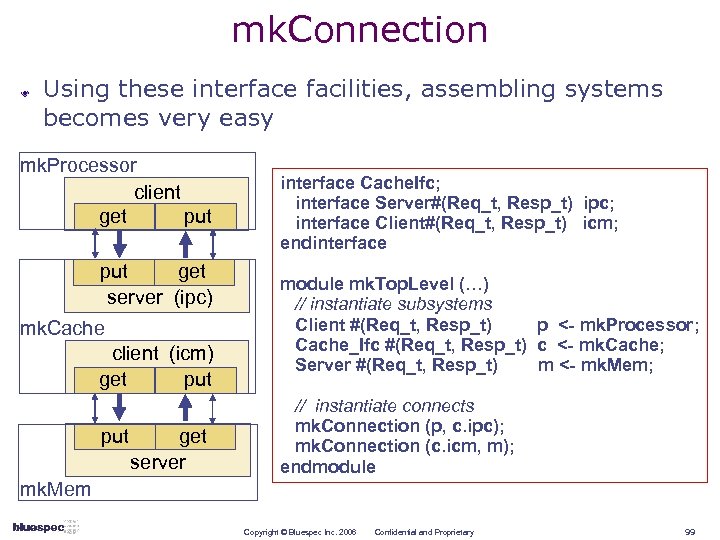

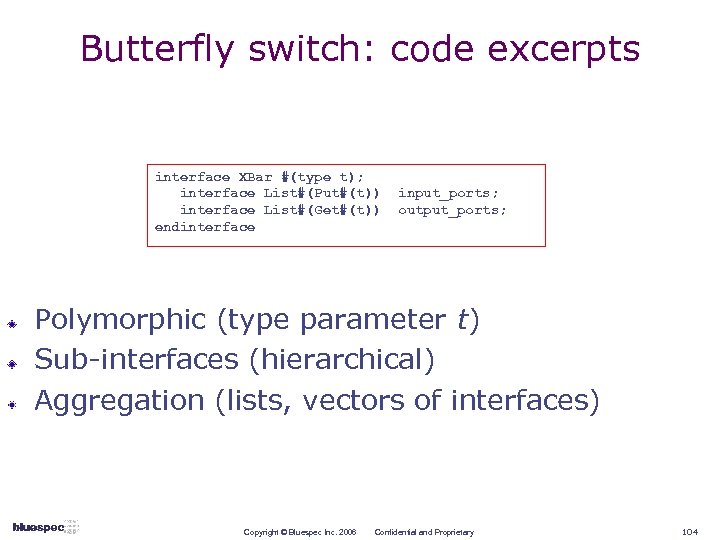

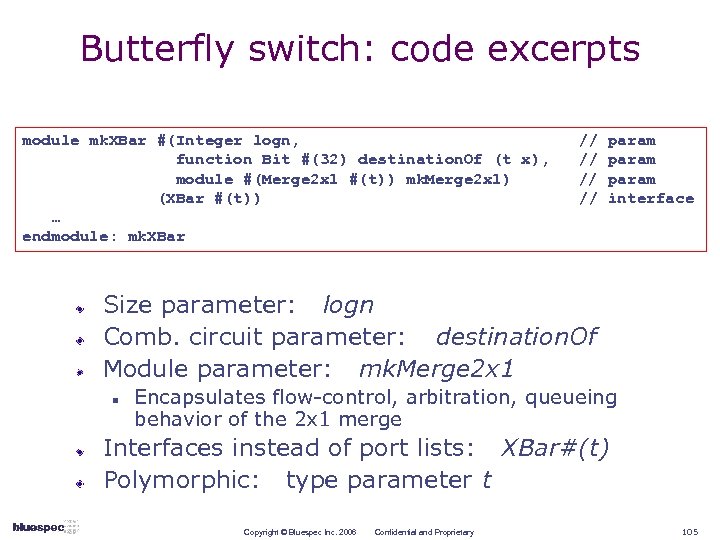

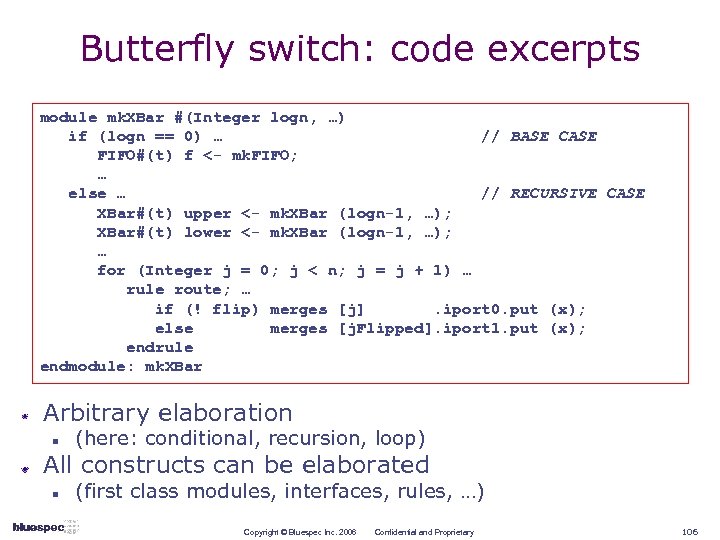

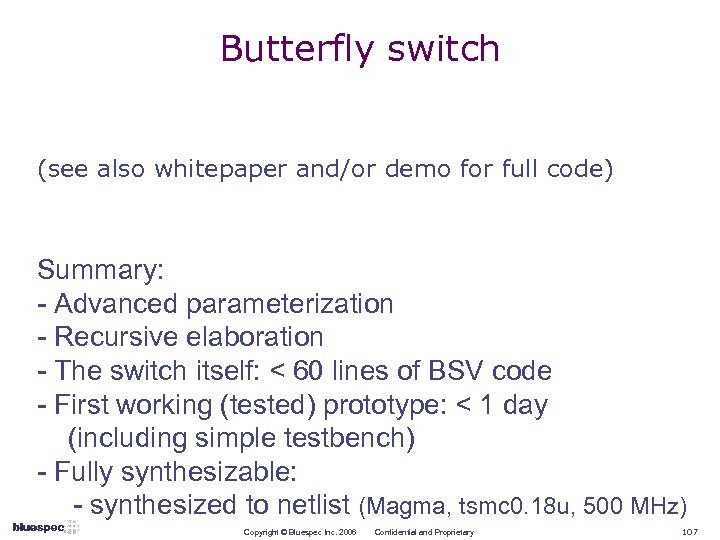

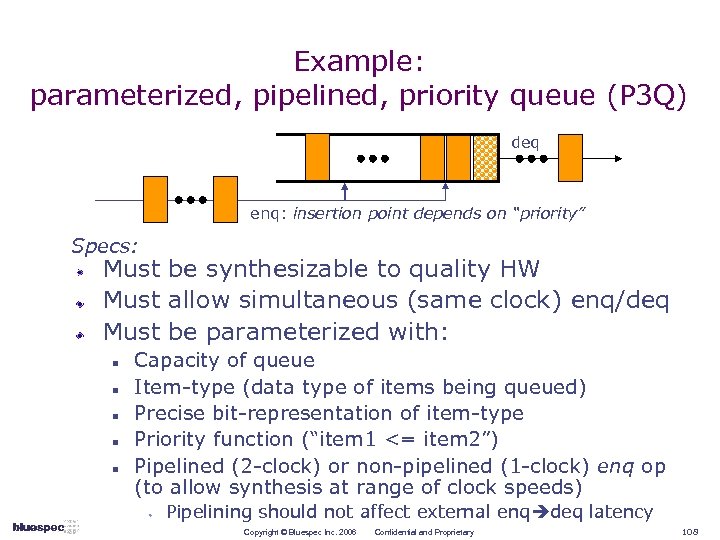

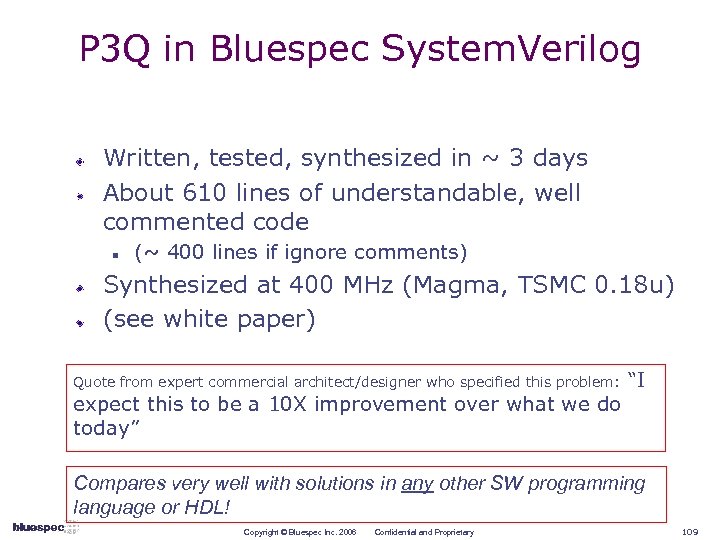

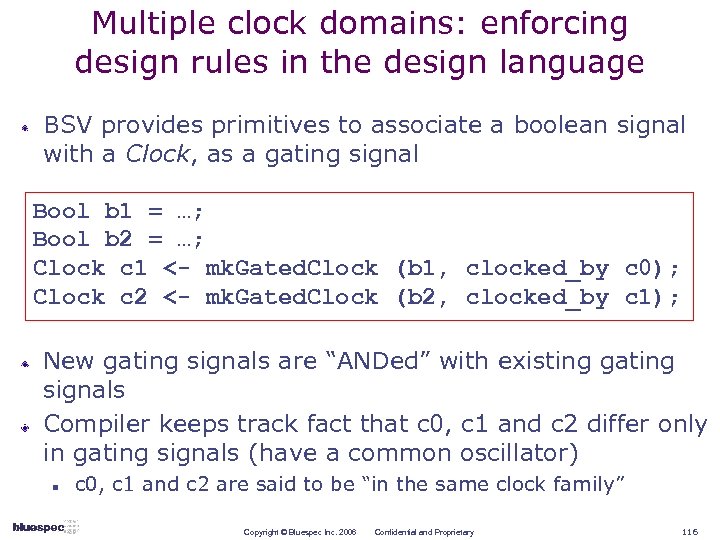

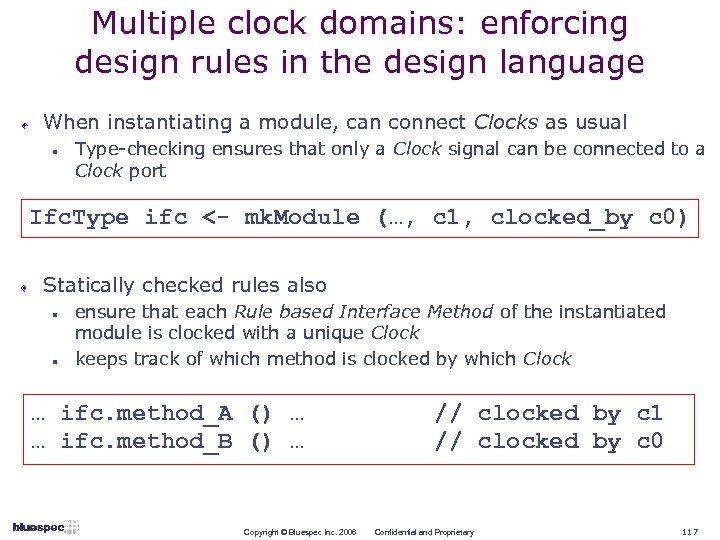

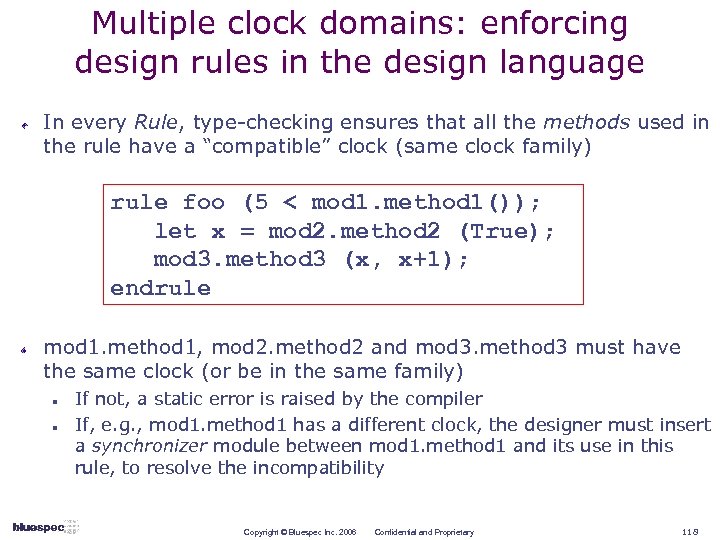

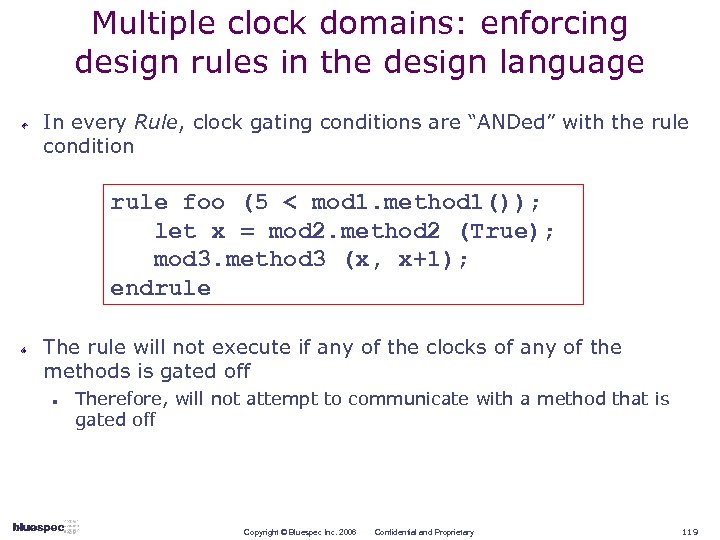

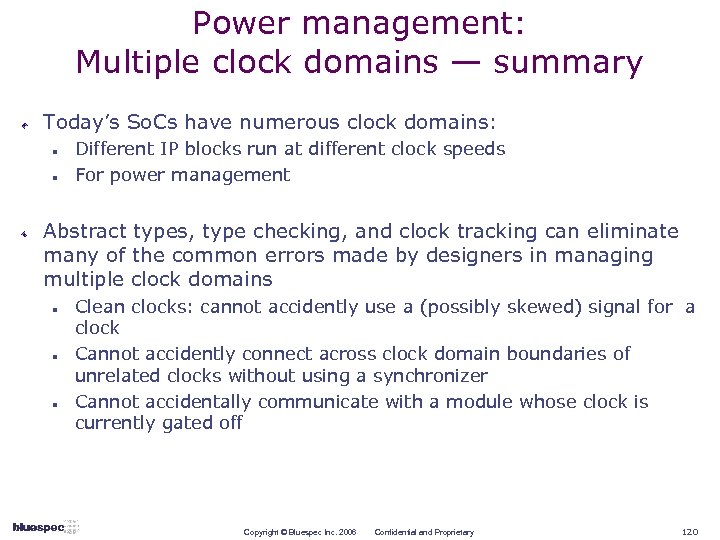

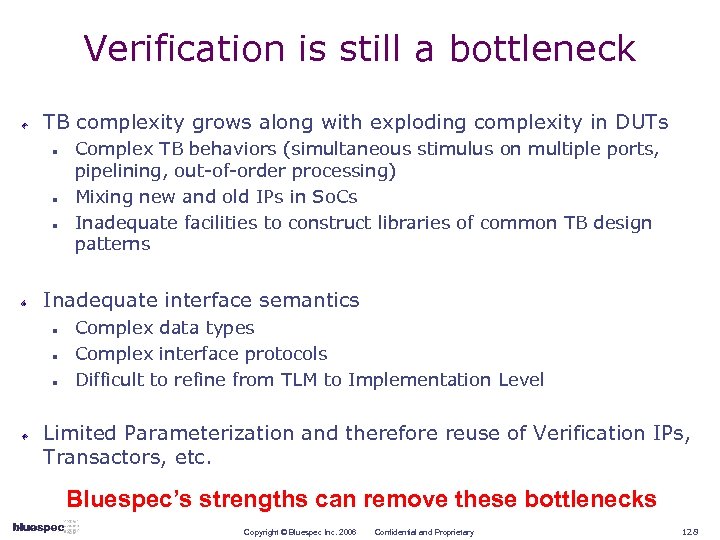

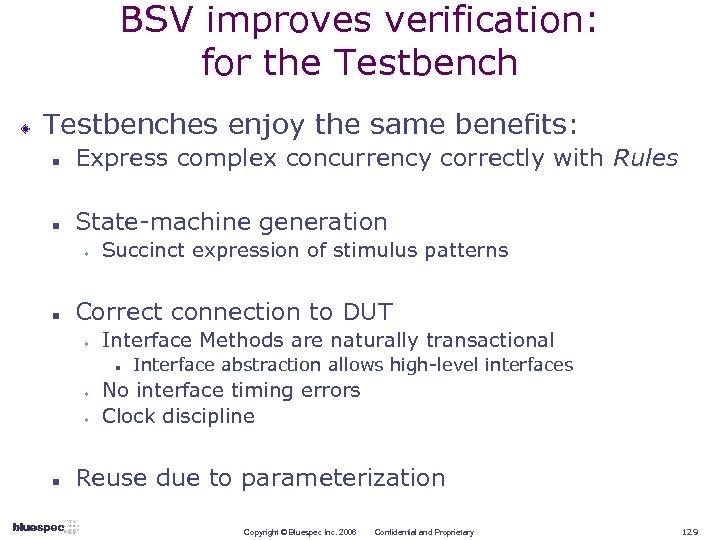

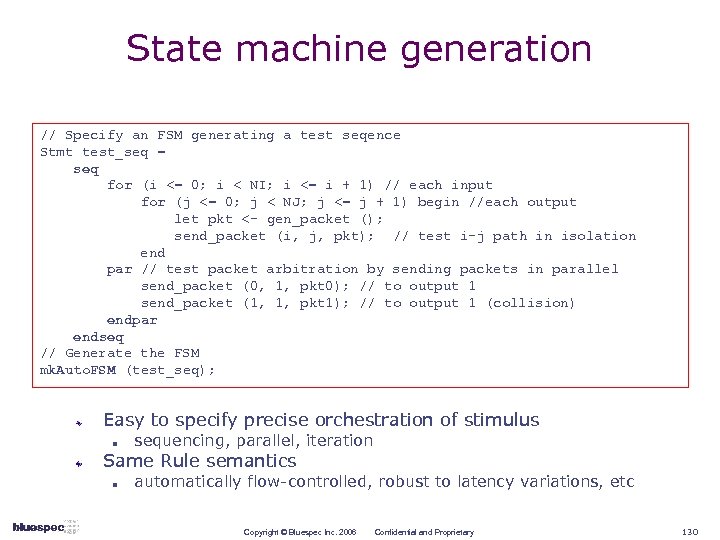

2 x 2 switch specs Input FIFOs can be empty Output FIFOs can be full Shared resource collision on an output FIFO: n if packets available on both input FIFOs, both have same destination, and destination FIFO is not full Shared resource collision on counter: n if packets available on both input FIFOs, each has different destination, both output FIFOs are not full, and both packets are “interesting” Resolve collisions in favor of packets from the first input FIFO Must have maximum throughput: a packet must move if it can, modulo the above rules Copyright © Bluespec Inc. 2006 Confidential and Proprietary 89