0bac48e351651b890ee686db23f408c1.ppt

- Количество слайдов: 8

FPPA design methodology Outline Intersil FPPA methodology design constraints "Symbolic" versus "Full" FPPA 98 -FPPA 2000 FPPA 2001 1 design flow Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA design methodology Outline Intersil FPPA methodology design constraints "Symbolic" versus "Full" FPPA 98 -FPPA 2000 FPPA 2001 1 design flow Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

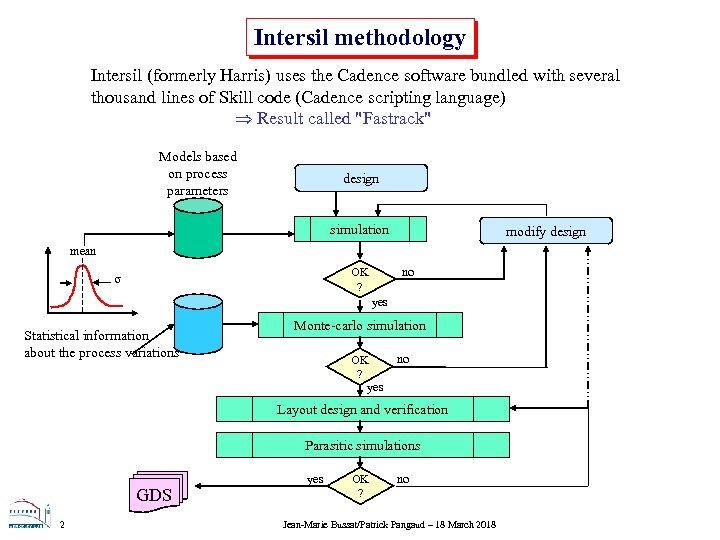

Intersil methodology Intersil (formerly Harris) uses the Cadence software bundled with several thousand lines of Skill code (Cadence scripting language) Result called "Fastrack" Models based on process parameters design simulation modify design mean no OK ? σ yes Statistical information about the process variations Monte-carlo simulation OK ? yes no Layout design and verification Parasitic simulations GDS 2 yes OK ? no Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

Intersil methodology Intersil (formerly Harris) uses the Cadence software bundled with several thousand lines of Skill code (Cadence scripting language) Result called "Fastrack" Models based on process parameters design simulation modify design mean no OK ? σ yes Statistical information about the process variations Monte-carlo simulation OK ? yes no Layout design and verification Parasitic simulations GDS 2 yes OK ? no Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA design "constraints" Problem: Instersil had a bad experience with its custom IC program: Some "big" customers had non-working designs and blamed Intersil for that. Bad publicity for the foundry. To prevent this to happen again Intersil don't want to deal directly with customers anymore. • Customers must submit design ideas to Design House. • The design house do the design and submit it to foundry This method doesn't work for the FPPA: • Design too specific. . . • To much interaction needed between the engineer who has the design idea and the "real" designer. Must be the same person. But Intersil do not want to give away Fastrack (Fastrack means direct access to the foundry). 3 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA design "constraints" Problem: Instersil had a bad experience with its custom IC program: Some "big" customers had non-working designs and blamed Intersil for that. Bad publicity for the foundry. To prevent this to happen again Intersil don't want to deal directly with customers anymore. • Customers must submit design ideas to Design House. • The design house do the design and submit it to foundry This method doesn't work for the FPPA: • Design too specific. . . • To much interaction needed between the engineer who has the design idea and the "real" designer. Must be the same person. But Intersil do not want to give away Fastrack (Fastrack means direct access to the foundry). 3 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA design "constraints" (cont. ) Agreement: We can do the design ourselves but we must interact with a design house (Sd. M, Charleroi, Belgium). Sd. M duties: - Provide a simplified Design Kit based on Fastrack. missing devices = Semi-custom library: components are seen as black boxes - Provide simplified typical simulation models. wrong models - Do Monte-Carlo simulations. wrong simulations - Perform parasitic extraction and simulation. - Do final checking of the design. - Convert our design database into final Fastrack database. conversion errors Many problems came with this simplified Design Kit: - Incomplete kit - Bugs - Poor user's interface - Request for modification 4 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA design "constraints" (cont. ) Agreement: We can do the design ourselves but we must interact with a design house (Sd. M, Charleroi, Belgium). Sd. M duties: - Provide a simplified Design Kit based on Fastrack. missing devices = Semi-custom library: components are seen as black boxes - Provide simplified typical simulation models. wrong models - Do Monte-Carlo simulations. wrong simulations - Perform parasitic extraction and simulation. - Do final checking of the design. - Convert our design database into final Fastrack database. conversion errors Many problems came with this simplified Design Kit: - Incomplete kit - Bugs - Poor user's interface - Request for modification 4 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

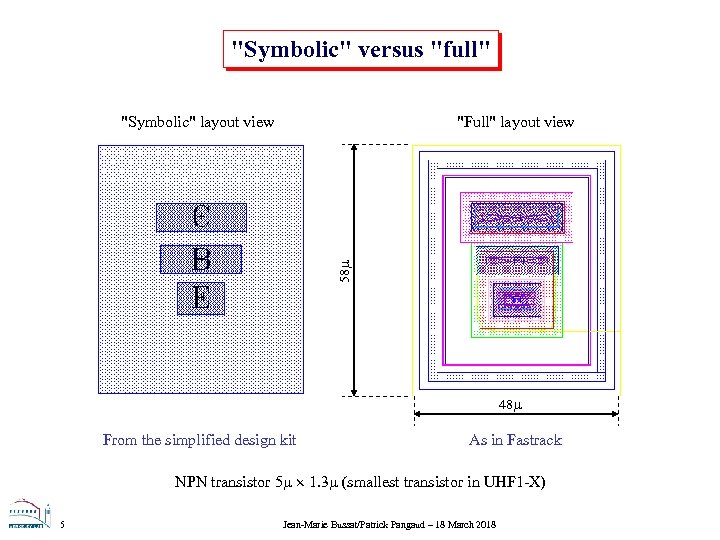

"Symbolic" versus "full" "Full" layout view 58µ "Symbolic" layout view 48µ From the simplified design kit As in Fastrack NPN transistor 5µ 1. 3µ (smallest transistor in UHF 1 -X) 5 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

"Symbolic" versus "full" "Full" layout view 58µ "Symbolic" layout view 48µ From the simplified design kit As in Fastrack NPN transistor 5µ 1. 3µ (smallest transistor in UHF 1 -X) 5 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

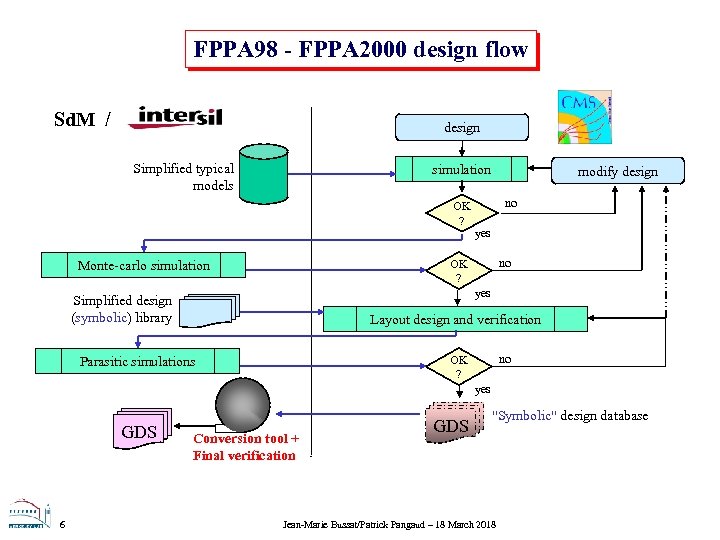

FPPA 98 - FPPA 2000 design flow Sd. M / design Simplified typical models simulation OK ? modify design no yes no OK ? Monte-carlo simulation yes Simplified design (symbolic) library Layout design and verification no OK ? Parasitic simulations yes GDS 6 Conversion tool + Final verification GDS "Symbolic" design database Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA 98 - FPPA 2000 design flow Sd. M / design Simplified typical models simulation OK ? modify design no yes no OK ? Monte-carlo simulation yes Simplified design (symbolic) library Layout design and verification no OK ? Parasitic simulations yes GDS 6 Conversion tool + Final verification GDS "Symbolic" design database Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

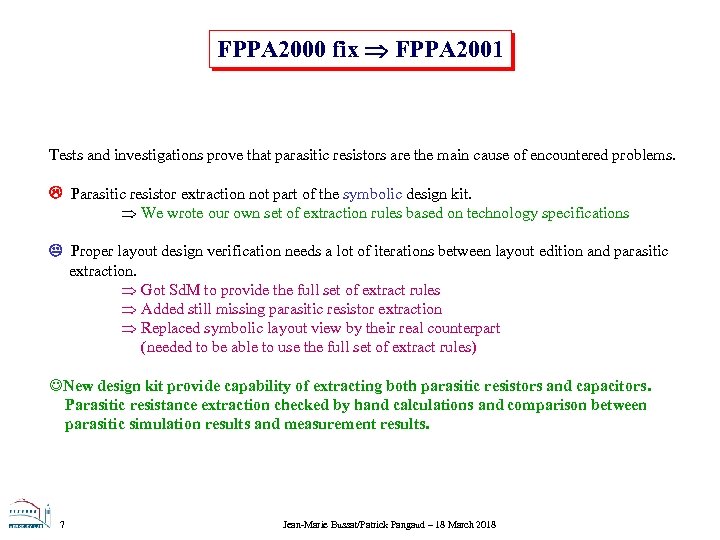

FPPA 2000 fix FPPA 2001 Tests and investigations prove that parasitic resistors are the main cause of encountered problems. Parasitic resistor extraction not part of the symbolic design kit. We wrote our own set of extraction rules based on technology specifications Proper layout design verification needs a lot of iterations between layout edition and parasitic extraction. Got Sd. M to provide the full set of extract rules Added still missing parasitic resistor extraction Replaced symbolic layout view by their real counterpart (needed to be able to use the full set of extract rules) JNew design kit provide capability of extracting both parasitic resistors and capacitors. Parasitic resistance extraction checked by hand calculations and comparison between parasitic simulation results and measurement results. 7 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

FPPA 2000 fix FPPA 2001 Tests and investigations prove that parasitic resistors are the main cause of encountered problems. Parasitic resistor extraction not part of the symbolic design kit. We wrote our own set of extraction rules based on technology specifications Proper layout design verification needs a lot of iterations between layout edition and parasitic extraction. Got Sd. M to provide the full set of extract rules Added still missing parasitic resistor extraction Replaced symbolic layout view by their real counterpart (needed to be able to use the full set of extract rules) JNew design kit provide capability of extracting both parasitic resistors and capacitors. Parasitic resistance extraction checked by hand calculations and comparison between parasitic simulation results and measurement results. 7 Jean-Marie Bussat/Patrick Pangaud – 18 March 2018

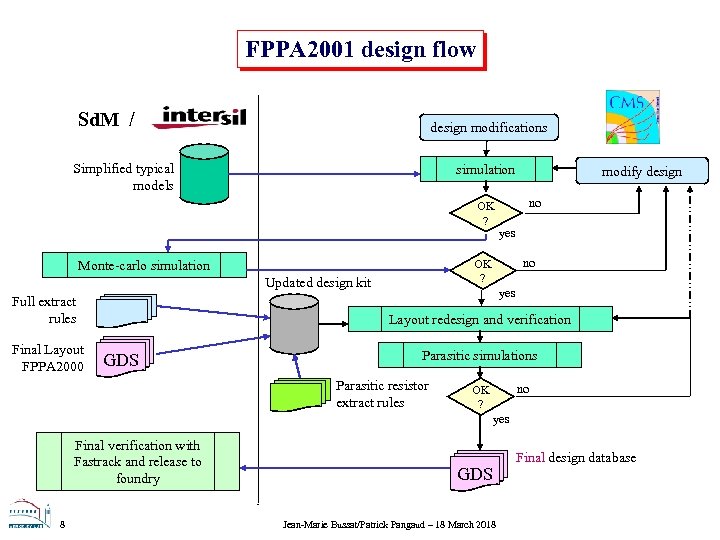

FPPA 2001 design flow Sd. M / design modifications Simplified typical models simulation OK ? Updated design kit Full extract rules Final Layout FPPA 2000 no yes no OK ? Monte-carlo simulation modify design yes Layout redesign and verification GDS Parasitic simulations Parasitic resistor extract rules no OK ? yes Final verification with Fastrack and release to foundry 8 GDS Jean-Marie Bussat/Patrick Pangaud – 18 March 2018 Final design database

FPPA 2001 design flow Sd. M / design modifications Simplified typical models simulation OK ? Updated design kit Full extract rules Final Layout FPPA 2000 no yes no OK ? Monte-carlo simulation modify design yes Layout redesign and verification GDS Parasitic simulations Parasitic resistor extract rules no OK ? yes Final verification with Fastrack and release to foundry 8 GDS Jean-Marie Bussat/Patrick Pangaud – 18 March 2018 Final design database