f90c1b0cc76f403a9e14aa39514d2eff.ppt

- Количество слайдов: 21

FPGA IP Verification for Use in Severe Environments 2005 MAPLD International Conference September 2005 Paper #237

FPGA IP Verification for Use in Severe Environments 2005 MAPLD International Conference September 2005 Paper #237

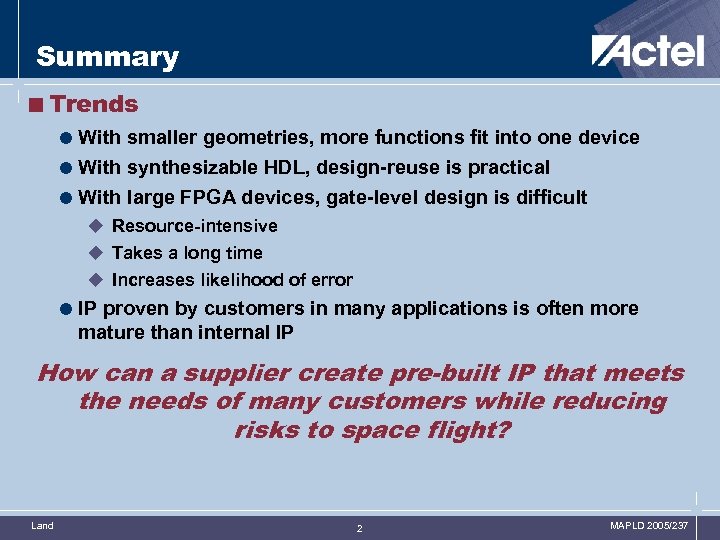

Summary

Summary

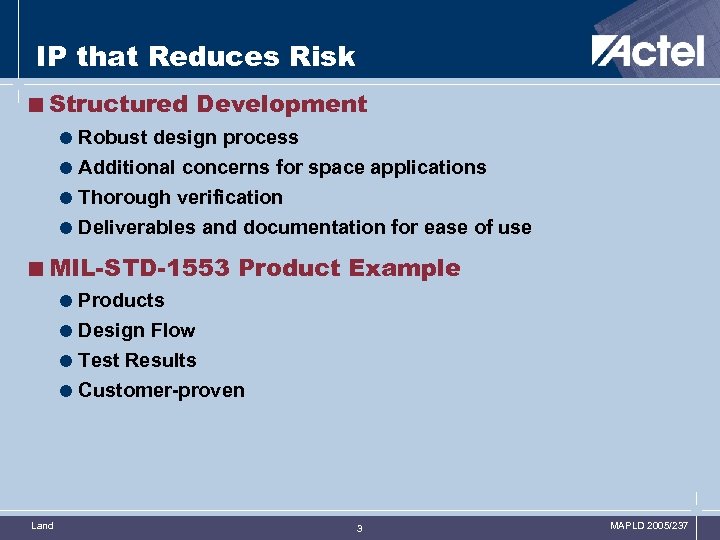

IP that Reduces Risk

IP that Reduces Risk

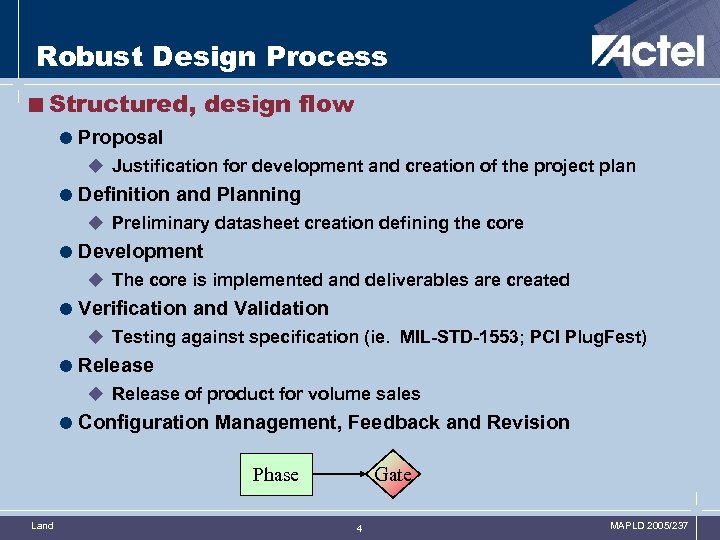

Robust Design Process

Robust Design Process

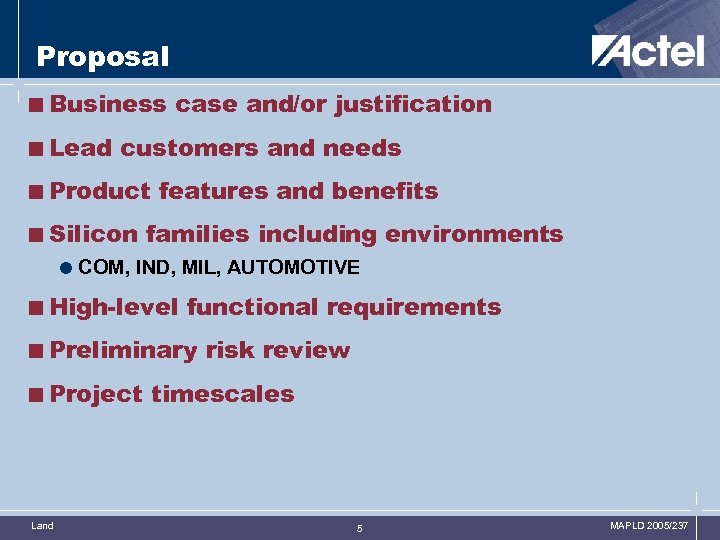

Proposal

Proposal

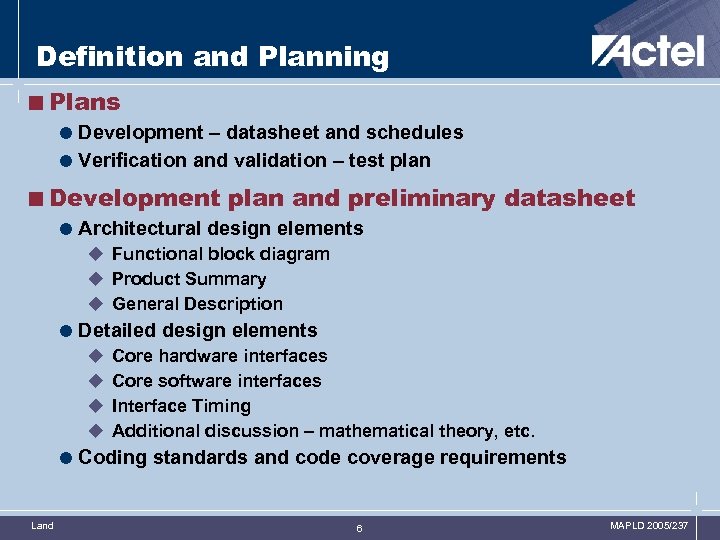

Definition and Planning

Definition and Planning

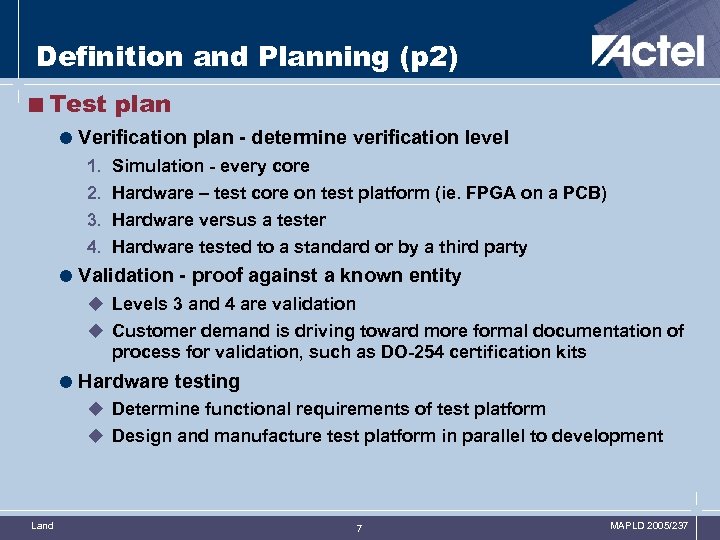

Definition and Planning (p 2)

Definition and Planning (p 2)

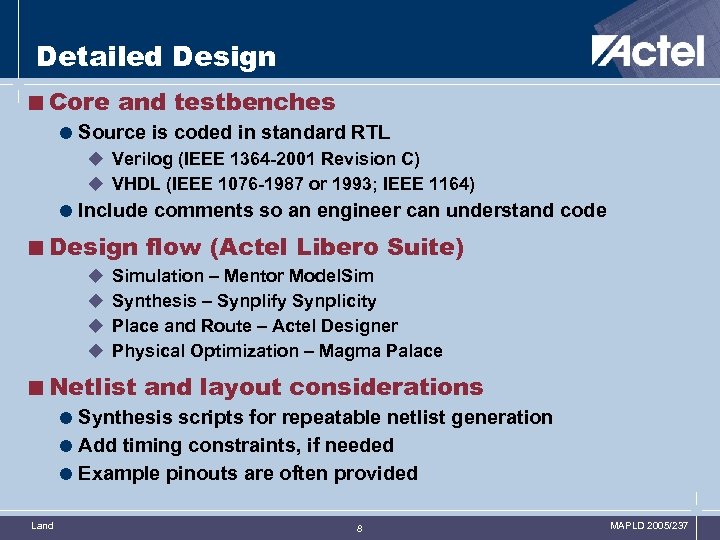

Detailed Design

Detailed Design

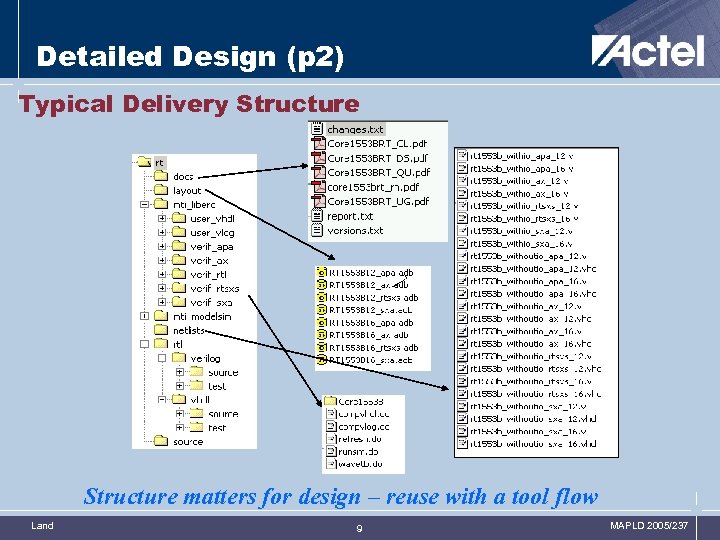

Detailed Design (p 2) Typical Delivery Structure matters for design – reuse with a tool flow Land 9 MAPLD 2005/237

Detailed Design (p 2) Typical Delivery Structure matters for design – reuse with a tool flow Land 9 MAPLD 2005/237

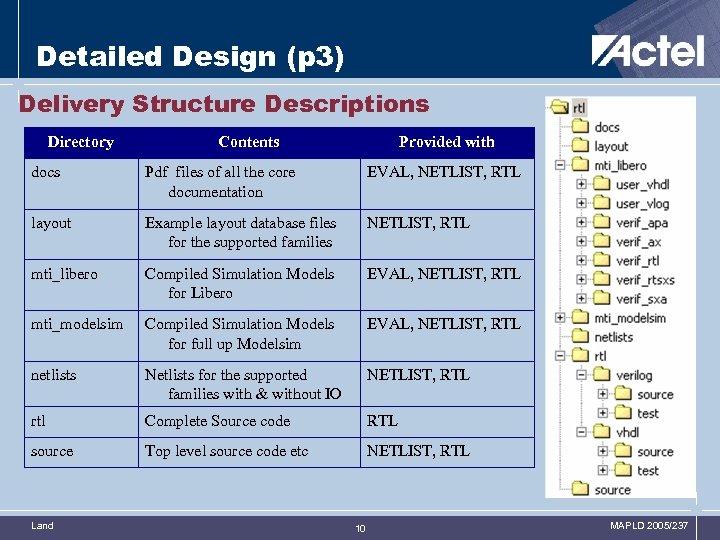

Detailed Design (p 3) Delivery Structure Descriptions Directory Contents Provided with docs Pdf files of all the core documentation EVAL, NETLIST, RTL layout Example layout database files for the supported families NETLIST, RTL mti_libero Compiled Simulation Models for Libero EVAL, NETLIST, RTL mti_modelsim Compiled Simulation Models for full up Modelsim EVAL, NETLIST, RTL netlists Netlists for the supported families with & without IO NETLIST, RTL rtl Complete Source code RTL source Top level source code etc NETLIST, RTL Land 10 MAPLD 2005/237

Detailed Design (p 3) Delivery Structure Descriptions Directory Contents Provided with docs Pdf files of all the core documentation EVAL, NETLIST, RTL layout Example layout database files for the supported families NETLIST, RTL mti_libero Compiled Simulation Models for Libero EVAL, NETLIST, RTL mti_modelsim Compiled Simulation Models for full up Modelsim EVAL, NETLIST, RTL netlists Netlists for the supported families with & without IO NETLIST, RTL rtl Complete Source code RTL source Top level source code etc NETLIST, RTL Land 10 MAPLD 2005/237

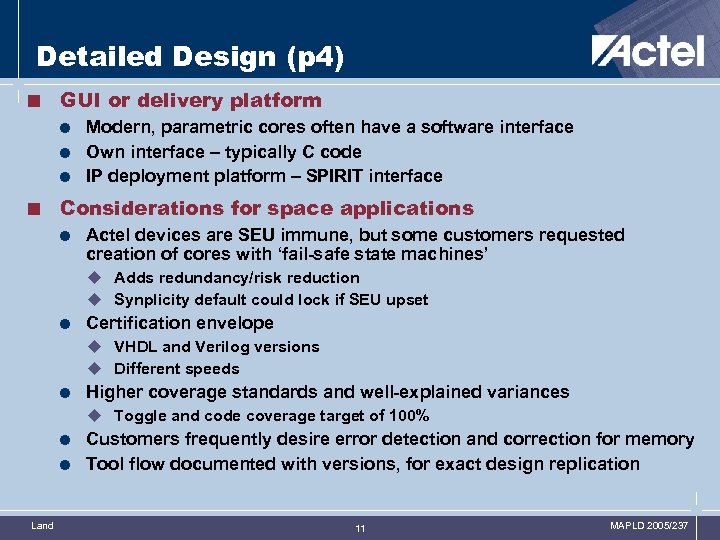

Detailed Design (p 4) < GUI or delivery platform = Modern, parametric cores often have a software interface = Own interface – typically C code = IP deployment platform – SPIRIT interface < Considerations for space applications = Actel devices are SEU immune, but some customers requested creation of cores with ‘fail-safe state machines’ u Adds redundancy/risk reduction u Synplicity default could lock if SEU upset = Certification envelope u VHDL and Verilog versions u Different speeds = Higher coverage standards and well-explained variances u Toggle and code coverage target of 100% = Customers frequently desire error detection and correction for memory = Tool flow documented with versions, for exact design replication Land 11 MAPLD 2005/237

Detailed Design (p 4) < GUI or delivery platform = Modern, parametric cores often have a software interface = Own interface – typically C code = IP deployment platform – SPIRIT interface < Considerations for space applications = Actel devices are SEU immune, but some customers requested creation of cores with ‘fail-safe state machines’ u Adds redundancy/risk reduction u Synplicity default could lock if SEU upset = Certification envelope u VHDL and Verilog versions u Different speeds = Higher coverage standards and well-explained variances u Toggle and code coverage target of 100% = Customers frequently desire error detection and correction for memory = Tool flow documented with versions, for exact design replication Land 11 MAPLD 2005/237

Verification and Validation < Verify per the test plan = Simulations u RTL u Gate-level = Hardware platform u Verify FPGA programming via a checksum test u Evaluate against an analyzer, another HW platform and/or validated tester = Verify key parameters – frequencies, instructions, timing = Check corner cases and unlikely scenarios < Validate = Actual validation required will vary for each core = MIL-STD-1553 cores have 3 rd-party review at Test Systems, Inc. = A validation report review - actions and responses Land 12 MAPLD 2005/237

Verification and Validation < Verify per the test plan = Simulations u RTL u Gate-level = Hardware platform u Verify FPGA programming via a checksum test u Evaluate against an analyzer, another HW platform and/or validated tester = Verify key parameters – frequencies, instructions, timing = Check corner cases and unlikely scenarios < Validate = Actual validation required will vary for each core = MIL-STD-1553 cores have 3 rd-party review at Test Systems, Inc. = A validation report review - actions and responses Land 12 MAPLD 2005/237

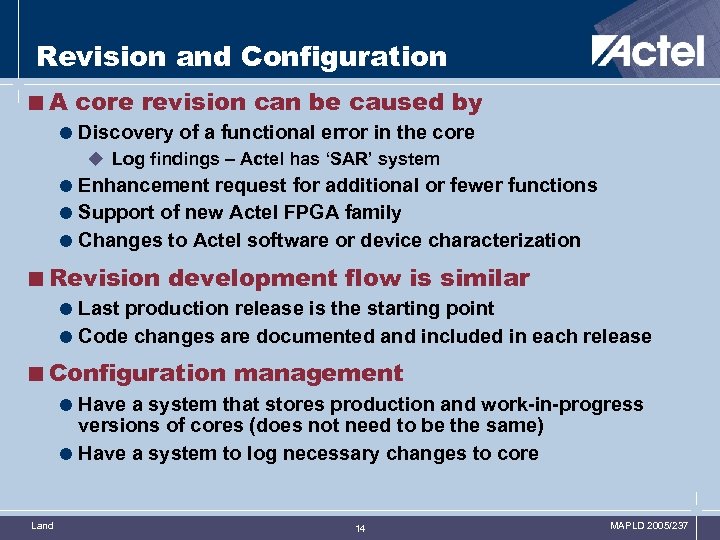

Release

Release

IP that Reduces Risk

IP that Reduces Risk

MIL-STD-1553 Products

MIL-STD-1553 Products

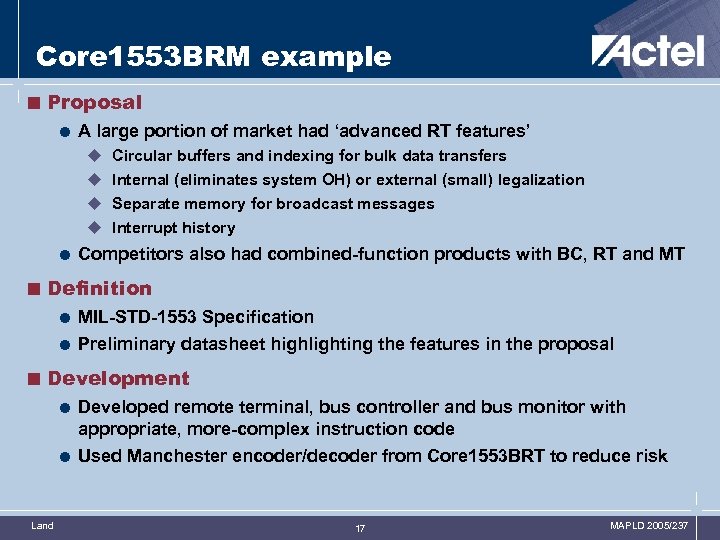

Core 1553 BRM example < Proposal = A large portion of market had ‘advanced RT features’ u Circular buffers and indexing for bulk data transfers u Internal (eliminates system OH) or external (small) legalization u Separate memory for broadcast messages u Interrupt history = Competitors also had combined-function products with BC, RT and MT < Definition = MIL-STD-1553 Specification = Preliminary datasheet highlighting the features in the proposal < Development = Developed remote terminal, bus controller and bus monitor with appropriate, more-complex instruction code = Used Manchester encoder/decoder from Core 1553 BRT to reduce risk Land 17 MAPLD 2005/237

Core 1553 BRM example < Proposal = A large portion of market had ‘advanced RT features’ u Circular buffers and indexing for bulk data transfers u Internal (eliminates system OH) or external (small) legalization u Separate memory for broadcast messages u Interrupt history = Competitors also had combined-function products with BC, RT and MT < Definition = MIL-STD-1553 Specification = Preliminary datasheet highlighting the features in the proposal < Development = Developed remote terminal, bus controller and bus monitor with appropriate, more-complex instruction code = Used Manchester encoder/decoder from Core 1553 BRT to reduce risk Land 17 MAPLD 2005/237

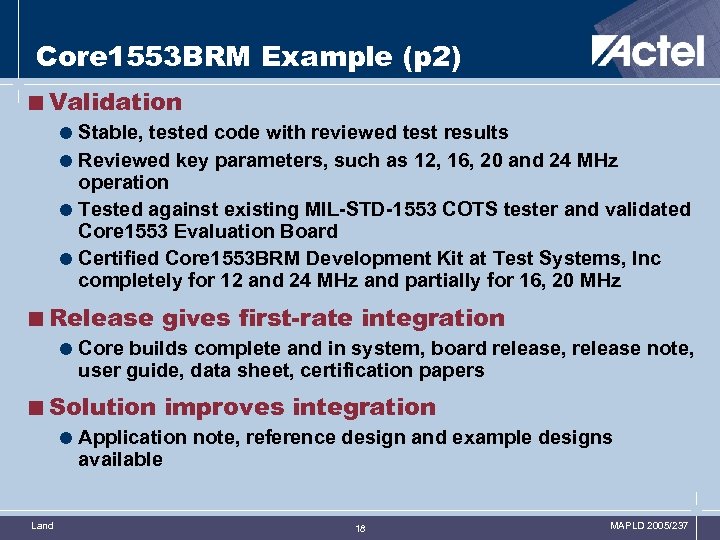

Core 1553 BRM Example (p 2)

Core 1553 BRM Example (p 2)

Core 1553 Customers

Core 1553 Customers

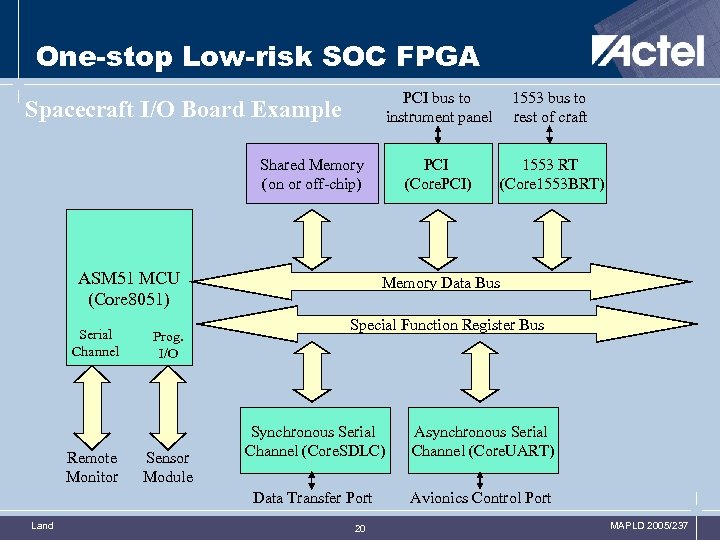

One-stop Low-risk SOC FPGA PCI bus to instrument panel PCI (Core. PCI) Spacecraft I/O Board Example Shared Memory (on or off-chip) ASM 51 MCU (Core 8051) Serial Channel Prog. I/O 1553 bus to rest of craft 1553 RT (Core 1553 BRT) Memory Data Bus Special Function Register Bus Land Sensor Module Asynchronous Serial Channel (Core. UART) Data Transfer Port Remote Monitor Synchronous Serial Channel (Core. SDLC) Avionics Control Port 20 MAPLD 2005/237

One-stop Low-risk SOC FPGA PCI bus to instrument panel PCI (Core. PCI) Spacecraft I/O Board Example Shared Memory (on or off-chip) ASM 51 MCU (Core 8051) Serial Channel Prog. I/O 1553 bus to rest of craft 1553 RT (Core 1553 BRT) Memory Data Bus Special Function Register Bus Land Sensor Module Asynchronous Serial Channel (Core. UART) Data Transfer Port Remote Monitor Synchronous Serial Channel (Core. SDLC) Avionics Control Port 20 MAPLD 2005/237

Conclusion

Conclusion