e12736a8b63b14f374cdf1c5e663f9a2.ppt

- Количество слайдов: 21

FPGA Design Using the LEON 3 Fault Tolerant Processor Core Jiri Gaisler and Sandi Habinc Gaisler 1 MAPLD 2005/1027

FPGA Design Using the LEON 3 Fault Tolerant Processor Core Jiri Gaisler and Sandi Habinc Gaisler 1 MAPLD 2005/1027

Outline § § § § Introduction Fault tolerant LEON 3 processor Design environment Design flow Results Validation Projects and availability Lessons learned Gaisler 2 MAPLD 2005/1027

Outline § § § § Introduction Fault tolerant LEON 3 processor Design environment Design flow Results Validation Projects and availability Lessons learned Gaisler 2 MAPLD 2005/1027

Introduction § High density FPGA devices are now large enough to support SOC design for space application § This allows completely new applications to be implemented in FPGAs, which have previously been limited to ASICs § One problem however remains the same: How to implement fault tolerant processor based SOC designs? Gaisler 3 MAPLD 2005/1027

Introduction § High density FPGA devices are now large enough to support SOC design for space application § This allows completely new applications to be implemented in FPGAs, which have previously been limited to ASICs § One problem however remains the same: How to implement fault tolerant processor based SOC designs? Gaisler 3 MAPLD 2005/1027

Common design issues § Processor availability issues: • Component obsolescence, export licenses etc. § Space application issues: • SEU protection or hardening § System integration issues: • Harmonisation of interfaces (on-chip buses) • Mapping of technology specific cells (RAM) § Software environment issues: • Operating system support Gaisler 4 MAPLD 2005/1027

Common design issues § Processor availability issues: • Component obsolescence, export licenses etc. § Space application issues: • SEU protection or hardening § System integration issues: • Harmonisation of interfaces (on-chip buses) • Mapping of technology specific cells (RAM) § Software environment issues: • Operating system support Gaisler 4 MAPLD 2005/1027

LEON 3 SPARC V 8 Processor § Advanced 32 -bit processor IP core implementing the SPARC V 8 standard instruction set § 7 -stage pipline, hardware mul/div § Separate instruction and data multi-set caches § Multi-processor support (up to 16 processors) § On-chip debug support unit for: • Non-intrusive hardware debugging • Instruction trace buffer • On-chip bus trace buffer Gaisler 5 MAPLD 2005/1027

LEON 3 SPARC V 8 Processor § Advanced 32 -bit processor IP core implementing the SPARC V 8 standard instruction set § 7 -stage pipline, hardware mul/div § Separate instruction and data multi-set caches § Multi-processor support (up to 16 processors) § On-chip debug support unit for: • Non-intrusive hardware debugging • Instruction trace buffer • On-chip bus trace buffer Gaisler 5 MAPLD 2005/1027

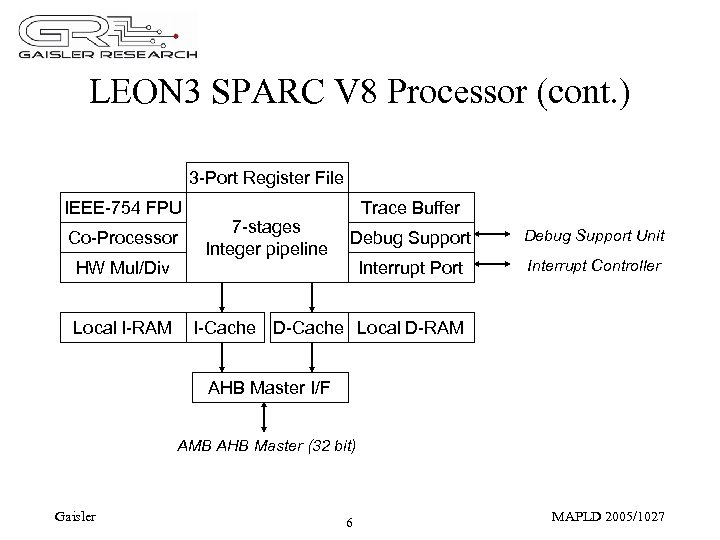

LEON 3 SPARC V 8 Processor (cont. ) 3 -Port Register File IEEE-754 FPU Co-Processor HW Mul/Div Local I-RAM 7 -stages Integer pipeline Trace Buffer Debug Support Unit Interrupt Port Interrupt Controller I-Cache D-Cache Local D-RAM AHB Master I/F AMB AHB Master (32 bit) Gaisler 6 MAPLD 2005/1027

LEON 3 SPARC V 8 Processor (cont. ) 3 -Port Register File IEEE-754 FPU Co-Processor HW Mul/Div Local I-RAM 7 -stages Integer pipeline Trace Buffer Debug Support Unit Interrupt Port Interrupt Controller I-Cache D-Cache Local D-RAM AHB Master I/F AMB AHB Master (32 bit) Gaisler 6 MAPLD 2005/1027

LEON 3 Fault Tolerant Processor § SEU tolerance by design for space applications § All on-chip memory protected against SEUs: • 136 x 32 bit register file: 4 -bit parity and duplication • Cache RAMs use 4 -bit parity and forced cache miss on error • No timing penalty • Instruction re-scheduling on error § Flip-flops assumed to be protected by technology specific cells (or by TMR) Gaisler 7 MAPLD 2005/1027

LEON 3 Fault Tolerant Processor § SEU tolerance by design for space applications § All on-chip memory protected against SEUs: • 136 x 32 bit register file: 4 -bit parity and duplication • Cache RAMs use 4 -bit parity and forced cache miss on error • No timing penalty • Instruction re-scheduling on error § Flip-flops assumed to be protected by technology specific cells (or by TMR) Gaisler 7 MAPLD 2005/1027

LEON 3 design environment § LEON 3 is part of a complete design environment: • Floating Point Unit, Mul/Div • Timers, Interrupt Controller, • Memory controllers (SRAM, SDRAM) • Space. Wire, CAN, Ethernet, PS 2, UART, PCI, MIL-STD-1553 B • CCSDS Telemetry/Telecommand § AMBA on-chip bus with new Plug and Play support § Support for many tools and prototyping boards § Support for portability between technologies Gaisler 8 MAPLD 2005/1027

LEON 3 design environment § LEON 3 is part of a complete design environment: • Floating Point Unit, Mul/Div • Timers, Interrupt Controller, • Memory controllers (SRAM, SDRAM) • Space. Wire, CAN, Ethernet, PS 2, UART, PCI, MIL-STD-1553 B • CCSDS Telemetry/Telecommand § AMBA on-chip bus with new Plug and Play support § Support for many tools and prototyping boards § Support for portability between technologies Gaisler 8 MAPLD 2005/1027

Typical design flow § Download LEON 3 source code from the web § Modify design example by adding design blocks § Simulate using one of many simulators (several simulators supported, one free) § Synthesize using one of many tools (several tools supported, some free) § Place and route FPGA using vendor specific tools (several FPGA vendors supported, some free) § Target design to one of many development boards (several boards supported) Gaisler 9 MAPLD 2005/1027

Typical design flow § Download LEON 3 source code from the web § Modify design example by adding design blocks § Simulate using one of many simulators (several simulators supported, one free) § Synthesize using one of many tools (several tools supported, some free) § Place and route FPGA using vendor specific tools (several FPGA vendors supported, some free) § Target design to one of many development boards (several boards supported) Gaisler 9 MAPLD 2005/1027

Fault Tolerant design flow § Modify LEON 3 design example by adding additional design blocks § Synthesize and place and route design (e. g. free Xilinx XST web-pack or Altera Quartus web-pack) § Validate the design on your prototype board § This complete initial flow is based on the non-FT version of LEON 3 Gaisler 10 MAPLD 2005/1027

Fault Tolerant design flow § Modify LEON 3 design example by adding additional design blocks § Synthesize and place and route design (e. g. free Xilinx XST web-pack or Altera Quartus web-pack) § Validate the design on your prototype board § This complete initial flow is based on the non-FT version of LEON 3 Gaisler 10 MAPLD 2005/1027

Fault Tolerant design flow (cont. ) § Synthesize design, using e. g. Synplify, targeting Actel RTAX-S § Place and route design using Actel Designer, including the LEON 3 -FT EDIF netlist § Validate the design on your enginering or flight board § The only thing changed is the LEON 3 -FT core Gaisler 11 MAPLD 2005/1027

Fault Tolerant design flow (cont. ) § Synthesize design, using e. g. Synplify, targeting Actel RTAX-S § Place and route design using Actel Designer, including the LEON 3 -FT EDIF netlist § Validate the design on your enginering or flight board § The only thing changed is the LEON 3 -FT core Gaisler 11 MAPLD 2005/1027

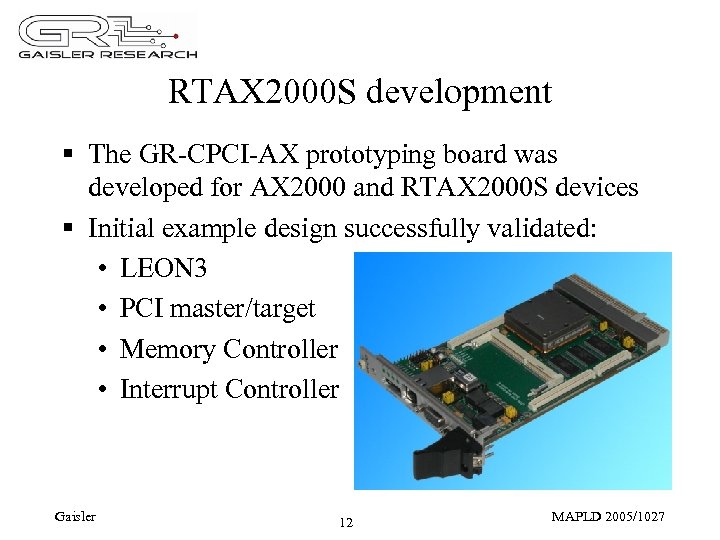

RTAX 2000 S development § The GR-CPCI-AX prototyping board was developed for AX 2000 and RTAX 2000 S devices § Initial example design successfully validated: • LEON 3 • PCI master/target • Memory Controller • Interrupt Controller Gaisler 12 MAPLD 2005/1027

RTAX 2000 S development § The GR-CPCI-AX prototyping board was developed for AX 2000 and RTAX 2000 S devices § Initial example design successfully validated: • LEON 3 • PCI master/target • Memory Controller • Interrupt Controller Gaisler 12 MAPLD 2005/1027

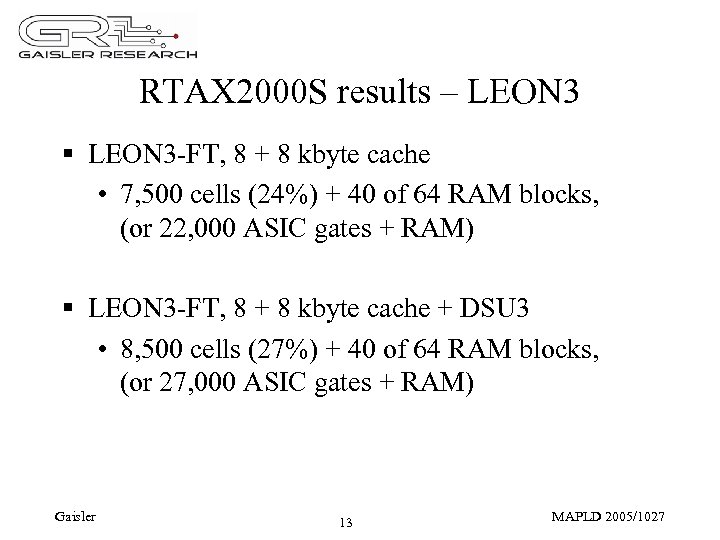

RTAX 2000 S results – LEON 3 § LEON 3 -FT, 8 + 8 kbyte cache • 7, 500 cells (24%) + 40 of 64 RAM blocks, (or 22, 000 ASIC gates + RAM) § LEON 3 -FT, 8 + 8 kbyte cache + DSU 3 • 8, 500 cells (27%) + 40 of 64 RAM blocks, (or 27, 000 ASIC gates + RAM) Gaisler 13 MAPLD 2005/1027

RTAX 2000 S results – LEON 3 § LEON 3 -FT, 8 + 8 kbyte cache • 7, 500 cells (24%) + 40 of 64 RAM blocks, (or 22, 000 ASIC gates + RAM) § LEON 3 -FT, 8 + 8 kbyte cache + DSU 3 • 8, 500 cells (27%) + 40 of 64 RAM blocks, (or 27, 000 ASIC gates + RAM) Gaisler 13 MAPLD 2005/1027

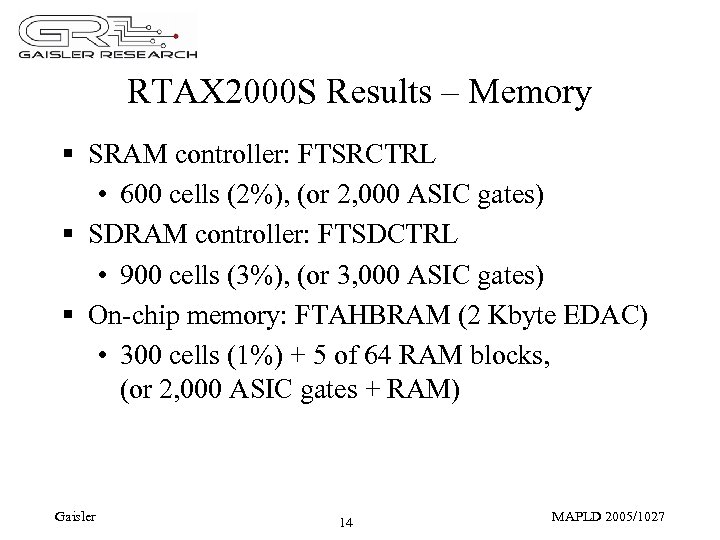

RTAX 2000 S Results – Memory § SRAM controller: FTSRCTRL • 600 cells (2%), (or 2, 000 ASIC gates) § SDRAM controller: FTSDCTRL • 900 cells (3%), (or 3, 000 ASIC gates) § On-chip memory: FTAHBRAM (2 Kbyte EDAC) • 300 cells (1%) + 5 of 64 RAM blocks, (or 2, 000 ASIC gates + RAM) Gaisler 14 MAPLD 2005/1027

RTAX 2000 S Results – Memory § SRAM controller: FTSRCTRL • 600 cells (2%), (or 2, 000 ASIC gates) § SDRAM controller: FTSDCTRL • 900 cells (3%), (or 3, 000 ASIC gates) § On-chip memory: FTAHBRAM (2 Kbyte EDAC) • 300 cells (1%) + 5 of 64 RAM blocks, (or 2, 000 ASIC gates + RAM) Gaisler 14 MAPLD 2005/1027

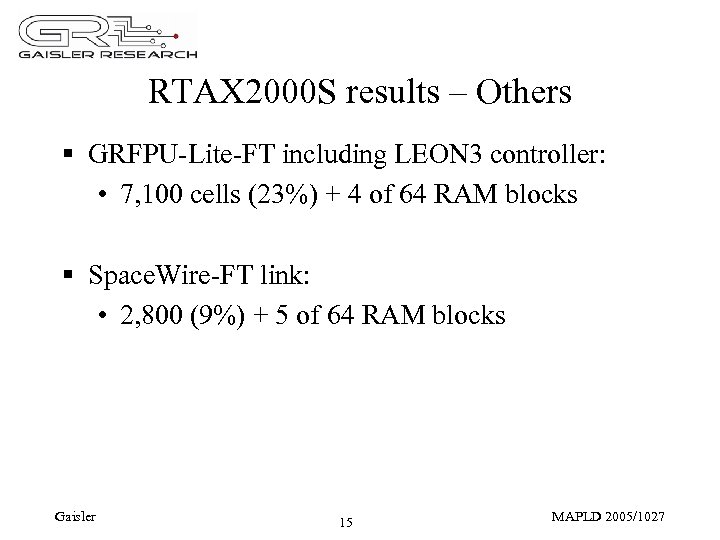

RTAX 2000 S results – Others § GRFPU-Lite-FT including LEON 3 controller: • 7, 100 cells (23%) + 4 of 64 RAM blocks § Space. Wire-FT link: • 2, 800 (9%) + 5 of 64 RAM blocks Gaisler 15 MAPLD 2005/1027

RTAX 2000 S results – Others § GRFPU-Lite-FT including LEON 3 controller: • 7, 100 cells (23%) + 4 of 64 RAM blocks § Space. Wire-FT link: • 2, 800 (9%) + 5 of 64 RAM blocks Gaisler 15 MAPLD 2005/1027

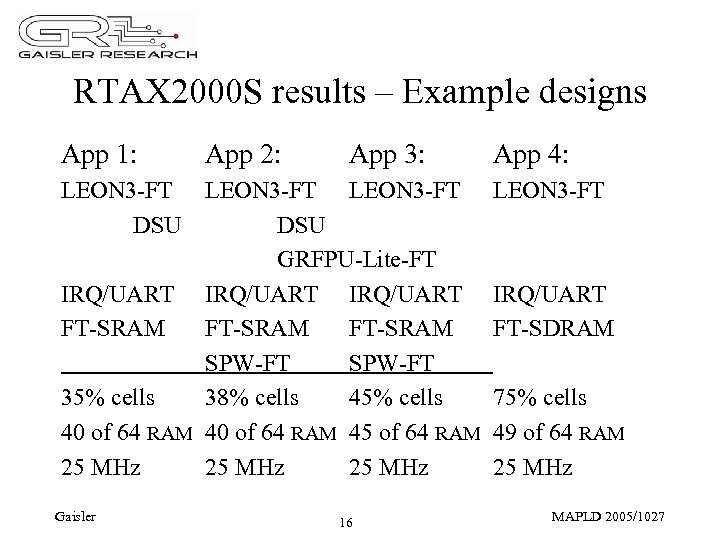

RTAX 2000 S results – Example designs App 1: App 2: App 3: LEON 3 -FT DSU GRFPU-Lite-FT IRQ/UART FT-SRAM SPW-FT 35% cells 38% cells 45% cells 40 of 64 RAM 45 of 64 RAM 25 MHz Gaisler 16 App 4: LEON 3 -FT IRQ/UART FT-SDRAM 75% cells 49 of 64 RAM 25 MHz MAPLD 2005/1027

RTAX 2000 S results – Example designs App 1: App 2: App 3: LEON 3 -FT DSU GRFPU-Lite-FT IRQ/UART FT-SRAM SPW-FT 35% cells 38% cells 45% cells 40 of 64 RAM 45 of 64 RAM 25 MHz Gaisler 16 App 4: LEON 3 -FT IRQ/UART FT-SDRAM 75% cells 49 of 64 RAM 25 MHz MAPLD 2005/1027

Validation § § § LEON 3 has passed SPARC V 8 validation AX 2000 based design running since 2005 Q 2 RTAX 2000 S based design planned for 2005 Q 3 Software induced SEU testing on-going Radiation testing planned for 2005 Q 3: • Heavy Ion • Californium • Louvain-la-Neuve • Proton Gaisler 17 MAPLD 2005/1027

Validation § § § LEON 3 has passed SPARC V 8 validation AX 2000 based design running since 2005 Q 2 RTAX 2000 S based design planned for 2005 Q 3 Software induced SEU testing on-going Radiation testing planned for 2005 Q 3: • Heavy Ion • Californium • Louvain-la-Neuve • Proton Gaisler 17 MAPLD 2005/1027

Projects § LEON 3 -FT processor being evaluated in the frame of the European spacecraft Bepi-Colombo • To be used in 5 -10 different instruments as primary controller • Includes Space. Wire interface and Floating Point Unit § LEON 3 -FT processor is on the road map for the European Space Agency, replacing the LEON 2 processor Gaisler 18 MAPLD 2005/1027

Projects § LEON 3 -FT processor being evaluated in the frame of the European spacecraft Bepi-Colombo • To be used in 5 -10 different instruments as primary controller • Includes Space. Wire interface and Floating Point Unit § LEON 3 -FT processor is on the road map for the European Space Agency, replacing the LEON 2 processor Gaisler 18 MAPLD 2005/1027

LEON 3 Availablity § § Freely available in source code under GNU GPL Valuable tool for academic research Improves test-coverage due to large user-base Allows early prototyping and try-before-buy § Commercial licensing possible without restrictions § The fault-tolerant version of the cores are not initially released in open-source, but the long-term strategy is to release all cores under GPL Gaisler 19 MAPLD 2005/1027

LEON 3 Availablity § § Freely available in source code under GNU GPL Valuable tool for academic research Improves test-coverage due to large user-base Allows early prototyping and try-before-buy § Commercial licensing possible without restrictions § The fault-tolerant version of the cores are not initially released in open-source, but the long-term strategy is to release all cores under GPL Gaisler 19 MAPLD 2005/1027

Lessons learned § Fault tolerance implementation differs between ASIC and FPGA: • The critical timing paths for ASIC and FPGA differs, forcing different FT implementations • FPGAs have fixed on-chip resources that can be used for FT implemenation without additional area penalty § Mixed GPL and commercial licensing model necessary to allow both academic and commercial use Gaisler 20 MAPLD 2005/1027

Lessons learned § Fault tolerance implementation differs between ASIC and FPGA: • The critical timing paths for ASIC and FPGA differs, forcing different FT implementations • FPGAs have fixed on-chip resources that can be used for FT implemenation without additional area penalty § Mixed GPL and commercial licensing model necessary to allow both academic and commercial use Gaisler 20 MAPLD 2005/1027

Conclusions § LEON 3 Fault Tolerant SPARC processor core is ready for FPGA /ASIC integration, including: • SEU protection • Design environment with several cores • Development board for RTAX and AX § RTAX 2000 S with LEON 3 -FT leaves ample space for customer specific logic and memory: • Cells: 25% to 65% (up to 60 k ASIC gates) • RAM: 24% to 37% (up to 100 k bits) Gaisler 21 MAPLD 2005/1027

Conclusions § LEON 3 Fault Tolerant SPARC processor core is ready for FPGA /ASIC integration, including: • SEU protection • Design environment with several cores • Development board for RTAX and AX § RTAX 2000 S with LEON 3 -FT leaves ample space for customer specific logic and memory: • Cells: 25% to 65% (up to 60 k ASIC gates) • RAM: 24% to 37% (up to 100 k bits) Gaisler 21 MAPLD 2005/1027