14cf8295c18564c2e3709357130d3e7c.ppt

- Количество слайдов: 27

First fabrication of full -detectors at SINTEF 3 D Pixel 2008 International Workshop, FNAL September 23 -26, 2008 T. E. Hansena, A. Koka, C. Da’Viab, T. A. Hansena, J. Hasib, C. Kenneyd, N. Lietaera, M. Mielnika, S. Parkerc, P. Storåsa a SINTEF Mi. Na. Lab, Norway b The University of Manchester, UK c The University of Hawaii, USA d Molecular Biology Consortium, USA ICT 1

Outline n Motivation for 3 D-detector activity and SINTEF involvement n Technology issues n Results from first SINTEF 3 D-run n Further developments and next run ICT 2

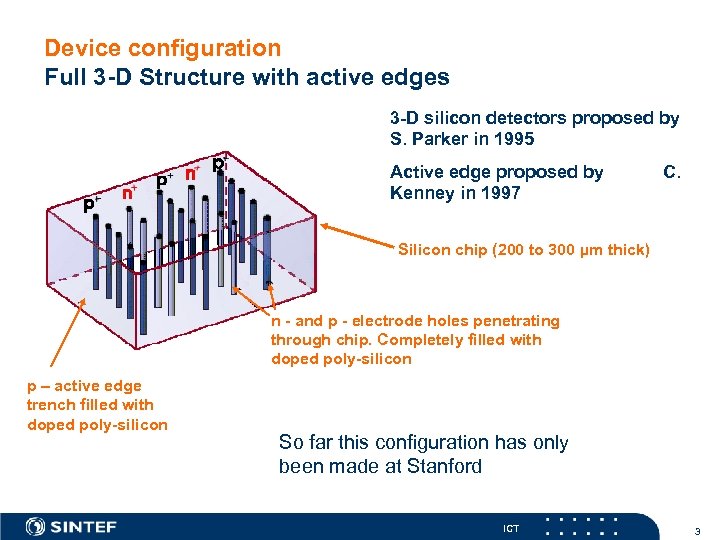

Device configuration Full 3 -D Structure with active edges 3 -D silicon detectors proposed by S. Parker in 1995 Active edge proposed by Kenney in 1997 C. Silicon chip (200 to 300 µm thick) n - and p - electrode holes penetrating through chip. Completely filled with doped poly-silicon p – active edge trench filled with doped poly-silicon So far this configuration has only been made at Stanford ICT 3

Motivation for 3 D-detectors n Advantages of 3 D-detectors n Low pre-irradiated depletion voltage n Fast time response n Edgeless capability (active edge), no dead area due to broad guard ring areas n Non surpassed radiation hardness Motivation for SINTEF to get involved n SINTEF joined 3 D-collaboration in 2006. Part of effort to transfer 3 D technology to affordable(? ) small and medium scale production n Processing line adapted to detector fabrication. Experience in detector technology since early 1980 ties n Number of in-house state-of-art Deep Reactive Ion Etchers (DRIE) n Long experience in 3 D silicon micromachining ICT 4

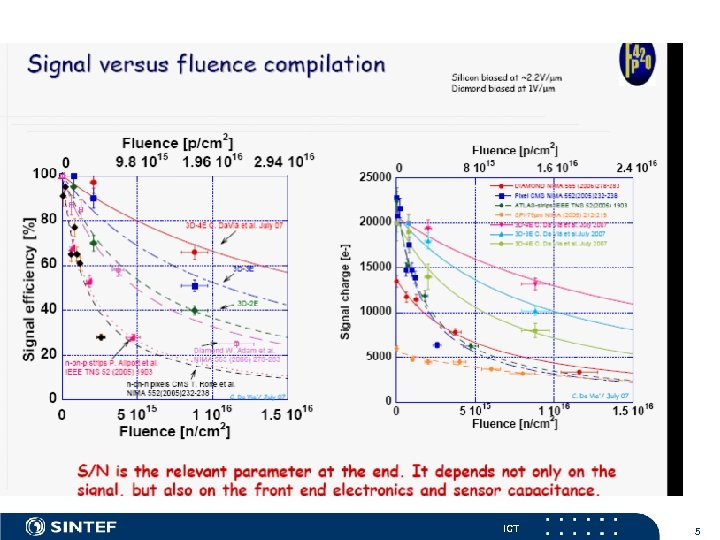

ICT 5

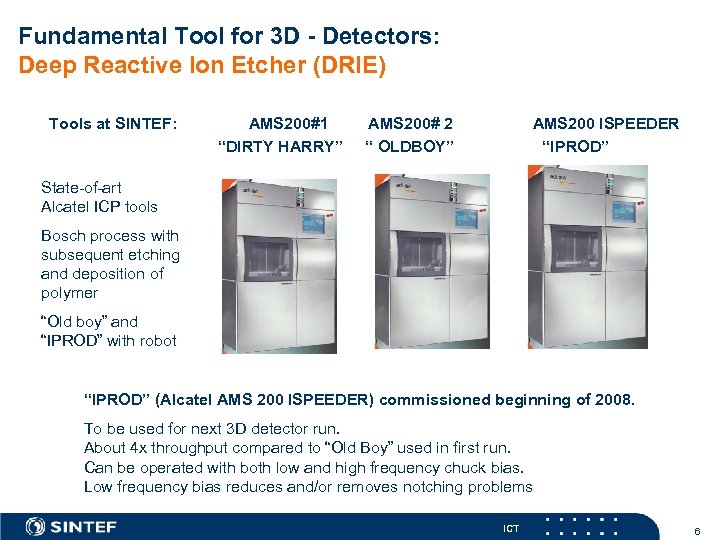

Fundamental Tool for 3 D - Detectors: Deep Reactive Ion Etcher (DRIE) Tools at SINTEF: AMS 200#1 “DIRTY HARRY” AMS 200# 2 “ OLDBOY” AMS 200 ISPEEDER “IPROD” State-of-art Alcatel ICP tools Bosch process with subsequent etching and deposition of polymer “Old boy” and “IPROD” with robot “IPROD” (Alcatel AMS 200 ISPEEDER) commissioned beginning of 2008. To be used for next 3 D detector run. About 4 x throughput compared to “Old Boy” used in first run. Can be operated with both low and high frequency chuck bias. Low frequency bias reduces and/or removes notching problems ICT 6

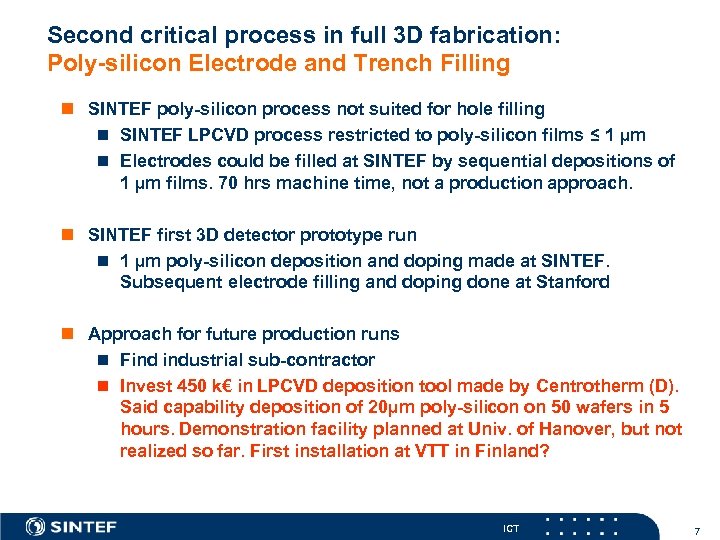

Second critical process in full 3 D fabrication: Poly-silicon Electrode and Trench Filling n SINTEF poly-silicon process not suited for hole filling n SINTEF LPCVD process restricted to poly-silicon films ≤ 1 µm n Electrodes could be filled at SINTEF by sequential depositions of 1 µm films. 70 hrs machine time, not a production approach. n SINTEF first 3 D detector prototype run n 1 µm poly-silicon deposition and doping made at SINTEF. Subsequent electrode filling and doping done at Stanford n Approach for future production runs n Find industrial sub-contractor n Invest 450 k€ in LPCVD deposition tool made by Centrotherm (D). Said capability deposition of 20µm poly-silicon on 50 wafers in 5 hours. Demonstration facility planned at Univ. of Hanover, but not realized so far. First installation at VTT in Finland? ICT 7

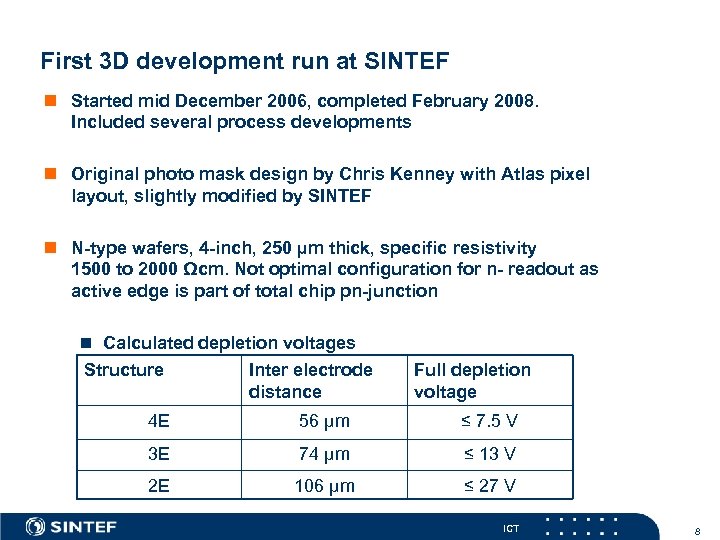

First 3 D development run at SINTEF n Started mid December 2006, completed February 2008. Included several process developments n Original photo mask design by Chris Kenney with Atlas pixel layout, slightly modified by SINTEF n N-type wafers, 4 -inch, 250 µm thick, specific resistivity 1500 to 2000 Ωcm. Not optimal configuration for n- readout as active edge is part of total chip pn-junction n Calculated depletion voltages Structure Inter electrode distance Full depletion voltage 4 E 56 µm ≤ 7. 5 V 3 E 74 µm ≤ 13 V 2 E 106 µm ≤ 27 V ICT 8

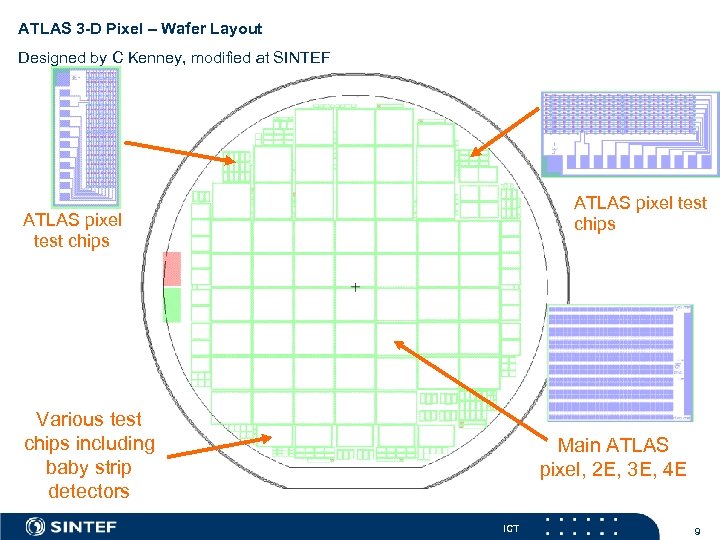

ATLAS 3 -D Pixel – Wafer Layout Designed by C Kenney, modified at SINTEF ATLAS pixel test chips Various test chips including baby strip detectors Main ATLAS pixel, 2 E, 3 E, 4 E ICT 9

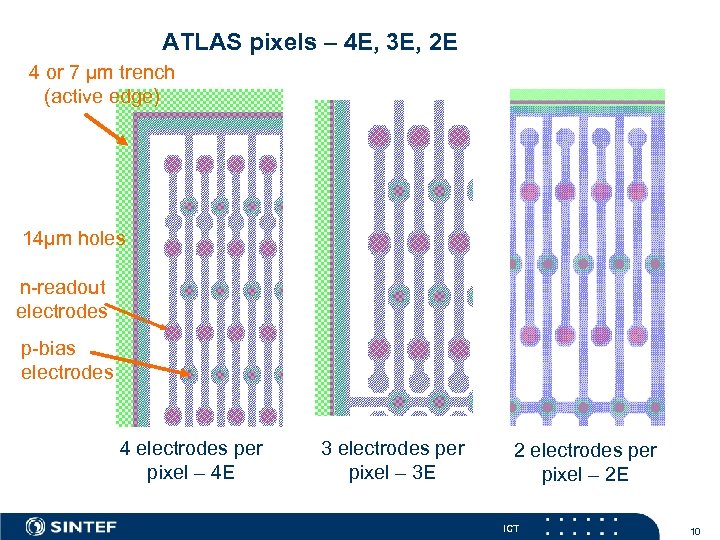

ATLAS pixels – 4 E, 3 E, 2 E 4 or 7 µm trench (active edge) 14µm holes n-readout electrodes p-bias electrodes 4 electrodes per pixel – 4 E 3 electrodes per pixel – 3 E 2 electrodes per pixel – 2 E ICT 10

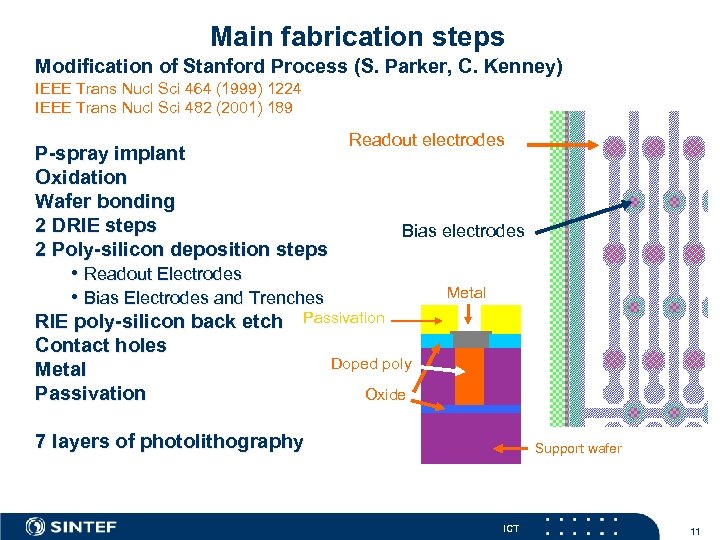

Main fabrication steps Modification of Stanford Process (S. Parker, C. Kenney) IEEE Trans Nucl Sci 464 (1999) 1224 IEEE Trans Nucl Sci 482 (2001) 189 Readout electrodes P-spray implant Oxidation Wafer bonding 2 DRIE steps Bias electrodes 2 Poly-silicon deposition steps • Readout Electrodes Metal • Bias Electrodes and Trenches RIE poly-silicon back etch Passivation Contact holes Doped poly Metal Oxide Passivation 7 layers of photolithography Support wafer ICT 11

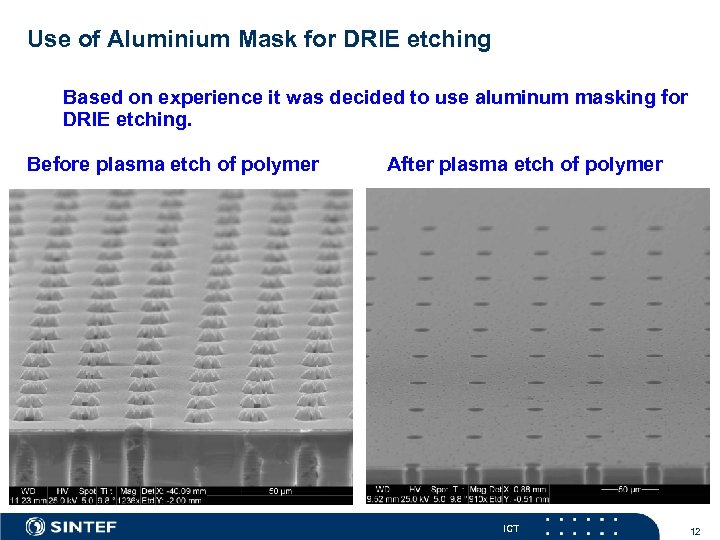

Use of Aluminium Mask for DRIE etching Based on experience it was decided to use aluminum masking for DRIE etching. Before plasma etch of polymer After plasma etch of polymer ICT 12

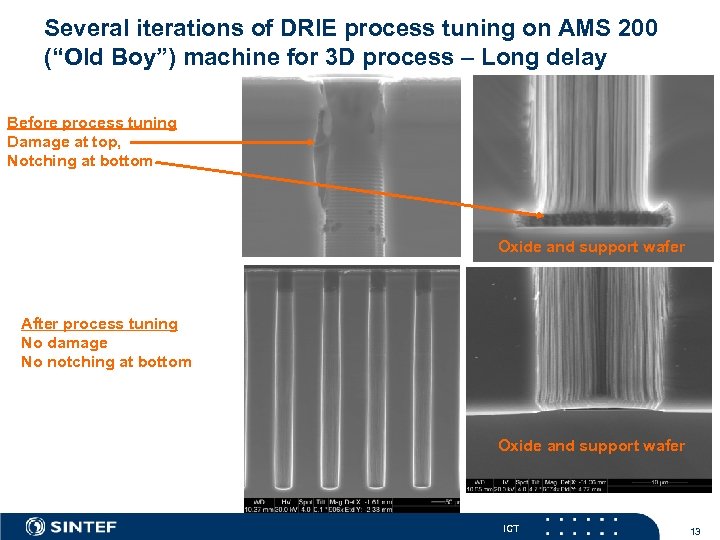

Several iterations of DRIE process tuning on AMS 200 (“Old Boy”) machine for 3 D process – Long delay Before process tuning Damage at top, Notching at bottom Oxide and support wafer After process tuning No damage No notching at bottom Oxide and support wafer ICT 13

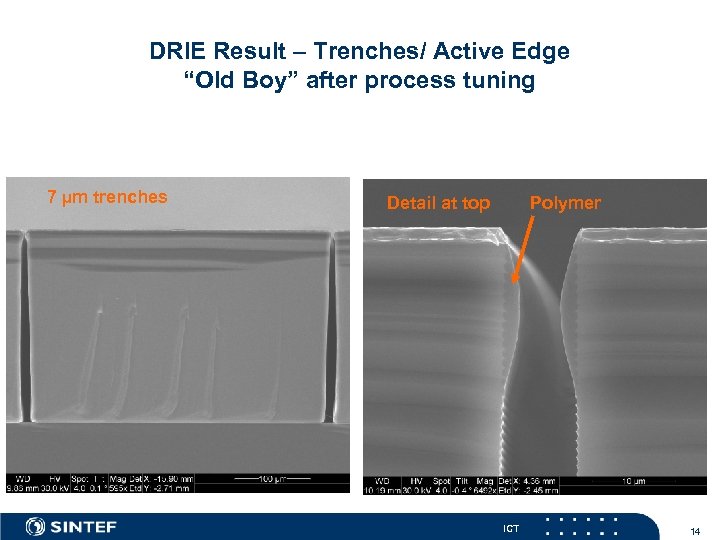

DRIE Result – Trenches/ Active Edge “Old Boy” after process tuning 7 µm trenches Detail at top Polymer ICT 14

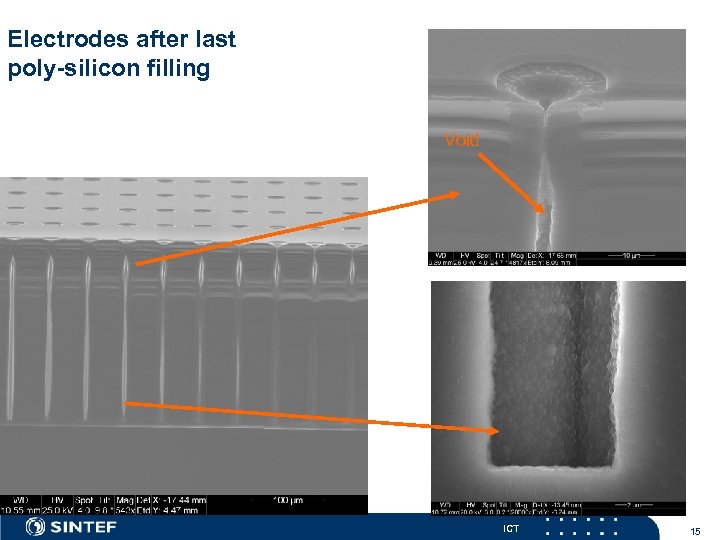

Electrodes after last poly-silicon filling Void ICT 15

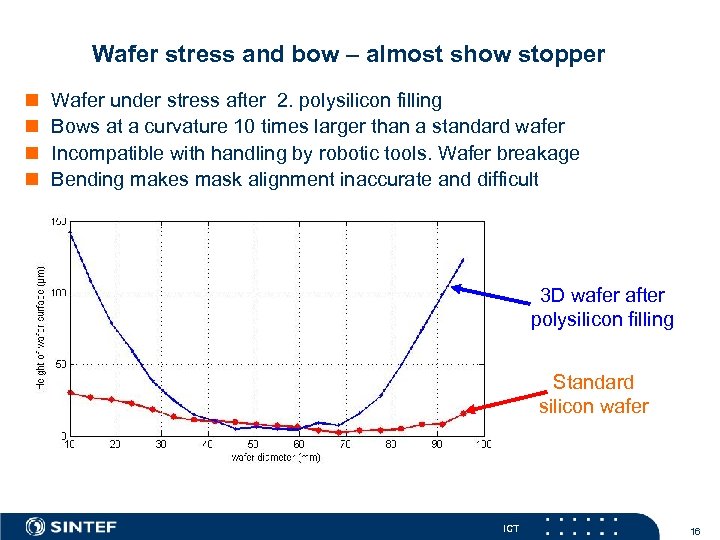

Wafer stress and bow – almost show stopper n n Wafer under stress after 2. polysilicon filling Bows at a curvature 10 times larger than a standard wafer Incompatible with handling by robotic tools. Wafer breakage Bending makes mask alignment inaccurate and difficult 3 D wafer after polysilicon filling Standard silicon wafer ICT 16

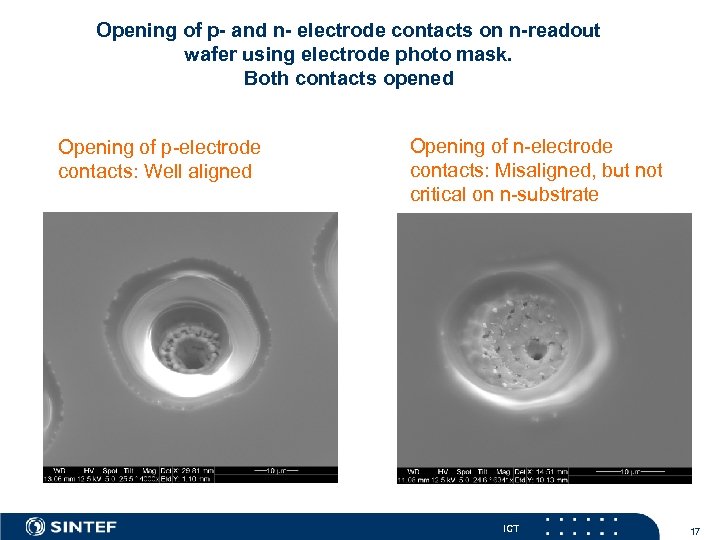

Opening of p- and n- electrode contacts on n-readout wafer using electrode photo mask. Both contacts opened Opening of p-electrode contacts: Well aligned Opening of n-electrode contacts: Misaligned, but not critical on n-substrate ICT 17

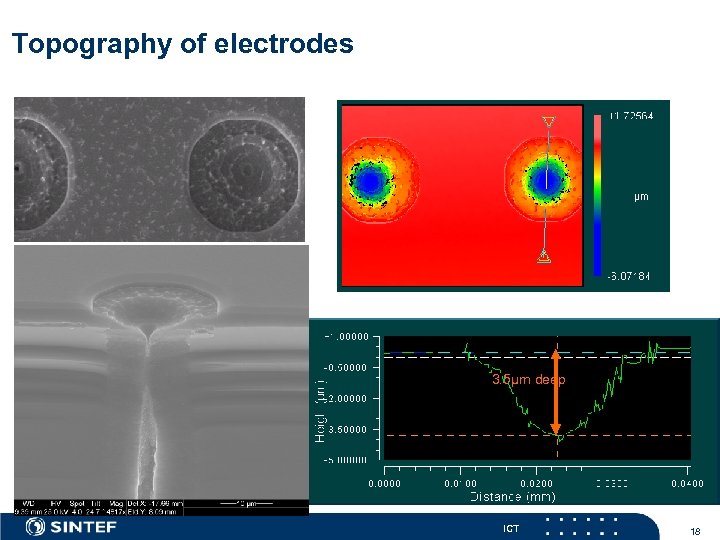

Topography of electrodes 3. 5µm deep ICT 18

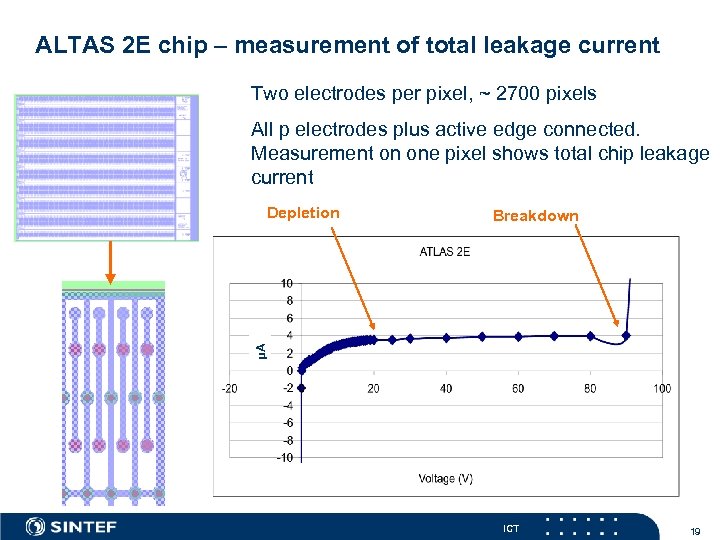

ALTAS 2 E chip – measurement of total leakage current Two electrodes per pixel, ~ 2700 pixels All p electrodes plus active edge connected. Measurement on one pixel shows total chip leakage current Breakdown µA Depletion ICT 19

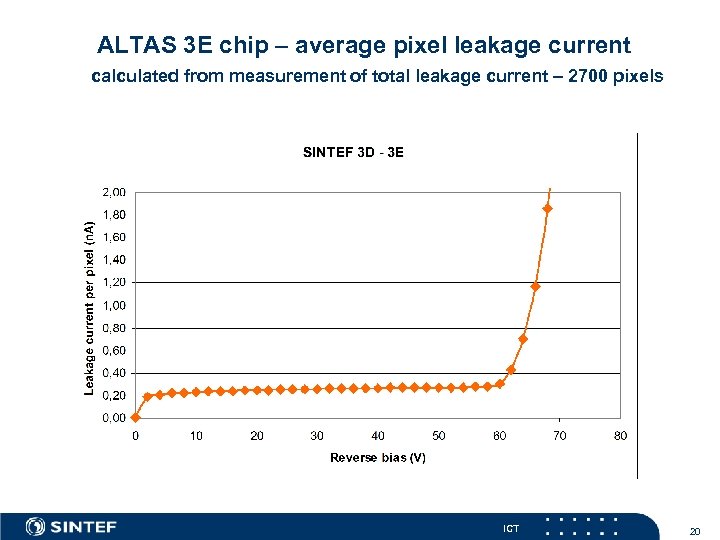

ALTAS 3 E chip – average pixel leakage current calculated from measurement of total leakage current – 2700 pixels ICT 20

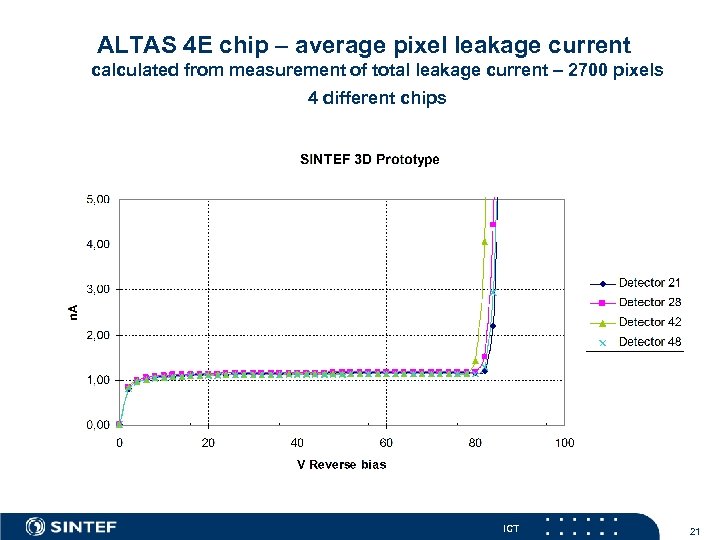

ALTAS 4 E chip – average pixel leakage current calculated from measurement of total leakage current – 2700 pixels 4 different chips ICT 21

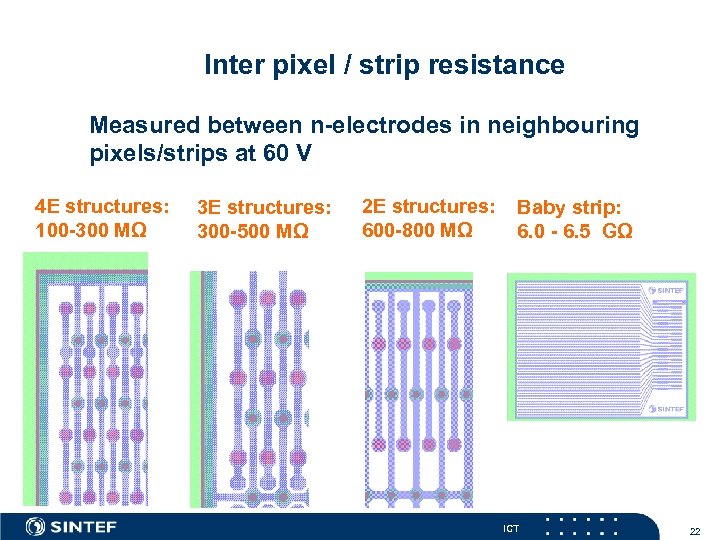

Inter pixel / strip resistance Measured between n-electrodes in neighbouring pixels/strips at 60 V 4 E structures: 100 -300 MΩ 3 E structures: 300 -500 MΩ 2 E structures: 600 -800 MΩ Baby strip: 6. 0 - 6. 5 GΩ ICT 22

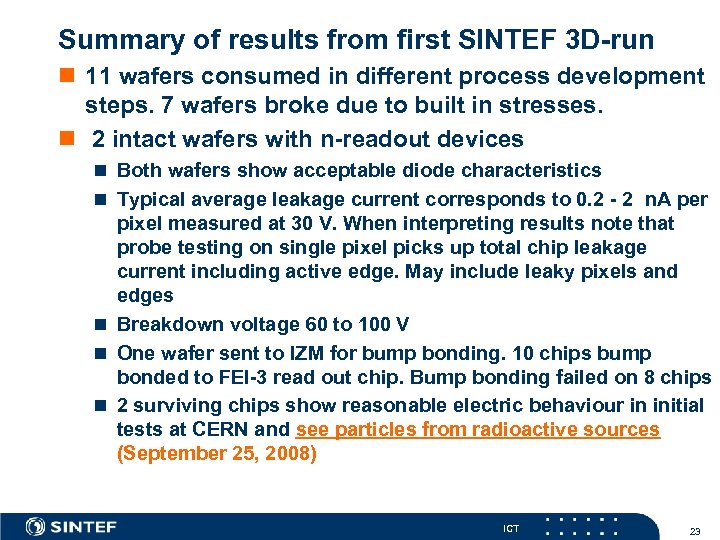

Summary of results from first SINTEF 3 D-run n 11 wafers consumed in different process development steps. 7 wafers broke due to built in stresses. n 2 intact wafers with n-readout devices n Both wafers show acceptable diode characteristics n Typical average leakage current corresponds to 0. 2 - 2 n. A per pixel measured at 30 V. When interpreting results note that probe testing on single pixel picks up total chip leakage current including active edge. May include leaky pixels and edges n Breakdown voltage 60 to 100 V n One wafer sent to IZM for bump bonding. 10 chips bump bonded to FEI-3 read out chip. Bump bonding failed on 8 chips n 2 surviving chips show reasonable electric behaviour in initial tests at CERN and see particles from radioactive sources (September 25, 2008) ICT 23

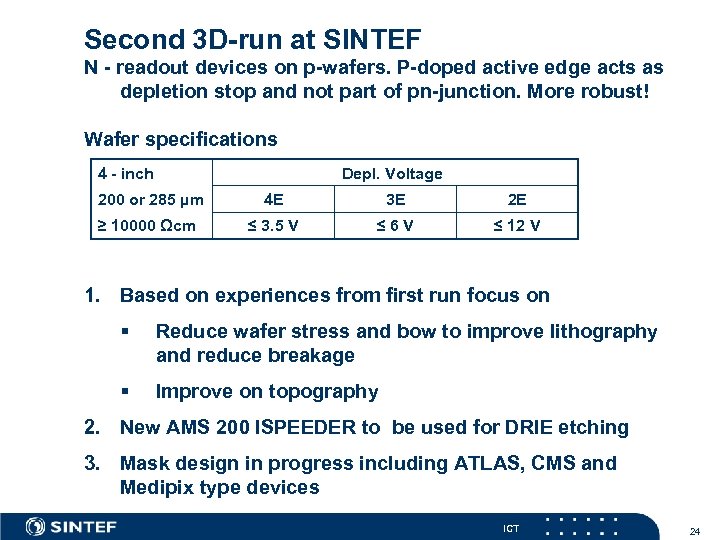

Second 3 D-run at SINTEF N - readout devices on p-wafers. P-doped active edge acts as depletion stop and not part of pn-junction. More robust! Wafer specifications 4 - inch Depl. Voltage 200 or 285 µm 4 E 3 E 2 E ≥ 10000 Ωcm ≤ 3. 5 V ≤ 6 V ≤ 12 V 1. Based on experiences from first run focus on § Reduce wafer stress and bow to improve lithography and reduce breakage § Improve on topography 2. New AMS 200 ISPEEDER to be used for DRIE etching 3. Mask design in progress including ATLAS, CMS and Medipix type devices ICT 24

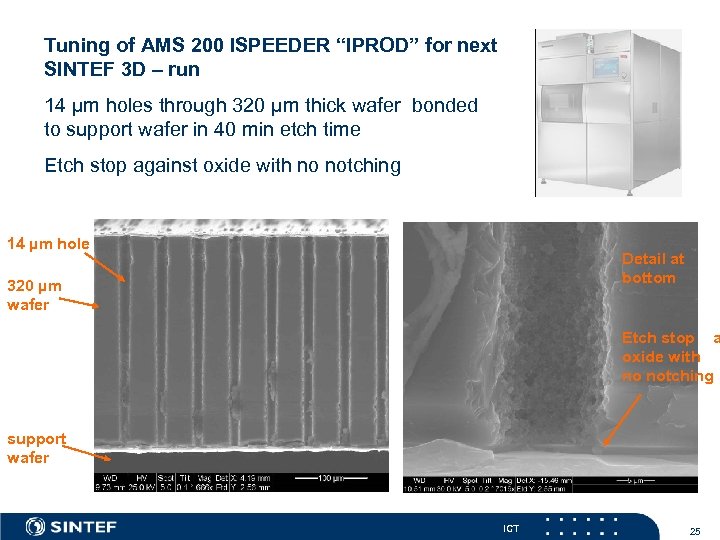

Tuning of AMS 200 ISPEEDER “IPROD” for next SINTEF 3 D – run 14 µm holes through 320 µm thick wafer bonded to support wafer in 40 min etch time Etch stop against oxide with no notching 14 µm hole Detail at bottom 320 µm wafer Etch stop a oxide with no notching support wafer ICT 25

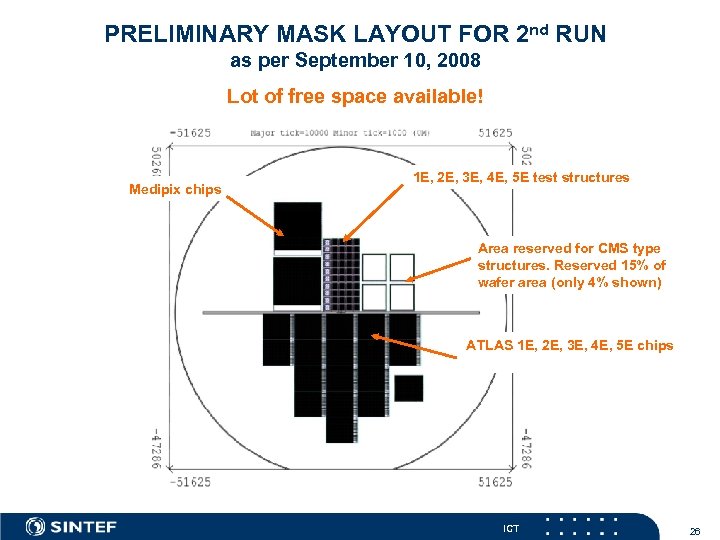

PRELIMINARY MASK LAYOUT FOR 2 nd RUN as per September 10, 2008 Lot of free space available! Medipix chips 1 E, 2 E, 3 E, 4 E, 5 E test structures Area reserved for CMS type structures. Reserved 15% of wafer area (only 4% shown) ATLAS 1 E, 2 E, 3 E, 4 E, 5 E chips ICT 26

Thank you for your attention! ICT 27

14cf8295c18564c2e3709357130d3e7c.ppt