b73c69fcfda079db65ec02f22ebdff57.ppt

- Количество слайдов: 38

Fast position resolution silicon detectors Gregor Kramberger , DESY OUTLINE • General properties of position sensitive detectors • Column Parallel CCD (CPCDD) • Monolithic Active Pixel Detectors (CMOS imager) • Depleted Field Effect Transistor Detectors (DEPFET) • Hybrid Active Pixel Detectors (HAPS)

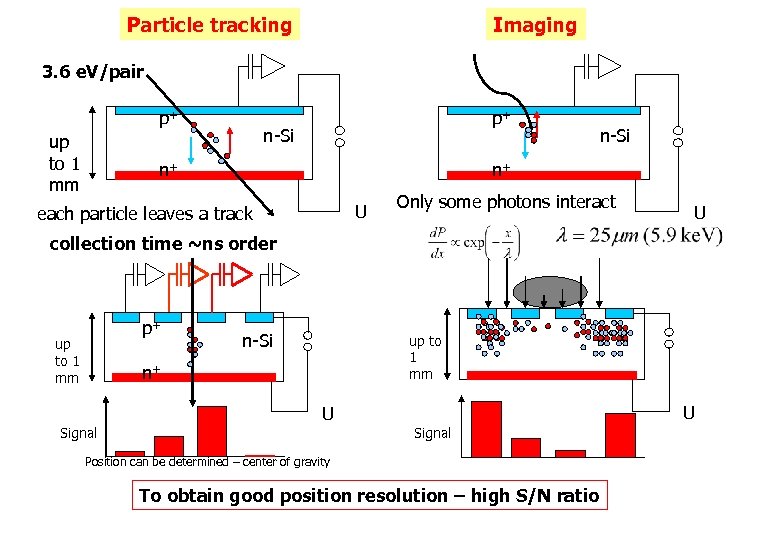

Particle tracking Imaging 3. 6 e. V/pair p+ up to 1 mm p+ n-Si n+ U each particle leaves a track Only some photons interact U collection time ~ns order p+ up to 1 mm n-Si up to 1 mm n+ U U Signal Position can be determined – center of gravity To obtain good position resolution – high S/N ratio

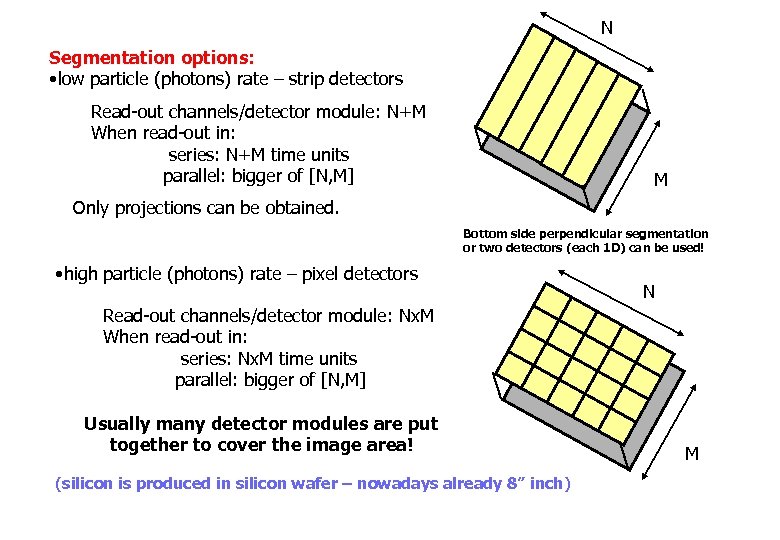

N Segmentation options: • low particle (photons) rate – strip detectors Read-out channels/detector module: N+M When read-out in: series: N+M time units parallel: bigger of [N, M] M Only projections can be obtained. Bottom side perpendicular segmentation or two detectors (each 1 D) can be used! • high particle (photons) rate – pixel detectors N Read-out channels/detector module: Nx. M When read-out in: series: Nx. M time units parallel: bigger of [N, M] Usually many detector modules are put together to cover the image area! (silicon is produced in silicon wafer – nowadays already 8” inch) M

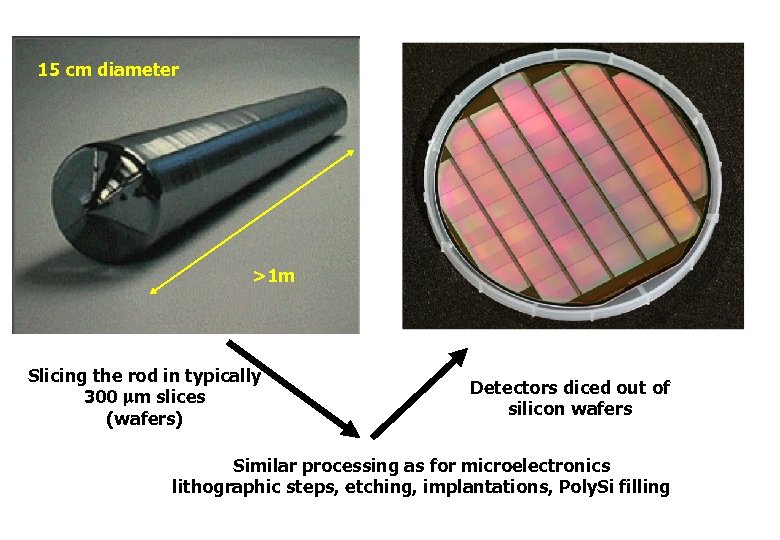

15 cm diameter >1 m Slicing the rod in typically 300 mm slices (wafers) Detectors diced out of silicon wafers Similar processing as for microelectronics lithographic steps, etching, implantations, Poly. Si filling

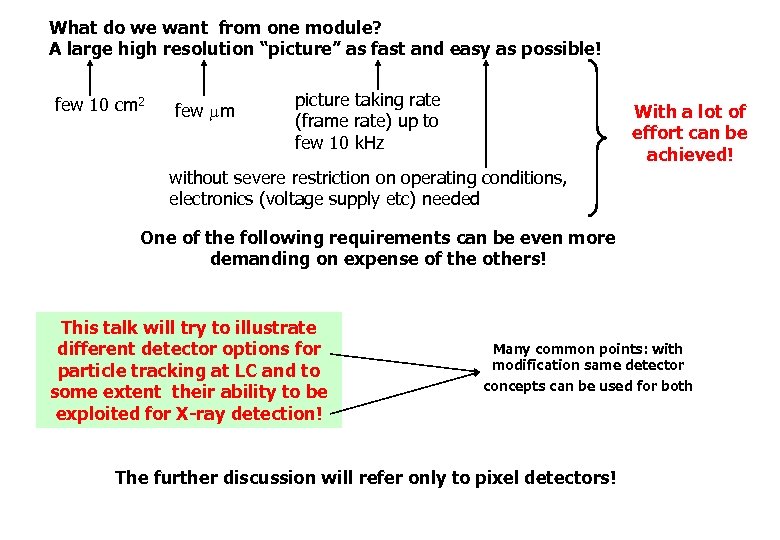

What do we want from one module? A large high resolution “picture” as fast and easy as possible! few 10 cm 2 few m picture taking rate (frame rate) up to few 10 k. Hz With a lot of effort can be achieved! without severe restriction on operating conditions, electronics (voltage supply etc) needed One of the following requirements can be even more demanding on expense of the others! This talk will try to illustrate different detector options for particle tracking at LC and to some extent their ability to be exploited for X-ray detection! Many common points: with modification same detector concepts can be used for both The further discussion will refer only to pixel detectors!

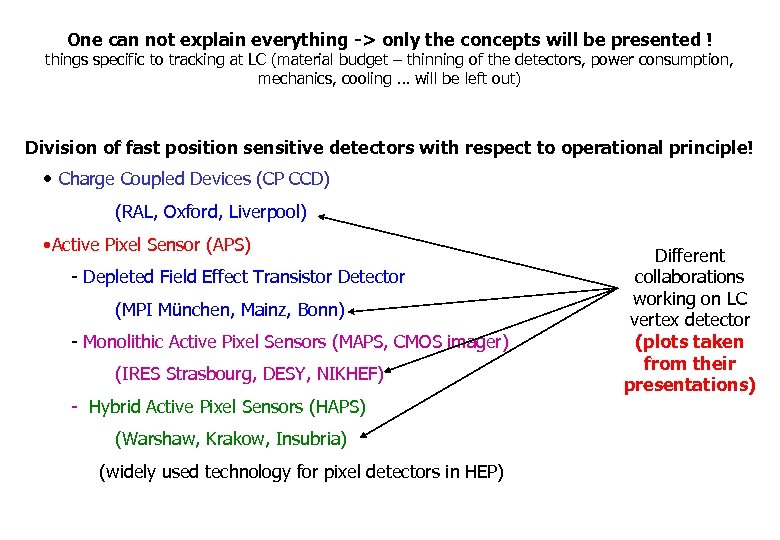

One can not explain everything -> only the concepts will be presented ! things specific to tracking at LC (material budget – thinning of the detectors, power consumption, mechanics, cooling … will be left out) Division of fast position sensitive detectors with respect to operational principle! • Charge Coupled Devices (CP CCD) (RAL, Oxford, Liverpool) • Active Pixel Sensor (APS) - Depleted Field Effect Transistor Detector (MPI München, Mainz, Bonn) - Monolithic Active Pixel Sensors (MAPS, CMOS imager) (IRES Strasbourg, DESY, NIKHEF) - Hybrid Active Pixel Sensors (HAPS) (Warshaw, Krakow, Insubria) (widely used technology for pixel detectors in HEP) Different collaborations working on LC vertex detector (plots taken from their presentations)

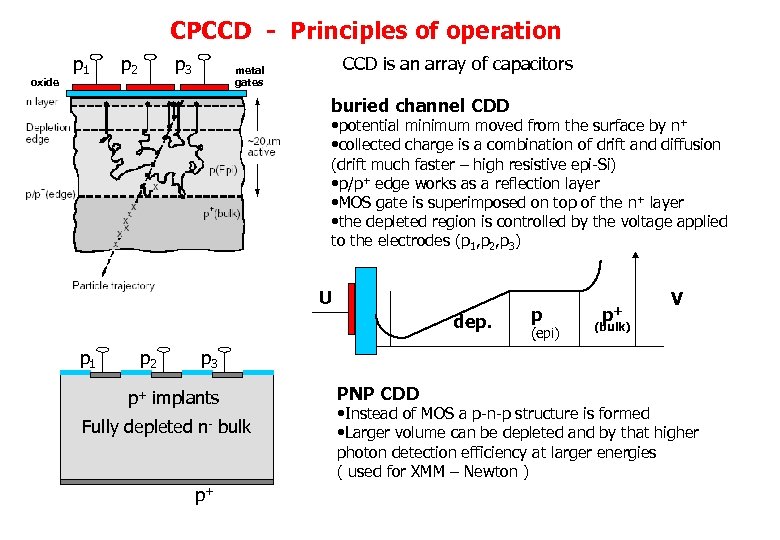

CPCCD - Principles of operation oxide p 1 p 2 p 3 CCD is an array of capacitors metal gates buried channel CDD • potential minimum moved from the surface by n+ • collected charge is a combination of drift and diffusion (drift much faster – high resistive epi-Si) • p/p+ edge works as a reflection layer • MOS gate is superimposed on top of the n+ layer • the depleted region is controlled by the voltage applied to the electrodes (p 1, p 2, p 3) U dep. p 1 p 2 p (epi) p+ (bulk) V p 3 p+ implants Fully depleted n- bulk p+ PNP CDD • Instead of MOS a p-n-p structure is formed • Larger volume can be depleted and by that higher photon detection efficiency at larger energies ( used for XMM – Newton )

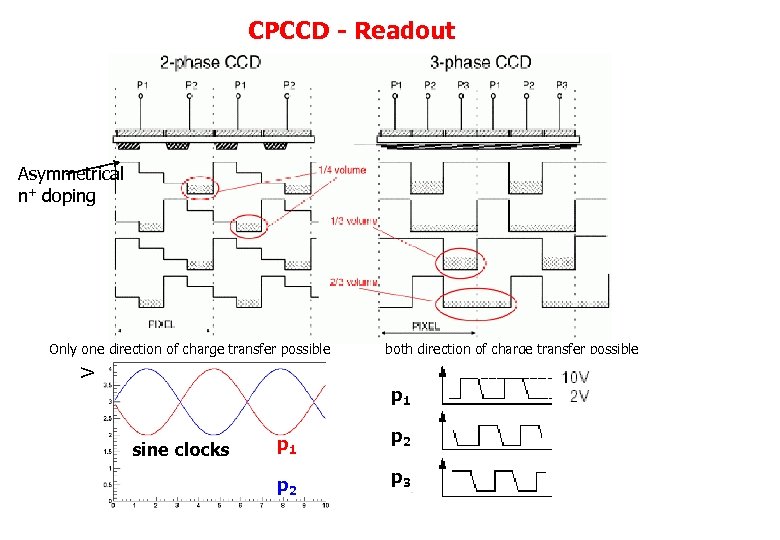

CPCCD - Readout Asymmetrical n+ doping both direction of charge transfer possible V Only one direction of charge transfer possible p 1 sine clocks p 1 p 2 p 3

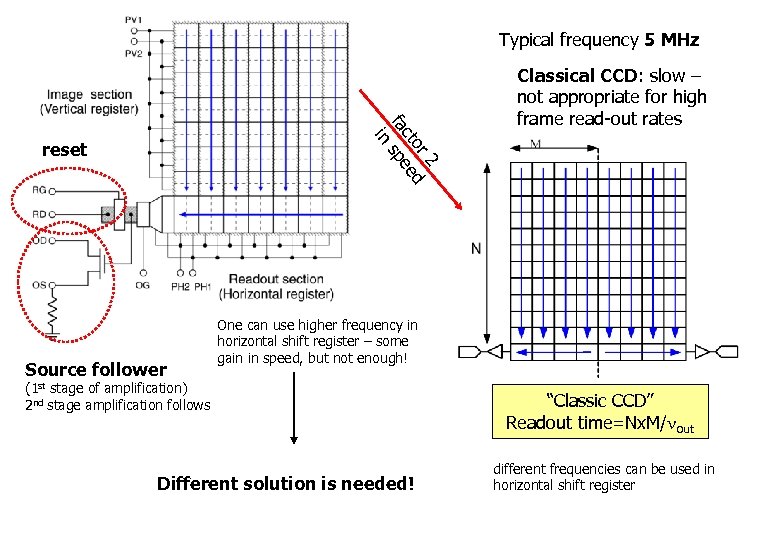

Typical frequency 5 MHz 2 or ed ct fa spe in reset Source follower Classical CCD: slow – not appropriate for high frame read-out rates One can use higher frequency in horizontal shift register – some gain in speed, but not enough! (1 st stage of amplification) 2 nd stage amplification follows Different solution is needed! “Classic CCD” Readout time=Nx. M/nout different frequencies can be used in horizontal shift register

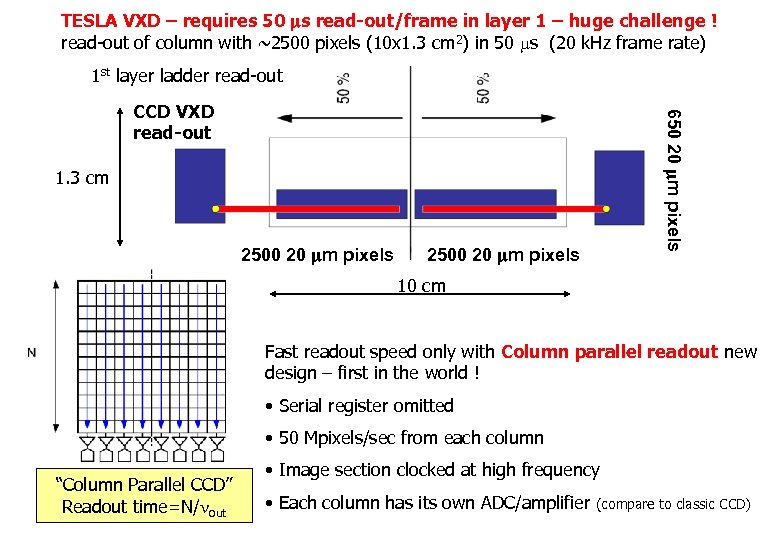

TESLA VXD – requires 50 ms read-out/frame in layer 1 – huge challenge ! read-out of column with ~2500 pixels (10 x 1. 3 cm 2) in 50 s (20 k. Hz frame rate) 1 st layer ladder read-out 1. 3 cm S=13 cm 2 2500 20 mm pixels 650 20 mm pixels CCD VXD read-out 10 cm Fast readout speed only with Column parallel readout new design – first in the world ! • Serial register omitted • 50 Mpixels/sec from each column “Column Parallel CCD” Readout time=N/nout • Image section clocked at high frequency • Each column has its own ADC/amplifier (compare to classic CCD)

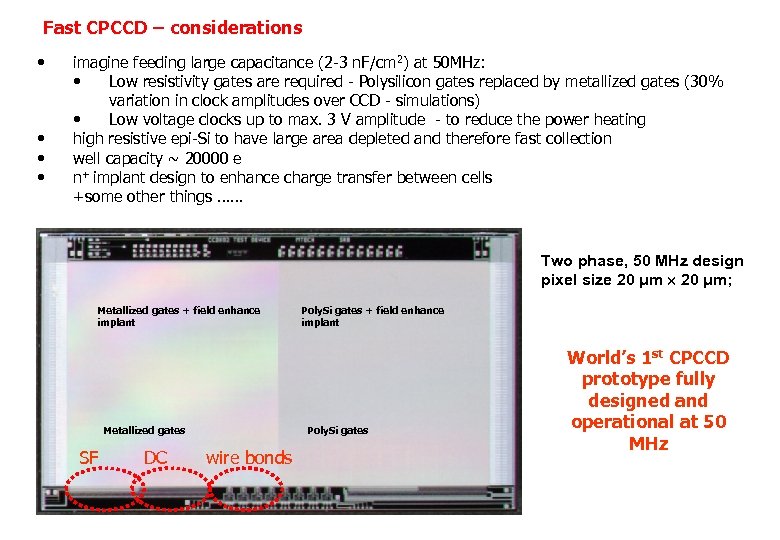

Fast CPCCD – considerations • • imagine feeding large capacitance (2 -3 n. F/cm 2) at 50 MHz: • Low resistivity gates are required - Polysilicon gates replaced by metallized gates (30% variation in clock amplitudes over CCD - simulations) • Low voltage clocks up to max. 3 V amplitude - to reduce the power heating high resistive epi-Si to have large area depleted and therefore fast collection well capacity ~ 20000 e n+ implant design to enhance charge transfer between cells +some other things …… Two phase, 50 MHz design pixel size 20 μm; Metallized gates + field enhance implant Metallized gates SF DC wire bonds Poly. Si gates + field enhance implant Poly. Si gates World’s 1 st CPCCD prototype fully designed and operational at 50 MHz

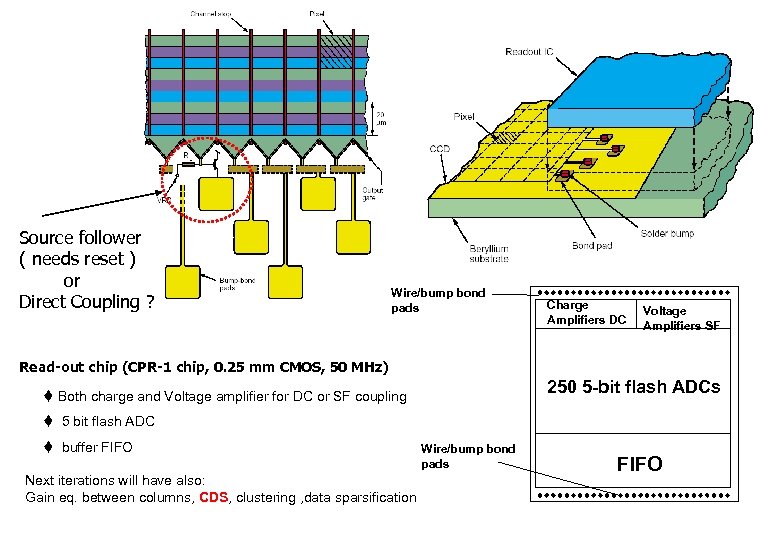

Source follower ( needs reset ) or Direct Coupling ? Wire/bump bond pads Charge Amplifiers DC Voltage Amplifiers SF Read-out chip (CPR-1 chip, 0. 25 mm CMOS, 50 MHz) 250 5 -bit flash ADCs t Both charge and Voltage amplifier for DC or SF coupling t 5 bit flash ADC t buffer FIFO Next iterations will have also: Gain eq. between columns, CDS, clustering , data sparsification Wire/bump bond pads FIFO

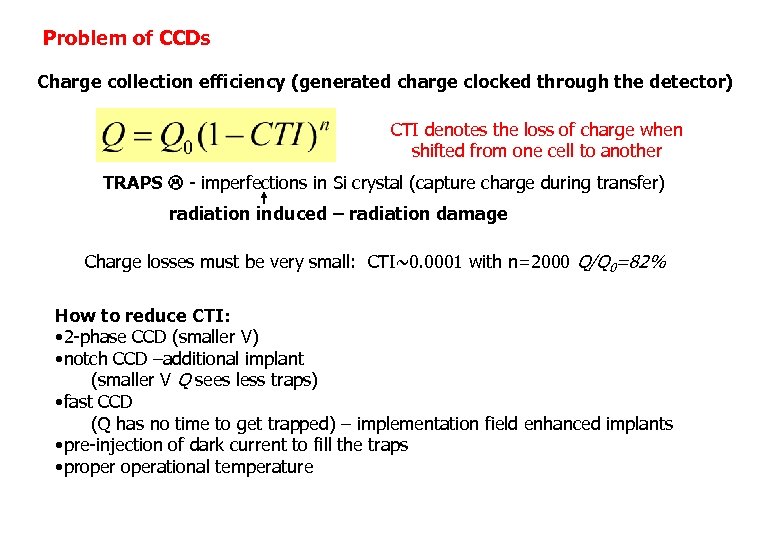

Problem of CCDs Charge collection efficiency (generated charge clocked through the detector) CTI denotes the loss of charge when shifted from one cell to another TRAPS - imperfections in Si crystal (capture charge during transfer) radiation induced – radiation damage Charge losses must be very small: CTI~0. 0001 with n=2000 Q/Q 0=82% How to reduce CTI: • 2 -phase CCD (smaller V) • notch CCD –additional implant (smaller V Q sees less traps) • fast CCD (Q has no time to get trapped) – implementation field enhanced implants • pre-injection of dark current to fill the traps • properational temperature

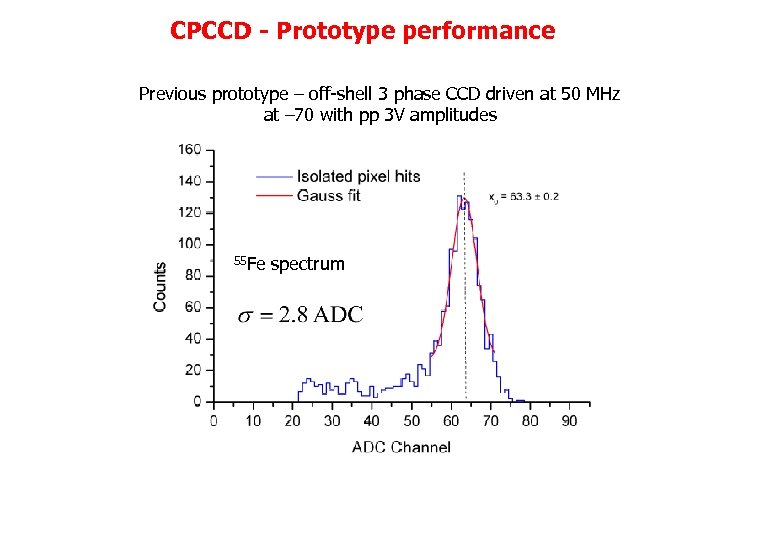

CPCCD - Prototype performance Previous prototype – off-shell 3 phase CCD driven at 50 MHz at – 70 with pp 3 V amplitudes 55 Fe spectrum

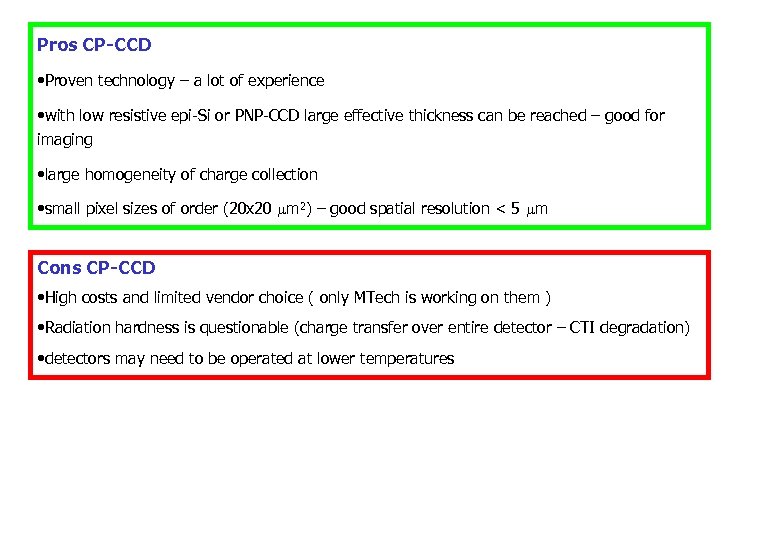

Pros CP-CCD • Proven technology – a lot of experience • with low resistive epi-Si or PNP-CCD large effective thickness can be reached – good for imaging • large homogeneity of charge collection • small pixel sizes of order (20 x 20 m 2) – good spatial resolution < 5 m Cons CP-CCD • High costs and limited vendor choice ( only MTech is working on them ) • Radiation hardness is questionable (charge transfer over entire detector – CTI degradation) • detectors may need to be operated at lower temperatures

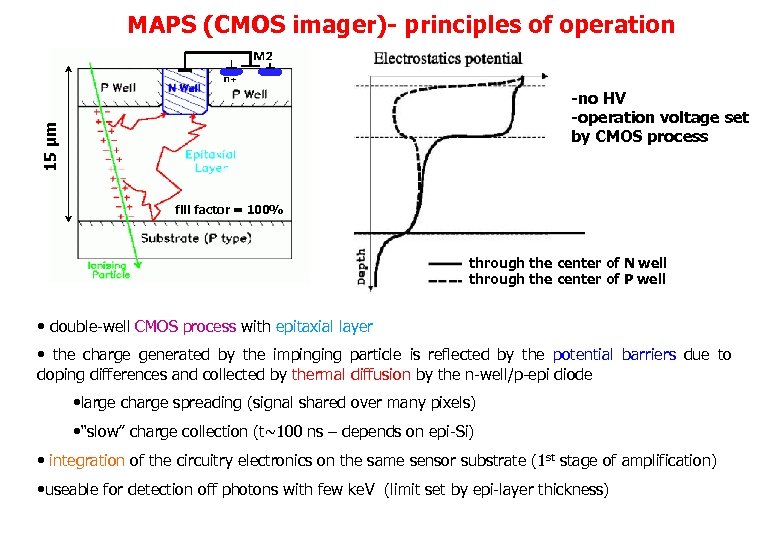

MAPS (CMOS imager)- principles of operation 15 µm -no HV -operation voltage set by CMOS process fill factor = 100% through the center of N well through the center of P well • double-well CMOS process with epitaxial layer • the charge generated by the impinging particle is reflected by the potential barriers due to doping differences and collected by thermal diffusion by the n-well/p-epi diode • large charge spreading (signal shared over many pixels) • “slow” charge collection (t~100 ns – depends on epi-Si) • integration of the circuitry electronics on the same sensor substrate (1 st stage of amplification) • useable for detection off photons with few ke. V (limit set by epi-layer thickness)

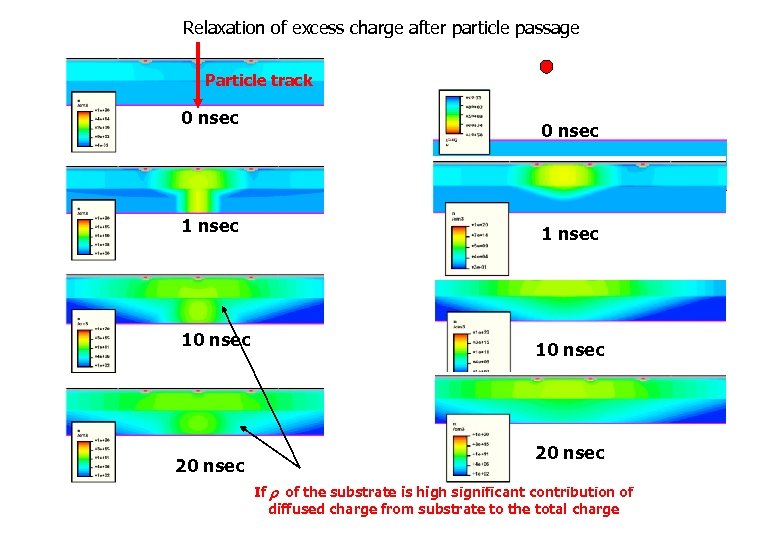

Relaxation of excess charge after particle passage Particle track 0 nsec 10 nsec 20 nsec If r of the substrate is high significant contribution of diffused charge from substrate to the total charge

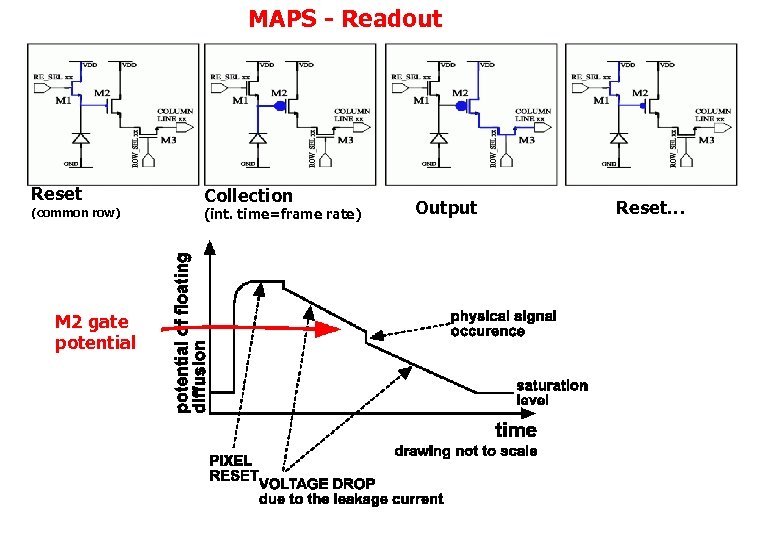

MAPS - Readout Reset (common row) M 2 gate potential Collection (int. time=frame rate) Output Reset…

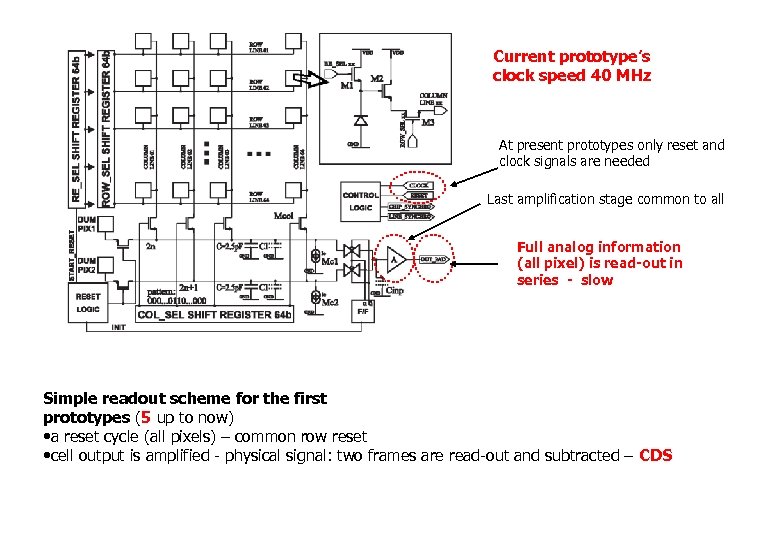

Current prototype’s clock speed 40 MHz At present prototypes only reset and clock signals are needed Last amplification stage common to all Full analog information (all pixel) is read-out in series - slow Simple readout scheme for the first prototypes (5 up to now) • a reset cycle (all pixels) – common row reset • cell output is amplified - physical signal: two frames are read-out and subtracted – CDS

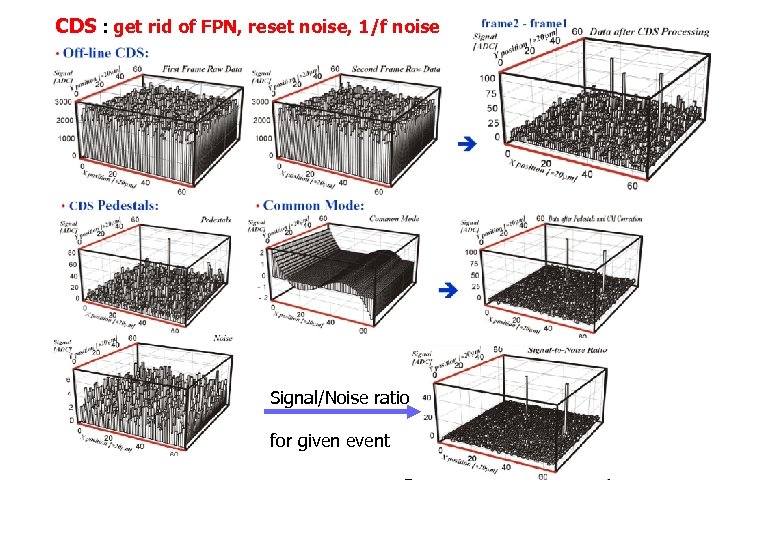

CDS : get rid of FPN, reset noise, 1/f noise Signal/Noise ratio for given event

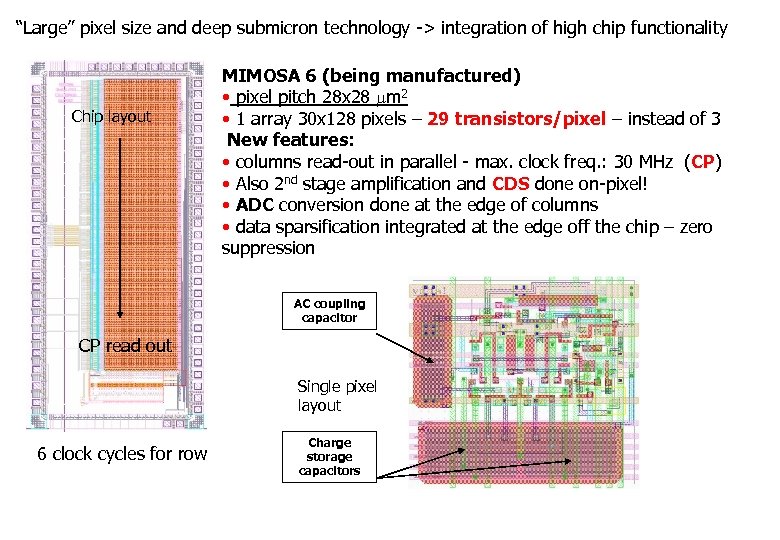

“Large” pixel size and deep submicron technology -> integration of high chip functionality Chip layout MIMOSA 6 (being manufactured) • pixel pitch 28 x 28 m 2 • 1 array 30 x 128 pixels – 29 transistors/pixel – instead of 3 New features: • columns read-out in parallel - max. clock freq. : 30 MHz (CP) • Also 2 nd stage amplification and CDS done on-pixel! • ADC conversion done at the edge of columns • data sparsification integrated at the edge off the chip – zero suppression AC coupling capacitor CP read out Single pixel layout 6 clock cycles for row Charge storage capacitors

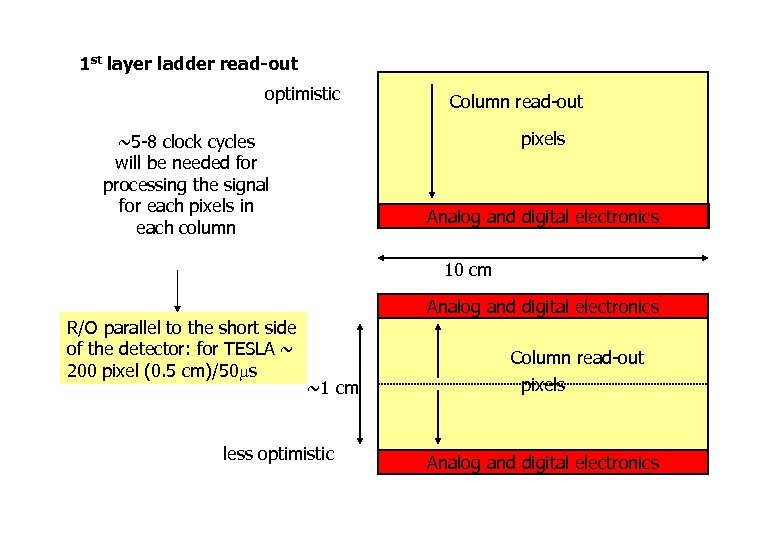

1 st layer ladder read-out optimistic Column read-out pixels ~5 -8 clock cycles will be needed for processing the signal for each pixels in each column Analog and digital electronics 10 cm R/O parallel to the short side of the detector: for TESLA ~ 200 pixel (0. 5 cm)/50 s Analog and digital electronics Column read-out ~1 cm less optimistic pixels Analog and digital electronics

MAPS – prototype performance 5 prototypes build so far in different technologies (deep sub ), different pixel sizes, clock frequencies and epilayer thicknesses MIMOSA 5 – large size detector - standard 0. 6 m CMOS of AMS with 14 m thick EPI layer (1014 cm-3), pixel 17 x 17 m 2, well capacity > 10000 e chip size 1. 73 x 1. 73 cm 2 Wafer view ~10% of the total surface max. CMOS die size 2 x 2 cm 2 Pixel read-out direction • First stitched ladders of few neighboring chips are produced (100 m between chips – can be reduced to 1 m – almost no dead area) • simple serial frame read-out – 150 Hz frame rate (full analog information read-out) • problem with fabrication yield!

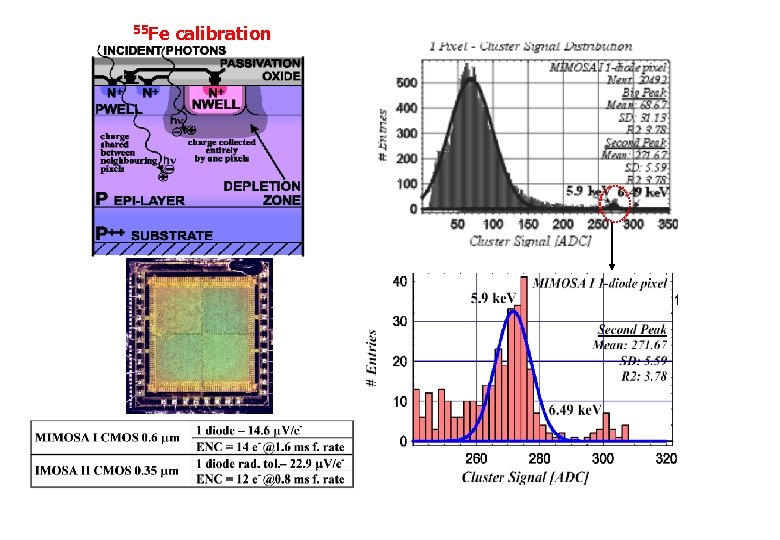

55 Fe calibration

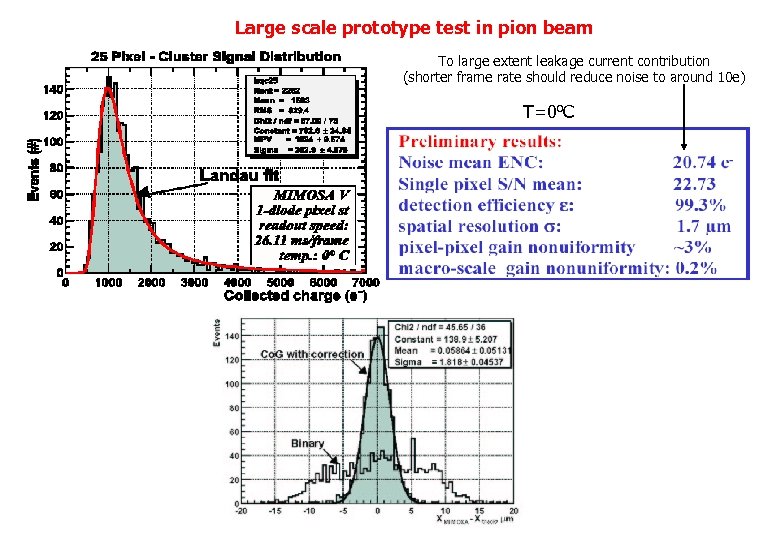

Large scale prototype test in pion beam To large extent leakage current contribution (shorter frame rate should reduce noise to around 10 e) T=0 o. C

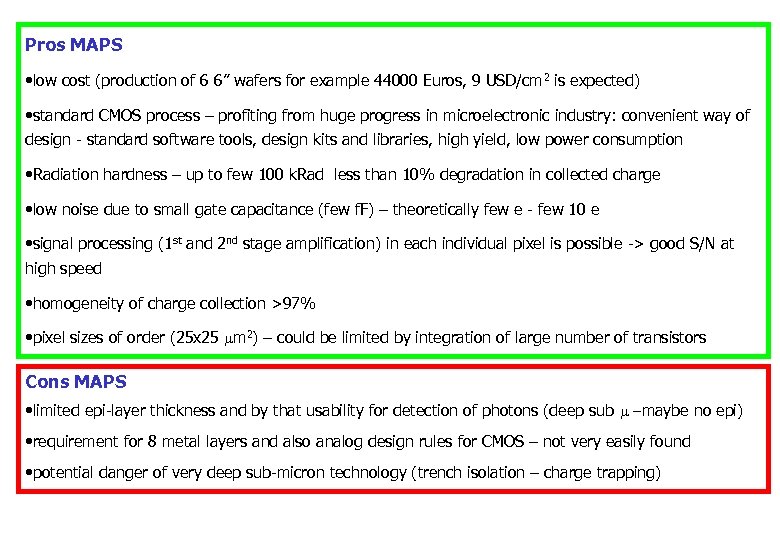

Pros MAPS • low cost (production of 6 6” wafers for example 44000 Euros, 9 USD/cm 2 is expected) • standard CMOS process – profiting from huge progress in microelectronic industry: convenient way of design - standard software tools, design kits and libraries, high yield, low power consumption • Radiation hardness – up to few 100 k. Rad less than 10% degradation in collected charge • low noise due to small gate capacitance (few f. F) – theoretically few e - few 10 e • signal processing (1 st and 2 nd stage amplification) in each individual pixel is possible -> good S/N at high speed • homogeneity of charge collection >97% • pixel sizes of order (25 x 25 m 2) – could be limited by integration of large number of transistors Cons MAPS • limited epi-layer thickness and by that usability for detection of photons (deep sub -maybe no epi) • requirement for 8 metal layers and also analog design rules for CMOS – not very easily found • potential danger of very deep sub-micron technology (trench isolation – charge trapping)

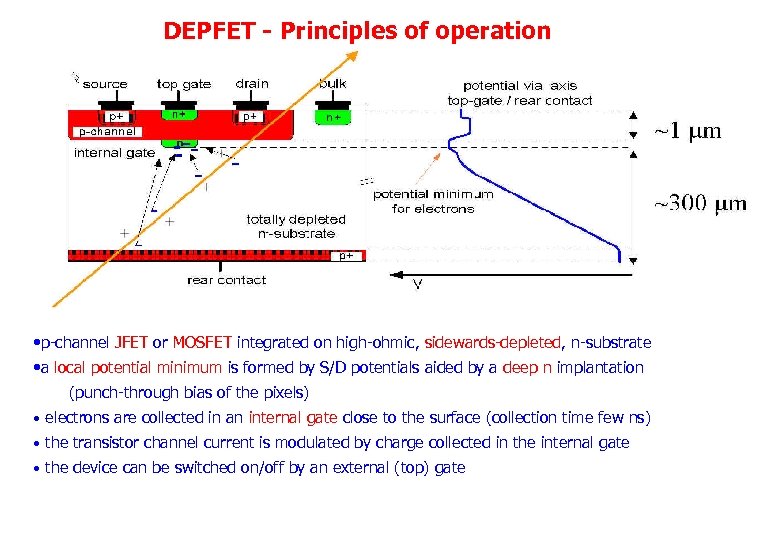

DEPFET - Principles of operation • p-channel JFET or MOSFET integrated on high-ohmic, sidewards-depleted, n-substrate • a local potential minimum is formed by S/D potentials aided by a deep n implantation (punch-through bias of the pixels) • electrons are collected in an internal gate close to the surface (collection time few ns) • the transistor channel current is modulated by charge collected in the internal gate • the device can be switched on/off by an external (top) gate

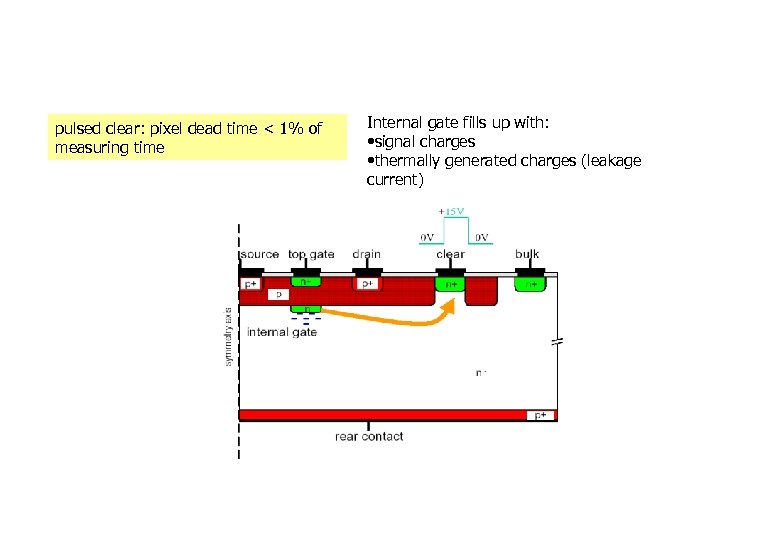

pulsed clear: pixel dead time < 1% of measuring time Internal gate fills up with: • signal charges • thermally generated charges (leakage current)

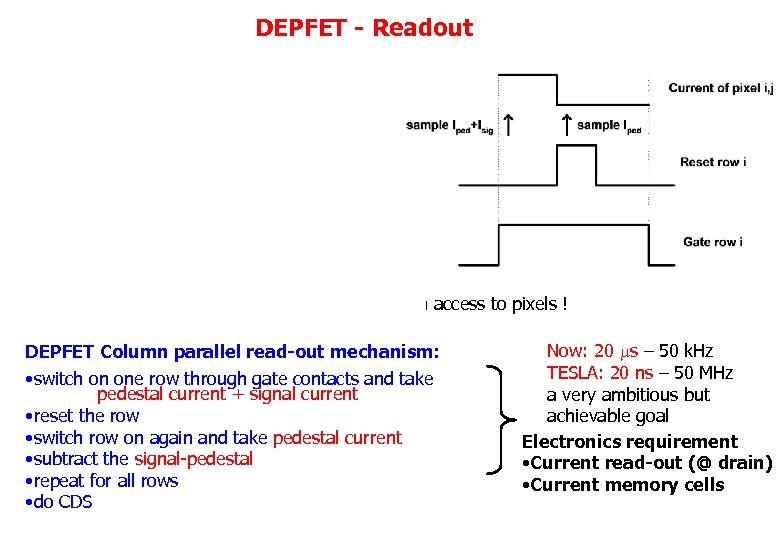

DEPFET - Readout random access to pixels ! DEPFET Column parallel read-out mechanism: • switch on one row through gate contacts and take pedestal current + signal current • reset the row • switch row on again and take pedestal current • subtract the signal-pedestal • repeat for all rows • do CDS Now: 20 s – 50 k. Hz TESLA: 20 ns – 50 MHz a very ambitious but achievable goal Electronics requirement • Current read-out (@ drain) • Current memory cells

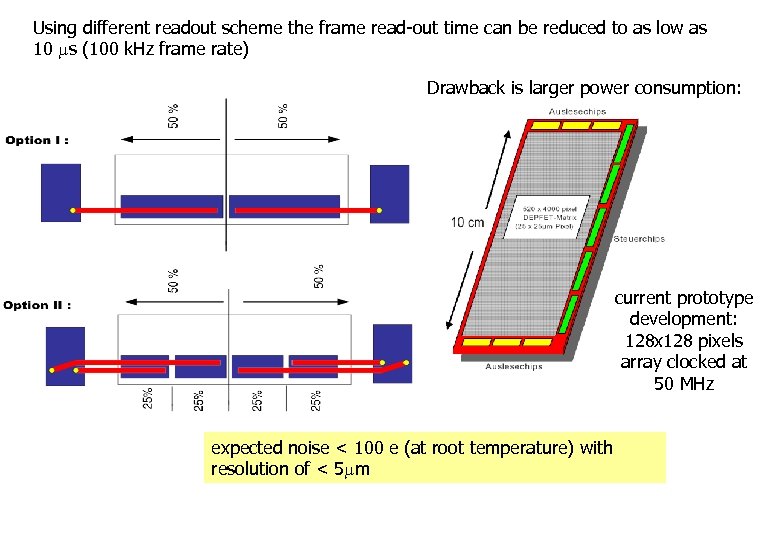

Using different readout scheme the frame read-out time can be reduced to as low as 10 s (100 k. Hz frame rate) Drawback is larger power consumption: current prototype development: 128 x 128 pixels array clocked at 50 MHz expected noise < 100 e (at root temperature) with resolution of < 5 m

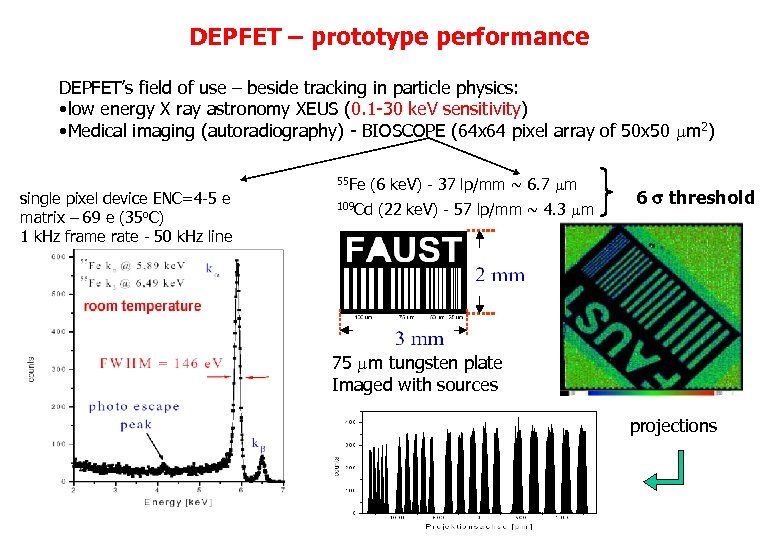

DEPFET – prototype performance DEPFET’s field of use – beside tracking in particle physics: • low energy X ray astronomy XEUS (0. 1 -30 ke. V sensitivity) • Medical imaging (autoradiography) - BIOSCOPE (64 x 64 pixel array of 50 x 50 m 2) single pixel device ENC=4 -5 e matrix – 69 e (35 o. C) 1 k. Hz frame rate - 50 k. Hz line 55 Fe (6 ke. V) - 37 lp/mm ~ 6. 7 m 109 Cd (22 ke. V) - 57 lp/mm ~ 4. 3 m 6 s threshold 75 m tungsten plate Imaged with sources projections

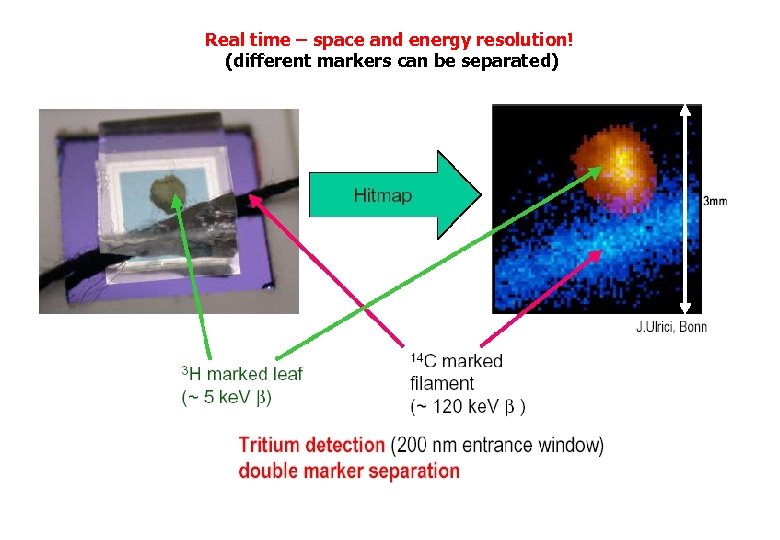

Real time – space and energy resolution! (different markers can be separated)

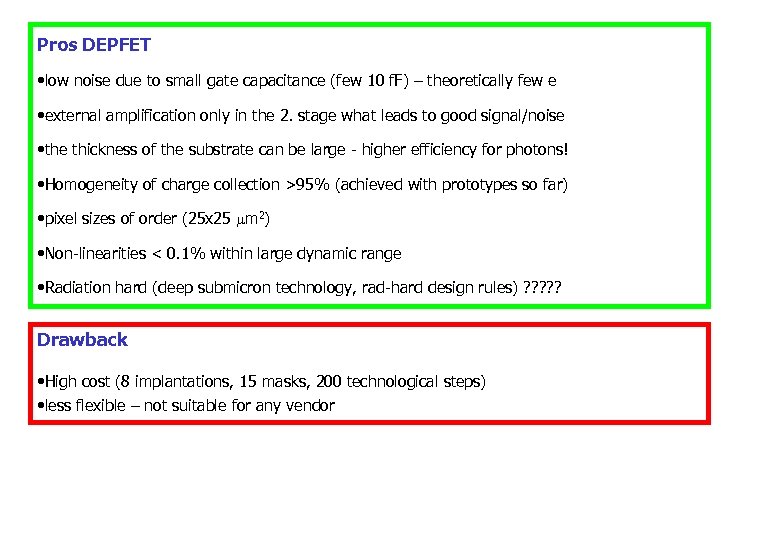

Pros DEPFET • low noise due to small gate capacitance (few 10 f. F) – theoretically few e • external amplification only in the 2. stage what leads to good signal/noise • the thickness of the substrate can be large - higher efficiency for photons! • Homogeneity of charge collection >95% (achieved with prototypes so far) • pixel sizes of order (25 x 25 m 2) • Non-linearities < 0. 1% within large dynamic range • Radiation hard (deep submicron technology, rad-hard design rules) ? ? ? Drawback • High cost (8 implantations, 15 masks, 200 technological steps) • less flexible – not suitable for any vendor

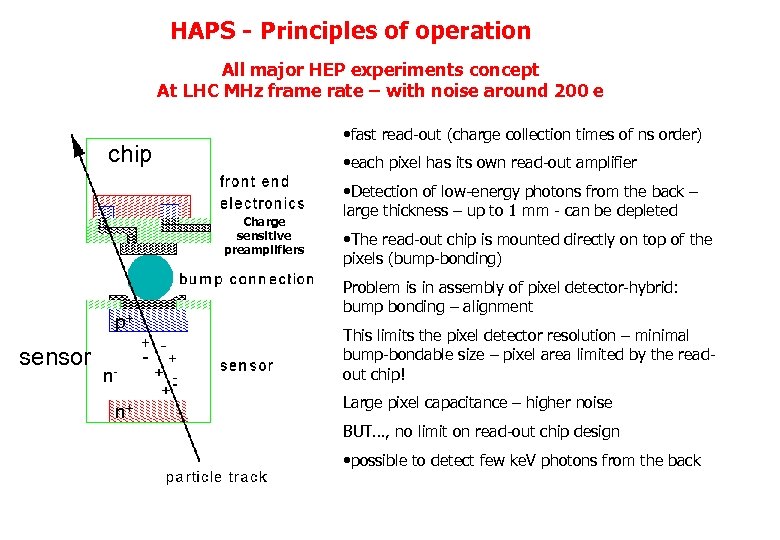

HAPS - Principles of operation All major HEP experiments concept At LHC MHz frame rate – with noise around 200 e • fast read-out (charge collection times of ns order) chip • each pixel has its own read-out amplifier Charge sensitive preamplifiers p+ sensor nn+ • Detection of low-energy photons from the back – large thickness – up to 1 mm - can be depleted • The read-out chip is mounted directly on top of the pixels (bump-bonding) Problem is in assembly of pixel detector-hybrid: bump bonding – alignment This limits the pixel detector resolution – minimal bump-bondable size – pixel area limited by the readout chip! Large pixel capacitance – higher noise BUT…, no limit on read-out chip design • possible to detect few ke. V photons from the back

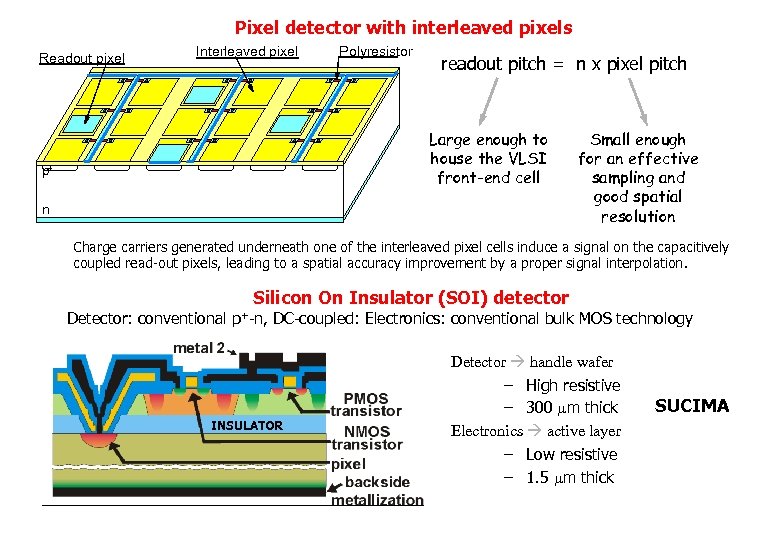

Pixel detector with interleaved pixels Readout pixel Interleaved pixel Polyresistor readout pitch = n x pixel pitch Large enough to house the VLSI front-end cell p+ n Small enough for an effective sampling and good spatial resolution Charge carriers generated underneath one of the interleaved pixel cells induce a signal on the capacitively coupled read-out pixels, leading to a spatial accuracy improvement by a proper signal interpolation. Silicon On Insulator (SOI) detector Detector: conventional p+-n, DC-coupled: Electronics: conventional bulk MOS technology INSULATOR Detector handle wafer – High resistive – 300 m thick Electronics active layer – Low resistive – 1. 5 m thick SUCIMA

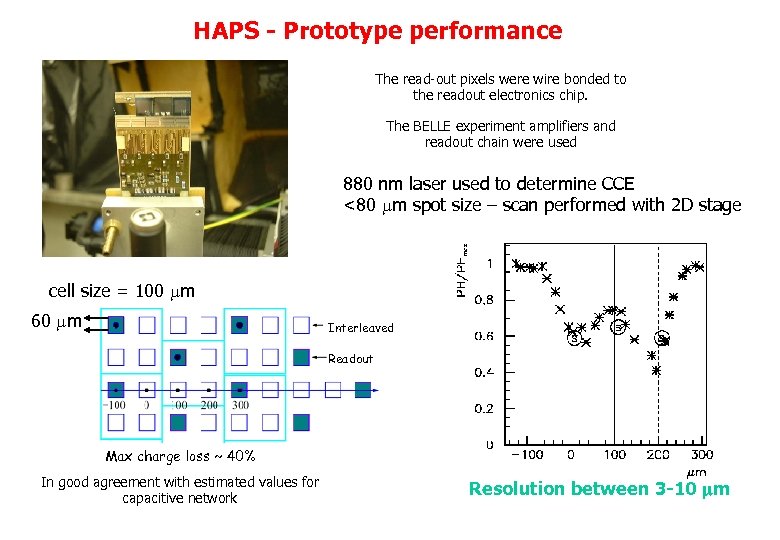

HAPS - Prototype performance The read-out pixels were wire bonded to the readout electronics chip. The BELLE experiment amplifiers and readout chain were used 880 nm laser used to determine CCE <80 m spot size – scan performed with 2 D stage cell size = 100 m 60 m Interleaved Readout Max charge loss ~ 40% In good agreement with estimated values for capacitive network Resolution between 3 -10 mm

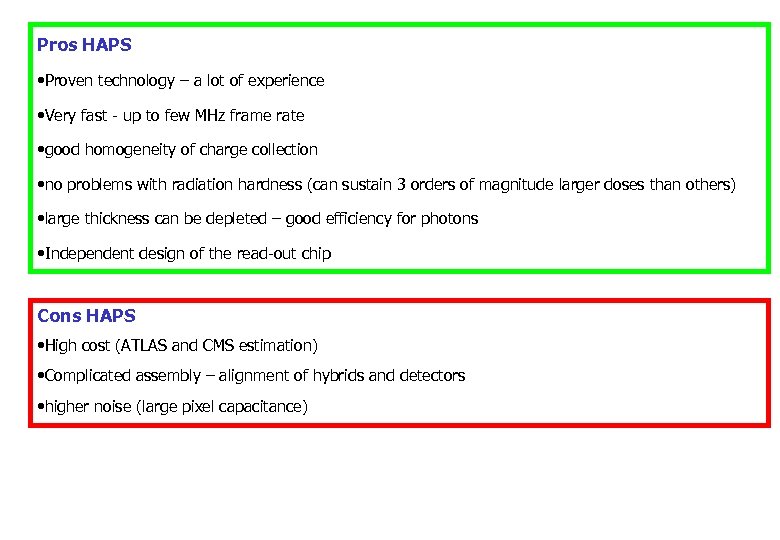

Pros HAPS • Proven technology – a lot of experience • Very fast - up to few MHz frame rate • good homogeneity of charge collection • no problems with radiation hardness (can sustain 3 orders of magnitude larger doses than others) • large thickness can be depleted – good efficiency for photons • Independent design of the read-out chip Cons HAPS • High cost (ATLAS and CMS estimation) • Complicated assembly – alignment of hybrids and detectors • higher noise (large pixel capacitance)

SUMMARY There is a bright future for silicon in the field of particle detectors! With new ideas coming and microelectronics industry growing … sky is the limit

b73c69fcfda079db65ec02f22ebdff57.ppt