Лекция2 Вычислительные системы.ppt

- Количество слайдов: 58

Эволюция технологий изготовления процессора l Электромеханическое реле l Вакуумные лампы l Транзисторы Микропроцессор Intel 4004 • 1971 год • первый в мире коммерчески доступный однокристальный микропроцессор • стоимость 200 долларов • на одном кристалле все функции процессора большой ЭВМ • 60 000 (в среднем, максимально до 93 000) инструкций в секунду • Количество транзисторов: 2250

Эволюция технологий изготовления процессора l Электромеханическое реле l Вакуумные лампы l Транзисторы Микропроцессор Intel 4004 • 1971 год • первый в мире коммерчески доступный однокристальный микропроцессор • стоимость 200 долларов • на одном кристалле все функции процессора большой ЭВМ • 60 000 (в среднем, максимально до 93 000) инструкций в секунду • Количество транзисторов: 2250

В настоящее время l Intel Core i 3 2100 l l 2011 год 995 000 транзисторов ~145 000 000 операций с плавающей точкой в секунду 2013 год: Ivy Bridge 1, 4 млрд. транзисторов на площади кристалла 160 мм².

В настоящее время l Intel Core i 3 2100 l l 2011 год 995 000 транзисторов ~145 000 000 операций с плавающей точкой в секунду 2013 год: Ivy Bridge 1, 4 млрд. транзисторов на площади кристалла 160 мм².

Закон Мура l Удвоение числа транзисторов каждые 2 года Журнал «В мире науки» (1983, № 08) Если бы авиапромышленность в последние 25 лет развивалась столь же стремительно, как промышленность средств вычислительной техники, то сейчас самолёт Boeing 767 стоил бы 500 долл. и совершал облёт земного шара за 20 минут, затрачивая при этом пять галлонов (~18, 9 л) топлива.

Закон Мура l Удвоение числа транзисторов каждые 2 года Журнал «В мире науки» (1983, № 08) Если бы авиапромышленность в последние 25 лет развивалась столь же стремительно, как промышленность средств вычислительной техники, то сейчас самолёт Boeing 767 стоил бы 500 долл. и совершал облёт земного шара за 20 минут, затрачивая при этом пять галлонов (~18, 9 л) топлива.

Схема работы транзистора +V l Vout Коллектор l Vin База Напряжение на базе ниже критического – транзистор действует как большое сопротивление; выходное напряжение высоко Напряжение на базе выше критического - транзистор открывается; выходное напряжение падает Эмиттер Таблица истинности Vin 0 1 1 Vout 1 0 Инвертор

Схема работы транзистора +V l Vout Коллектор l Vin База Напряжение на базе ниже критического – транзистор действует как большое сопротивление; выходное напряжение высоко Напряжение на базе выше критического - транзистор открывается; выходное напряжение падает Эмиттер Таблица истинности Vin 0 1 1 Vout 1 0 Инвертор

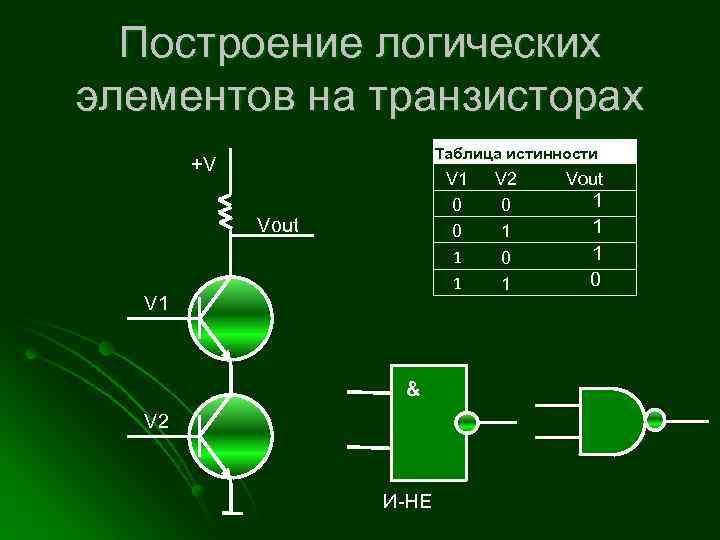

Построение логических элементов на транзисторах Таблица истинности +V V 1 0 0 1 1 Vout V 1 & V 2 И-НЕ V 2 0 1 Vout 1 1 1 0

Построение логических элементов на транзисторах Таблица истинности +V V 1 0 0 1 1 Vout V 1 & V 2 И-НЕ V 2 0 1 Vout 1 1 1 0

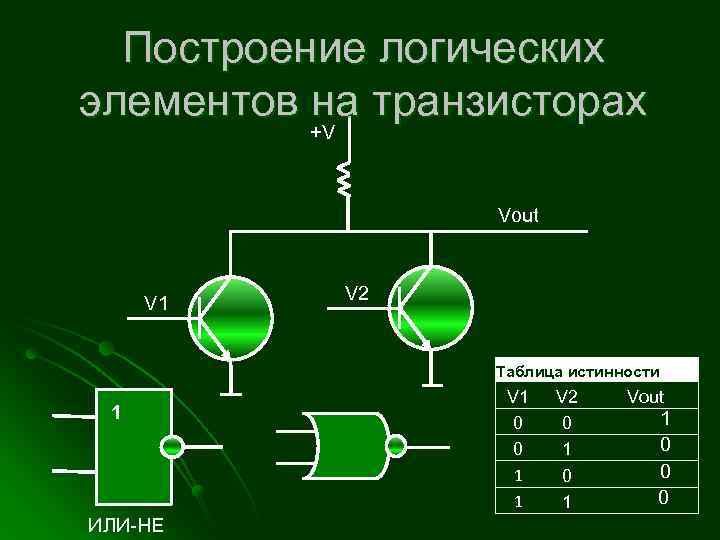

Построение логических элементов на транзисторах +V Vout V 1 V 2 Таблица истинности 1 ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0

Построение логических элементов на транзисторах +V Vout V 1 V 2 Таблица истинности 1 ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0

Логические функции Таблица истинности V 1 0 0 1 1 l V 2 F 1 F 2 F 3 F 4 F 5 F 6 F 7 F 8 F 9 F 10 F 11 F 12 F 13 F 14 F 15 F 16 0 0 1 0 1 1 0 0 1 1 0 0 0 1 1 1 0 0 0 0 1 1 1 1 Любую логическую функцию можно построить на базисных логических элементах

Логические функции Таблица истинности V 1 0 0 1 1 l V 2 F 1 F 2 F 3 F 4 F 5 F 6 F 7 F 8 F 9 F 10 F 11 F 12 F 13 F 14 F 15 F 16 0 0 1 0 1 1 0 0 1 1 0 0 0 1 1 1 0 0 0 0 1 1 1 1 Любую логическую функцию можно построить на базисных логических элементах

Таблица истинности сумматора Таблица истинности V 1 0 0 1 1 V 2 0 1 Сумма Перенос 0 1 1 0 0 1 Таблица истинности V 1 0 0 1 1 V 2 0 1 0 1 Перенос1 Сумма Перенос2 0 0 1 0 0 0 1 1 1 0 1 1

Таблица истинности сумматора Таблица истинности V 1 0 0 1 1 V 2 0 1 Сумма Перенос 0 1 1 0 0 1 Таблица истинности V 1 0 0 1 1 V 2 0 1 0 1 Перенос1 Сумма Перенос2 0 0 1 0 0 0 1 1 1 0 1 1

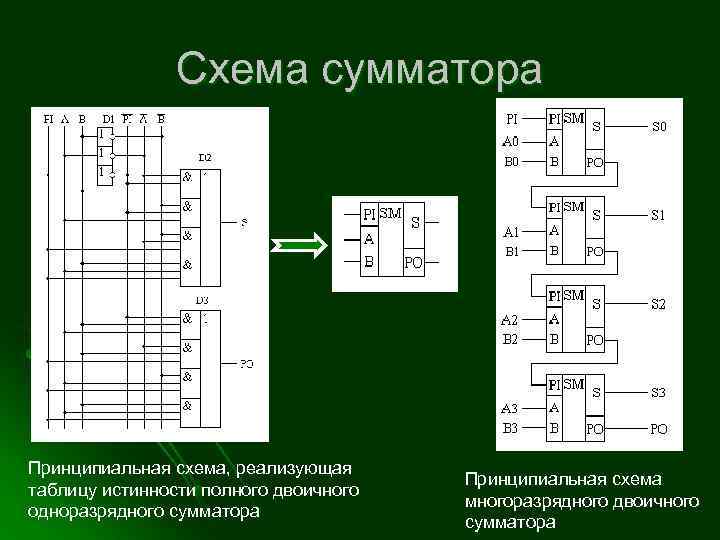

Схема сумматора Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора Принципиальная схема многоразрядного двоичного сумматора

Схема сумматора Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора Принципиальная схема многоразрядного двоичного сумматора

Схема материнс кой платы ПК

Схема материнс кой платы ПК

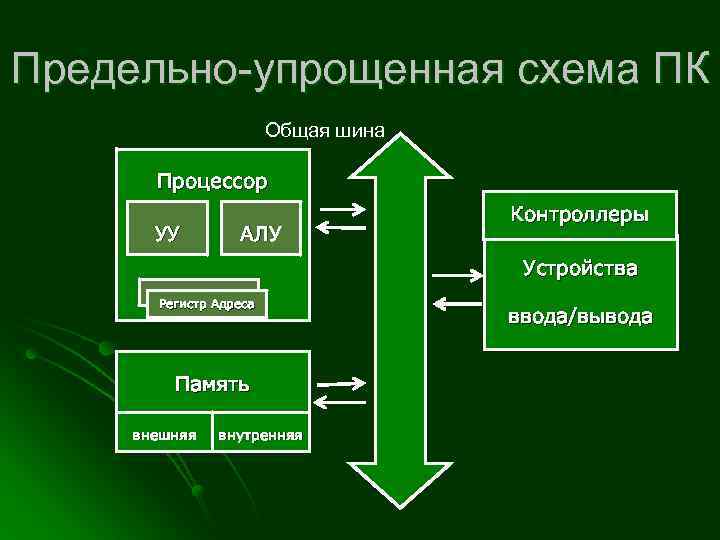

Предельно-упрощенная схема ПК Общая шина Процессор УУ АЛУ Контроллеры Устройства Регистр Адреса Память внешняя внутренняя ввода/вывода

Предельно-упрощенная схема ПК Общая шина Процессор УУ АЛУ Контроллеры Устройства Регистр Адреса Память внешняя внутренняя ввода/вывода

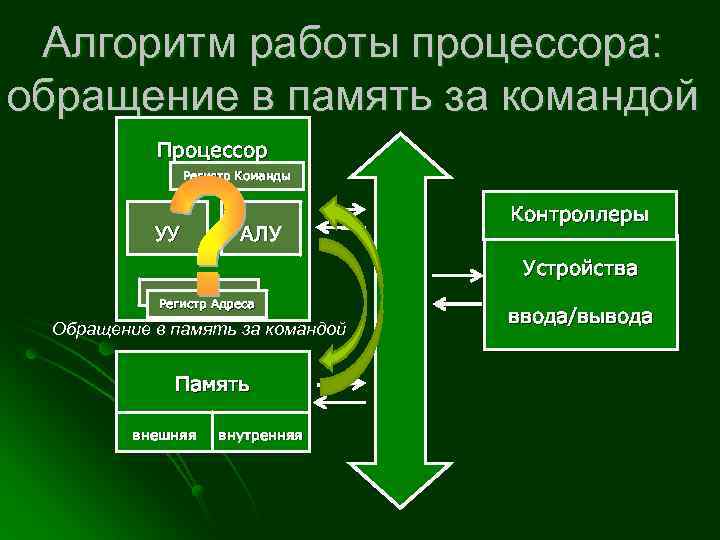

Алгоритм работы процессора: обращение в память за командой Процессор Регистр Команды УУ АЛУ Контроллеры Устройства Регистр Адреса Обращение в память за командой Память внешняя внутренняя ввода/вывода

Алгоритм работы процессора: обращение в память за командой Процессор Регистр Команды УУ АЛУ Контроллеры Устройства Регистр Адреса Обращение в память за командой Память внешняя внутренняя ввода/вывода

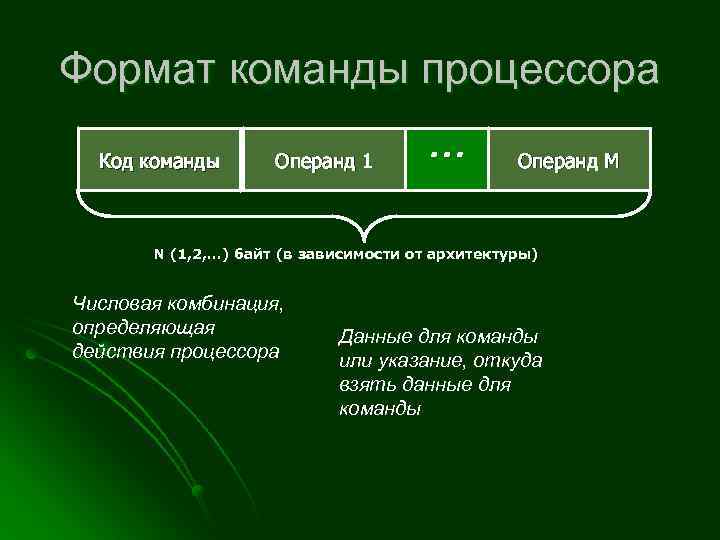

Формат команды процессора Код команды Операнд 1 … Операнд M N (1, 2, …) байт (в зависимости от архитектуры) Числовая комбинация, определяющая действия процессора Данные для команды или указание, откуда взять данные для команды

Формат команды процессора Код команды Операнд 1 … Операнд M N (1, 2, …) байт (в зависимости от архитектуры) Числовая комбинация, определяющая действия процессора Данные для команды или указание, откуда взять данные для команды

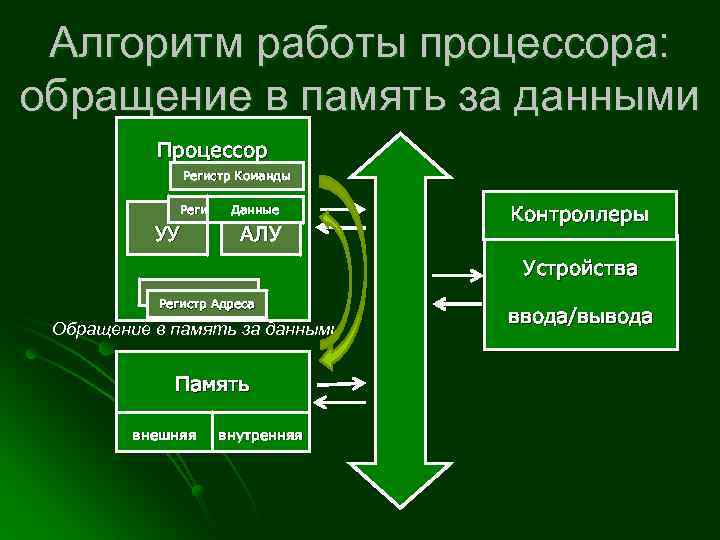

Алгоритм работы процессора: обращение в память за данными Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Контроллеры Устройства Регистр Адреса Обращение в память за данными Память внешняя внутренняя ввода/вывода

Алгоритм работы процессора: обращение в память за данными Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Контроллеры Устройства Регистр Адреса Обращение в память за данными Память внешняя внутренняя ввода/вывода

Алгоритм работы процессора: обработка данных в АЛУ Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Признаки операции Данные Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора: обработка данных в АЛУ Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Признаки операции Данные Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора: отправка данных в память Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора: отправка данных в память Процессор Регистр Команды Данные Регистры Данных УУ АЛУ Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора: определение адреса команды Процессор Регистр Команды Регистры Данных УУ В счетчике команд определяется адрес следующей команды АЛУ Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора: определение адреса команды Процессор Регистр Команды Регистры Данных УУ В счетчике команд определяется адрес следующей команды АЛУ Регистр Состояния Регистр Адреса Память внешняя внутренняя Контроллеры Устройства ввода/вывода

Алгоритм работы процессора l l l Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков Запись результата Увеличение (изменение) счетчика команд

Алгоритм работы процессора l l l Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков Запись результата Увеличение (изменение) счетчика команд

Упрощенная структурная схема процессора (следующий слайд)

Упрощенная структурная схема процессора (следующий слайд)

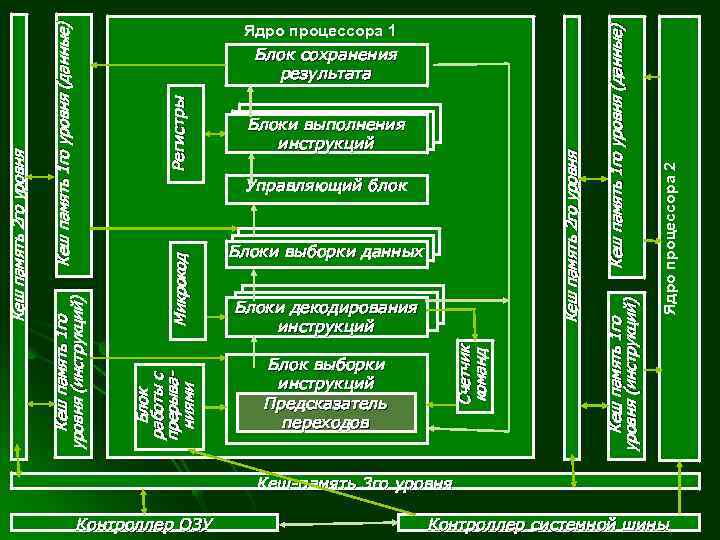

Блок работы с прерываниями Контроллер ОЗУ Блок выборки инструкций Предсказатель переходов Блоки выполнения инструкций Управляющий блок Блоки выборки данных Блоки декодирования инструкций Ядро процессора 2 Кеш память 1 го уровня (данные) Кеш память 2 го уровня Блок сохранения результата Кеш память 1 го уровня (инструкций) Счетчик команд Регистры Кеш память 1 го уровня (данные) Микрокод Кеш память 1 го уровня (инструкций) Кеш память 2 го уровня Ядро процессора 1 Кеш-память 3 го уровня Контроллер системной шины

Блок работы с прерываниями Контроллер ОЗУ Блок выборки инструкций Предсказатель переходов Блоки выполнения инструкций Управляющий блок Блоки выборки данных Блоки декодирования инструкций Ядро процессора 2 Кеш память 1 го уровня (данные) Кеш память 2 го уровня Блок сохранения результата Кеш память 1 го уровня (инструкций) Счетчик команд Регистры Кеш память 1 го уровня (данные) Микрокод Кеш память 1 го уровня (инструкций) Кеш память 2 го уровня Ядро процессора 1 Кеш-память 3 го уровня Контроллер системной шины

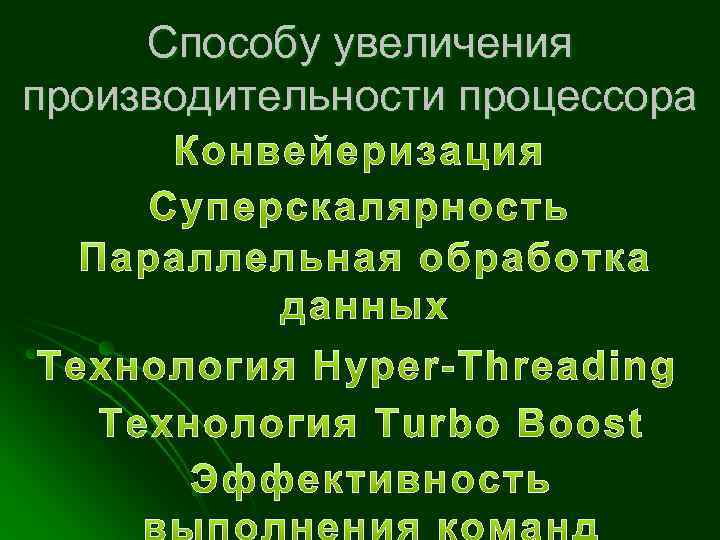

Способу увеличения производительности процессора

Способу увеличения производительности процессора

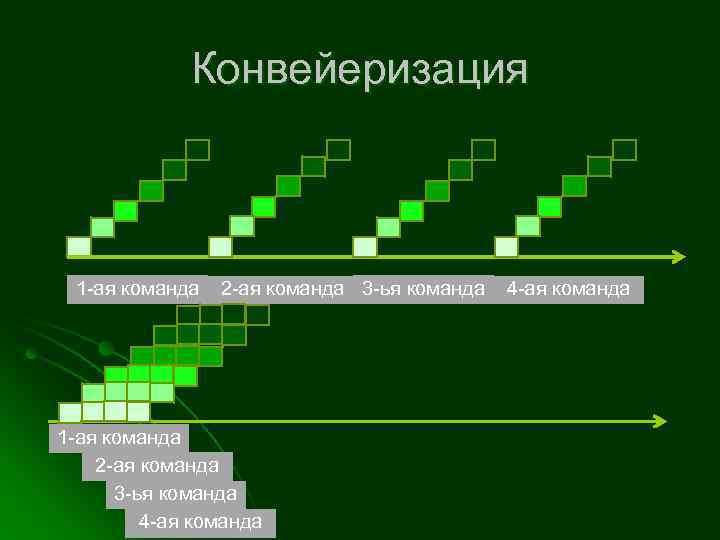

Конвейер l l l Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков Запись результата Увеличение (изменение) счетчика команд

Конвейер l l l Выбор команды Дешифрация Запрос операндов Выполнение команды с получением результата и/или формированием признаков Запись результата Увеличение (изменение) счетчика команд

Конвейеризация 1 -ая команда 2 -ая команда 3 -ья команда 4 -ая команда

Конвейеризация 1 -ая команда 2 -ая команда 3 -ья команда 4 -ая команда

Системы команд: направления развития архитектур l RISC (Reduced Instruction Set Computer): Небольшое количество простых команд, выполняемых за небольшое время l MISC (Minimal Instruction Set Computer): Развитие Set Computer) RISC; 20 -30 простых инструкций l CISC (Complex Instruction Set Computing): Много сложных команд, способных выполнять различные действия; Много шагов на одну команду l VLIW (Very long instruction word): длина инструкций : может достигать 256 бит

Системы команд: направления развития архитектур l RISC (Reduced Instruction Set Computer): Небольшое количество простых команд, выполняемых за небольшое время l MISC (Minimal Instruction Set Computer): Развитие Set Computer) RISC; 20 -30 простых инструкций l CISC (Complex Instruction Set Computing): Много сложных команд, способных выполнять различные действия; Много шагов на одну команду l VLIW (Very long instruction word): длина инструкций : может достигать 256 бит

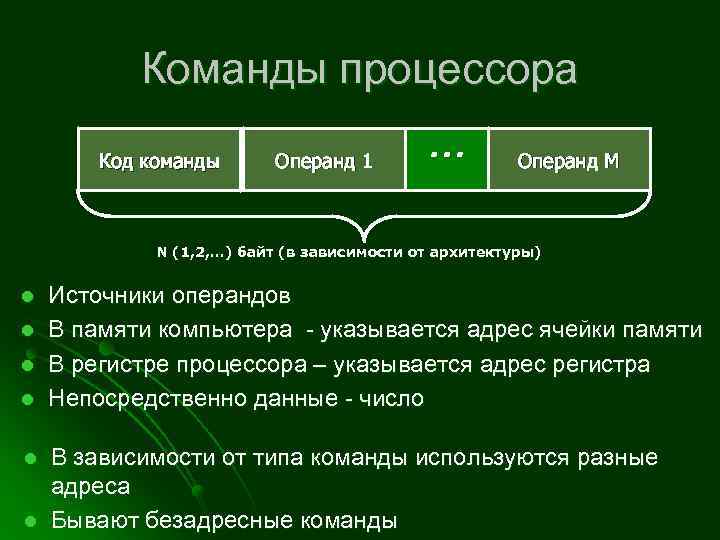

Команды процессора Код команды Операнд 1 … Операнд M N (1, 2, …) байт (в зависимости от архитектуры) l l l Источники операндов В памяти компьютера - указывается адрес ячейки памяти В регистре процессора – указывается адрес регистра Непосредственно данные - число В зависимости от типа команды используются разные адреса Бывают безадресные команды

Команды процессора Код команды Операнд 1 … Операнд M N (1, 2, …) байт (в зависимости от архитектуры) l l l Источники операндов В памяти компьютера - указывается адрес ячейки памяти В регистре процессора – указывается адрес регистра Непосредственно данные - число В зависимости от типа команды используются разные адреса Бывают безадресные команды

Операторные языки l l СИ Паскаль Бейсик - опираются на систему команд процессора l. A=B пересылка данных 0 0 1 0 1 0 1 0

Операторные языки l l СИ Паскаль Бейсик - опираются на систему команд процессора l. A=B пересылка данных 0 0 1 0 1 0 1 0

Выполнение команды пересылки Процессор Регистр Команды УУ АЛУ Контроллеры Устройства Регистр Адреса Память внешняя внутренняя ввода/вывода Обращение за командой Обращение за операндом Запись результата Вывод: команды должны быть как можно более короткие

Выполнение команды пересылки Процессор Регистр Команды УУ АЛУ Контроллеры Устройства Регистр Адреса Память внешняя внутренняя ввода/вывода Обращение за командой Обращение за операндом Запись результата Вывод: команды должны быть как можно более короткие

Как уменьшить длину команды? Сложение Слагаемое 1 Слагаемое 2 Сумма A=(B+С)*В^D l l Промежуточные результаты расчетов не нужны Организовывать вычисления с минимальным количеством обращений к памяти

Как уменьшить длину команды? Сложение Слагаемое 1 Слагаемое 2 Сумма A=(B+С)*В^D l l Промежуточные результаты расчетов не нужны Организовывать вычисления с минимальным количеством обращений к памяти

Регистры Один из операторов обязательно регистр l Регистр - последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. l Регистр - упорядоченная последовательность триггеров l

Регистры Один из операторов обязательно регистр l Регистр - последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. l Регистр - упорядоченная последовательность триггеров l

Устройство триггера 0 0 1 0 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=0 S=0 Не изменяет состояние триггера

Устройство триггера 0 0 1 0 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=0 S=0 Не изменяет состояние триггера

Устройство триггера 0 0 1 10 1 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=0 S=1 изменяет состояние триггера

Устройство триггера 0 0 1 10 1 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=0 S=1 изменяет состояние триггера

Устройство триггера 1 0 1 10 0 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=1 S=0 изменяет состояние триггера R=1 S=1 запрещено

Устройство триггера 1 0 1 10 0 Таблица истинности ИЛИ-НЕ V 1 0 0 1 1 V 2 0 1 Vout 1 0 0 0 R=1 S=0 изменяет состояние триггера R=1 S=1 запрещено

Регистр – совокупность триггеров l Схема синхронного RSтриггера на элементах 2 И-НЕ l Условное графическое обозначение синхронного RS-триггера

Регистр – совокупность триггеров l Схема синхронного RSтриггера на элементах 2 И-НЕ l Условное графическое обозначение синхронного RS-триггера

Регистры процессора Регистры общего назначения Сегментные регистры – обращение к памяти

Регистры процессора Регистры общего назначения Сегментные регистры – обращение к памяти

Регистры общего назначения l Могут использоваться как по усмотрению программиста, так и выполнять заранее назначенные роли l l l l RAX EAX - регистр-аккумулятор EBX - базового адреса. ECX - регистр-счетчик EDX - регистр данных. ESI - индекс источника. EDI - индекс назначения. EBP - указатель базы. ESP - указатель стека. RCX EAX RDX ECX RBX EDX EBX AX CX DX BX AH AL CH CL DH DL BH BL

Регистры общего назначения l Могут использоваться как по усмотрению программиста, так и выполнять заранее назначенные роли l l l l RAX EAX - регистр-аккумулятор EBX - базового адреса. ECX - регистр-счетчик EDX - регистр данных. ESI - индекс источника. EDI - индекс назначения. EBP - указатель базы. ESP - указатель стека. RCX EAX RDX ECX RBX EDX EBX AX CX DX BX AH AL CH CL DH DL BH BL

Сегментные регистры l l CS сегмента кода - в каком месте памяти находится программа DS сегмента данных - локализует используемые программой данные. ES дополняет сегмент данных. SS сегмента стека - стек компьютера. l Сегмент – выделенная область пространства памяти

Сегментные регистры l l CS сегмента кода - в каком месте памяти находится программа DS сегмента данных - локализует используемые программой данные. ES дополняет сегмент данных. SS сегмента стека - стек компьютера. l Сегмент – выделенная область пространства памяти

Стек l Структура данных с методом доступа к элементам LIFO (Last In — First Out, «последним пришёл — первым вышел» ) l Специальная область памяти

Стек l Структура данных с методом доступа к элементам LIFO (Last In — First Out, «последним пришёл — первым вышел» ) l Специальная область памяти

Регистр признаков l Содержит слово состояния процессора

Регистр признаков l Содержит слово состояния процессора

Система команд Команды пересылки l Команды обработки данных: l Арифметические l Логические команды l Команды сдвига l Команды ветвления или управления l Команды обращения к процедурам l Системные команды l

Система команд Команды пересылки l Команды обработки данных: l Арифметические l Логические команды l Команды сдвига l Команды ветвления или управления l Команды обращения к процедурам l Системные команды l

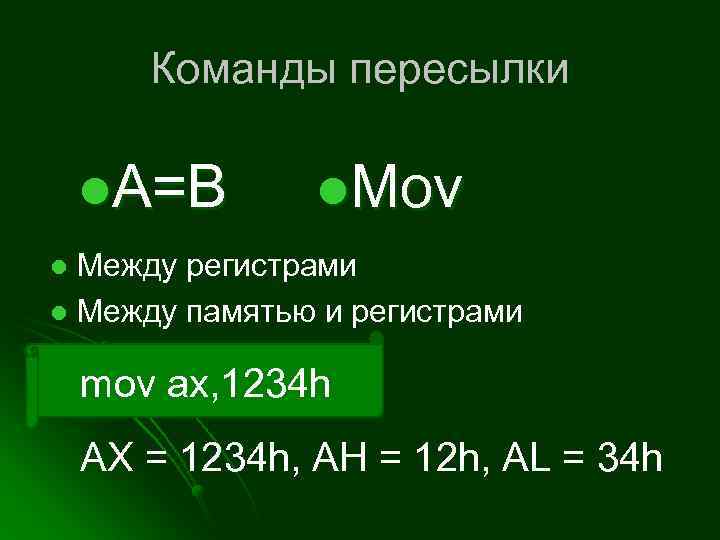

Команды пересылки l. A=B l. Mov Между регистрами l Между памятью и регистрами l mov ax, 1234 h AX = 1234 h, AH = 12 h, AL = 34 h

Команды пересылки l. A=B l. Mov Между регистрами l Между памятью и регистрами l mov ax, 1234 h AX = 1234 h, AH = 12 h, AL = 34 h

Размещении и извлечении значений в стеке mov ax, 4560 h push ax mov cx, FFFFh push cx pop edx 4560 FFFFh.

Размещении и извлечении значений в стеке mov ax, 4560 h push ax mov cx, FFFFh push cx pop edx 4560 FFFFh.

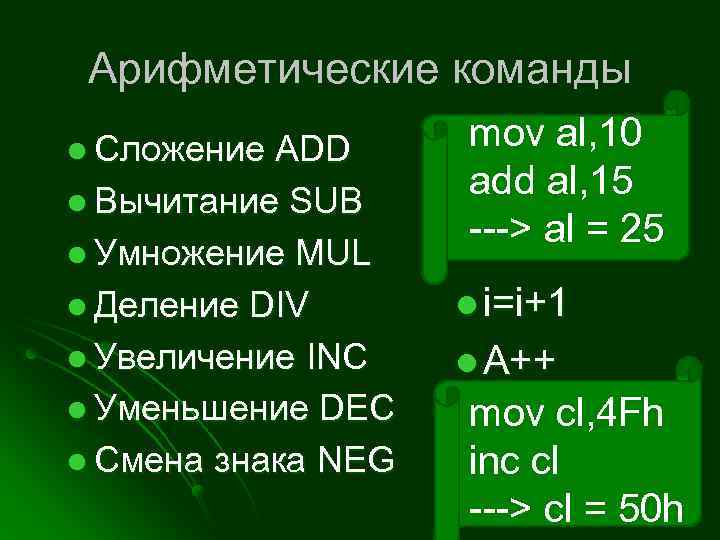

Арифметические команды l Сложение ADD l Вычитание SUB l Умножение MUL mov al, 10 add al, 15 ---> al = 25 l Деление DIV l i=i+1 l Увеличение INC l A++ l Уменьшение DEC l Смена знака NEG mov cl, 4 Fh inc cl ---> cl = 50 h

Арифметические команды l Сложение ADD l Вычитание SUB l Умножение MUL mov al, 10 add al, 15 ---> al = 25 l Деление DIV l i=i+1 l Увеличение INC l A++ l Уменьшение DEC l Смена знака NEG mov cl, 4 Fh inc cl ---> cl = 50 h

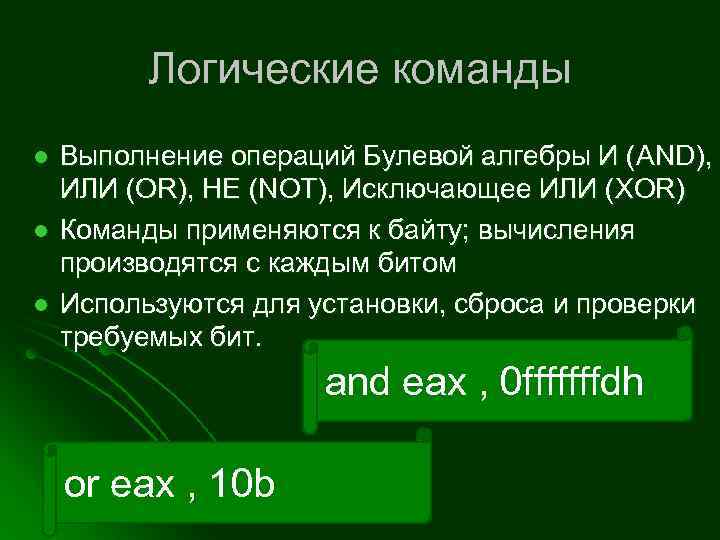

Логические команды l l l Выполнение операций Булевой алгебры И (AND), ИЛИ (OR), НЕ (NOT), Исключающее ИЛИ (XOR) Команды применяются к байту; вычисления производятся с каждым битом Используются для установки, сброса и проверки требуемых бит. and еах , 0 fffffffdh or еах , 10 b

Логические команды l l l Выполнение операций Булевой алгебры И (AND), ИЛИ (OR), НЕ (NOT), Исключающее ИЛИ (XOR) Команды применяются к байту; вычисления производятся с каждым битом Используются для установки, сброса и проверки требуемых бит. and еах , 0 fffffffdh or еах , 10 b

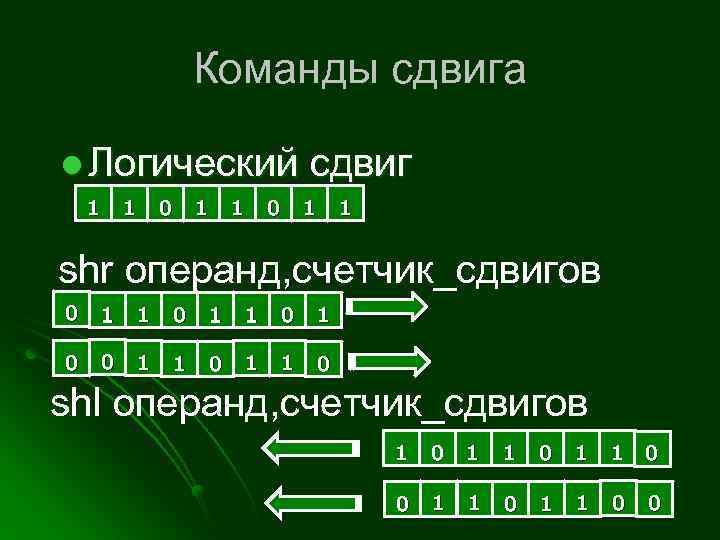

Команды сдвига l Логический сдвиг 1 1 1 0 1 1 shr операнд, счетчик_сдвигов 0 1 1 0 1 0 0 1 1 0 shl операнд, счетчик_сдвигов 1 0 1 1 0 0

Команды сдвига l Логический сдвиг 1 1 1 0 1 1 shr операнд, счетчик_сдвигов 0 1 1 0 1 0 0 1 1 0 shl операнд, счетчик_сдвигов 1 0 1 1 0 0

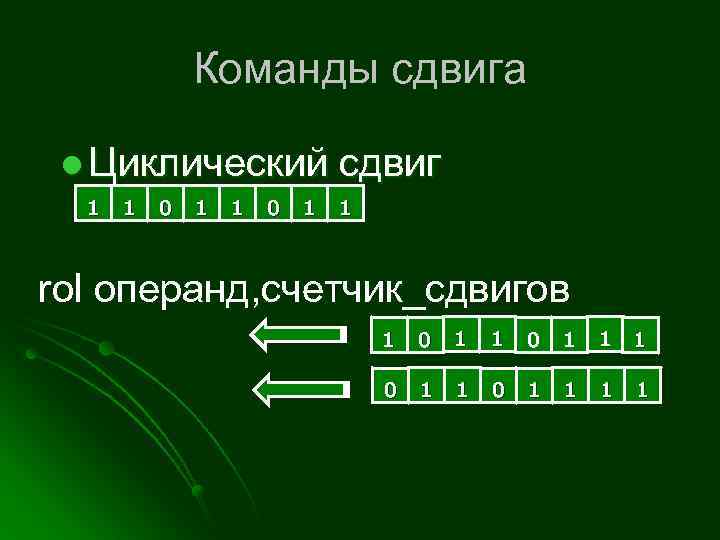

Команды сдвига l Циклический сдвиг 1 1 0 1 1 rol операнд, счетчик_сдвигов 1 0 1 1 1 1

Команды сдвига l Циклический сдвиг 1 1 0 1 1 rol операнд, счетчик_сдвигов 1 0 1 1 1 1

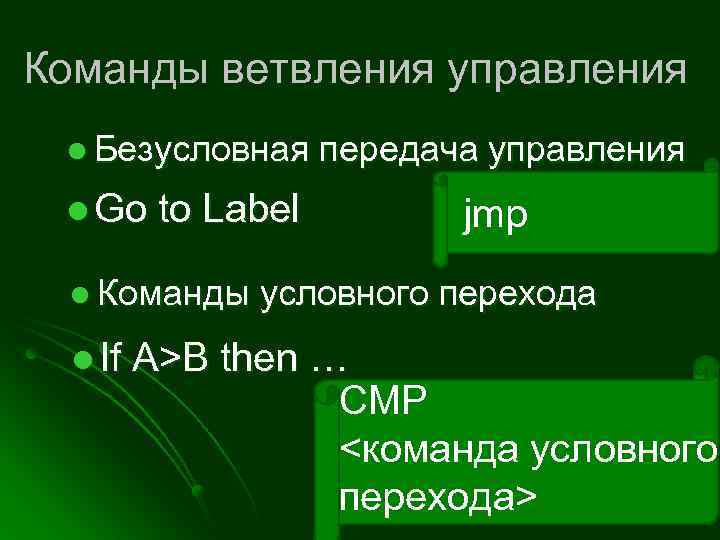

Команды ветвления управления l Безусловная передача управления l Go to Label jmp l Команды условного перехода l If A>B then … CMP <команда условного перехода>

Команды ветвления управления l Безусловная передача управления l Go to Label jmp l Команды условного перехода l If A>B then … CMP <команда условного перехода>

Команды условного перехода Мнемокод команды условного перехода Критерий условного перехода Значения флагов для перехода JE операнд_1=операнд_2 ZF=1 JNE операнд_1<>операнд_2 ZF=0 JL/JNGE операнд_1<операнд_2 SF<>OF JLE/JNG операнд_1<=операнд_2 SF<>OF или ZF=1 JG/JNLE операнд_1>операнд_2 SF=OF или ZF=0 JGE/JNL операнд_1=>операнд_2 SF=OF JB/JNAE операнд_1<операнд_2 CF=1 JBE/JNA операнд_1<=операнд_2 CF=1 или ZF=1 JA/JNBE операнд_1>операнд_2 CF=0 и ZF=0 JAE/JNB операнд_1=>операнд_2 CF=0

Команды условного перехода Мнемокод команды условного перехода Критерий условного перехода Значения флагов для перехода JE операнд_1=операнд_2 ZF=1 JNE операнд_1<>операнд_2 ZF=0 JL/JNGE операнд_1<операнд_2 SF<>OF JLE/JNG операнд_1<=операнд_2 SF<>OF или ZF=1 JG/JNLE операнд_1>операнд_2 SF=OF или ZF=0 JGE/JNL операнд_1=>операнд_2 SF=OF JB/JNAE операнд_1<операнд_2 CF=1 JBE/JNA операнд_1<=операнд_2 CF=1 или ZF=1 JA/JNBE операнд_1>операнд_2 CF=0 и ZF=0 JAE/JNB операнд_1=>операнд_2 CF=0

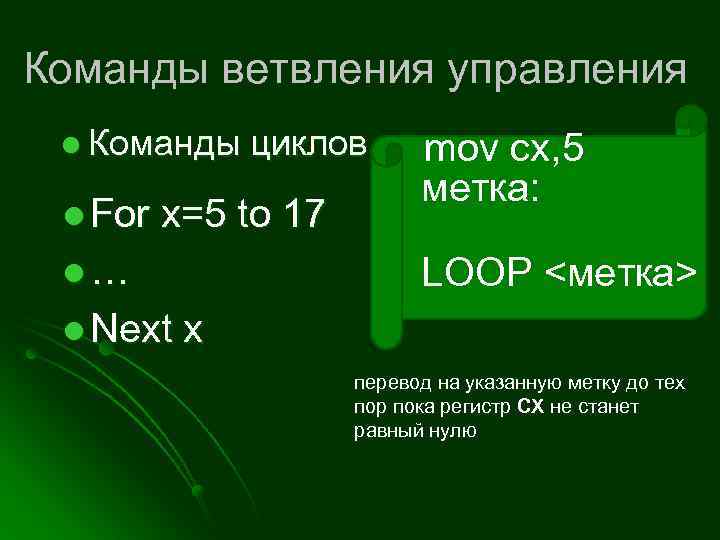

Команды ветвления управления l Команды циклов l For x=5 to 17 l… mov cx, 5 метка: LOOP <метка> l Next x перевод на указанную метку до тех пор пока регистр CX не станет равный нулю

Команды ветвления управления l Команды циклов l For x=5 to 17 l… mov cx, 5 метка: LOOP <метка> l Next x перевод на указанную метку до тех пор пока регистр CX не станет равный нулю

Процедуры l Программа разбивается на части proc 1 proc 2 proc 3 … программа l CALL передача управления процедуре l В конце процедуры команда RET возвращает управление программе

Процедуры l Программа разбивается на части proc 1 proc 2 proc 3 … программа l CALL передача управления процедуре l В конце процедуры команда RET возвращает управление программе

Использование процедур программа … … CALL proc 1 CALL proc 2 CALL proc 1 CALL proc 3 proc 1 proc 2 proc 3

Использование процедур программа … … CALL proc 1 CALL proc 2 CALL proc 1 CALL proc 3 proc 1 proc 2 proc 3

Использование процедур программа CALL proc 1 … … proc 1 CALL proc 2 CALL proc 1 proc 2 CALL proc 3

Использование процедур программа CALL proc 1 … … proc 1 CALL proc 2 CALL proc 1 proc 2 CALL proc 3

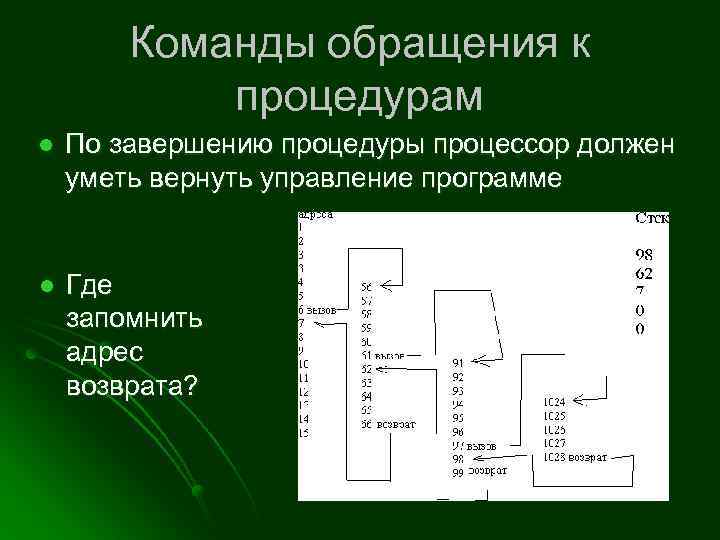

Команды обращения к процедурам l По завершению процедуры процессор должен уметь вернуть управление программе l Где запомнить адрес возврата?

Команды обращения к процедурам l По завершению процедуры процессор должен уметь вернуть управление программе l Где запомнить адрес возврата?

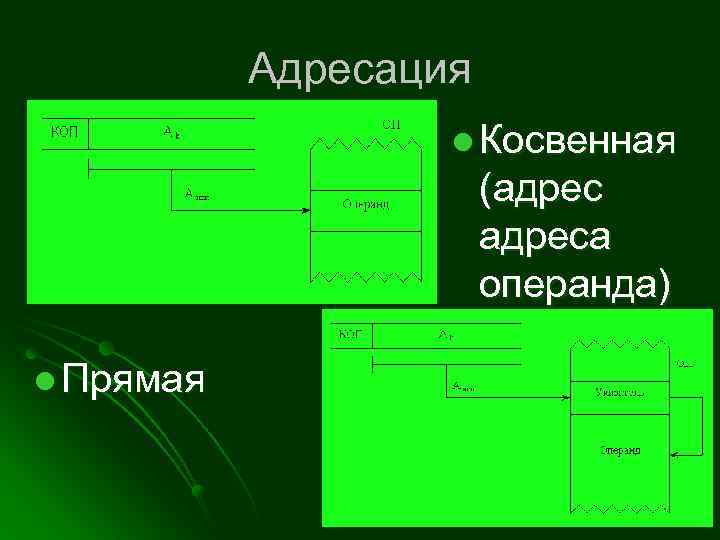

Адресация l Косвенная (адреса операнда) l Прямая

Адресация l Косвенная (адреса операнда) l Прямая

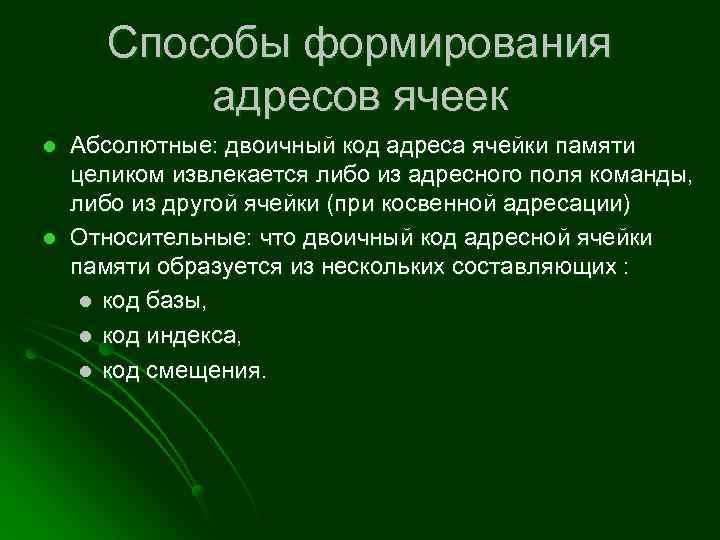

Способы формирования адресов ячеек l l Абсолютные: двоичный код адреса ячейки памяти целиком извлекается либо из адресного поля команды, либо из другой ячейки (при косвенной адресации) Относительные: что двоичный код адресной ячейки памяти образуется из нескольких составляющих : l код базы, l код индекса, l код смещения.

Способы формирования адресов ячеек l l Абсолютные: двоичный код адреса ячейки памяти целиком извлекается либо из адресного поля команды, либо из другой ячейки (при косвенной адресации) Относительные: что двоичный код адресной ячейки памяти образуется из нескольких составляющих : l код базы, l код индекса, l код смещения.

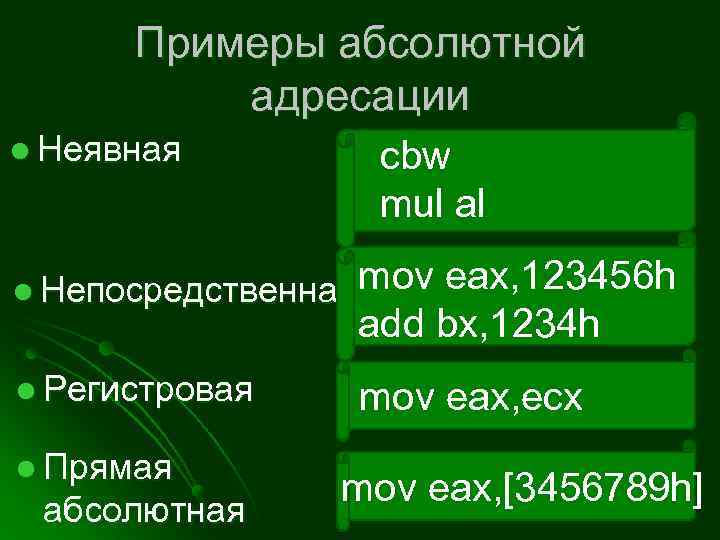

Примеры абсолютной адресации l Неявная cbw mul al l Непосредственная mov eax, 123456 h add bx, 1234 h l Регистровая l Прямая абсолютная mov eax, ecx mov eax, [3456789 h]

Примеры абсолютной адресации l Неявная cbw mul al l Непосредственная mov eax, 123456 h add bx, 1234 h l Регистровая l Прямая абсолютная mov eax, ecx mov eax, [3456789 h]

![Косвенная адресация l Косвенно регистровая mov eax, [ecx] Косвенная адресация l Косвенно регистровая mov eax, [ecx]](https://present5.com/presentation/-57401306_227602664/image-56.jpg) Косвенная адресация l Косвенно регистровая mov eax, [ecx]

Косвенная адресация l Косвенно регистровая mov eax, [ecx]

Индексная адресация

Индексная адресация

![Косвенная адресация l Косвенная регистровая add ax, [bx+2] (базовая) адресация со смещением l Косвенная Косвенная адресация l Косвенная регистровая add ax, [bx+2] (базовая) адресация со смещением l Косвенная](https://present5.com/presentation/-57401306_227602664/image-58.jpg) Косвенная адресация l Косвенная регистровая add ax, [bx+2] (базовая) адресация со смещением l Косвенная базовая mov ax, [bp+si] индексная адресация add ax, [bx+di]

Косвенная адресация l Косвенная регистровая add ax, [bx+2] (базовая) адресация со смещением l Косвенная базовая mov ax, [bp+si] индексная адресация add ax, [bx+di]