Лекция_5t_Эвм_Традиционной_арх.ppt

- Количество слайдов: 30

ЭВМ традиционной архитектуры

ЭВМ традиционной архитектуры

ЭВМ фон-неймановской архитектуры. • Архитектура фон Неймана — широко известный принцип совместного хранения программ и данных в памяти компьютера. Вычислительные системы такого рода часто обозначают термином «Машина фон Неймана» . • В общем случае, когда говорят об архитектуре фон Неймана (нем. von Neumann), подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

ЭВМ фон-неймановской архитектуры. • Архитектура фон Неймана — широко известный принцип совместного хранения программ и данных в памяти компьютера. Вычислительные системы такого рода часто обозначают термином «Машина фон Неймана» . • В общем случае, когда говорят об архитектуре фон Неймана (нем. von Neumann), подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

ЭВМ фон-неймановской архитектуры. • В 1946 году группа учёных во главе с Джоном фон Нейманом (Г. Голдстайн, А. Беркс) опубликовали статью «Предварительное рассмотрение логической конструкции Электронно-вычислительного устройства» . • В статье обосновывалось использование двоичной системы для представления данных в ЭВМ (преимущественно для технической реализации, простота выполнения арифметических и логических операций. До этого машины хранили данные в десятеричном виде), выдвигалась идея использования программами общей памяти. • Имя фон Неймана было достаточно широко известно в науке того времени, что отодвинуло на второй план его соавторов, и данные идеи получили название «Принципы фон Неймана» .

ЭВМ фон-неймановской архитектуры. • В 1946 году группа учёных во главе с Джоном фон Нейманом (Г. Голдстайн, А. Беркс) опубликовали статью «Предварительное рассмотрение логической конструкции Электронно-вычислительного устройства» . • В статье обосновывалось использование двоичной системы для представления данных в ЭВМ (преимущественно для технической реализации, простота выполнения арифметических и логических операций. До этого машины хранили данные в десятеричном виде), выдвигалась идея использования программами общей памяти. • Имя фон Неймана было достаточно широко известно в науке того времени, что отодвинуло на второй план его соавторов, и данные идеи получили название «Принципы фон Неймана» .

ЭВМ фон-неймановской архитектуры. 1. Принцип программного управления. Программа состоит из набора команд, которые выполняются процессором друг за другом в определенной последовательности. 2. Принцип однородности памяти. Как программы, так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления - чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными. 3. Принцип адресуемости памяти. Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Компьютеры, построенные на этих принципах, относят к типу фоннеймановских.

ЭВМ фон-неймановской архитектуры. 1. Принцип программного управления. Программа состоит из набора команд, которые выполняются процессором друг за другом в определенной последовательности. 2. Принцип однородности памяти. Как программы, так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления - чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными. 3. Принцип адресуемости памяти. Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Компьютеры, построенные на этих принципах, относят к типу фоннеймановских.

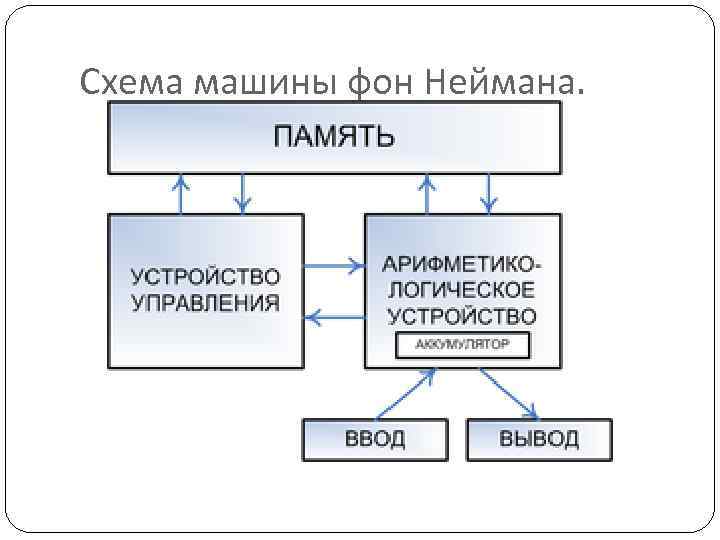

Схема машины фон Неймана.

Схема машины фон Неймана.

Гарвардская архитектура • Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930 -х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. • Гарвардская архитектура не использовалась вплоть до конца 70 -х годов. • Виды : – Классическая гарвардская архитектура – Модифицированная гарвардская архитектура – Расширенная гарвардская архитектура

Гарвардская архитектура • Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930 -х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. • Гарвардская архитектура не использовалась вплоть до конца 70 -х годов. • Виды : – Классическая гарвардская архитектура – Модифицированная гарвардская архитектура – Расширенная гарвардская архитектура

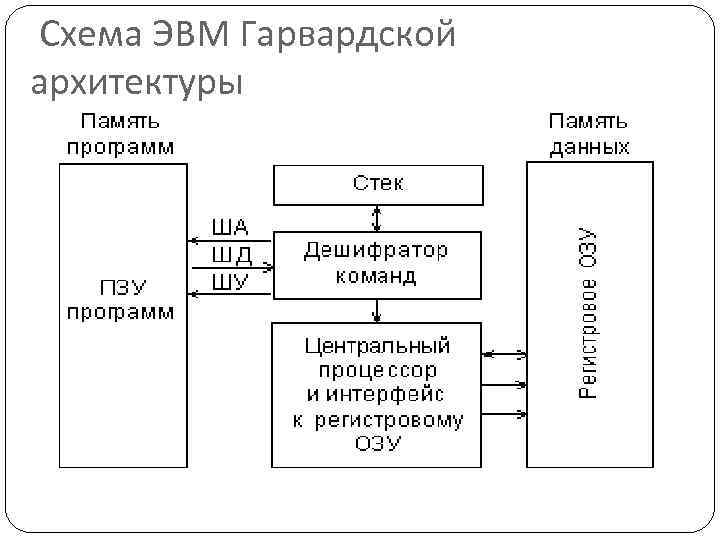

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных

Схема ЭВМ Гарвардской архитектуры

Схема ЭВМ Гарвардской архитектуры

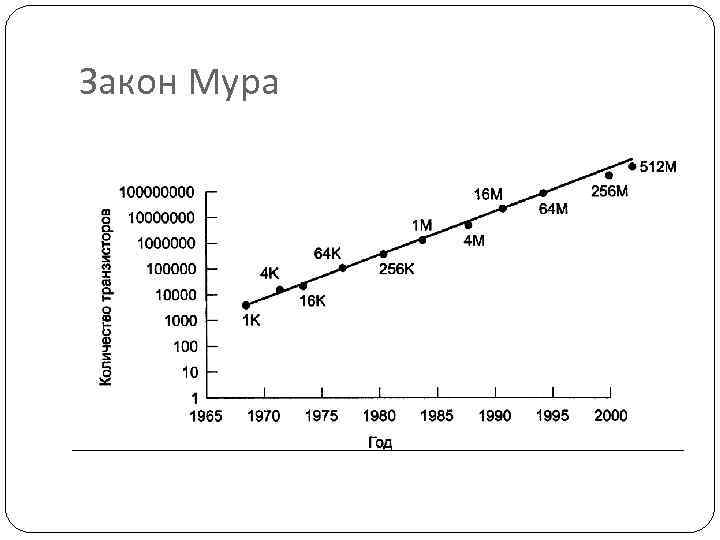

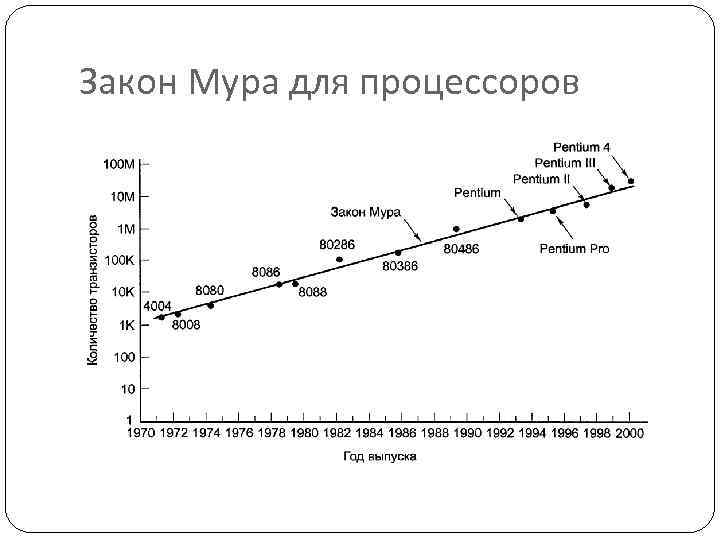

Закон Мура • Поскольку у каждого нового поколения компьютеров было в 4 раза больше памяти, чем у предыдущего, стало понятно, что число транзисторов на микросхеме возрастает на постоянную величину и, таким образом, этот рост можно предсказать на годы вперед. • Закон Мура гласит, что количество транзисторов на одной микросхеме удваивается каждые 18 месяцев,

Закон Мура • Поскольку у каждого нового поколения компьютеров было в 4 раза больше памяти, чем у предыдущего, стало понятно, что число транзисторов на микросхеме возрастает на постоянную величину и, таким образом, этот рост можно предсказать на годы вперед. • Закон Мура гласит, что количество транзисторов на одной микросхеме удваивается каждые 18 месяцев,

Закон Мура

Закон Мура

Первый закон программного обеспечения Первый закон программного обеспечения, названный в честь Натана Мирвольда (Nathan Myhrvold), главного администратора компании Microsoft. Этот закон гласит: «Программное обеспечение — это газ. Он распространяется и полностью заполняет резервуар, в котором находится» .

Первый закон программного обеспечения Первый закон программного обеспечения, названный в честь Натана Мирвольда (Nathan Myhrvold), главного администратора компании Microsoft. Этот закон гласит: «Программное обеспечение — это газ. Он распространяется и полностью заполняет резервуар, в котором находится» .

Pentium 4 • В 1968 году Роберт Нойс (Robert Noyce), изобретатель кремниевой интегральной схемы, Гордон Мур (Gordon Moore), автор известного закона Мура, и Артур Рок (Arthur Rock), венчурный капиталист из Сан-Франциско, основали корпорацию Intel для производства компьютерных микросхем. За первый год своего существования корпорация продала микросхем всего на 3000 долларов, но потом объем продаж заметно вырос.

Pentium 4 • В 1968 году Роберт Нойс (Robert Noyce), изобретатель кремниевой интегральной схемы, Гордон Мур (Gordon Moore), автор известного закона Мура, и Артур Рок (Arthur Rock), венчурный капиталист из Сан-Франциско, основали корпорацию Intel для производства компьютерных микросхем. За первый год своего существования корпорация продала микросхем всего на 3000 долларов, но потом объем продаж заметно вырос.

Семейство процессоров Intel. Микросхе Дата МГц Количество Объем Примечание ма выпуска транзисторов памяти 4004 4/1971 0, 108 2 300 640 байт Первый микропроцессор на микросхеме 8008 4/1972 0, 08 3 500 16 Кбайт Первый 8 разрядный микропроцессор 8080 4/1974 2 6 000 64 Кбайт Первый многоцелевой процессор на микросхеме 8086 6/1978 5 -10 29 000 1 Мбайт Первый 16 разрядный процессор на микросхеме

Семейство процессоров Intel. Микросхе Дата МГц Количество Объем Примечание ма выпуска транзисторов памяти 4004 4/1971 0, 108 2 300 640 байт Первый микропроцессор на микросхеме 8008 4/1972 0, 08 3 500 16 Кбайт Первый 8 разрядный микропроцессор 8080 4/1974 2 6 000 64 Кбайт Первый многоцелевой процессор на микросхеме 8086 6/1978 5 -10 29 000 1 Мбайт Первый 16 разрядный процессор на микросхеме

Семейство процессоров Intel. Микросхе Дата МГц ма выпуска 8088 6/1979 5 -8 80286 80386 80486 Pentium Количество Объем Примечание транзисторов памяти 29 000 1 Мбайт Использовался в IBM PC 2/1982 8 -12 134 000 16 Мбайт Появилась защита памяти 10/1985 16 -33 275 000 4 Гбайт Первый 32 разрядный процессор 4/1989 25 -100 1 200 000 4 Гбайт Кэш-память на 8 Кбайт 3/1993 60 -223 3 100 000 4 Гбайт Два конвейера, у более поздних моделей — ММХ

Семейство процессоров Intel. Микросхе Дата МГц ма выпуска 8088 6/1979 5 -8 80286 80386 80486 Pentium Количество Объем Примечание транзисторов памяти 29 000 1 Мбайт Использовался в IBM PC 2/1982 8 -12 134 000 16 Мбайт Появилась защита памяти 10/1985 16 -33 275 000 4 Гбайт Первый 32 разрядный процессор 4/1989 25 -100 1 200 000 4 Гбайт Кэш-память на 8 Кбайт 3/1993 60 -223 3 100 000 4 Гбайт Два конвейера, у более поздних моделей — ММХ

Семейство процессоров Intel. Микросхе ма Pentium Pro Pentium II Дата МГц выпуска 3/1995 150200 5/1997 233400 Pentium lll 2/1999 6501400 Количество Объем транзисторов памяти 5 500 000 4 Гбайт Pentium 4 11/2000 13003800 7 500 000 4 Гбайт 9 500 000 4 Гбайт 42 000 4 Гбайт Примечание 2 Два уровня кэшпамяти Pentium Pro плюс ММХ Появились SSEкоманды, ускоряющие обработку трехмерной графики Гиперпоточность, дополнительные SSE-команды

Семейство процессоров Intel. Микросхе ма Pentium Pro Pentium II Дата МГц выпуска 3/1995 150200 5/1997 233400 Pentium lll 2/1999 6501400 Количество Объем транзисторов памяти 5 500 000 4 Гбайт Pentium 4 11/2000 13003800 7 500 000 4 Гбайт 9 500 000 4 Гбайт 42 000 4 Гбайт Примечание 2 Два уровня кэшпамяти Pentium Pro плюс ММХ Появились SSEкоманды, ускоряющие обработку трехмерной графики Гиперпоточность, дополнительные SSE-команды

Закон Мура для процессоров

Закон Мура для процессоров

Тракт данных обычной фоннеймановской машины

Тракт данных обычной фоннеймановской машины

Шаги выполнения команд процессором Вызывает следующую команду из памяти и переносит ее в регистр команд. Меняет положение счетчика команд, который после этого указывает на следующую команду1. Определяет тип вызванной команды. Если команда использует слово из памяти, определяет, где находится это слово. Переносит слово, если это необходимо, в регистр центрального процессора 2. Выполняет команду. Переходит к шагу 1, чтобы начать выполнение следующей команды.

Шаги выполнения команд процессором Вызывает следующую команду из памяти и переносит ее в регистр команд. Меняет положение счетчика команд, который после этого указывает на следующую команду1. Определяет тип вызванной команды. Если команда использует слово из памяти, определяет, где находится это слово. Переносит слово, если это необходимо, в регистр центрального процессора 2. Выполняет команду. Переходит к шагу 1, чтобы начать выполнение следующей команды.

Архитектура МП Микроархитектуры и макроархитектуры. Микроархитектура МП – это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали. Макроархитектура – это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

Архитектура МП Микроархитектуры и макроархитектуры. Микроархитектура МП – это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали. Макроархитектура – это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

Характеристики микропроцессоров Макроархитектуры CISC (Complex Instruction Set Computing) с полным набором команд; RISC (Reduced Instruction Set Computing) с сокращенным набором команд; MISC (Minimum Instruction Set Computing) с минимальным набором команд.

Характеристики микропроцессоров Макроархитектуры CISC (Complex Instruction Set Computing) с полным набором команд; RISC (Reduced Instruction Set Computing) с сокращенным набором команд; MISC (Minimum Instruction Set Computing) с минимальным набором команд.

Особенности RISC Выполняется больше команд чем в процессорах CISC, но быстро действие выше у процессоров RISC Мало распространены из-за коммерческой не «эффективности» Косвенно реализована и в CISC процессорах (Процессоры Intel содержат RISC-ядро)

Особенности RISC Выполняется больше команд чем в процессорах CISC, но быстро действие выше у процессоров RISC Мало распространены из-за коммерческой не «эффективности» Косвенно реализована и в CISC процессорах (Процессоры Intel содержат RISC-ядро)

Параллелизм параллелизм на уровне команд - запуска большого количества команд каждую секунду. параллелизм на уровне процессоров. – над одним заданием работают одновременно несколько процессоров.

Параллелизм параллелизм на уровне команд - запуска большого количества команд каждую секунду. параллелизм на уровне процессоров. – над одним заданием работают одновременно несколько процессоров.

Параллелизм на уровне команд Конвейеры Суперскалярные архитектуры

Параллелизм на уровне команд Конвейеры Суперскалярные архитектуры

Конвейеры главным препятствием высокой скорости выполнения команд - необходимость их вызова из памяти. Решение - можно вызывать команды из памяти заранее и хранить в специальном наборе регистров. вызов команды, а затем – ее выполнение.

Конвейеры главным препятствием высокой скорости выполнения команд - необходимость их вызова из памяти. Решение - можно вызывать команды из памяти заранее и хранить в специальном наборе регистров. вызов команды, а затем – ее выполнение.

Пятиступенчатый конвейер

Пятиступенчатый конвейер

Пятиступенчатый конвейер • Первая ступень (блок С 1) вызывает команду из памяти и помещает ее в буфер, где она хранится до тех пор, пока не потребуется. • Вторая ступень (блок С 2) декодирует эту команду, определяя ее тип и тип ее операндов. • Третья ступень (блок СЗ) определяет местонахождение операндов и вызывает их из регистров или из памяти.

Пятиступенчатый конвейер • Первая ступень (блок С 1) вызывает команду из памяти и помещает ее в буфер, где она хранится до тех пор, пока не потребуется. • Вторая ступень (блок С 2) декодирует эту команду, определяя ее тип и тип ее операндов. • Третья ступень (блок СЗ) определяет местонахождение операндов и вызывает их из регистров или из памяти.

Пятиступенчатый конвейер Четвертая ступень (блок С 4) выполняет команду, обычно проводя операнды через тракт данных. Пятая ступень (блок С 5) записывает результат обратно в нужный регистр.

Пятиступенчатый конвейер Четвертая ступень (блок С 4) выполняет команду, обычно проводя операнды через тракт данных. Пятая ступень (блок С 5) записывает результат обратно в нужный регистр.

Достоинство конвейера Конвейеры позволяют добиться компромисса между временем запаздывания (время выполнения одной команды) и пропускной способностью процессора (количество команд, выполняемых процессором в секунду).

Достоинство конвейера Конвейеры позволяют добиться компромисса между временем запаздывания (время выполнения одной команды) и пропускной способностью процессора (количество команд, выполняемых процессором в секунду).

Суперскалярные архитектуры Суперскалярными называют процессоры, способные запускать несколько команд (зачастую от четырех до шести) за один тактовый цикл.

Суперскалярные архитектуры Суперскалярными называют процессоры, способные запускать несколько команд (зачастую от четырех до шести) за один тактовый цикл.

Суперскалярный процессор с пятью функциональными блоками

Суперскалярный процессор с пятью функциональными блоками