9311e369fb9306da6e9d017eb4952ebd.ppt

- Количество слайдов: 11

EPICS Meeting 2005, SLAC Spallation Neutron Source Low-Level RF Control System Kay-Uwe Kasemir, Mark Champion April 2005 ORNL/SNS

EPICS Meeting 2005, SLAC Spallation Neutron Source Low-Level RF Control System Kay-Uwe Kasemir, Mark Champion April 2005 ORNL/SNS

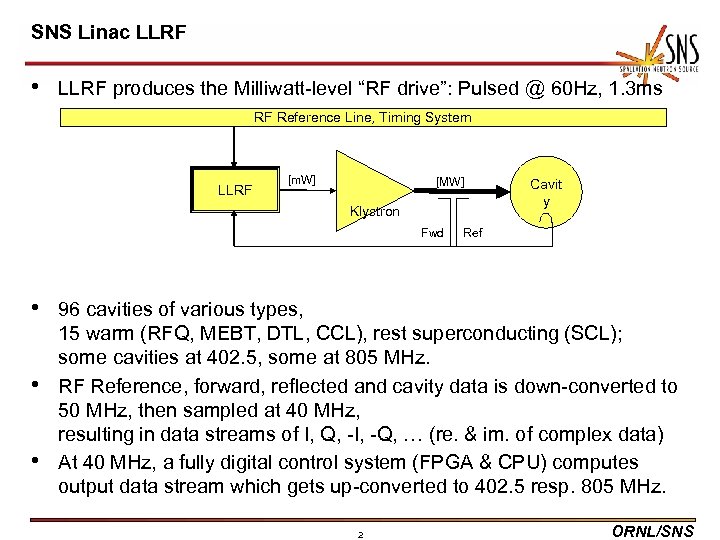

SNS Linac LLRF • LLRF produces the Milliwatt-level “RF drive”: Pulsed @ 60 Hz, 1. 3 ms RF Reference Line, Timing System LLRF [m. W] [MW] Klystron Fwd Cavit y Ref • 96 cavities of various types, • • 15 warm (RFQ, MEBT, DTL, CCL), rest superconducting (SCL); some cavities at 402. 5, some at 805 MHz. RF Reference, forward, reflected and cavity data is down-converted to 50 MHz, then sampled at 40 MHz, resulting in data streams of I, Q, -I, -Q, … (re. & im. of complex data) At 40 MHz, a fully digital control system (FPGA & CPU) computes output data stream which gets up-converted to 402. 5 resp. 805 MHz. 2 ORNL/SNS

SNS Linac LLRF • LLRF produces the Milliwatt-level “RF drive”: Pulsed @ 60 Hz, 1. 3 ms RF Reference Line, Timing System LLRF [m. W] [MW] Klystron Fwd Cavit y Ref • 96 cavities of various types, • • 15 warm (RFQ, MEBT, DTL, CCL), rest superconducting (SCL); some cavities at 402. 5, some at 805 MHz. RF Reference, forward, reflected and cavity data is down-converted to 50 MHz, then sampled at 40 MHz, resulting in data streams of I, Q, -I, -Q, … (re. & im. of complex data) At 40 MHz, a fully digital control system (FPGA & CPU) computes output data stream which gets up-converted to 402. 5 resp. 805 MHz. 2 ORNL/SNS

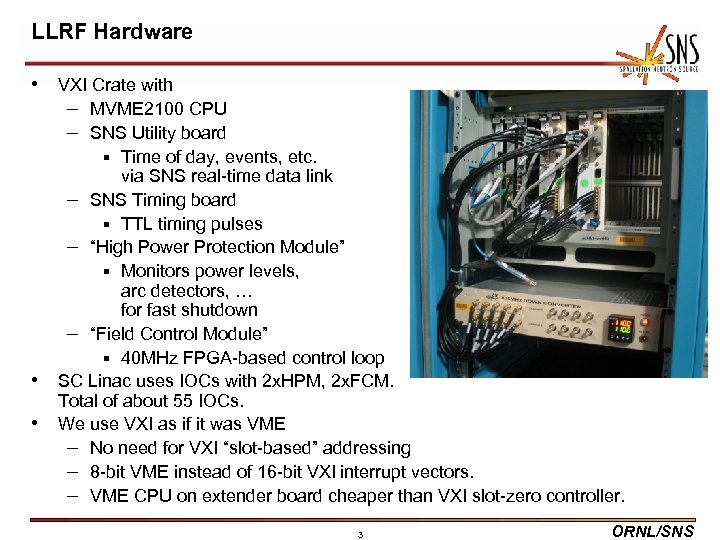

LLRF Hardware • VXI Crate with – MVME 2100 CPU – SNS Utility board § Time of day, events, etc. • • via SNS real-time data link – SNS Timing board § TTL timing pulses – “High Power Protection Module” § Monitors power levels, arc detectors, … for fast shutdown – “Field Control Module” § 40 MHz FPGA-based control loop SC Linac uses IOCs with 2 x. HPM, 2 x. FCM. Total of about 55 IOCs. We use VXI as if it was VME – No need for VXI “slot-based” addressing – 8 -bit VME instead of 16 -bit VXI interrupt vectors. – VME CPU on extender board cheaper than VXI slot-zero controller. 3 ORNL/SNS

LLRF Hardware • VXI Crate with – MVME 2100 CPU – SNS Utility board § Time of day, events, etc. • • via SNS real-time data link – SNS Timing board § TTL timing pulses – “High Power Protection Module” § Monitors power levels, arc detectors, … for fast shutdown – “Field Control Module” § 40 MHz FPGA-based control loop SC Linac uses IOCs with 2 x. HPM, 2 x. FCM. Total of about 55 IOCs. We use VXI as if it was VME – No need for VXI “slot-based” addressing – 8 -bit VME instead of 16 -bit VXI interrupt vectors. – VME CPU on extender board cheaper than VXI slot-zero controller. 3 ORNL/SNS

HPM - High Power Protection Module • Fast RF Shutdown • Monitors 8 RF channels, • • • -50…+10 d. Bm (10 n. W… 10 m. W), for the duration of the RF gate. – Per-channel threshold and time limit. Trips when RF above threshold longer than time limit. Monitors 14 arc detector inputs. Computed/software interlocks. Everything can be enabled/disabled, except one hardware input for “Vacuum OK” signal. 2 history buffers capture 2 ms of data (2 s resolution). User selectable for any RF channel, arc detector, or misc. other internals of the HPM. Trip information is sent to the FCM via redundant VXI backplane lines. FCM then cuts the RF drive. 4 ORNL/SNS

HPM - High Power Protection Module • Fast RF Shutdown • Monitors 8 RF channels, • • • -50…+10 d. Bm (10 n. W… 10 m. W), for the duration of the RF gate. – Per-channel threshold and time limit. Trips when RF above threshold longer than time limit. Monitors 14 arc detector inputs. Computed/software interlocks. Everything can be enabled/disabled, except one hardware input for “Vacuum OK” signal. 2 history buffers capture 2 ms of data (2 s resolution). User selectable for any RF channel, arc detector, or misc. other internals of the HPM. Trip information is sent to the FCM via redundant VXI backplane lines. FCM then cuts the RF drive. 4 ORNL/SNS

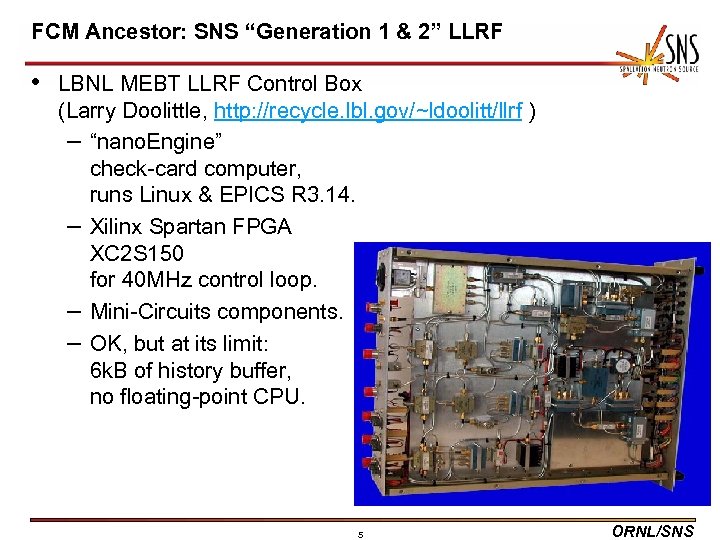

FCM Ancestor: SNS “Generation 1 & 2” LLRF • LBNL MEBT LLRF Control Box (Larry Doolittle, http: //recycle. lbl. gov/~ldoolitt/llrf ) – “nano. Engine” check-card computer, runs Linux & EPICS R 3. 14. – Xilinx Spartan FPGA XC 2 S 150 for 40 MHz control loop. – Mini-Circuits components. – OK, but at its limit: 6 k. B of history buffer, no floating-point CPU. 5 ORNL/SNS

FCM Ancestor: SNS “Generation 1 & 2” LLRF • LBNL MEBT LLRF Control Box (Larry Doolittle, http: //recycle. lbl. gov/~ldoolitt/llrf ) – “nano. Engine” check-card computer, runs Linux & EPICS R 3. 14. – Xilinx Spartan FPGA XC 2 S 150 for 40 MHz control loop. – Mini-Circuits components. – OK, but at its limit: 6 k. B of history buffer, no floating-point CPU. 5 ORNL/SNS

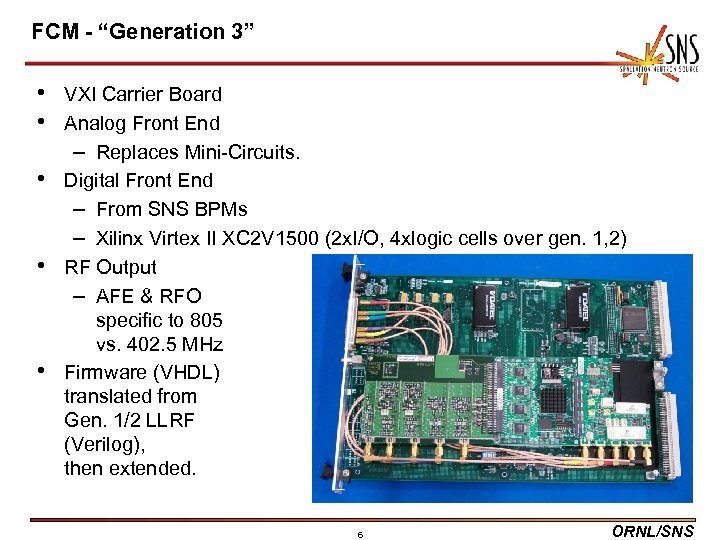

FCM - “Generation 3” • VXI Carrier Board • Analog Front End – Replaces Mini-Circuits. • Digital Front End – From SNS BPMs – Xilinx Virtex II XC 2 V 1500 (2 x. I/O, 4 xlogic cells over gen. 1, 2) • RF Output – AFE & RFO • specific to 805 vs. 402. 5 MHz Firmware (VHDL) translated from Gen. 1/2 LLRF (Verilog), then extended. 6 ORNL/SNS

FCM - “Generation 3” • VXI Carrier Board • Analog Front End – Replaces Mini-Circuits. • Digital Front End – From SNS BPMs – Xilinx Virtex II XC 2 V 1500 (2 x. I/O, 4 xlogic cells over gen. 1, 2) • RF Output – AFE & RFO • specific to 805 vs. 402. 5 MHz Firmware (VHDL) translated from Gen. 1/2 LLRF (Verilog), then extended. 6 ORNL/SNS

FCM Firmware vs. CPU Software • FCM Firmware – 40 Mhz PI controller. – History Buffers: 5 x 512 x 16 bit x {I, Q} • with configurable zoom & pan. – Feed-Forward Buffer: 4096 x 8 bit x {I, Q}, 200 ns or 400 ns granularity. CPU Software – ‘Arm’ waveform updates synchronously with SNS event link. – Decode raw buffer data into I, Q, Phase, Amplitude waveforms. – Resonance Error Calculation. – Adaptive Feed-Forward. – Automation. 7 ORNL/SNS

FCM Firmware vs. CPU Software • FCM Firmware – 40 Mhz PI controller. – History Buffers: 5 x 512 x 16 bit x {I, Q} • with configurable zoom & pan. – Feed-Forward Buffer: 4096 x 8 bit x {I, Q}, 200 ns or 400 ns granularity. CPU Software – ‘Arm’ waveform updates synchronously with SNS event link. – Decode raw buffer data into I, Q, Phase, Amplitude waveforms. – Resonance Error Calculation. – Adaptive Feed-Forward. – Automation. 7 ORNL/SNS

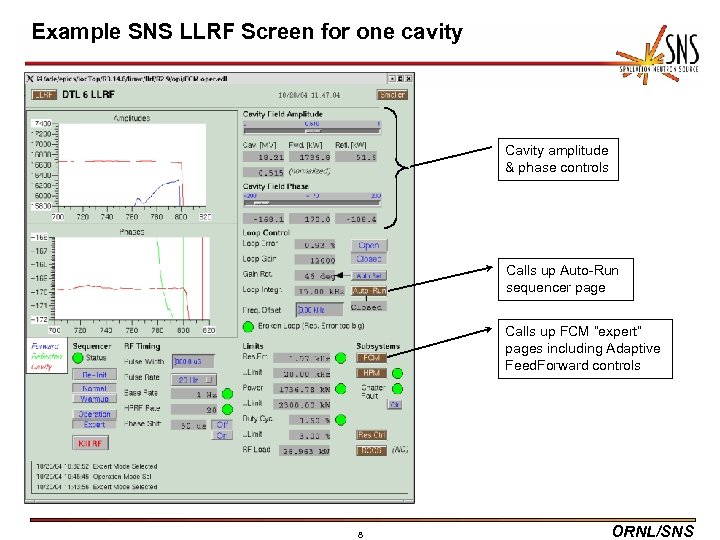

Example SNS LLRF Screen for one cavity Cavity amplitude & phase controls Calls up Auto-Run sequencer page Calls up FCM “expert” pages including Adaptive Feed. Forward controls 8 ORNL/SNS

Example SNS LLRF Screen for one cavity Cavity amplitude & phase controls Calls up Auto-Run sequencer page Calls up FCM “expert” pages including Adaptive Feed. Forward controls 8 ORNL/SNS

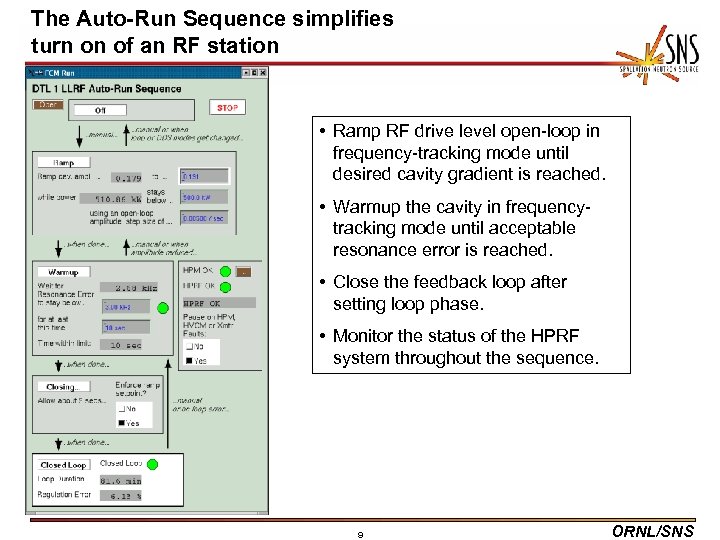

The Auto-Run Sequence simplifies turn on of an RF station • Ramp RF drive level open-loop in frequency-tracking mode until desired cavity gradient is reached. • Warmup the cavity in frequencytracking mode until acceptable resonance error is reached. • Close the feedback loop after setting loop phase. • Monitor the status of the HPRF system throughout the sequence. 9 ORNL/SNS

The Auto-Run Sequence simplifies turn on of an RF station • Ramp RF drive level open-loop in frequency-tracking mode until desired cavity gradient is reached. • Warmup the cavity in frequencytracking mode until acceptable resonance error is reached. • Close the feedback loop after setting loop phase. • Monitor the status of the HPRF system throughout the sequence. 9 ORNL/SNS

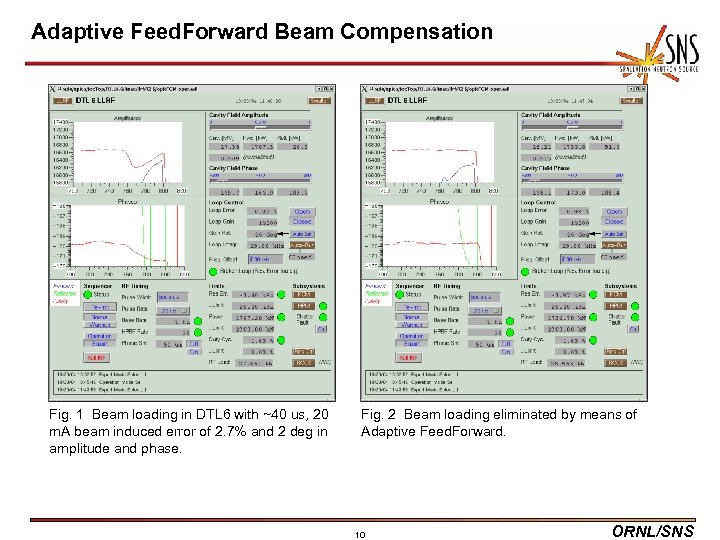

Adaptive Feed. Forward Beam Compensation Fig. 1 Beam loading in DTL 6 with ~40 us, 20 m. A beam induced error of 2. 7% and 2 deg in amplitude and phase. Fig. 2 Beam loading eliminated by means of Adaptive Feed. Forward. 10 ORNL/SNS

Adaptive Feed. Forward Beam Compensation Fig. 1 Beam loading in DTL 6 with ~40 us, 20 m. A beam induced error of 2. 7% and 2 deg in amplitude and phase. Fig. 2 Beam loading eliminated by means of Adaptive Feed. Forward. 10 ORNL/SNS

SNS LLRF Status • Installation of IOCs completed, • maybe 80% of the cavities connected. Working on improved – Interlocks – Closed loop for superconducting section – Adaptive feed forward – Firmware: Larry Doolittle wrote new firmware in Verilog which synthesizes for Generation 1, 2 & 3 hardware. Debug this ‘portable’ firmware and use it, or stay with proven ‘FCM-only’ firmware? 11 ORNL/SNS

SNS LLRF Status • Installation of IOCs completed, • maybe 80% of the cavities connected. Working on improved – Interlocks – Closed loop for superconducting section – Adaptive feed forward – Firmware: Larry Doolittle wrote new firmware in Verilog which synthesizes for Generation 1, 2 & 3 hardware. Debug this ‘portable’ firmware and use it, or stay with proven ‘FCM-only’ firmware? 11 ORNL/SNS