23eb5e7cbec5fea9b7270abe7353ccfc.ppt

- Количество слайдов: 36

EMBEDDED SYSTEMS SOFTWARE TRAINING CENTER ARM CORTEX-M 4 MCU AND STM 32 F 4 DISCOVERY BOARD DESCRIPTION COPYRIGHT © 2016 DSR CORPORATION

Instructor Introduction Matveev Alexey Igorevich Senior software developer, DSR corp. Copyright © 2016 DSR Corporation 2

Objectives Learn basics about ARM Cortex-M 4 background architecture STM 32 F 4 DISCOVERY board functional review Development tools for ARM Cortex-M 4 Getting started with STM 32 F 407 configuration and programming. Copyright © 2016 DSR Corporation 3

Agenda History and background of ARM CPUs STM 32 F 4 DISCOVERY board review STM 32 F 407 VGT 6 MCU functional review Development tools for ARM programming STM 32 F 407 programming basics Memory organization Chipset frequency configuration General Purpose Input/Output Hardware Timers Interrupt and exception handling Copyright © 2016 DSR Corporation 4

Embedded Systems Software Training Center HISTORY AND BACKGROUND OF ARM CPUS COPYRIGHT © 2016 DSR CORPORATION

ARM company ARM (Advanced RISC Machine, Acorn RISC Machine) - based on a reduced instruction set computing (RISC) architecture (RISC) developed by British company ARM Holdings. Official site http: //www. arm. com/ The company doesn't produce CPUs and MCUs in silicone. The company only designs CPU cores in Verilog (or VHDL) languages Anyone who wants to build its own ARM So. C should buy core license. After that he is able to construct his own So. C (ASIC, FPGA + peripherals) Copyright © 2016 DSR Corporation 6

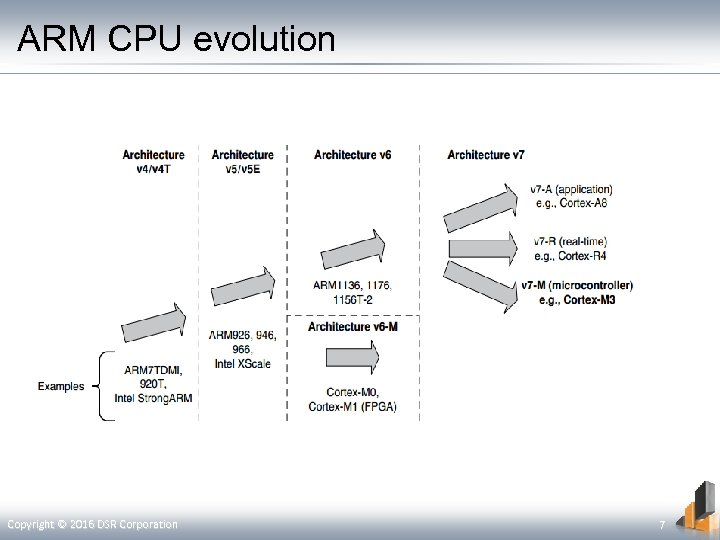

ARM CPU evolution Copyright © 2016 DSR Corporation 7

ARM CPU evolution (part 1) The main (well known in the embedded world) ARM old CPUs are: ARM 7 - for embedded applications (MCU) 30 – 75 MHz, up to 512 k. B Flash, up to 128 k. B RAM No cache, no MMU, 3 -stage pipeline. ARM 9 E - for mobile applications ~ 200 - 400 MHz, cache, MMU, DSP, external Flash and RAM ARM 11– for high-performance applications ~ 700 MHz, MMU, cache, 8 -stage pipeline, DSP, FPU, ext. Flash and RAM l l Copyright © 2016 DSR Corporation 8

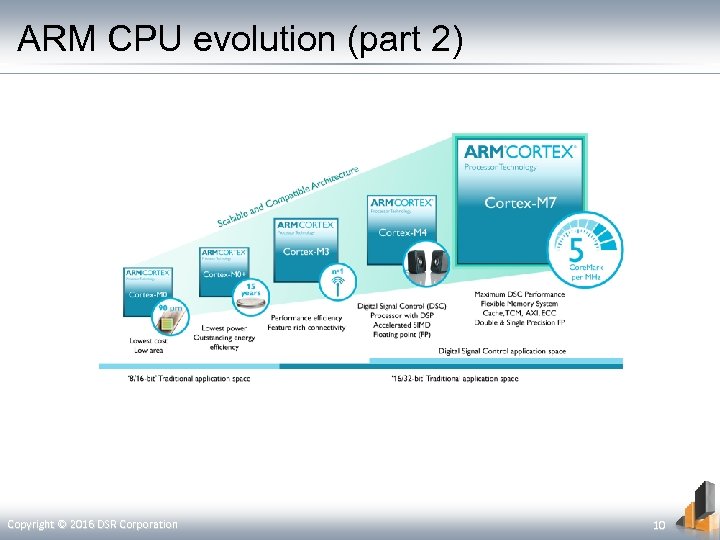

ARM CPU evolution (part 2) After re-branding ARM named their CPUs as Cortex<character>. ARM Cortex-M MCUs (Next generation of ARM 7 and ARM 9) For embedded applications ARM Cortex-R MCUs For hard real-time applications ARM Cortex-A CPUs (Next generation of ARM 11) For high-performance applications l l l Copyright © 2016 DSR Corporation 9

ARM CPU evolution (part 2) Copyright © 2016 DSR Corporation 10

Embedded Systems Software Training Center STM 32 F 4 DISCOVERY KIT COPYRIGHT © 2016 DSR CORPORATION

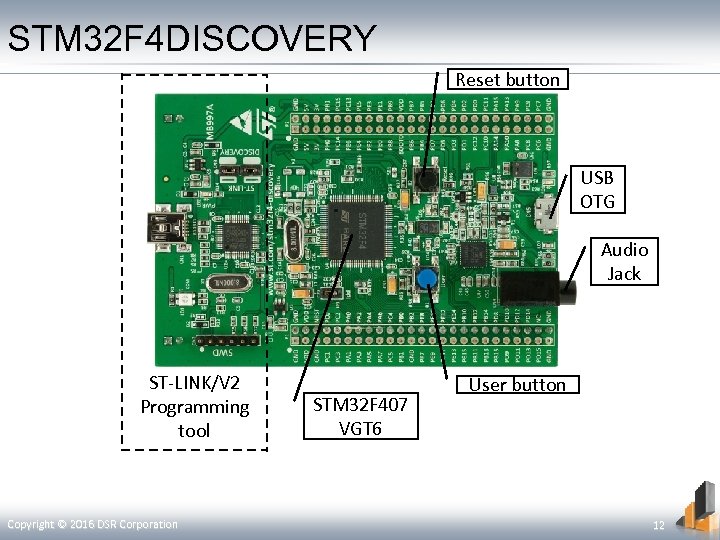

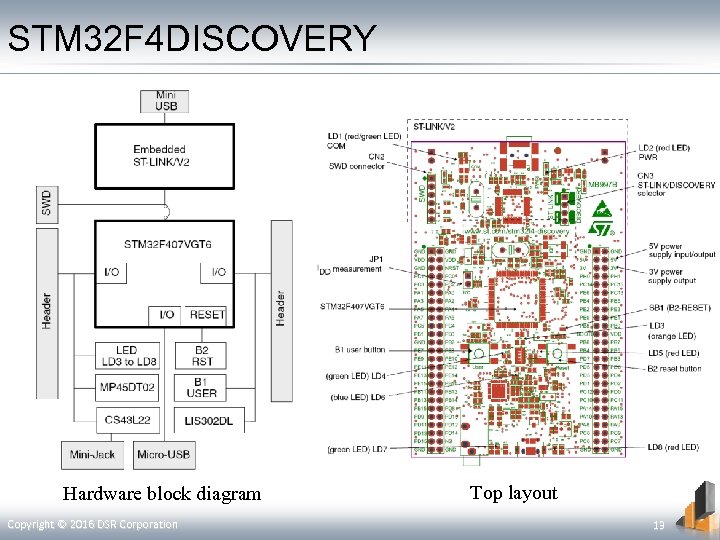

STM 32 F 4 DISCOVERY Reset button USB OTG Audio Jack ST-LINK/V 2 Programming tool Copyright © 2016 DSR Corporation STM 32 F 407 VGT 6 User button 12

STM 32 F 4 DISCOVERY Hardware block diagram Copyright © 2016 DSR Corporation Top layout 13

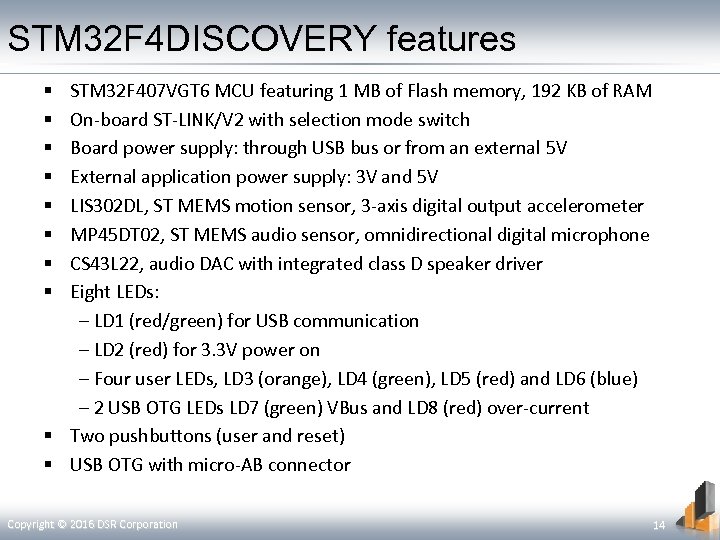

STM 32 F 4 DISCOVERY features STM 32 F 407 VGT 6 MCU featuring 1 MB of Flash memory, 192 KB of RAM On-board ST-LINK/V 2 with selection mode switch Board power supply: through USB bus or from an external 5 V External application power supply: 3 V and 5 V LIS 302 DL, ST MEMS motion sensor, 3 -axis digital output accelerometer MP 45 DT 02, ST MEMS audio sensor, omnidirectional digital microphone CS 43 L 22, audio DAC with integrated class D speaker driver Eight LEDs: – LD 1 (red/green) for USB communication – LD 2 (red) for 3. 3 V power on – Four user LEDs, LD 3 (orange), LD 4 (green), LD 5 (red) and LD 6 (blue) – 2 USB OTG LEDs LD 7 (green) VBus and LD 8 (red) over-current Two pushbuttons (user and reset) USB OTG with micro-AB connector Copyright © 2016 DSR Corporation 14

Useful links: STM 32 F 4 DISCOVERY Product page: http: //www. st. com/web/catalog/tools/FM 116/SC 959/SS 1532/ PF 252419 User manual: http: //www. st. com/st-webui/static/active/en/resource/technical/document/user_manual /DM 00039084. pdf STM 32 F 4 DISCOVERY board firmware package, including 22 examples : http: //www. st. com/st-webui/static/active/en/st_prod_software_internet/resource/techni cal/software/firmware/stsw-stm 32068. zip Copyright © 2016 DSR Corporation 15

Embedded Systems Software Training Center STM 32 F 407 VGT 6 MCU COPYRIGHT © 2016 DSR CORPORATION

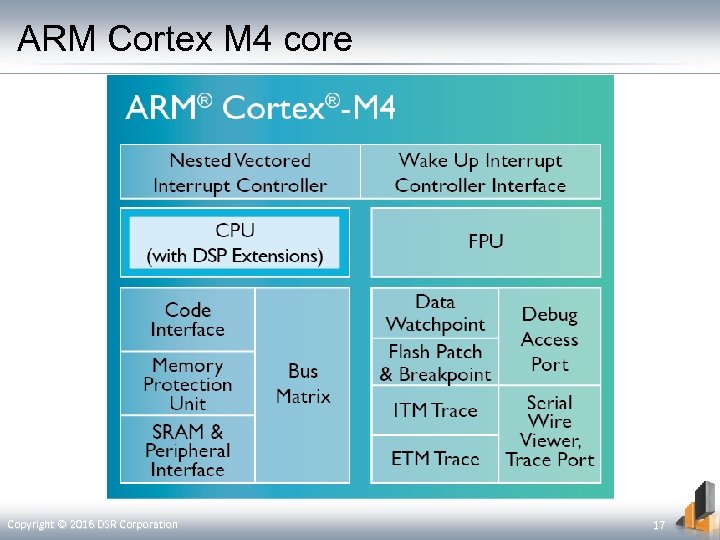

ARM Cortex M 4 core Copyright © 2016 DSR Corporation 17

STM 32 F 407 VGT 6 blocks Copyright © 2016 DSR Corporation 18

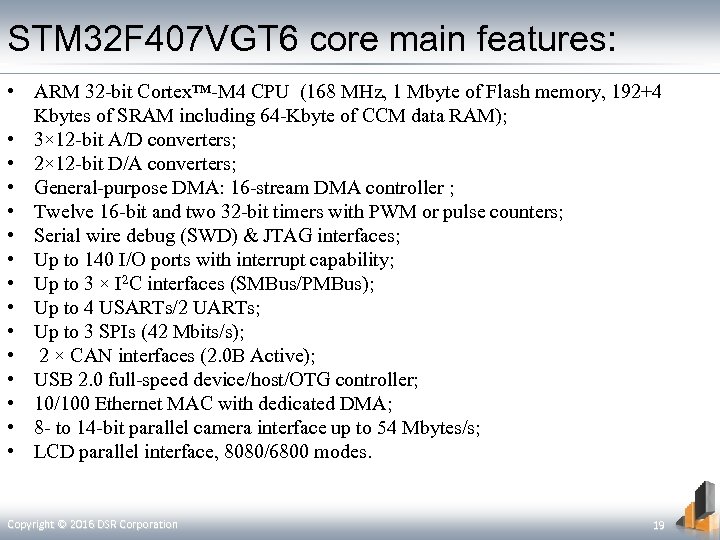

STM 32 F 407 VGT 6 core main features: • ARM 32 -bit Cortex™-M 4 CPU (168 MHz, 1 Mbyte of Flash memory, 192+4 Kbytes of SRAM including 64 -Kbyte of CCM data RAM); • 3× 12 -bit A/D converters; • 2× 12 -bit D/A converters; • General-purpose DMA: 16 -stream DMA controller ; • Twelve 16 -bit and two 32 -bit timers with PWM or pulse counters; • Serial wire debug (SWD) & JTAG interfaces; • Up to 140 I/O ports with interrupt capability; • Up to 3 × I 2 C interfaces (SMBus/PMBus); • Up to 4 USARTs/2 UARTs; • Up to 3 SPIs (42 Mbits/s); • 2 × CAN interfaces (2. 0 B Active); • USB 2. 0 full-speed device/host/OTG controller; • 10/100 Ethernet MAC with dedicated DMA; • 8 - to 14 -bit parallel camera interface up to 54 Mbytes/s; • LCD parallel interface, 8080/6800 modes. Copyright © 2016 DSR Corporation 19

Useful links: STM 32 F 407 VG product page: http: //www. st. com/web/catalog/mmc/FM 141/SC 1169/SS 1577 /LN 11/PF 252140# Reference manual including functional and register description: http: //www. st. com/st-webui/static/active/en/resource/technical/document/reference_manu al/DM 00031020. pdf Other documentation : http: //www. st. com/web/catalog/mmc/FM 141/SC 1169/SS 1577 /LN 11/PF 252140# Copyright © 2016 DSR Corporation 20

Embedded Systems Software Training Center DEVELOPMENT TOOLS AND LIBRARIES COPYRIGHT © 2016 DSR CORPORATION

Popular development tools for Cortex-M 4 • Atmel Studio by Atmel (based on Visual Studio and GNU GCC Toolchain) • Code Composer Studio by Texas Instruments • Co. IDE by Coo. Cox • Eclipse as IDE, with GNU Tools as compiler/linker, e. g. aided with GNU ARM Eclipse Plug-ins • GNU Tools (aka GCC) for ARM Embedded Processors by ARM Ltd - free GCC for bare metal • IAR Embedded Workbench for ARM by IAR • Keil MDK-ARM by Keil • Visual Studio by Microsoft as IDE, with GNU Tools as compiler/linker - e. g. supported by Visual. GDB Copyright © 2016 DSR Corporation 22

STM 32 F 4 libraries • CMSIS – Cortex Microcontroller Interface Standard vendorindependent hardware abstraction layer for the Cortex-M processor series and specifies debugger interfaces. • SPL – Standard Peripheral Library for STM 32 Microcontrollers. Implements Hardware Abstraction Layer for STM 32 peripherals. Often can be downloaded with CMSIS. • STM 32 Cube - Embedded software for STM 32 F 4 series (HAL low level drivers, USB, TCP/IP, File system, RTOS, Graphic - coming with examples running on ST boards). Modern version of STM 32 library from STMicroelectronics. Copyright © 2016 DSR Corporation 23

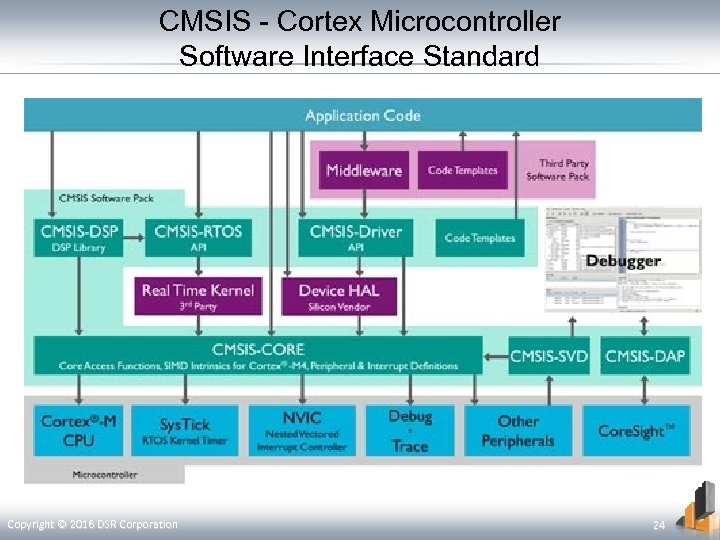

CMSIS - Cortex Microcontroller Software Interface Standard Copyright © 2016 DSR Corporation 24

CMSIS description CMSIS-CORE: API for the Cortex-M processor core and peripherals. It provides at standardized interface for Cortex-M 0, Cortex-M 3, Cortex-M 4, SC 000, and SC 300. CMSIS-DSP: DSP Library Collection CMSIS-RTOS API: Common API for Real-Time operating systems. CMSIS-SVD: System View Description for Peripherals. Describes the peripherals of a device in an XML file and can be used to create peripheral awareness in debuggers or header files with peripheral register and interrupt definitions. CMSIS-DAP: Debug Access Port. Standardized firmware for a Debug Unit that connects to the Core. Sight Debug Access Port. CMSIS-DAP is distributed as separate package and well suited for integration on evaluation boards. This component is provided as separate download. Copyright © 2016 DSR Corporation 25

Embedded Systems Software Training Center PROGRAMMING STM 32 F 407 COPYRIGHT © 2016 DSR CORPORATION

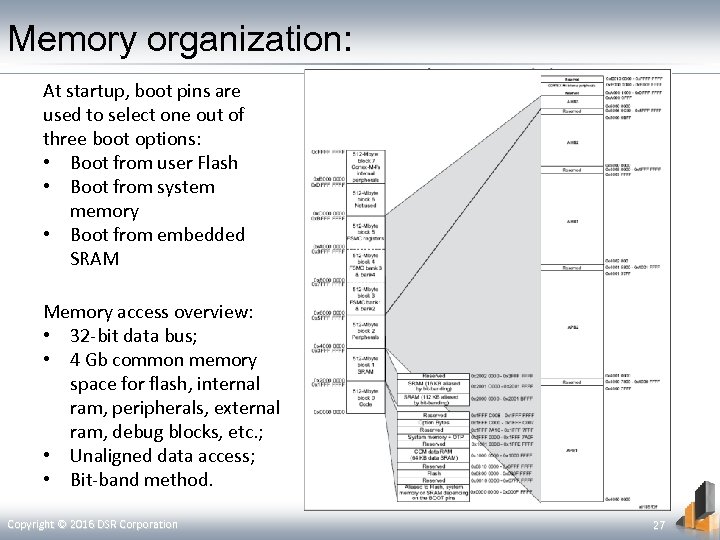

Memory organization: At startup, boot pins are used to select one out of three boot options: • Boot from user Flash • Boot from system memory • Boot from embedded SRAM Memory access overview: • 32 -bit data bus; • 4 Gb common memory space for flash, internal ram, peripherals, external ram, debug blocks, etc. ; • Unaligned data access; • Bit-band method. Copyright © 2016 DSR Corporation 27

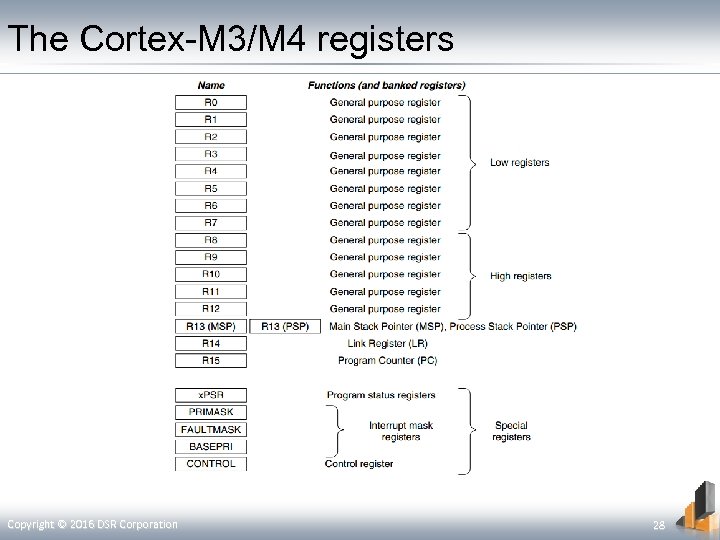

The Cortex-M 3/M 4 registers Copyright © 2016 DSR Corporation 28

Chipset frequency configuration Three different clock sources can be used to drive the system clock (SYSCLK): • HSI oscillator clock signal is generated from an internal 16 MHz RC oscillator and can be used directly as a system clock, or used as PLL input. • HSE oscillator clock signal can be generated from external crystal/ceramic resonator or external user clock • Main PLL (PLL) clock featuring high speed system clock (up to 168 MHz) and clock for the USB OTG FS (48 MHz), the random analog generator (≤ 48 MHz) and the SDIO (≤ 48 MHz). SYSCLK configuration for STM 32 F 4 DISCOVERY board: SYSCLK (system_ stm 32 f 4 xx. h) = PLL_VCO / PLL_P PLL_VCO(system_ stm 32 f 4 xx. h) = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N HSE_VALUE (stm 32 f 4 xx. h) = 8 000 Hz Copyright © 2016 DSR Corporation 29

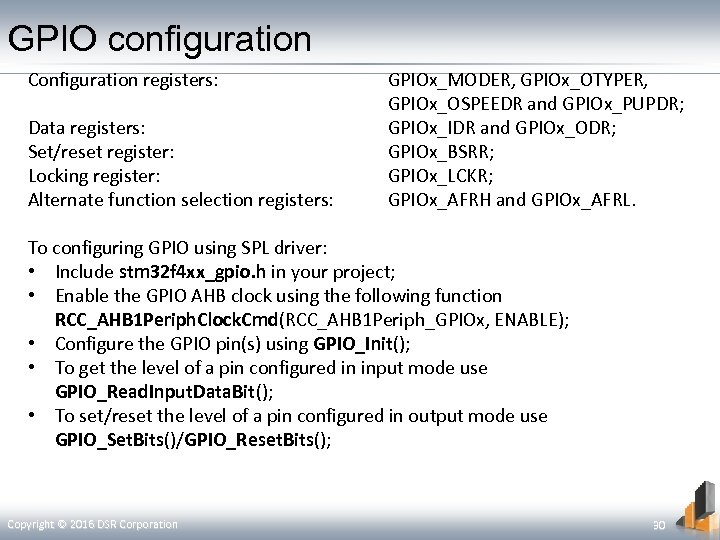

GPIO configuration Configuration registers: Data registers: Set/reset register: Locking register: Alternate function selection registers: GPIOx_MODER, GPIOx_OTYPER, GPIOx_OSPEEDR and GPIOx_PUPDR; GPIOx_IDR and GPIOx_ODR; GPIOx_BSRR; GPIOx_LCKR; GPIOx_AFRH and GPIOx_AFRL. To configuring GPIO using SPL driver: • Include stm 32 f 4 xx_gpio. h in your project; • Enable the GPIO AHB clock using the following function RCC_AHB 1 Periph. Clock. Cmd(RCC_AHB 1 Periph_GPIOx, ENABLE); • Configure the GPIO pin(s) using GPIO_Init(); • To get the level of a pin configured in input mode use GPIO_Read. Input. Data. Bit(); • To set/reset the level of a pin configured in output mode use GPIO_Set. Bits()/GPIO_Reset. Bits(); Copyright © 2016 DSR Corporation 30

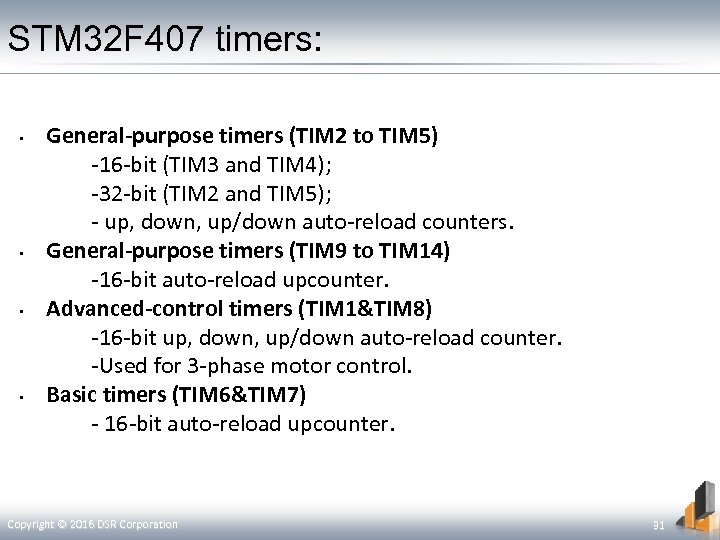

STM 32 F 407 timers: General-purpose timers (TIM 2 to TIM 5) -16 -bit (TIM 3 and TIM 4); -32 -bit (TIM 2 and TIM 5); - up, down, up/down auto-reload counters. • General-purpose timers (TIM 9 to TIM 14) -16 -bit auto-reload upcounter. • Advanced-control timers (TIM 1&TIM 8) -16 -bit up, down, up/down auto-reload counter. -Used for 3 -phase motor control. • Basic timers (TIM 6&TIM 7) - 16 -bit auto-reload upcounter. • Copyright © 2016 DSR Corporation 31

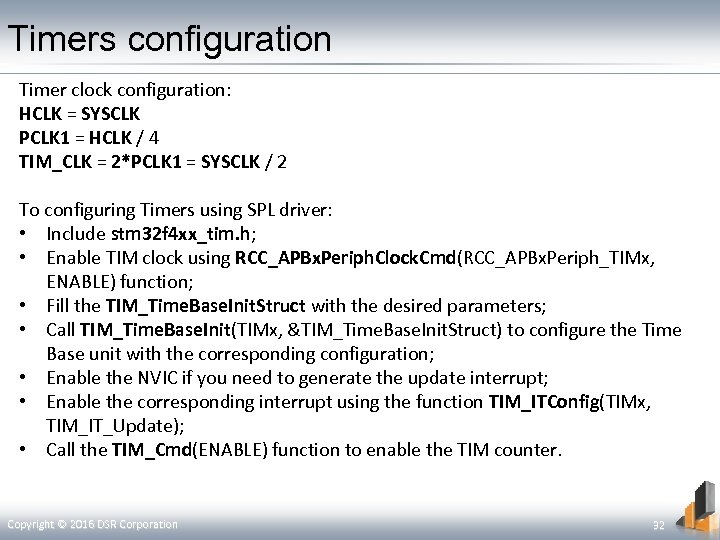

Timers configuration Timer clock configuration: HCLK = SYSCLK PCLK 1 = HCLK / 4 TIM_CLK = 2*PCLK 1 = SYSCLK / 2 To configuring Timers using SPL driver: • Include stm 32 f 4 xx_tim. h; • Enable TIM clock using RCC_APBx. Periph. Clock. Cmd(RCC_APBx. Periph_TIMx, ENABLE) function; • Fill the TIM_Time. Base. Init. Struct with the desired parameters; • Call TIM_Time. Base. Init(TIMx, &TIM_Time. Base. Init. Struct) to configure the Time Base unit with the corresponding configuration; • Enable the NVIC if you need to generate the update interrupt; • Enable the corresponding interrupt using the function TIM_ITConfig(TIMx, TIM_IT_Update); • Call the TIM_Cmd(ENABLE) function to enable the TIM counter. Copyright © 2016 DSR Corporation 32

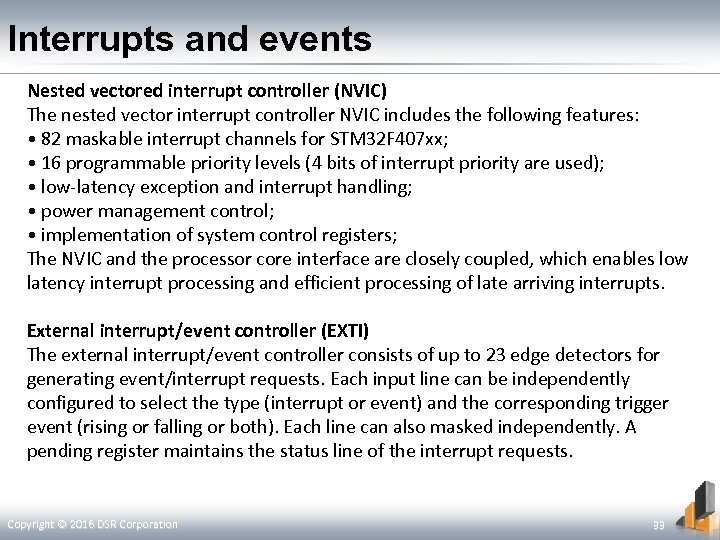

Interrupts and events Nested vectored interrupt controller (NVIC) The nested vector interrupt controller NVIC includes the following features: • 82 maskable interrupt channels for STM 32 F 407 xx; • 16 programmable priority levels (4 bits of interrupt priority are used); • low-latency exception and interrupt handling; • power management control; • implementation of system control registers; The NVIC and the processor core interface are closely coupled, which enables low latency interrupt processing and efficient processing of late arriving interrupts. External interrupt/event controller (EXTI) The external interrupt/event controller consists of up to 23 edge detectors for generating event/interrupt requests. Each input line can be independently configured to select the type (interrupt or event) and the corresponding trigger event (rising or falling or both). Each line can also masked independently. A pending register maintains the status line of the interrupt requests. Copyright © 2016 DSR Corporation 33

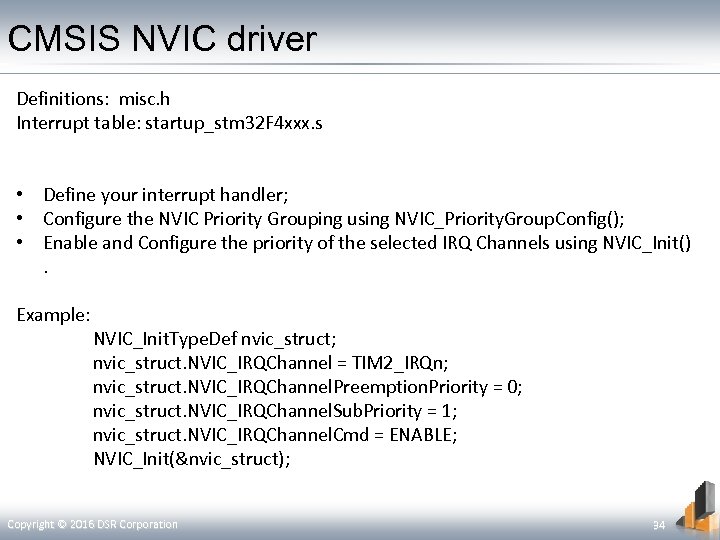

CMSIS NVIC driver Definitions: misc. h Interrupt table: startup_stm 32 F 4 xxx. s • Define your interrupt handler; • Configure the NVIC Priority Grouping using NVIC_Priority. Group. Config(); • Enable and Configure the priority of the selected IRQ Channels using NVIC_Init() . Example: NVIC_Init. Type. Def nvic_struct; nvic_struct. NVIC_IRQChannel = TIM 2_IRQn; nvic_struct. NVIC_IRQChannel. Preemption. Priority = 0; nvic_struct. NVIC_IRQChannel. Sub. Priority = 1; nvic_struct. NVIC_IRQChannel. Cmd = ENABLE; NVIC_Init(&nvic_struct); Copyright © 2016 DSR Corporation 34

Is there any questions? Copyright © 2016 DSR Corporation 35

Embedded Systems Software Training Center THANK YOU! COPYRIGHT © 2016 DSR CORPORATION

23eb5e7cbec5fea9b7270abe7353ccfc.ppt