0cb513a2d605aeae53bdfa4187ba1a43.ppt

- Количество слайдов: 42

Embedded Systems in Silicon TD 5102 Other Architectures Henk Corporaal http: //www. ics. ele. tue. nl/~heco/courses/Emb. Systems ACA 2003 Technical University Eindhoven DTI / NUS Singapore 2005/2006

Introduction n Design alternatives: u provide more powerful operations F F u goal is to reduce number of instructions executed danger is a slower cycle time and/or a higher CPI provide even simpler operations F n to reduce code size / complexity interpreter Sometimes referred to as “RISC vs. CISC” u u n ACA 2003 virtually all new instruction sets since 1982 have been RISC VAX: minimize code size, make assembly language easy instructions from 1 to 54 bytes long! We’ll look at IA-32 and Java Virtual Machine 2

Topics n Recap of MIPS architecture u Why n RISC? Other architecture styles u Accumulator architecture u Stack architecture u Memory-Memory architecture u Register architectures n Examples u 80 x 86 u Pentium Pro, III, 4 u JVM ACA 2003 3

Recap of MIPS n n n ACA 2003 RISC architecture Register space Addressing Instruction format Pipelining 4

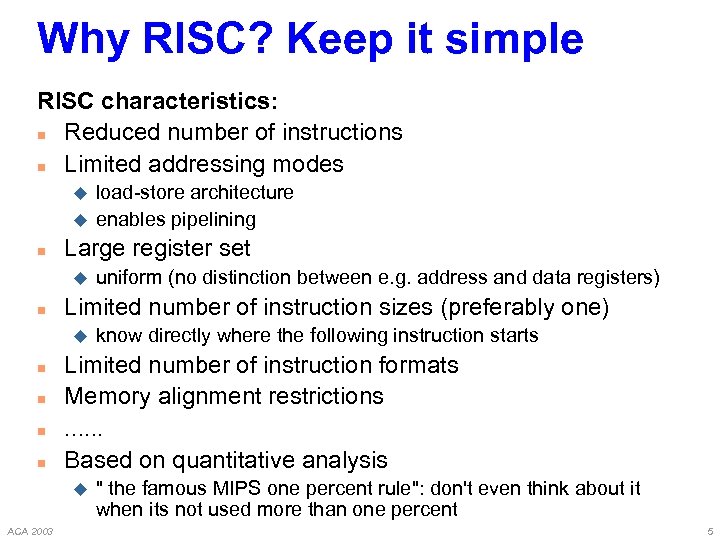

Why RISC? Keep it simple RISC characteristics: n Reduced number of instructions n Limited addressing modes u u n Large register set u n n know directly where the following instruction starts Limited number of instruction formats Memory alignment restrictions. . . Based on quantitative analysis u ACA 2003 uniform (no distinction between e. g. address and data registers) Limited number of instruction sizes (preferably one) u n load-store architecture enables pipelining " the famous MIPS one percent rule": don't even think about it when its not used more than one percent 5

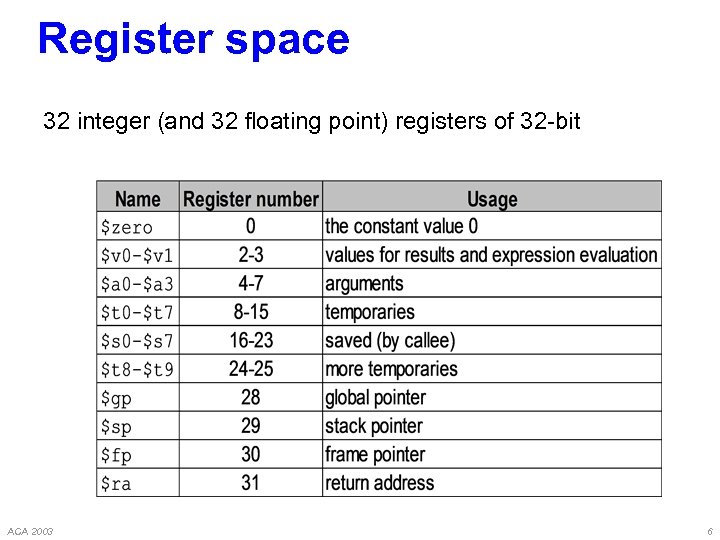

Register space 32 integer (and 32 floating point) registers of 32 -bit ACA 2003 6

Addressing ACA 2003 7

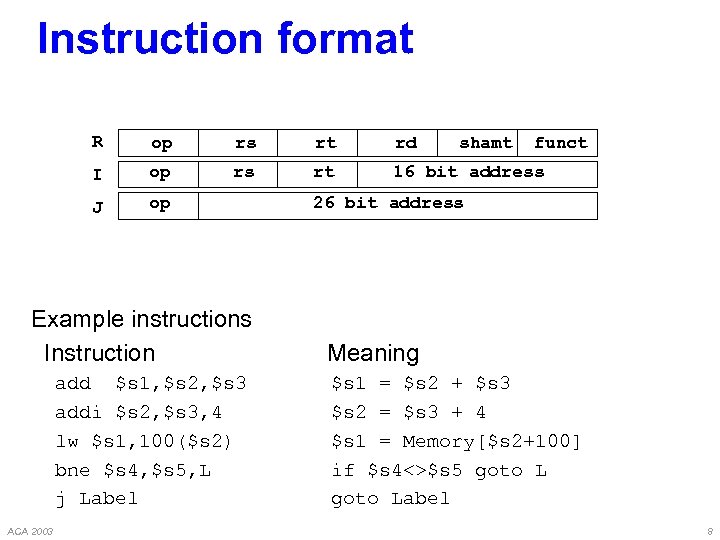

Instruction format R op rs rt rd I op rs rt 16 bit address J op Example instructions Instruction add $s 1, $s 2, $s 3 addi $s 2, $s 3, 4 lw $s 1, 100($s 2) bne $s 4, $s 5, L j Label ACA 2003 shamt funct 26 bit address Meaning $s 1 = $s 2 + $s 3 $s 2 = $s 3 + 4 $s 1 = Memory[$s 2+100] if $s 4<>$s 5 goto Label 8

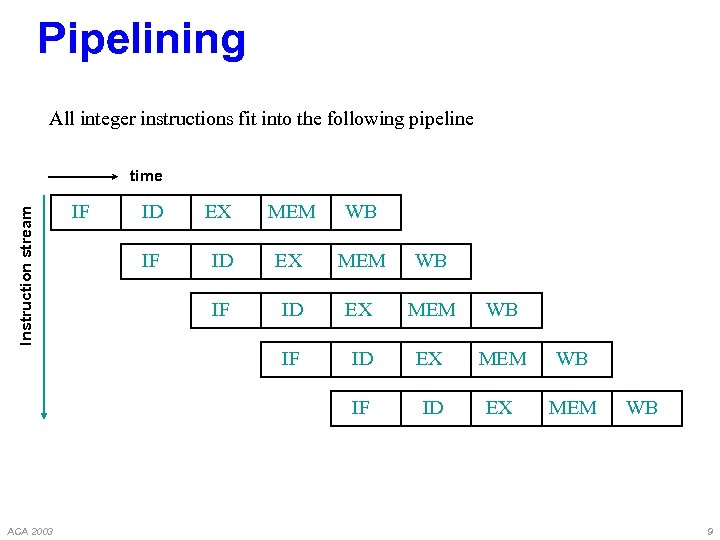

Pipelining All integer instructions fit into the following pipeline time EX MEM WB IF ID EX MEM WB IF Instruction stream ID IF ACA 2003 IF ID EX MEM WB 9

Other architecture styles n n n ACA 2003 Accumulator architecture Stack Register (load store) Register-Memory-Memory 10

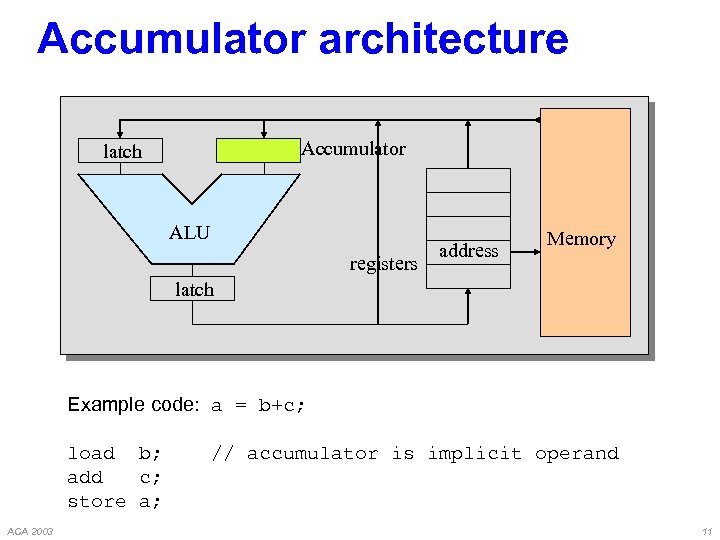

Accumulator architecture Accumulator latch ALU registers address Memory latch Example code: a = b+c; load b; add c; store a; ACA 2003 // accumulator is implicit operand 11

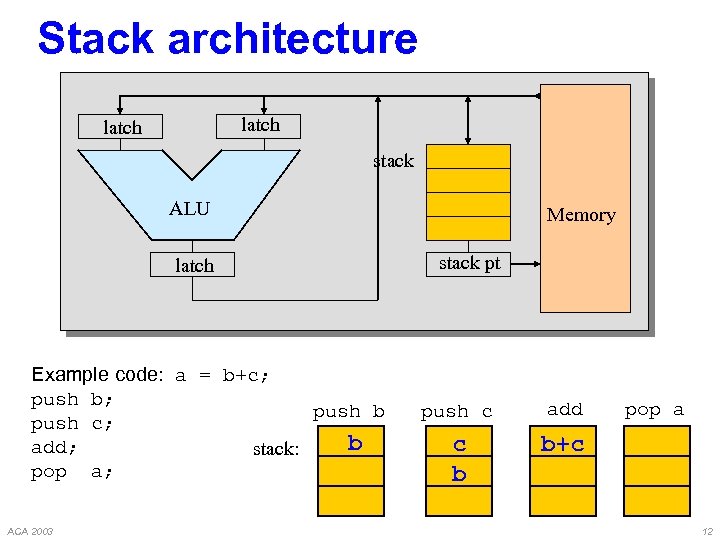

Stack architecture latch stack ALU latch Example code: a = b+c; push b push c; b add; stack: pop a; ACA 2003 Memory stack pt push c add c b pop a b+c 12

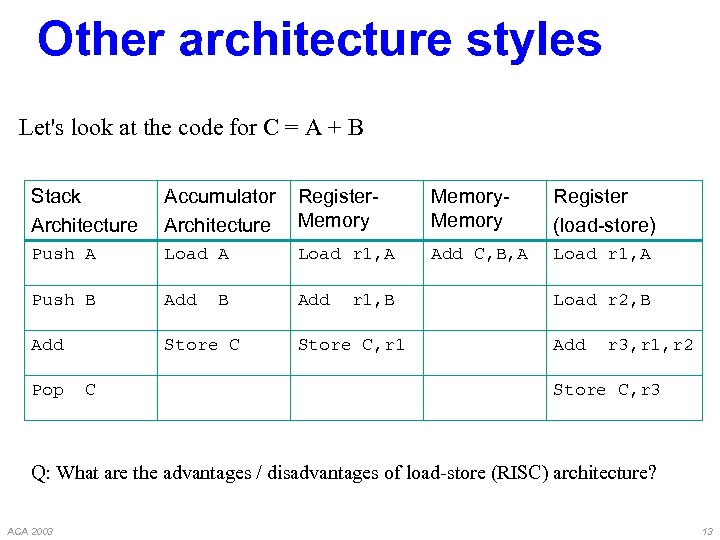

Other architecture styles Let's look at the code for C = A + B Stack Architecture Accumulator Architecture Register. Memory Register (load-store) Push A Load r 1, A Add C, B, A Load r 1, A Push B Add Add Store C Pop C B r 1, B Store C, r 1 Load r 2, B Add r 3, r 1, r 2 Store C, r 3 Q: What are the advantages / disadvantages of load-store (RISC) architecture? ACA 2003 13

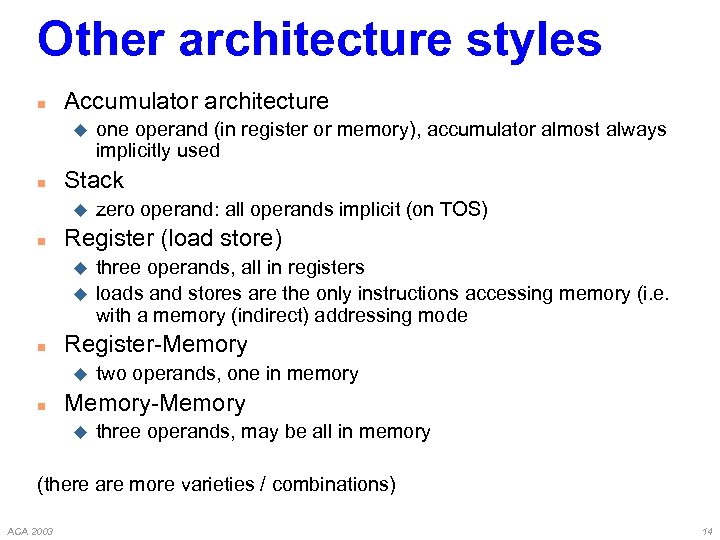

Other architecture styles n Accumulator architecture u n Stack u n u three operands, all in registers loads and stores are the only instructions accessing memory (i. e. with a memory (indirect) addressing mode Register-Memory u n zero operand: all operands implicit (on TOS) Register (load store) u n one operand (in register or memory), accumulator almost always implicitly used two operands, one in memory Memory-Memory u three operands, may be all in memory (there are more varieties / combinations) ACA 2003 14

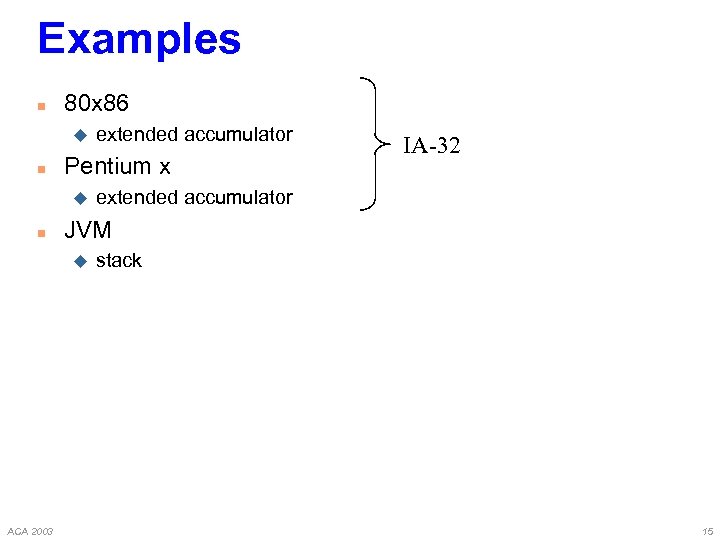

Examples n 80 x 86 u n Pentium x u n IA-32 extended accumulator JVM u ACA 2003 extended accumulator stack 15

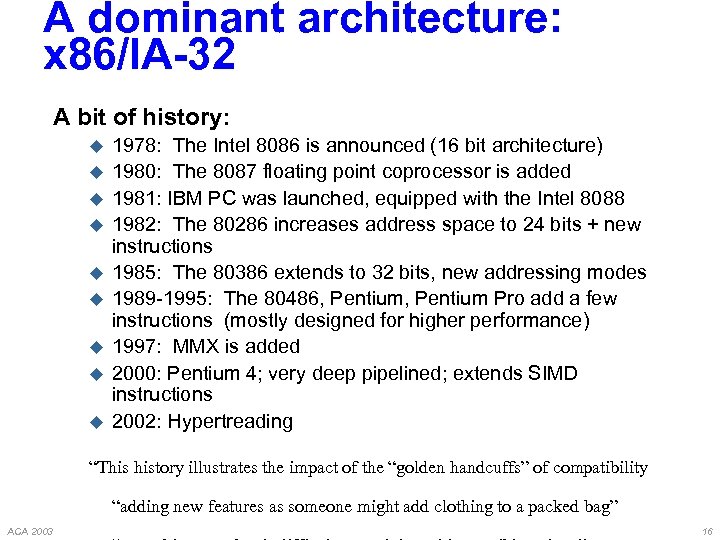

A dominant architecture: x 86/IA-32 A bit of history: u u u u u 1978: The Intel 8086 is announced (16 bit architecture) 1980: The 8087 floating point coprocessor is added 1981: IBM PC was launched, equipped with the Intel 8088 1982: The 80286 increases address space to 24 bits + new instructions 1985: The 80386 extends to 32 bits, new addressing modes 1989 -1995: The 80486, Pentium Pro add a few instructions (mostly designed for higher performance) 1997: MMX is added 2000: Pentium 4; very deep pipelined; extends SIMD instructions 2002: Hypertreading “This history illustrates the impact of the “golden handcuffs” of compatibility “adding new features as someone might add clothing to a packed bag” ACA 2003 16

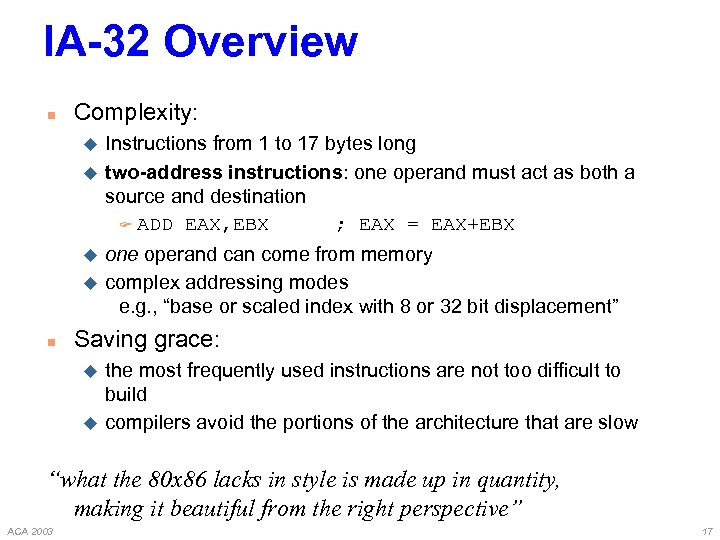

IA-32 Overview n Complexity: u u n Instructions from 1 to 17 bytes long two-address instructions: one operand must act as both a source and destination F ADD EAX, EBX ; EAX = EAX+EBX one operand can come from memory complex addressing modes e. g. , “base or scaled index with 8 or 32 bit displacement” Saving grace: u u the most frequently used instructions are not too difficult to build compilers avoid the portions of the architecture that are slow “what the 80 x 86 lacks in style is made up in quantity, making it beautiful from the right perspective” ACA 2003 17

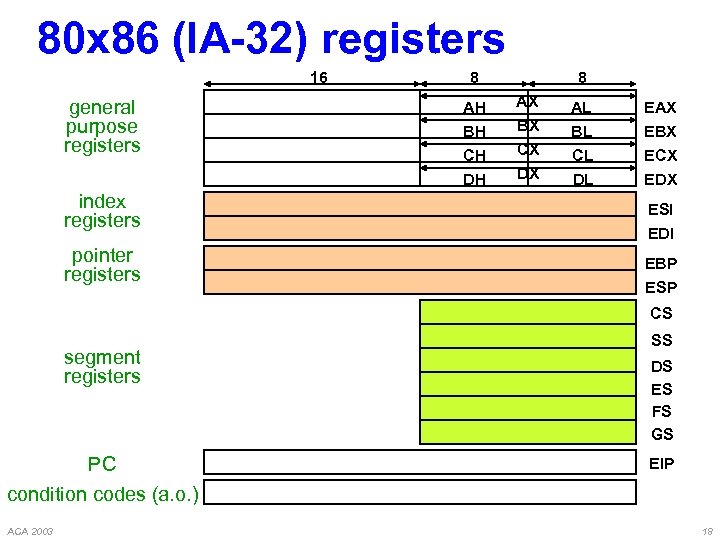

80 x 86 (IA-32) registers 16 general purpose registers index registers pointer registers 8 8 AH BH AX BX AL BL EAX EBX CH DH CX DX CL DL ECX EDX ESI EDI EBP ESP CS segment registers PC condition codes (a. o. ) ACA 2003 SS DS ES FS GS EIP 18

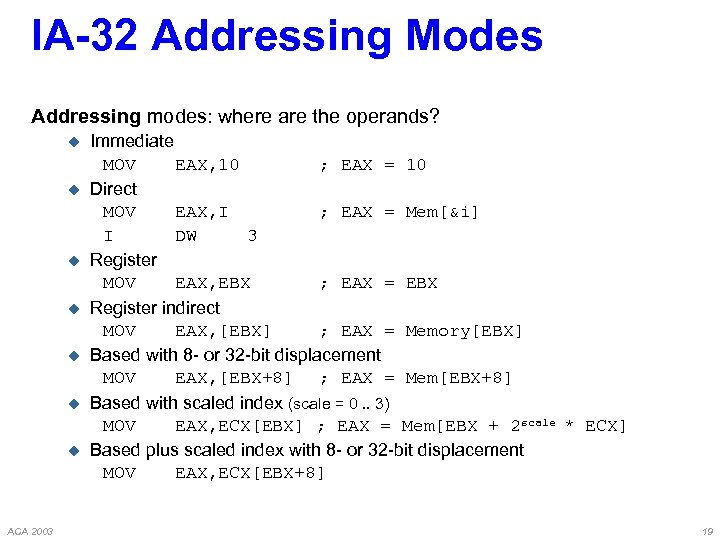

IA-32 Addressing Modes Addressing modes: where are the operands? u u u u ACA 2003 Immediate MOV EAX, 10 ; EAX = 10 Direct MOV EAX, I ; EAX = Mem[&i] I DW 3 Register MOV EAX, EBX ; EAX = EBX Register indirect MOV EAX, [EBX] ; EAX = Memory[EBX] Based with 8 - or 32 -bit displacement MOV EAX, [EBX+8] ; EAX = Mem[EBX+8] Based with scaled index (scale = 0. . 3) MOV EAX, ECX[EBX] ; EAX = Mem[EBX + 2 scale * ECX] Based plus scaled index with 8 - or 32 -bit displacement MOV EAX, ECX[EBX+8] 19

IA-32 Addressing Modes n Not all modes apply to all instructions u n n ACA 2003 one of the operands must be a register Not all registers can be used in all modes Why? Simply not enough bits in the instruction 20

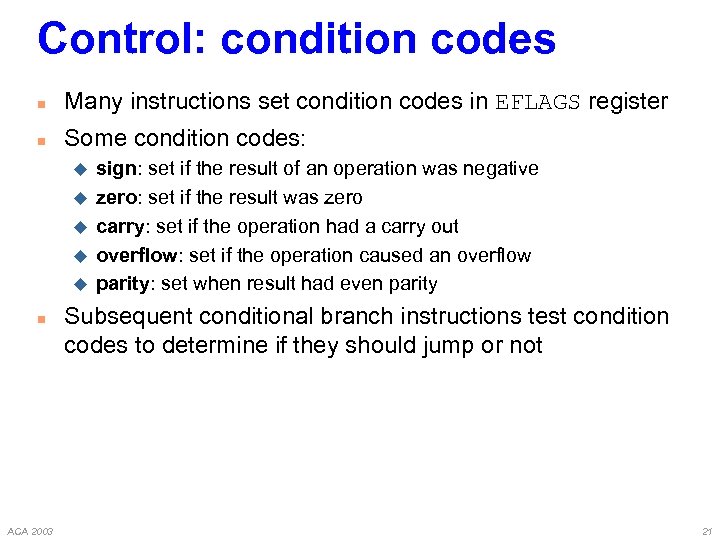

Control: condition codes n Many instructions set condition codes in EFLAGS register n Some condition codes: u u u n ACA 2003 sign: set if the result of an operation was negative zero: set if the result was zero carry: set if the operation had a carry out overflow: set if the operation caused an overflow parity: set when result had even parity Subsequent conditional branch instructions test condition codes to determine if they should jump or not 21

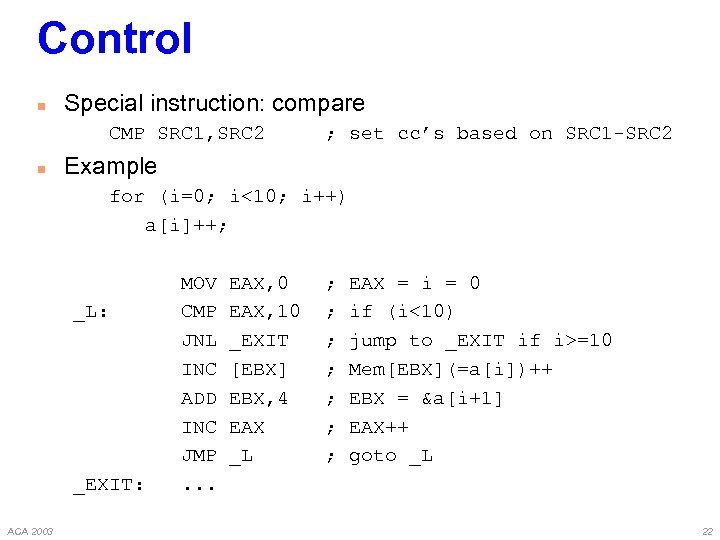

Control n Special instruction: compare CMP SRC 1, SRC 2 n ; set cc’s based on SRC 1 -SRC 2 Example for (i=0; i<10; i++) a[i]++; _L: _EXIT: ACA 2003 MOV CMP JNL INC ADD INC JMP. . . EAX, 0 EAX, 10 _EXIT [EBX] EBX, 4 EAX _L ; ; ; ; EAX = i = 0 if (i<10) jump to _EXIT if i>=10 Mem[EBX](=a[i])++ EBX = &a[i+1] EAX++ goto _L 22

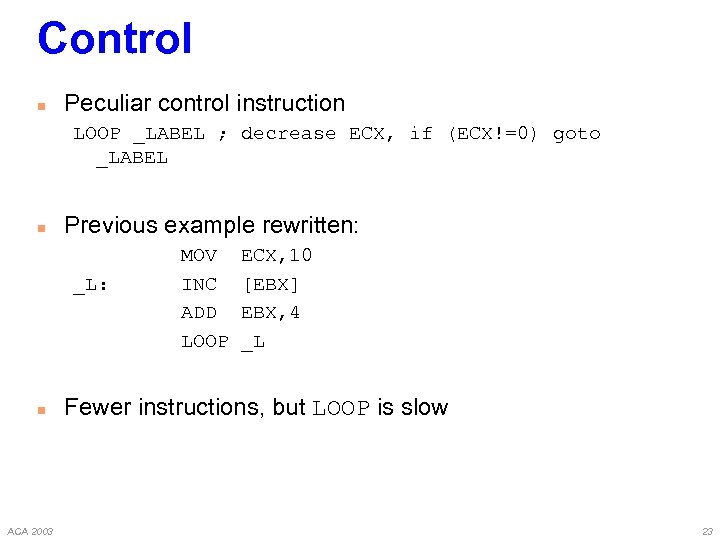

Control n Peculiar control instruction LOOP _LABEL ; decrease ECX, if (ECX!=0) goto _LABEL n Previous example rewritten: _L: n ACA 2003 MOV INC ADD LOOP ECX, 10 [EBX] EBX, 4 _L Fewer instructions, but LOOP is slow 23

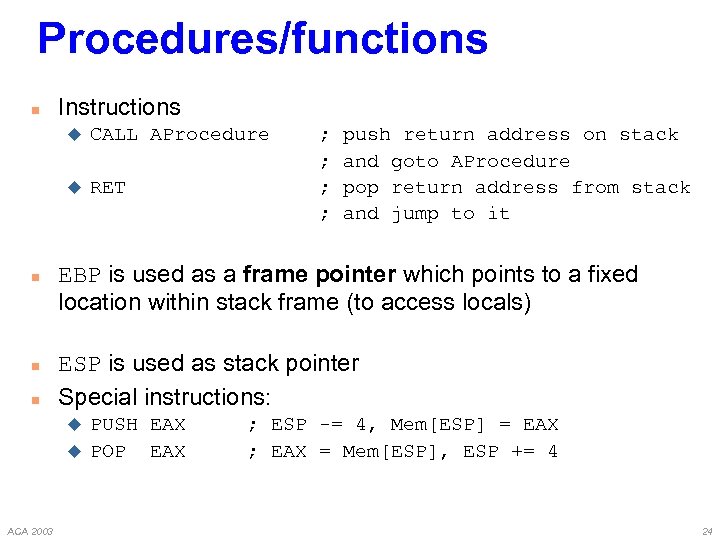

Procedures/functions n Instructions u u n n n CALL AProcedure RET push return address on stack and goto AProcedure pop return address from stack and jump to it EBP is used as a frame pointer which points to a fixed location within stack frame (to access locals) ESP is used as stack pointer Special instructions: u u ACA 2003 ; ; PUSH EAX POP EAX ; ESP -= 4, Mem[ESP] = EAX ; EAX = Mem[ESP], ESP += 4 24

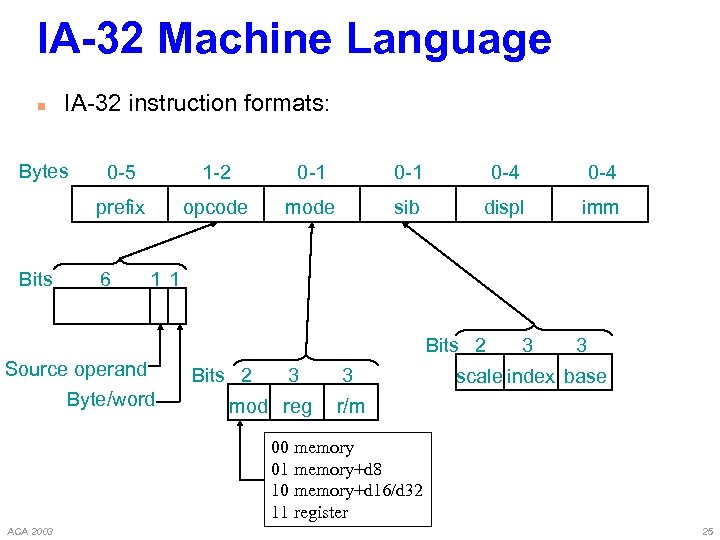

IA-32 Machine Language n IA-32 instruction formats: Bytes 1 -2 0 -1 0 -4 prefix Bits 0 -5 opcode mode sib displ imm 6 1 1 Bits 2 Source operand Byte/word Bits 2 3 mod reg 3 3 3 scale index base r/m 00 memory 01 memory+d 8 10 memory+d 16/d 32 11 register ACA 2003 25

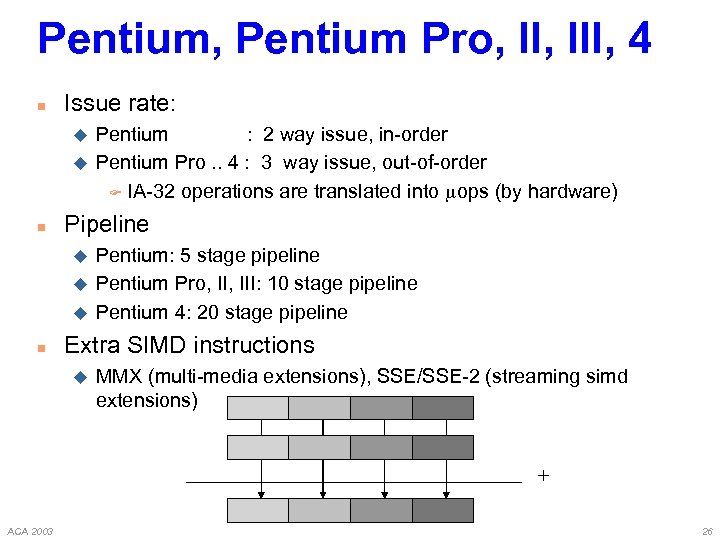

Pentium, Pentium Pro, III, 4 n Issue rate: u u n Pipeline u u u n Pentium : 2 way issue, in-order Pentium Pro. . 4 : 3 way issue, out-of-order F IA-32 operations are translated into ops (by hardware) Pentium: 5 stage pipeline Pentium Pro, III: 10 stage pipeline Pentium 4: 20 stage pipeline Extra SIMD instructions u MMX (multi-media extensions), SSE/SSE-2 (streaming simd extensions) + ACA 2003 26

Die example: Pentium 4 ACA 2003 27

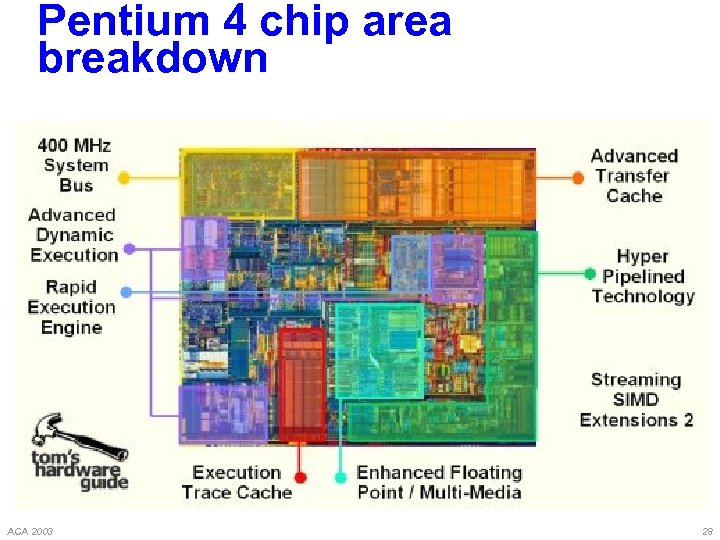

Pentium 4 chip area breakdown ACA 2003 28

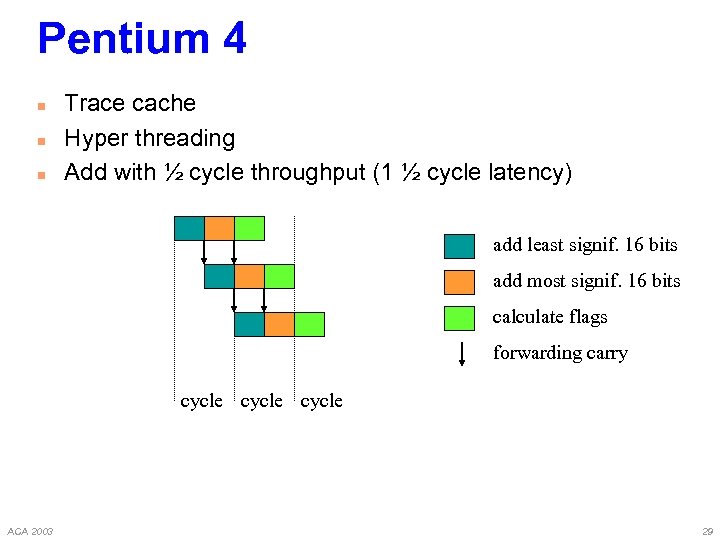

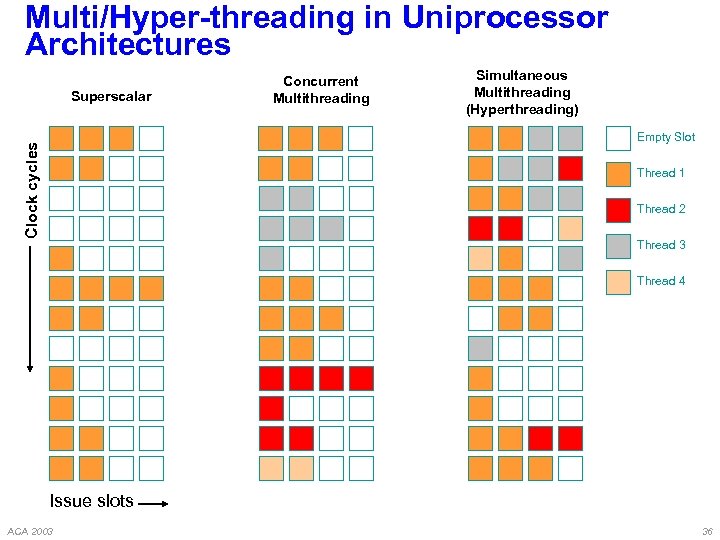

Pentium 4 n n n Trace cache Hyper threading Add with ½ cycle throughput (1 ½ cycle latency) add least signif. 16 bits add most signif. 16 bits calculate flags forwarding carry cycle ACA 2003 29

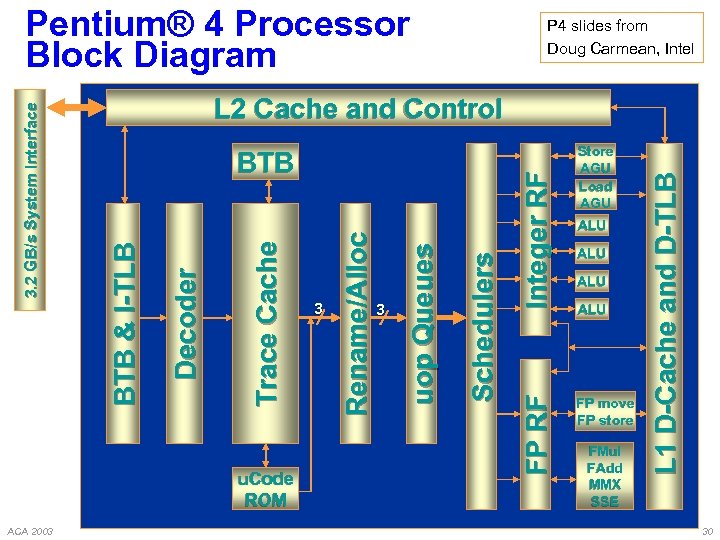

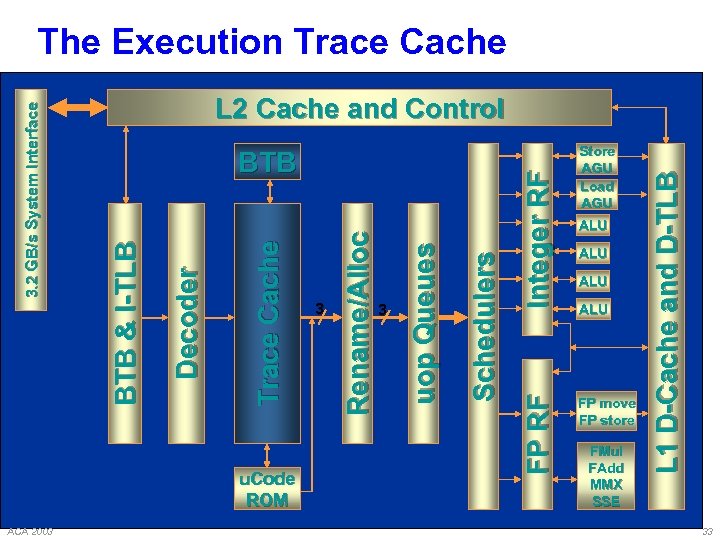

Store AGU Load AGU ALU ALU FP move FP store FMul FAdd MMX SSE L 1 D-Cache and D-TLB Integer RF FP RF Schedulers 3 uop Queues 3 Rename/Alloc Trace Cache Decoder BTB u. Code ROM ACA 2003 P 4 slides from Doug Carmean, Intel L 2 Cache and Control BTB & I-TLB 3. 2 GB/s System Interface Pentium® 4 Processor Block Diagram 30

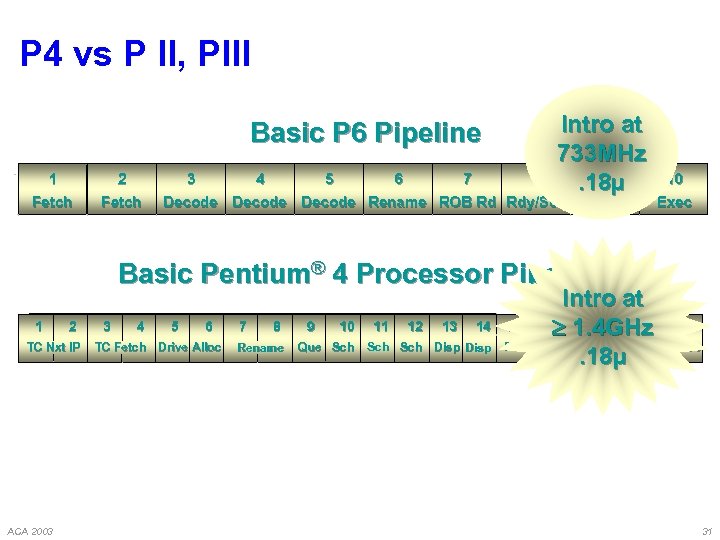

P 4 vs P II, PIII Intro at 733 MHz 9. 18µ Basic P 6 Pipeline 1 Fetch 2 Fetch 3 4 5 6 7 8 Decode Rename ROB Rd Rdy/Sch Dispatch 10 Exec Basic Pentium® 4 Processor Pipeline 1 2 TC Nxt IP ACA 2003 3 4 5 6 TC Fetch Drive Alloc 7 8 Rename 9 10 Que Sch 11 12 13 14 15 Sch Disp RF Intro at 16³ 17 18 19 20 1. 4 GHz RF Ex Flgs Br Ck Drive. 18µ 31

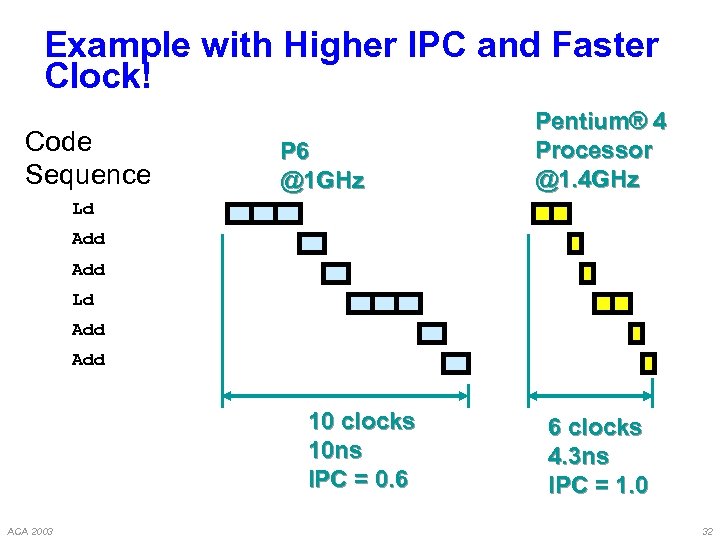

Example with Higher IPC and Faster Clock! Code Sequence P 6 @1 GHz Pentium® 4 Processor @1. 4 GHz Ld Add Add 10 clocks 10 ns IPC = 0. 6 ACA 2003 6 clocks 4. 3 ns IPC = 1. 0 32

ACA 2003 Store AGU Load AGU ALU ALU FP move FP store FMul FAdd MMX SSE L 1 D-Cache and D-TLB Schedulers uop Queues 3 FP RF u. Code ROM 3 Rename/Alloc Trace Cache Decoder BTB Integer RF L 2 Cache and Control BTB & I-TLB 3. 2 GB/s System Interface The Execution Trace Cache 33

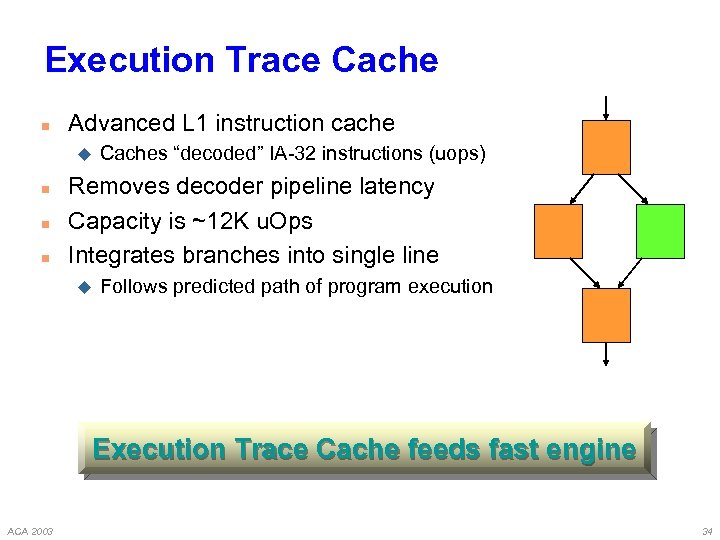

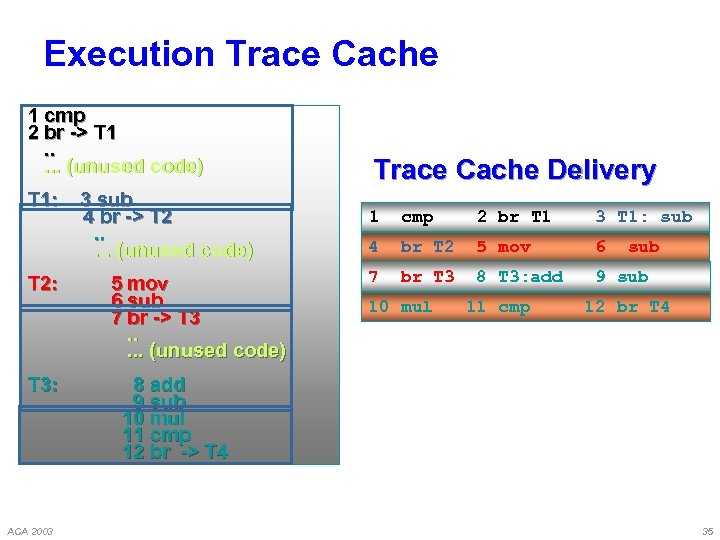

Execution Trace Cache n Advanced L 1 instruction cache u n n n Caches “decoded” IA-32 instructions (uops) Removes decoder pipeline latency Capacity is ~12 K u. Ops Integrates branches into single line u Follows predicted path of program execution Execution Trace Cache feeds fast engine ACA 2003 34

Execution Trace Cache 1 cmp 2 br -> T 1. . . (unused code) T 1: T 2: T 3: ACA 2003 3 sub 4 br -> T 2. . . (unused code) 5 mov 6 sub 7 br -> T 3. . . (unused code) Trace Cache Delivery 1 cmp 2 br T 1 3 T 1: sub 4 br T 2 5 mov 6 7 br T 3 8 T 3: add 9 sub 10 mul 11 cmp sub 12 br T 4 8 add 9 sub 10 mul 11 cmp 12 br -> T 4 35

Multi/Hyper-threading in Uniprocessor Architectures Superscalar Concurrent Multithreading Simultaneous Multithreading (Hyperthreading) Clock cycles Empty Slot Thread 1 Thread 2 Thread 3 Thread 4 Issue slots ACA 2003 36

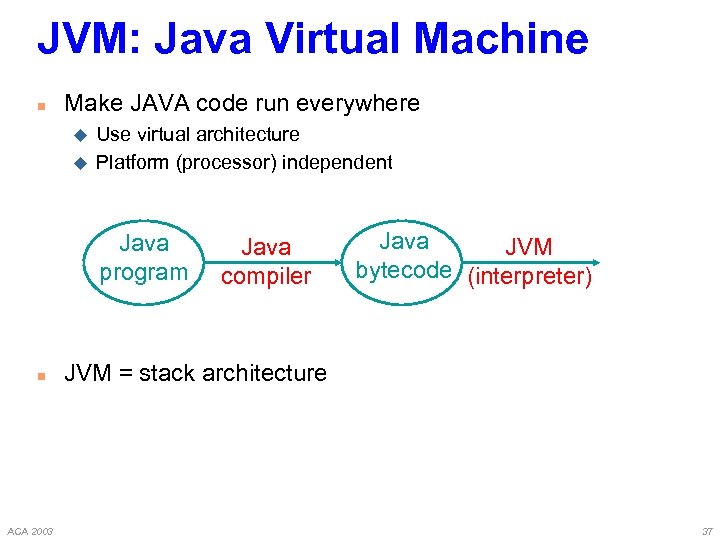

JVM: Java Virtual Machine n Make JAVA code run everywhere u u Use virtual architecture Platform (processor) independent Java program n ACA 2003 Java compiler Java JVM bytecode (interpreter) JVM = stack architecture 37

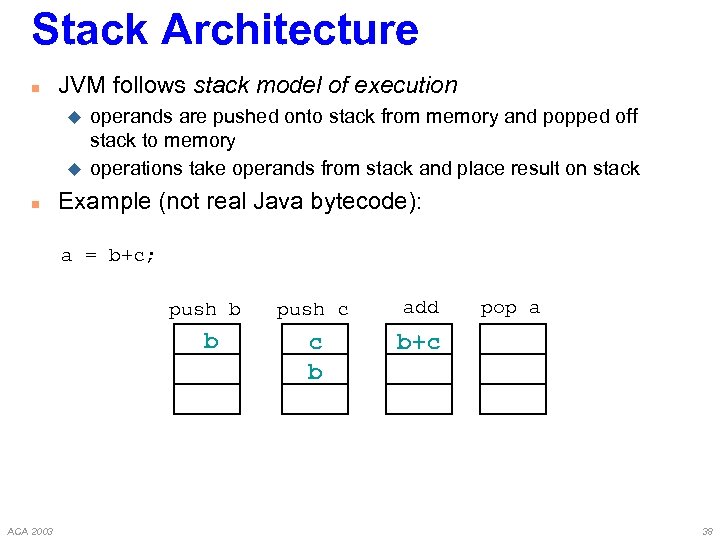

Stack Architecture n JVM follows stack model of execution u u n operands are pushed onto stack from memory and popped off stack to memory operations take operands from stack and place result on stack Example (not real Java bytecode): a = b+c; push b add b ACA 2003 push c c b pop a b+c 38

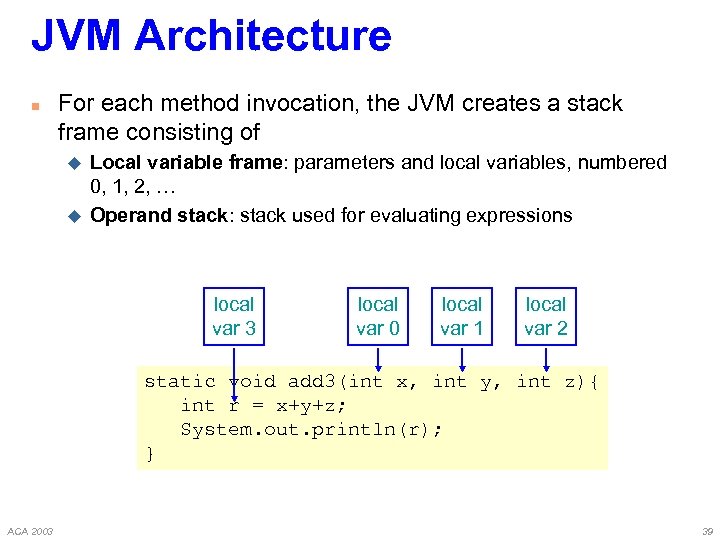

JVM Architecture n For each method invocation, the JVM creates a stack frame consisting of u u Local variable frame: parameters and local variables, numbered 0, 1, 2, … Operand stack: stack used for evaluating expressions local var 3 local var 0 local var 1 local var 2 static void add 3(int x, int y, int z){ int r = x+y+z; System. out. println(r); } ACA 2003 39

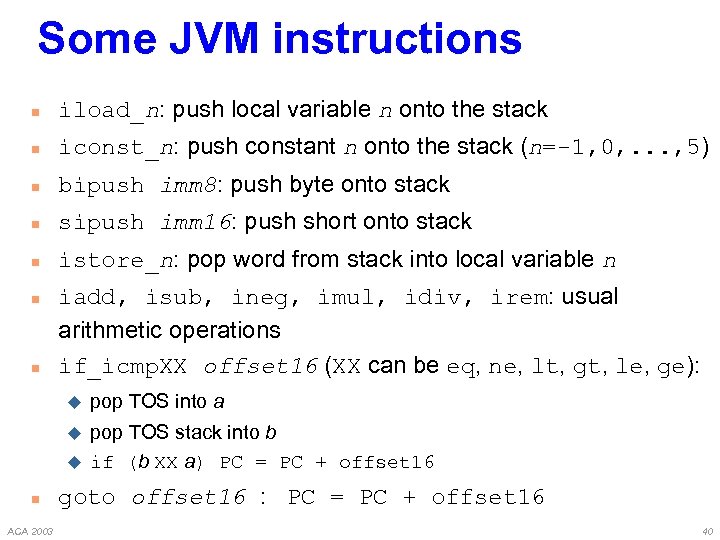

Some JVM instructions n iload_n: push local variable n onto the stack n iconst_n: push constant n onto the stack (n=-1, 0, . . . , 5) n bipush imm 8: push byte onto stack n sipush imm 16: push short onto stack n istore_n: pop word from stack into local variable n n n iadd, isub, ineg, imul, idiv, irem: usual arithmetic operations if_icmp. XX offset 16 (XX can be eq, ne, lt, gt, le, ge): u pop TOS into a u pop TOS stack into b if (b XX a) PC = PC + offset 16 u n ACA 2003 goto offset 16 : PC = PC + offset 16 40

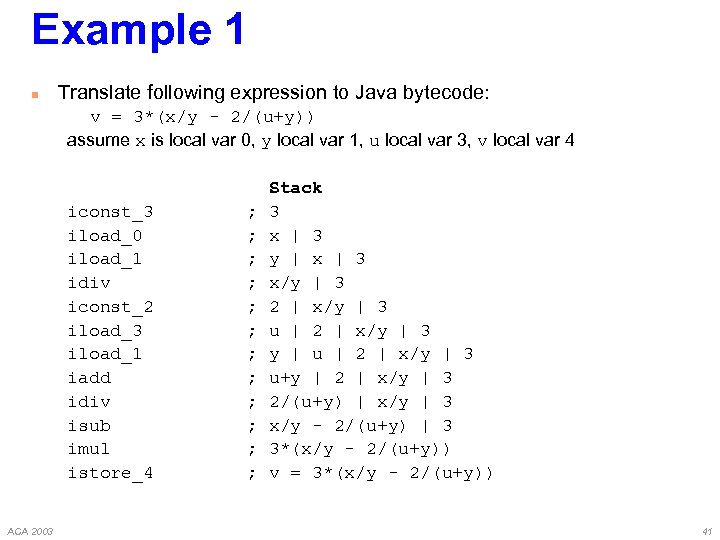

Example 1 n Translate following expression to Java bytecode: v = 3*(x/y - 2/(u+y)) assume x is local var 0, y local var 1, u local var 3, v local var 4 iconst_3 iload_0 iload_1 idiv iconst_2 iload_3 iload_1 iadd idiv isub imul istore_4 ACA 2003 ; ; ; Stack 3 x | 3 y | x | 3 x/y | 3 2 | x/y | 3 u | 2 | x/y | 3 y | u | 2 | x/y | 3 u+y | 2 | x/y | 3 2/(u+y) | x/y | 3 x/y - 2/(u+y) | 3 3*(x/y - 2/(u+y)) v = 3*(x/y - 2/(u+y)) 41

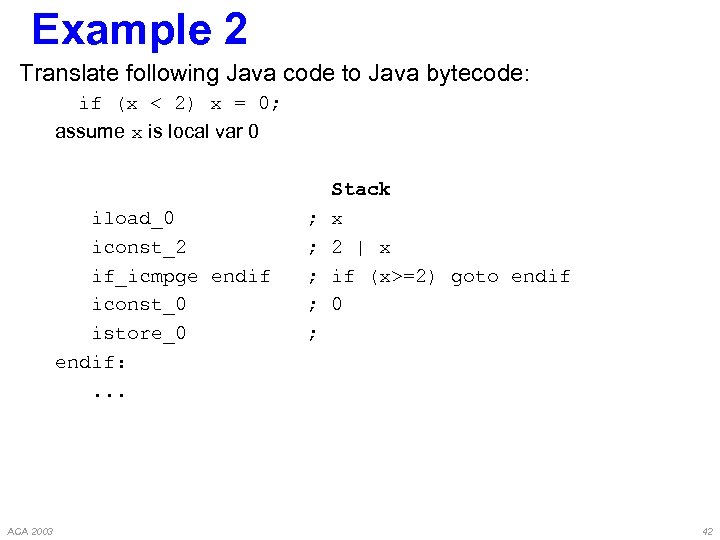

Example 2 Translate following Java code to Java bytecode: if (x < 2) x = 0; assume x is local var 0 iload_0 iconst_2 if_icmpge endif iconst_0 istore_0 endif: . . . ACA 2003 ; ; ; Stack x 2 | x if (x>=2) goto endif 0 42

0cb513a2d605aeae53bdfa4187ba1a43.ppt