879dc77e19a3d732fc4a779b62c7e801.ppt

- Количество слайдов: 11

Embedded Processor Design Confidential Artificial Intelligent Processor & Neuron-chips Design Project Master Plan ©Copyright Yongsoon Lee, 2006. All rights reserved. Some IDEA are protected by patents and papers. Any illegal action can be object of Legal Action. ECE Dept of UBC, Canada

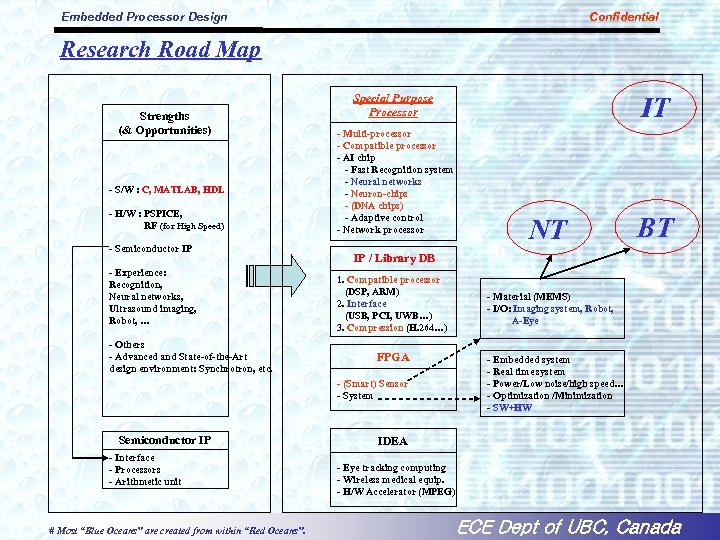

Embedded Processor Design Confidential Research Road Map Strengths (& Opportunities) - S/W : C, MATLAB, HDL - H/W : PSPICE, RF (for High Speed) - Semiconductor IP - Experience: Recognition, Neural networks, Ultrasound imaging, Robot, … - Others - Advanced and State-of-the-Art design environment: Synchrotron, etc. Special Purpose Processor - Multi-processor - Compatible processor - AI chip - Fast Recognition system - Neural networks - Neuron-chips - (DNA chips) - Adaptive control - Network processor - Interface - Processors - Arithmetic unit # Most “Blue Oceans” are created from within “Red Oceans”. NT BT IP / Library DB 1. Compatible processor (DSP, ARM) 2. Interface (USB, PCI, UWB…) 3. Compression (H. 264…) FPGA - (Smart) Sensor - System Semiconductor IP IT - Material (MEMS) - I/O: Imaging system, Robot, A-Eye - Embedded system - Real time system - Power/Low noise/high speed… - Optimization /Minimization - SW+HW IDEA - Eye tracking computing - Wireless medical equip. - H/W Accelerator (MPEG) ECE Dept of UBC, Canada

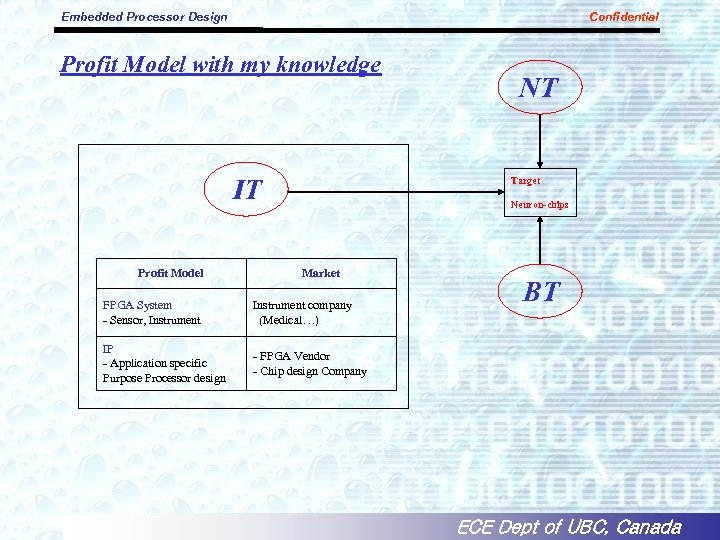

Embedded Processor Design Confidential Profit Model with my knowledge IT Profit Model NT Target Neuron-chips Market FPGA System - Sensor, Instrument company (Medical…) IP - Application specific Purpose Processor design BT - FPGA Vendor - Chip design Company ECE Dept of UBC, Canada

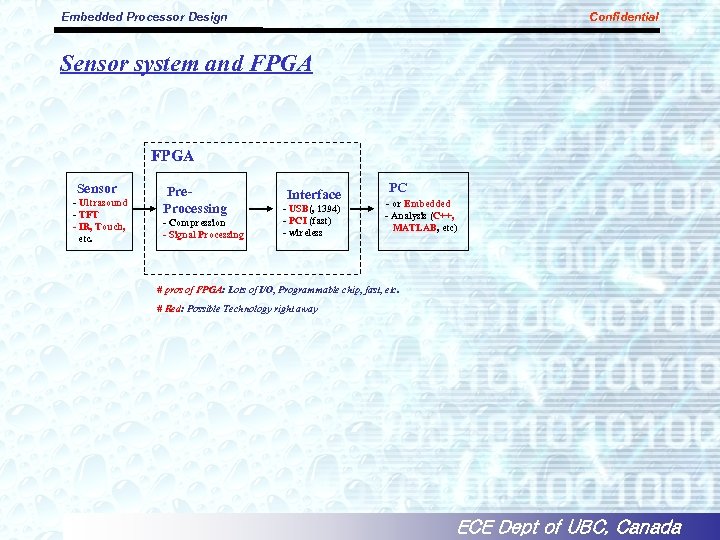

Embedded Processor Design Confidential Sensor system and FPGA Sensor - Ultrasound - TFT - IR, Touch, etc. Pre. Processing - Compression - Signal Processing Interface - USB(, 1394) - PCI (fast) - wireless PC - or Embedded - Analysis (C++, MATLAB, etc) # pros of FPGA: Lots of I/O, Programmable chip, fast, etc. # Red: Possible Technology right away ECE Dept of UBC, Canada

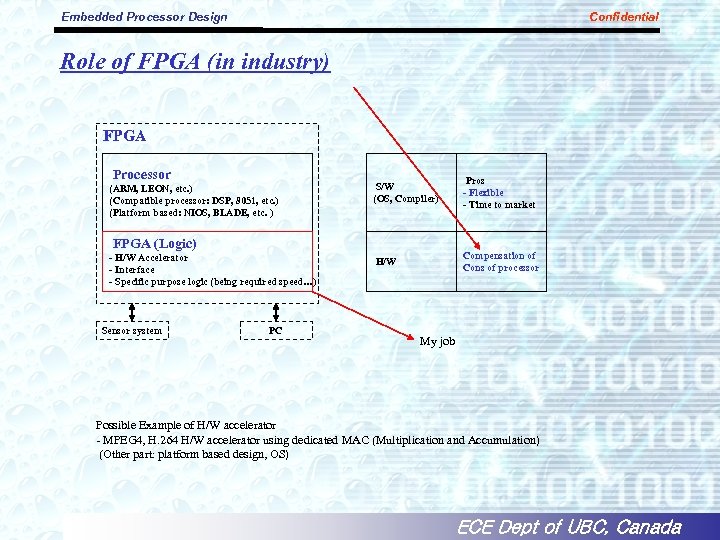

Embedded Processor Design Confidential Role of FPGA (in industry) FPGA Processor (ARM, LEON, etc. ) (Compatible processor: DSP, 8051, etc. ) (Platform based: NIOS, BLADE, etc. ) S/W (OS, Compiler) Pros - Flexible - Time to market H/W Compensation of Cons of processor FPGA (Logic) - H/W Accelerator - Interface - Specific purpose logic (being required speed…) Sensor system PC My job Possible Example of H/W accelerator - MPEG 4, H. 264 H/W accelerator using dedicated MAC (Multiplication and Accumulation) (Other part: platform based design, OS) ECE Dept of UBC, Canada

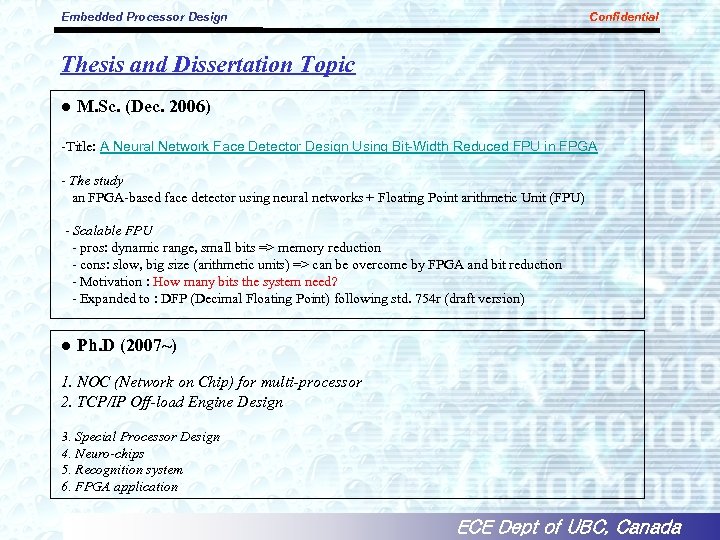

Embedded Processor Design Confidential Thesis and Dissertation Topic ● M. Sc. (Dec. 2006) -Title: A Neural Network Face Detector Design Using Bit-Width Reduced FPU in FPGA - The study an FPGA-based face detector using neural networks + Floating Point arithmetic Unit (FPU) - Scalable FPU - pros: dynamic range, small bits => memory reduction - cons: slow, big size (arithmetic units) => can be overcome by FPGA and bit reduction - Motivation : How many bits the system need? - Expanded to : DFP (Decimal Floating Point) following std. 754 r (draft version) ● Ph. D (2007~) 1. NOC (Network on Chip) for multi-processor 2. TCP/IP Off-load Engine Design 3. Special Processor Design 4. Neuro-chips 5. Recognition system 6. FPGA application ECE Dept of UBC, Canada

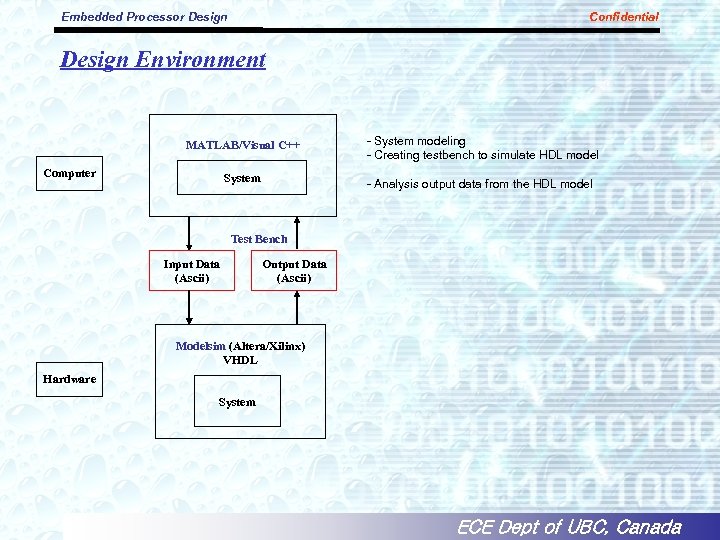

Embedded Processor Design Confidential Design Environment MATLAB/Visual C++ - System modeling - Creating testbench to simulate HDL model System - Analysis output data from the HDL model Computer Test Bench Input Data (Ascii) Output Data (Ascii) Modelsim (Altera/Xilinx) VHDL Hardware System ECE Dept of UBC, Canada

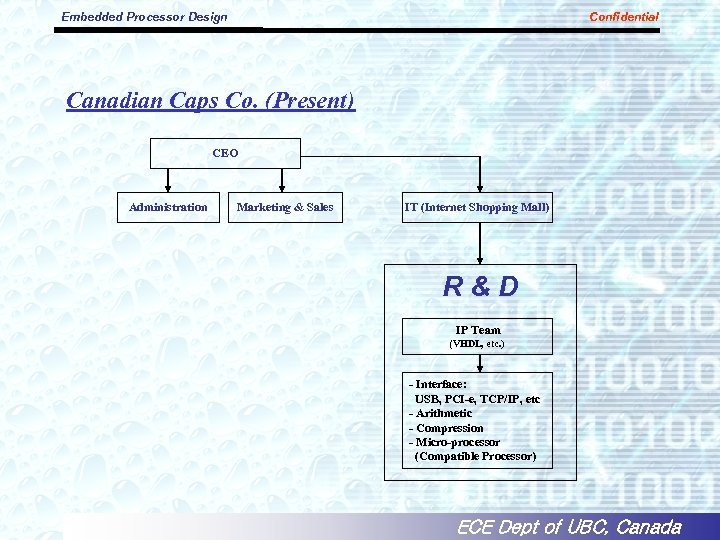

Embedded Processor Design Confidential Canadian Caps Co. (Present) CEO Administration Marketing & Sales IT (Internet Shopping Mall) R&D IP Team (VHDL, etc. ) - Interface: USB, PCI-e, TCP/IP, etc - Arithmetic - Compression - Micro-processor (Compatible Processor) ECE Dept of UBC, Canada

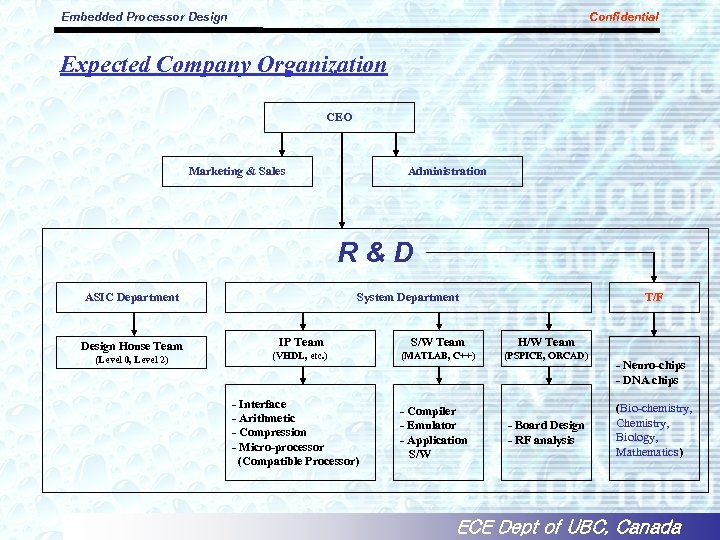

Embedded Processor Design Confidential Expected Company Organization CEO Marketing & Sales Administration R&D ASIC Department Design House Team (Level 0, Level 2) System Department T/F IP Team S/W Team H/W Team (VHDL, etc. ) (MATLAB, C++) (PSPICE, ORCAD) - Interface - Arithmetic - Compression - Micro-processor (Compatible Processor) - Compiler - Emulator - Application S/W - Board Design - RF analysis - Neuro-chips - DNA chips (Bio-chemistry, Chemistry, Biology, Mathematics) ECE Dept of UBC, Canada

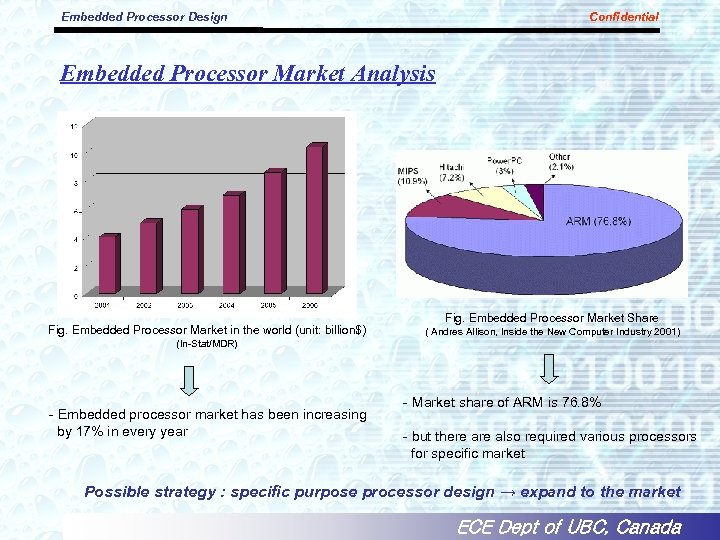

Embedded Processor Design Confidential Embedded Processor Market Analysis Fig. Embedded Processor Market in the world (unit: billion$) Fig. Embedded Processor Market Share ( Andres Allison, Inside the New Computer Industry 2001) (In-Stat/MDR) - Embedded processor market has been increasing by 17% in every year - Market share of ARM is 76. 8% - but there also required various processors for specific market Possible strategy : specific purpose processor design → expand to the market ECE Dept of UBC, Canada

Embedded Processor Design Confidential National Research Road Map Road map for country Country Focus - Canada : bio, resources - Korea : robot, communication, semi - U. S. : bio, space IRTS (International Technology Roadmap for Semiconductors) FPGA/VLSI/CAD Conferences (by Dr. Wilton) - Japan - Europe ECE Dept of UBC, Canada

879dc77e19a3d732fc4a779b62c7e801.ppt