ЭЛЕКТРОНИКА ЦИФРОВЫЕ ПРИБОРЫ Лекция

ЭЛЕКТРОНИКА ЦИФРОВЫЕ ПРИБОРЫ

Лекция 8 Структурная схема процессора 2

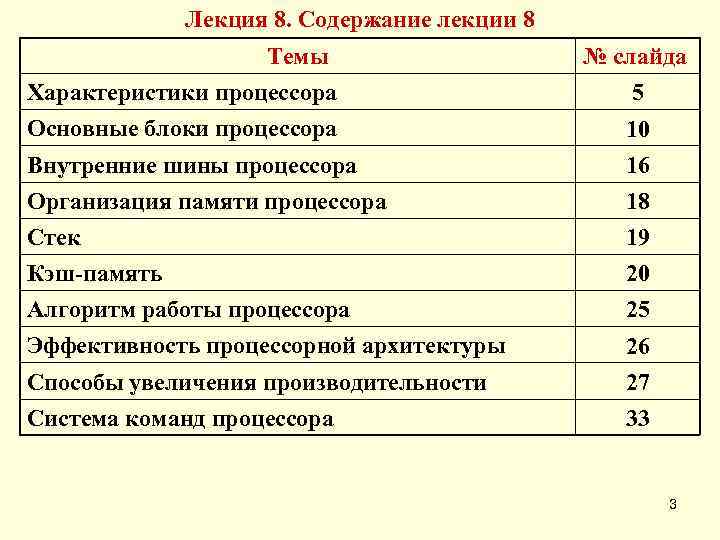

Лекция 8. Содержание лекции 8 Темы № слайда Характеристики процессора 5 Основные блоки процессора 10 Внутренние шины процессора 16 Организация памяти процессора 18 Стек 19 Кэш-память 20 Алгоритм работы процессора 25 Эффективность процессорной архитектуры 26 Способы увеличения производительности 27 Система команд процессора 33 3

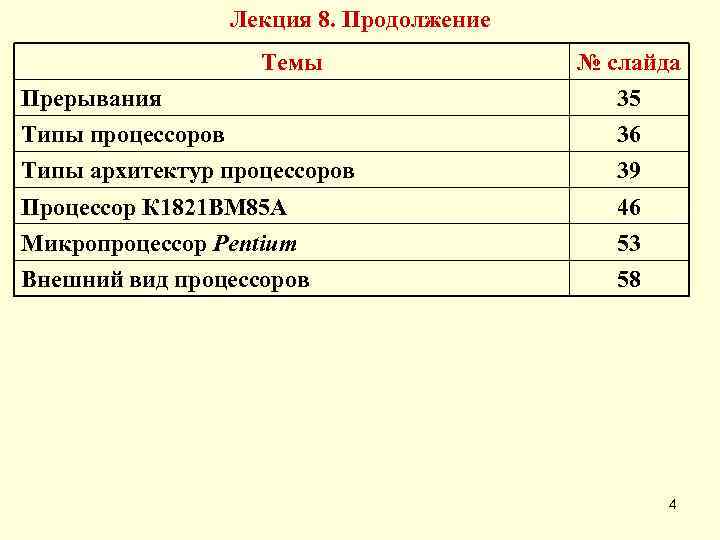

Лекция 8. Продолжение Темы № слайда Прерывания 35 Типы процессоров 36 Типы архитектур процессоров 39 Процессор К 1821 ВМ 85 А 46 Микропроцессор Pentium 53 Внешний вид процессоров 58 4

Характеристики процессора Процессор – функционально законченное устройство обработки информации, управляемое хранимой в памяти программой (в заданной последовательности команд). Программы хранятся в запоминающих устройствах – ЗУ (ПЗУ и ОЗУ). Процессор обращается к ЗУ через адресное пространство, где каждая ячейка памяти имеет индивидуальный адрес. Процессоры применяют для числового программного управления в технологических процессах, информационных, измерительных комплексах, энергетике и др. 5

Тактовая частота. Импульсы тактовой частоты поступают от задающего генератора. Тактовая частота - количество импульсов, создаваемых генератором за 1 секунду. Она необходима для синхронизации работы устройств процессора, влияет на скорость его работы. Быстродействие - это число элементарных операций, выполняемых процессором в единицу времени (операции/секунда). Разрядность - максимальное количество разрядов двоичного кода, которые могут обрабатываться или передаваться одновременно. 6

Процессор состоит из набора регистров памяти различного назначения, которые связаны между собой и работают в соответствии с определенной системой правил. Регистр – устройство, для хранения и обработки двоичного кода. К внутренним регистрам процессора относят: счетчик (адреса) команд, указатель стека, регистр состояний, регистры общего назначения. 7

Intel Pentium 8

Место процессора в структурной схеме компьютера 9

Основные блоки процессора Счетчик команд – для хранения адреса очередной команды программы и выбора адреса следующей. Алгоритм работы процессора: - чтение команды из памяти по адресу, записанному в счетчике команд; - увеличение числа в счетчике команд; - выполнение команды и повторение алгоритма. Арифметико-логическое устройство (АЛУ) – для выполнения арифметических и логических операций. Виды АЛУ: - Целочисленное, для операций с целыми числами, вещественными числами с фиксированной точкой; - АЛУ для чисел с плавающей точкой. 10

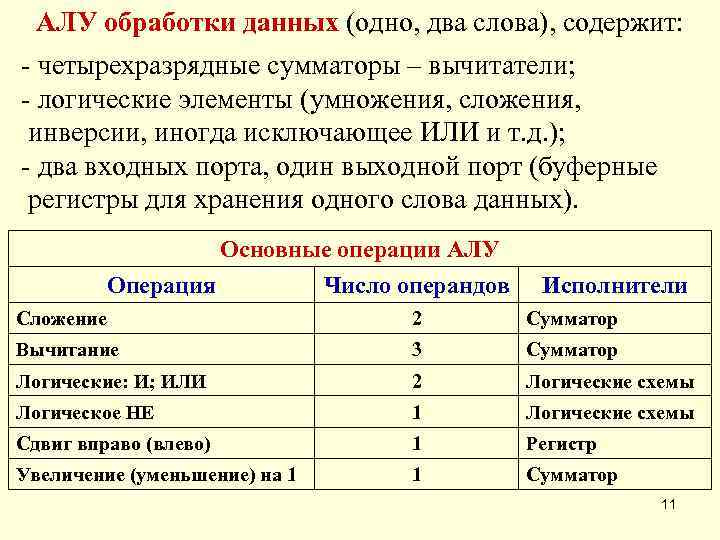

АЛУ обработки данных (одно, два слова), содержит: - четырехразрядные сумматоры – вычитатели; - логические элементы (умножения, сложения, инверсии, иногда исключающее ИЛИ и т. д. ); - два входных порта, один выходной порт (буферные регистры для хранения одного слова данных). Основные операции АЛУ Операция Число операндов Исполнители Сложение 2 Сумматор Вычитание 3 Сумматор Логические: И; ИЛИ 2 Логические схемы Логическое НЕ 1 Логические схемы Сдвиг вправо (влево) 1 Регистр Увеличение (уменьшение) на 1 1 Сумматор 11

Эти операции выполняются за один такт микропроцессора (с наибольшей скоростью), все другие операции осуществляются с их помощью. Пример. Вычитание целого числа В из целого числа А: - инверсия всех разрядов В (обратный код); - увеличение на 1 числа В (дополнительный код); - сложение А и В (старший разряд знаковый). Пример. Умножение целых чисел (16 разрядов) С = A·B: - если младший разряд B равен 1, то промежуточный результат С складывается с A (если равен 0, то переход к следующему шагу); - A: сдвиг влево на разряд; - повторение операций 15 раз. Итоговый результат C имеет 32 разряда. 12

Пример. Арифметико-логическое устройство БИС АЛУ К 1800 ВС 1 состоит из комбинационных цифровых устройств: мультиплексоров, дешифраторов, формирователя кодов, сумматора, узла управления шиной, сдвигателя. С ее помощью можно выполнять 28 логических операций и 40 арифметических (23 – с числами, представленными в двоичном коде, и 17 – с числами в двоично-десятичном коде). 13

Регистр состояний – для хранения сведений о текущих режимах работы процессора. Сюда же помещается информация о результатах выполняемых команд, например: равен ли результат нулю, отрицателен ли он, не возникли ли в ходе операции ошибки и т. п. Использование и анализ в этом регистре происходит побитно, каждый бит регистра имеет самостоятельное значение. Регистры общего назначения (РОН) – для хранения текущих обрабатываемых данных или их адреса в ОЗУ. У некоторых процессоров регистры функционально равнозначны, в других назначение регистров строго оговаривается. Информация из одного регистра может предаваться в другой. 14

Порт - схема сопряжения, включающая в себя один или несколько регистров ввода-вывода и позволяющая подключить, например периферийное устройство к внешним шинам процессора. Практически каждая микросхема использует для различных целей несколько портов ввода-вывода. Каждый порт в персональном компьютере имеет свой уникальный номер. Номера порта – это адрес регистра ввода-вывода, причём адресные пространства основной памяти и портов ввода- вывода не пересекаются. 15

Внутренние шины процессора - шина данных; - шина адресов; - шина управления. К шине данных присоединены все блоки процессора, но в каждый момент времени соединены только два блока: один передает информацию, другой ее считывает. В следующий момент соединяются другие блоки. Разрядность шины определяет разрядность процессора. Разрядность шины адресов определяет адресное пространство процессора (количество индивидуальных адресов ячеек памяти). По шине управления передаются команды. 16

Пример. Устройства на адресной шине процессор рассматривает либо как адресуемую память, либо как порты ввода-вывода. Шина - магистраль передачи данных. 17

Организация памяти процессора - Стек; - Кэш. 18

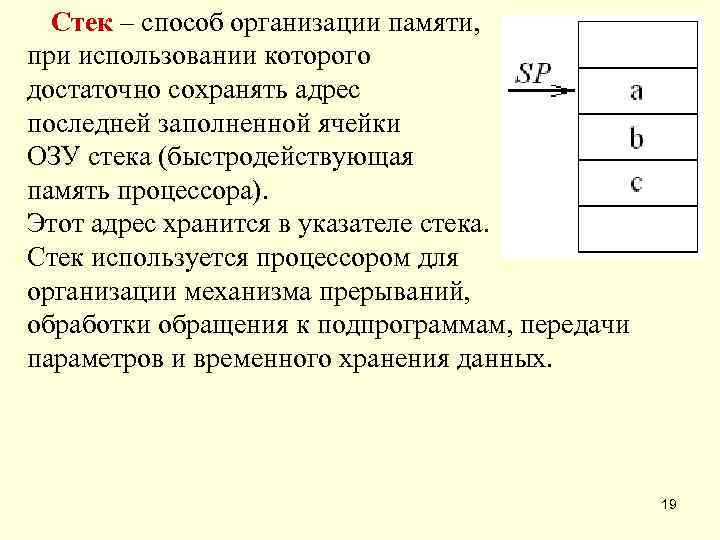

Стек – способ организации памяти, при использовании которого достаточно сохранять адрес последней заполненной ячейки ОЗУ стека (быстродействующая память процессора). Этот адрес хранится в указателе стека. Стек используется процессором для организации механизма прерываний, обработки обращения к подпрограммам, передачи параметров и временного хранения данных. 19

Кэш память Пример. Для объяснения – аналогия с холодильником: хранение запаса продуктов в холодильнике избавляет повара от необходимости ездить по магазинам, закупая провизию. При этом часть продуктов используется очень часто и держать их под рукой наиболее целесообразно. Другие используются крайне редко, и, т. к. холодильник имеет ограничение по объему, за такими продуктами можно съездить в магазин. «Холодильник» - это кэш-память, быстрая, но ограниченная по объему, а «магазин» (где доступны те же продукты) - более медленная оперативная память. 20

Назначение кэша - Быстрый доступ к часто используемым данным. Перехватываются запросы к основной памяти, определяется наличие копии данных в кэше. Если есть, данные извлекаются из кэша (кэш-попадание). Нет (промах) - запрос данных в оперативной памяти. - Согласование процессора и контроллера памяти. Процессор оперирует с ячейкой памяти (как правило байт). В каждом адресе оперативной памяти четыре 64 - разрядные ячейки (пакет). Излишки помещаются в кэш, процессор может обрабатывать эти данные с любой разрядностью. 21

- Упреждающая загрузка данных. - обращение к основной памяти после того, как их не окажется в кэше; - по запросу на чтение первой ячейки кэш-контроллер загружает несколько следующих ячеек в порядке возрастания адресов; - на основе анализа предыдущих обращений (последовательность кэш-промахов) контроллер пытается установить, какой зависимостью связны элементы и загружает последующие данные. Пример. Особенность процессора Pentium – небольшая кэш-память BTB (буфер меток перехода), которая позволяет предсказывать переходы в исполняемых программах. 22

- Отложенная запись данных. Кэш позволяет накапливать данные предназначенные для записи в оперативную память и, при освобождении шины данных, перенести их в оперативную память за один раз. Это увеличивает быстродействие процессора. 23

Структура кэш Обычно кэш-память имеет два уровня: Первый (L 1) - быстрая синхронная статическая память с частотой процессора. Объем невелик (~32 Кб), для самых необходимых данных, на их обработку уходит 1 такт. Вначале процессор обращается к ней. Второй (L 2): конвейерная статическая память (BSRAM), работает на пониженной тактовой частоте, дешевле L 1, объем до нескольких мегабайт. Скорость доступа относительно невелика (быстрее чем к основной памяти). При нехватке места L 1 переписывает данные в L 2 на место, где находились переданные L 1 данные (обмен данными). Переписывается наиболее востребованная информация. 24

Алгоритм работы процессора Четыре ступени обработки данных и команд: - Инструкции и данные забираются из кэша, разделенного на кэш данных и кэш команд; - Выбранные инструкции декодируются в машинные команды понятные процессору (декодирование); - Декодированные инструкции поступают в исполнительные блоки процессора и выполняются; - Результат записывается в кэш процессора. Это конвейер обработки команд, в данном случае четырехступенчатый. Ступень команда проходит за один такт работы процессора. Для четырехступенчатого конвейера обработка одной 25 команды занимает четыре такта.

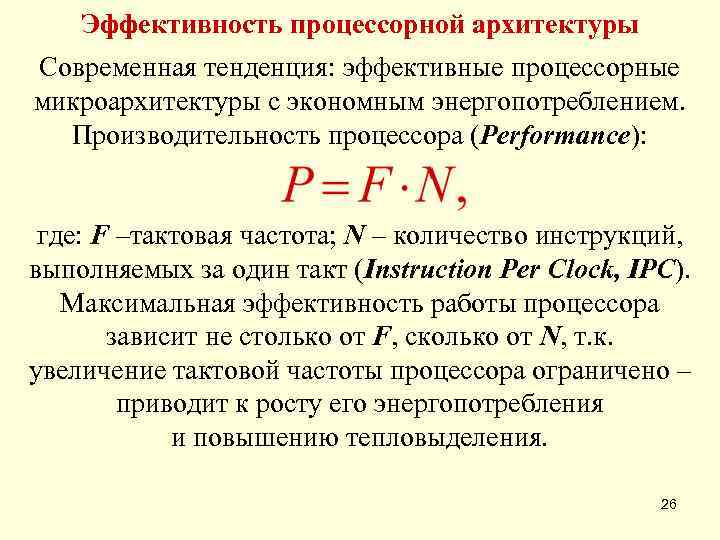

Эффективность процессорной архитектуры Современная тенденция: эффективные процессорные микроархитектуры с экономным энергопотреблением. Производительность процессора (Performance): где: F –тактовая частота; N – количество инструкций, выполняемых за один такт (Instruction Per Clock, IPC). Максимальная эффективность работы процессора зависит не столько от F, сколько от N, т. к. увеличение тактовой частоты процессора ограничено – приводит к росту его энергопотребления и повышению тепловыделения. 26

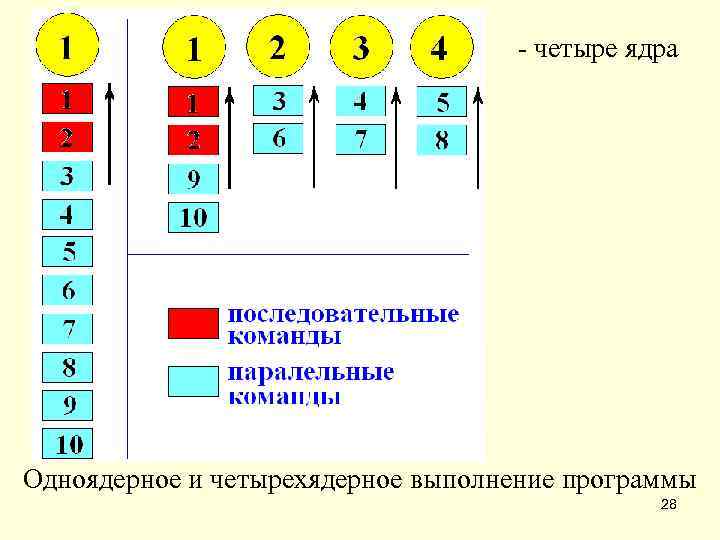

Способы увеличения производительности: - многоядерность: распараллеливание вычисления на множество ядер. Для операционной системы каждое ядро – дискретный процессор. Многоядерные процессоры содержат большее число функциональных исполнительных устройств для увеличения количества команд, одновременно исполняемых за один такт; - снижение количества инструкций, необходимых для исполнения задачи (оптимизация потока команд); - микрослияние команд (microfusion): несколько внутренних микроопераций (micro-ops) процессора скомбинированы в одну микрооперацию, это сокращает количество микроопераций для выполнения задачи. 27

- четыре ядра Одноядерное и четырехядерное выполнение программы 28

Пример. В многоядерных системах каждое ядро имеет свой кэш, поэтому операционная система имеет достаточно ресурсов для параллельного выполнения задач, требующих большой вычислительной мощности. Многоядерность процессора требует составления программ таким образом, чтобы можно было выполнять отдельные команды параллельно. Для этого, обычно, подходят программы обработки графических изображений. Если это условие не выполняется (ряд игровых программ), то многоядерность процессора не дает преимуществ перед одноядерным процессором. 29

100 ядерный процессор Процессор системы Glonass 30

- конвейерный режим: вид обработки, при котором функциональный узел выполняет процесс в несколько этапов, когда первый этап завершается, результаты передаются на второй этап, на котором используются другие средства. Устройство, используемое на первом этапе, оказывается свободным для начала новой обработки данных. Пример: существует четыре этапа обработки команды микропроцессора: выборка, декодирование, выполнение и запись результата. Пока первая команда выполняется, вторая может декодироваться, а третья выбираться. 31

Скорость работы внутренних блоков процессора в два раза выше скорости остальной части системы за счет технологии умножения частоты. Увеличить производительность системы можно за счёт хранения части данных и выполняемых кодов программ во внутренней кэш-памяти. Пример: увеличение кэш-памяти с 512 Кбайт до 1 Мбайт может привести к 20% росту общей производительности системы. Режим удвоенной производительности реализуется за счет двойной накачки - данные передаются как по переднему, так и по заднему фронтам тактовых импульсов (обычно по переднему), при этом передается до 533 Мбайт/с. 32

Система команд процессора Команды передачи данных перепись информации из одного блока в другой блок. Арифметические операции – операции сложения, вычитания. Умножение и деление реализуют специальные программы. Логические операции для анализа получаемой информации. Примеры команд: сравнение, логические операции И, ИЛИ, НЕ. Сдвиги двоичного кода влево и вправо для реализации умножения и деления. Команды ввода и вывода для обмена данными с внешними устройствами. В некоторых процессорах эти устройства являются адресами памяти, ввод и вывод осуществляется с помощью команд переписи. 33

Команды управления, например, команды обращения к подпрограмме (переход с возвратом), сюда относят операции по управлению процессором типа останов. Команда процессора обычно состоит из двух частей – операционной и адресной. Операционная часть (код операции) указывает, какое действие необходимо выполнить с информацией и имеется у любой команды. Код операции можно представить как условный номер в списке команд. Адресная часть указывает, где используемая информация хранится и куда поместить результат. Иногда адресная часть может отсутствовать, например, в команде останова. 34

Прерывания О совершении события процессор узнает по сигналу, называемому прерыванием. Исполнение текущей последовательности команд прерывается, вместо нее начинает выполняться последовательность, соответствующая прерыванию. Виды прерываний: аппаратные, логические, программные. Аппаратные прерывания – по запросам от внешних устройств (нажатие клавиши на клавиатуре). Логические прерывания – при работе процессора (деление на ноль), Программные используются для вызова специальных подпрограмм. 35

Типы процессоров Процессоры выполняют основные функции: - вычисляют (выполняют над числовыми данными арифметические и логические операции); - управляют потоками данных, организуя как сами вычисления, так их требуемую последовательность. По конструктивному признаку различают: - однокристальные процессоры с фиксированной длиной (разрядностью) слова и определенной системой команд; - многокристальные (секционные) МП с наращиваемой разрядностью слова и микропрограммным управлением. 36

От режима работы различают: - однопрограммные и многопрограммные (одновременное выполнение нескольких программ); - мультипроцессоры (многоядерные): одновременно активны несколько процессоров; - конвейерные: команды выполняются последовательно рядом устройств, причем различные устройства могут одновременно обрабатывать соответствующие части нескольких команд; - сопроцессоры: для расширения списка команд (самостоятельно не используются). 37

Технология Intel Wide Dynamic Execution призвана обеспечить выполнение большего количества команд за каждый такт, повышая эффективность выполнения приложений и сокращая энергопотребление. Каждое ядро процессора, поддерживающего эту технологию, теперь может выполнять до четырех инструкций одновременно с помощью 14 – стадийного конвейера. 38

Типы архитектур процессоров CISC - Complex Instruction Set Computer - Компьютер со сложной системой команд (включают большое количество команд). Все МП INTEL относятся к CISC. RISC - Reduced Instruction Set Computer – Компьютер с сокращенной системой команд. Упрощена система команд и сокращена до такой степени, что каждая инструкция выполняется за единственный такт (упростилась структура и увеличилось быстродействие процессора). MISC - Minimum Instruction Set Computer - Компьютер с минимальной системой команд. Последовательность простых инструкций объединяется в пакет, таким образом программа преобразуется в небольшое количество длинных команд. 39

Пример RISC: чип Cell (частота от 4 ГГц, 16· 1012 операций с плавающей запятой в секунду). Многоядерная архитектура, объем кэш-памяти второго уровня - 512 кб на ядро, использование с различными операционными системами. Применение в серверах, телевизорах Full. HD, игровых приставках Play. Station и пр. 40

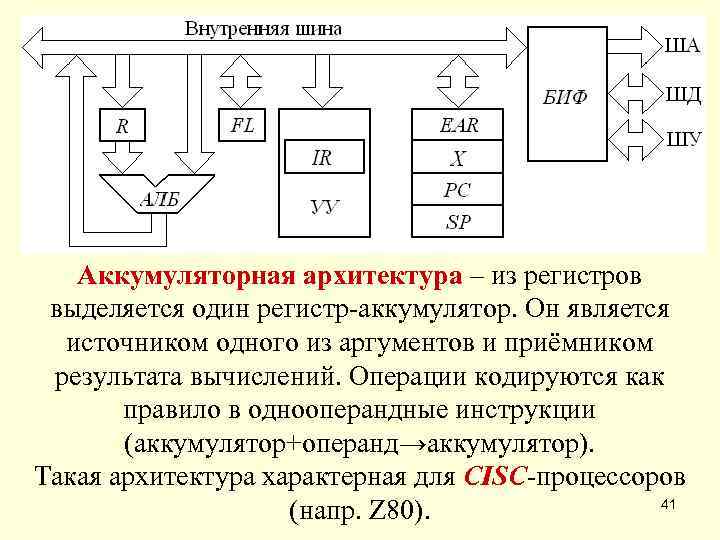

Аккумуляторная архитектура – из регистров выделяется один регистр-аккумулятор. Он является источником одного из аргументов и приёмником результата вычислений. Операции кодируются как правило в однооперандные инструкции (аккумулятор+операнд→аккумулятор). Такая архитектура характерная для CISC-процессоров (напр. Z 80). 41

УУ – устройство управления; АЛБ – арифметический-логический блок; R – регистр-аккумулятор; FL – регистр признаков (флажков); IR – регистр команд; EAR – регистр исполнительного адреса; X – регистр; SP – указатель стека; PC – программный счетчик; БИФ – блок интерфейса с выходными шинами. Первый операнд предварительно размещается в R, второй из ОП непосредственно на АЛБ. Результат – в R, а в FL признак операции. 42

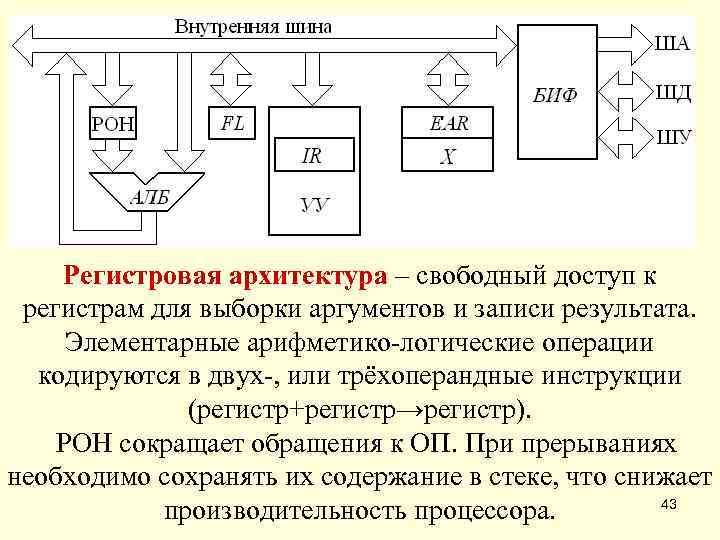

Регистровая архитектура – свободный доступ к регистрам для выборки аргументов и записи результата. Элементарные арифметико-логические операции кодируются в двух-, или трёхоперандные инструкции (регистр+регистр→регистр). РОН сокращает обращения к ОП. При прерываниях необходимо сохранять их содержание в стеке, что снижает производительность процессора. 43

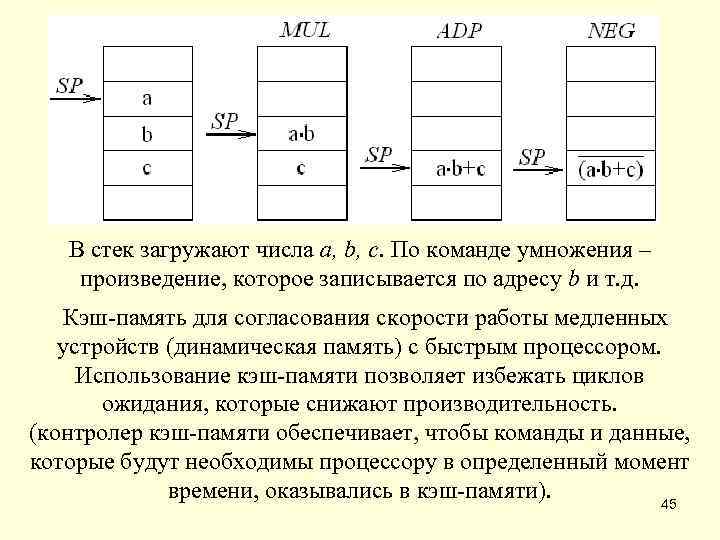

Стековая архитектура – организация регистрового файла в виде стека, и косвенная адресация регистров через указатель стека, который определяет положение вершины стека, операции производятся над значениями на вершине стека и результат кладётся также на вершину. Арифметические операции кодируются в нуль- операндные инструкции. Стековая архитектура является частью MISC-процессоров. Операнды размещают в стеке в последовательности выполнения над ними действий. 44

В стек загружают числа a, b, c. По команде умножения – произведение, которое записывается по адресу b и т. д. Кэш-память для согласования скорости работы медленных устройств (динамическая память) с быстрым процессором. Использование кэш-памяти позволяет избежать циклов ожидания, которые снижают производительность. (контролер кэш-памяти обеспечивает, чтобы команды и данные, которые будут необходимы процессору в определенный момент времени, оказывались в кэш-памяти). 45

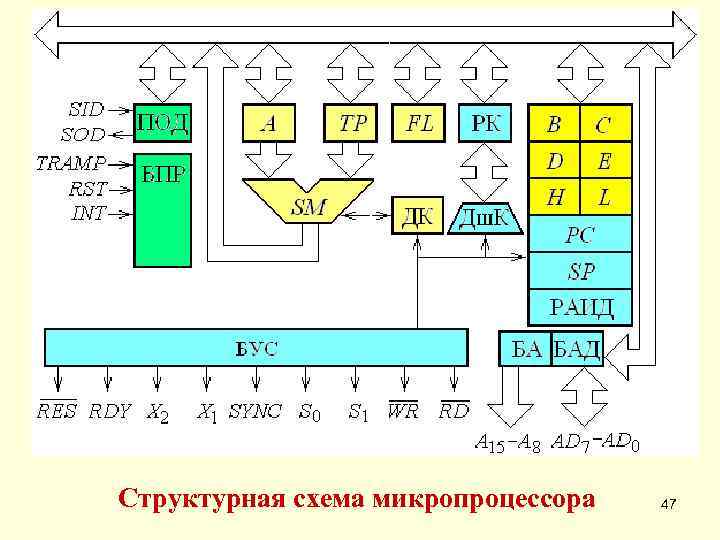

Пример: Структурная схема однокристального восьмиразрядного микропроцессора К 1821 ВМ 85 А Общая характеристика ВМ 85: - область применения: контроллеры; - система команд: фиксированная; - тактовая частота: 5 МГц; - число команд: 80; - может обслуживать 256 устройств ввода и 256 устройств вывода. 46

Структурная схема микропроцессора 47

Арифметико-логическое устройство: SM параллельный сумматор; А регистр-аккумулятор; ТР регистр временного хранения данных; FL регистр флажков (признаков); ДК схема десятичной коррекции. Блок регистров общего назначения: D, C, D, E, H, L. (все блоки восьмиразрядные) 48

Устройство управления: РК регистр команд (8 р. ); ДК дешифратор команд; РС программный счетчик команд (16 р. ); SP указатель стека; РАИД регистр адреса со схемой инкримента- декремента; БА буфер старшего байта адреса; БАД буфер младшего байта адреса (работает в мультиплексорном режиме); БУС длок выработки управляющих сигналов и синхронизации. 49

Блок управления прерываниями переключает МП с одной команды на другую: TRAP – прерывание, наивысший приоритет и не может отключаться и маскироваться; RST, INT – могут маскироваться. SID, SOD – последовательные вход и выход. RES – сброс. RDY – готовность. A 15 -A 8 – шина адреса. AД 7 -АД 0 – шина адреса-данных. SYNC – синхронизация. 50

SRO – выход сброса. WR, RD – чтение, запись. 51

Обозначение микропроцессора 52

Микропроцессор Pentium 53

Основные составляющие микропроцессора Pentium : - арифметико-логическое устройство (АЛУ), - регистры данных, - устройство управления, - внутренняя шина данных. 54

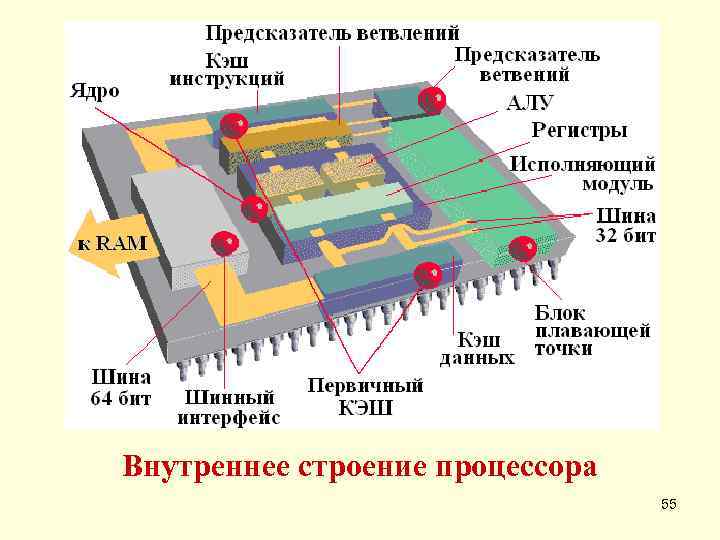

Внутреннее строение процессора 55

- Ядро: Сердце современного процессора - исполняющий модуль. Pentium имеет два параллельных целочисленных потока, позволяющих читать, интерпретировать, выполнять и отправлять две инструкции одновременно. - Предсказатель ветвлений: Модуль предсказания ветвлений пытается угадать, какая последовательность будет выполняться каждый раз когда программа содержит условный переход, так чтобы устройства предварительной выборки и декодирования получали бы инструкции готовыми предварительно. - Блок плавающей точки. Третий выполняющий модуль внутри Pentium, выполняющий нецелочисленные вычисления. - Первичный кэш: Pentium имеет два внутричиповых кэша по 8 kb, по одному для данных и инструкций, которые намного быстрее большего внешнего вторичного кэша. - Шинный интерфейс: принимает смесь кода и данных в CPU, разделяет их до готовности к использованию, и вновь соединяет, отправляя наружу. 56

По скорости выполнения операций с плавающей точкой Pentium опережает аналоги - i 486 DX-33 (почти в 10 раз), i 486 DX 2 -66 (2, 5 раза). Это достигается, благодаря реализации оптимальных алгоритмов, а также специализированным блокам сложения, умножения и деления с восмиступенчатой конвейеризацией, что позволяет выполнять операции с плавающей точкой за один такт. Pentium Pro использует технологию Dynamic Execution (предсказание ветвлений и т. д. ). В корпусе микросхемы размещены два кристалла, одним из которых является 256 - или 512 -Кбайтная кэш-память второго уровня. На кристалле процессора, как обычно, расположен 16 -Кбайтный кэш. Архитектура Pentium Pro позволяет соединять между собой множество процессоров. Так, Министерство энергетики США создала систему, базирующуюся на 9 тысячах процессоров. 57

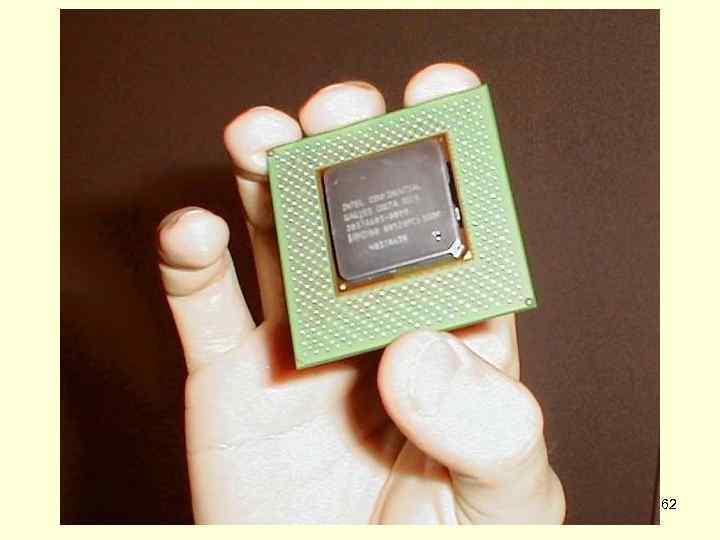

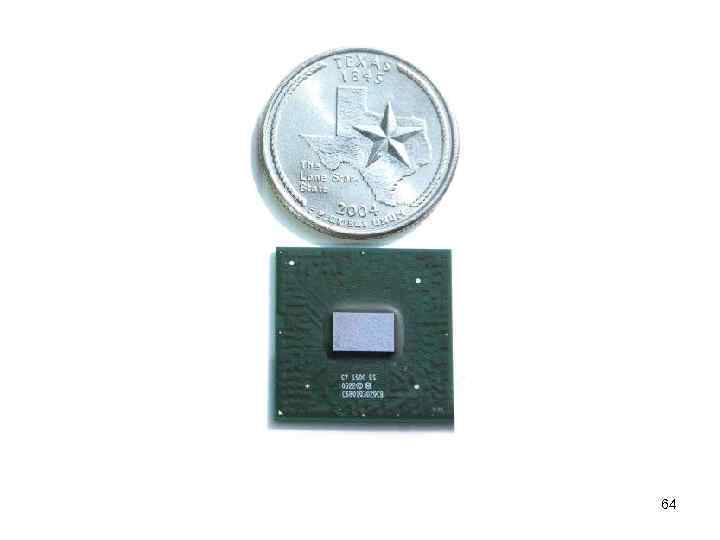

Внешний вид процессоров 58

Intel 80486 DX 2 59

Первый в мире гибкий 8 - битовый асинхронный микропроцессор ACT 11, с применением пластиковой основы (Компания Seiko Epson) 60

61

62

63

64

КОНЕЦ 65

Презентация кратко по всему курсу.ppt

- Количество слайдов: 65