3f2c772be2f6ebbe2dfcfeeb1525baef.ppt

- Количество слайдов: 25

Electronics R&D Projects @ GRAPES -3 in collaboration with VIIT Pune Atul Jain On Behalf of GRAPES-3 Collaboration WAPP – 2011, Bose Institute, Darjeelig 18 th December, 2011

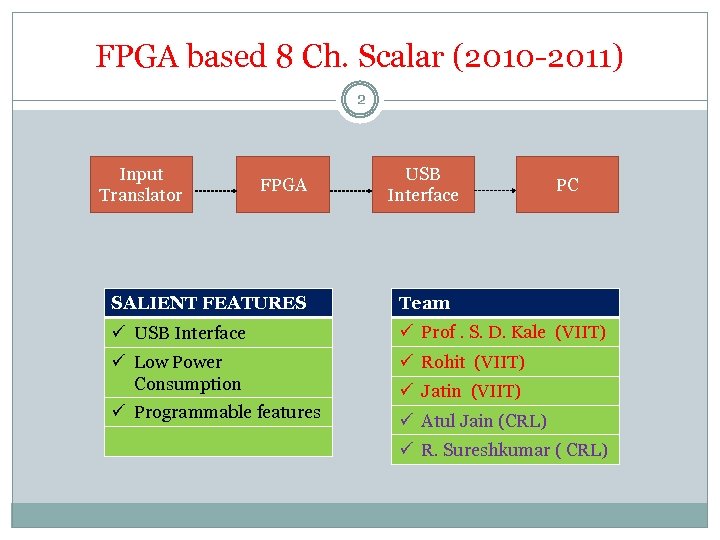

FPGA based 8 Ch. Scalar (2010 -2011) 2 Input Translator FPGA USB Interface PC SALIENT FEATURES Team ü USB Interface ü Prof. S. D. Kale (VIIT) ü Low Power Consumption ü Rohit (VIIT) ü Programmable features ü Atul Jain (CRL) ü Jatin (VIIT) ü R. Sureshkumar ( CRL)

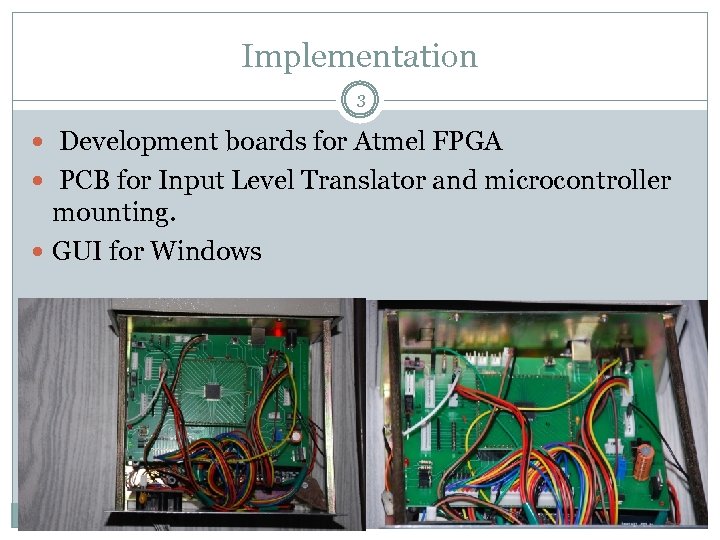

Implementation 3 Development boards for Atmel FPGA PCB for Input Level Translator and microcontroller mounting. GUI for Windows

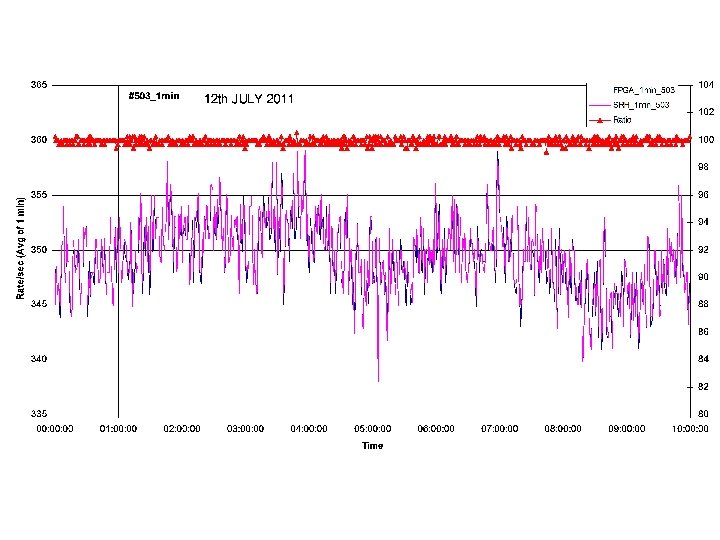

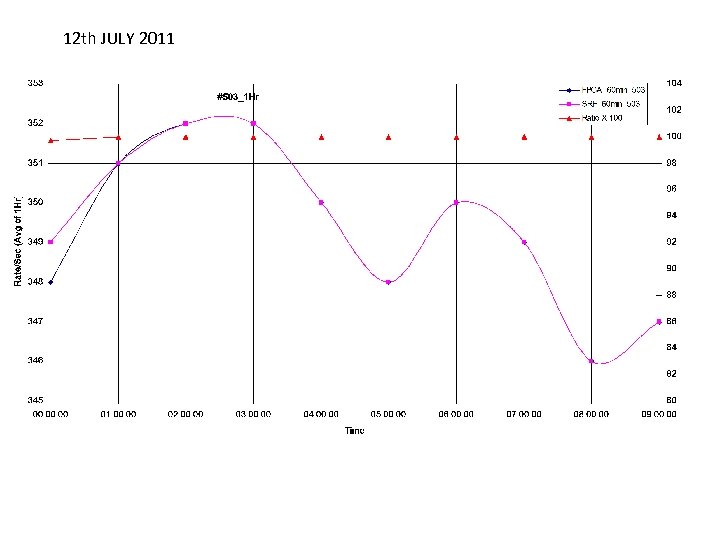

Real World Test 4

12 th JULY 2011

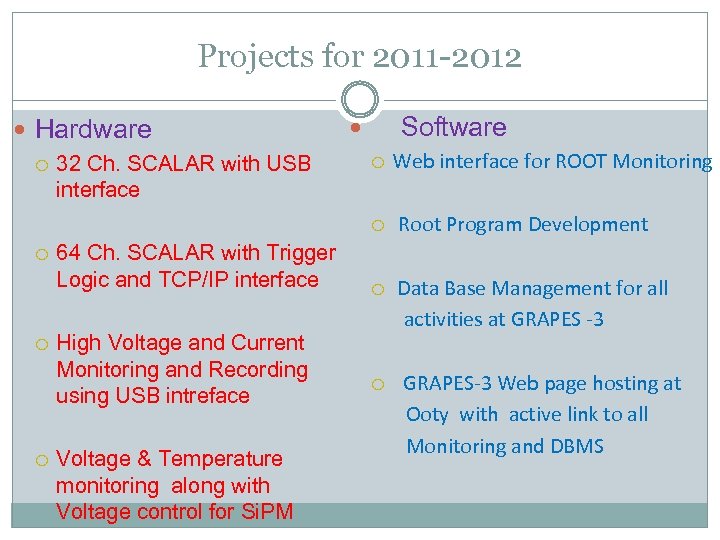

Projects for 2011 -2012 Hardware 32 Ch. SCALAR with USB interface Software Web interface for ROOT Monitoring 64 Ch. SCALAR with Trigger Logic and TCP/IP interface High Voltage and Current Monitoring and Recording using USB intreface Voltage & Temperature monitoring along with Voltage control for Si. PM Root Program Development Data Base Management for all activities at GRAPES -3 GRAPES-3 Web page hosting at Ooty with active link to all Monitoring and DBMS

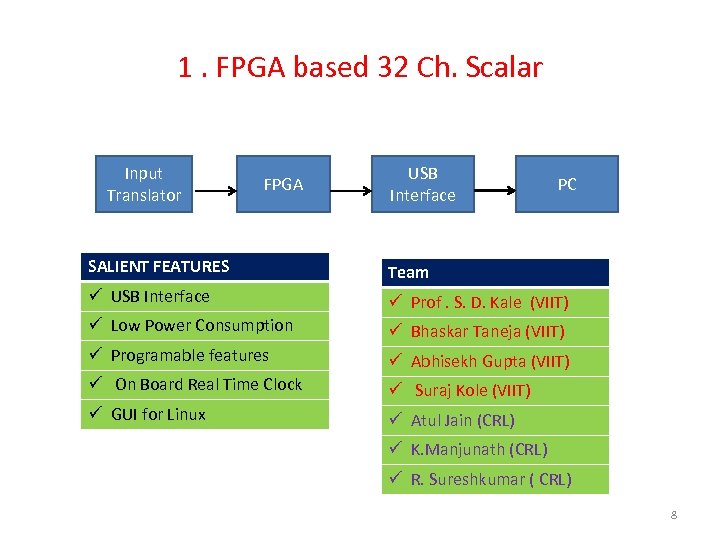

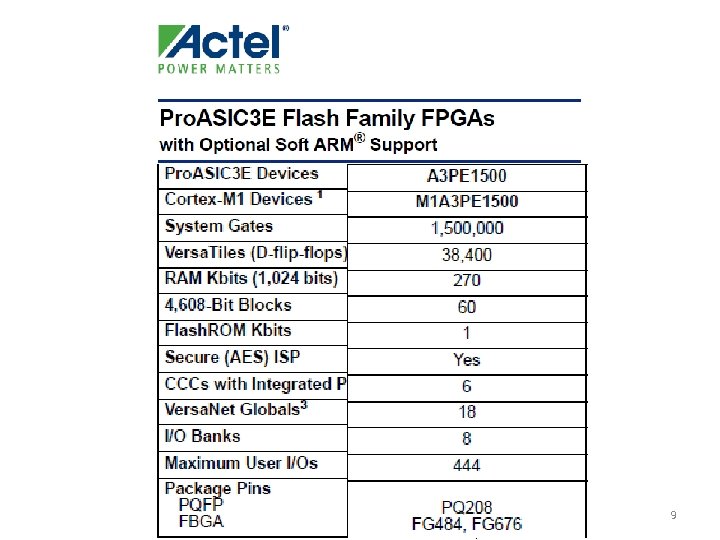

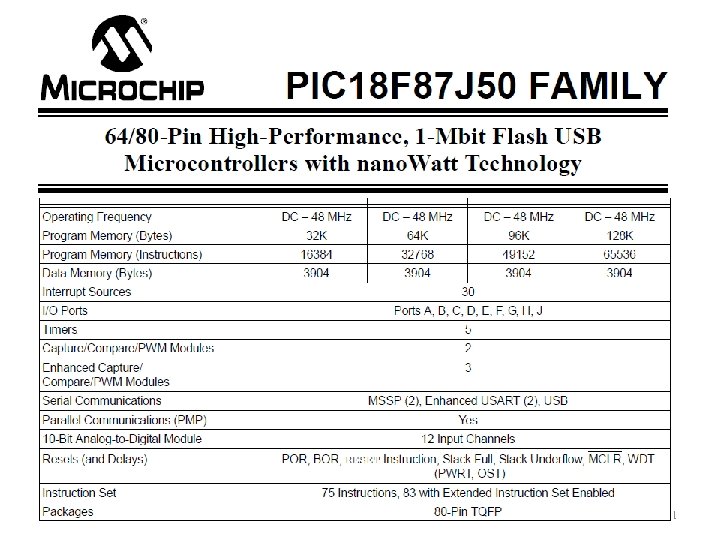

1. FPGA based 32 Ch. Scalar Input Translator FPGA USB Interface PC SALIENT FEATURES Team ü USB Interface ü Prof. S. D. Kale (VIIT) ü Low Power Consumption ü Bhaskar Taneja (VIIT) ü Programable features ü Abhisekh Gupta (VIIT) ü On Board Real Time Clock ü Suraj Kole (VIIT) ü GUI for Linux ü Atul Jain (CRL) ü K. Manjunath (CRL) ü R. Sureshkumar ( CRL) 8

9

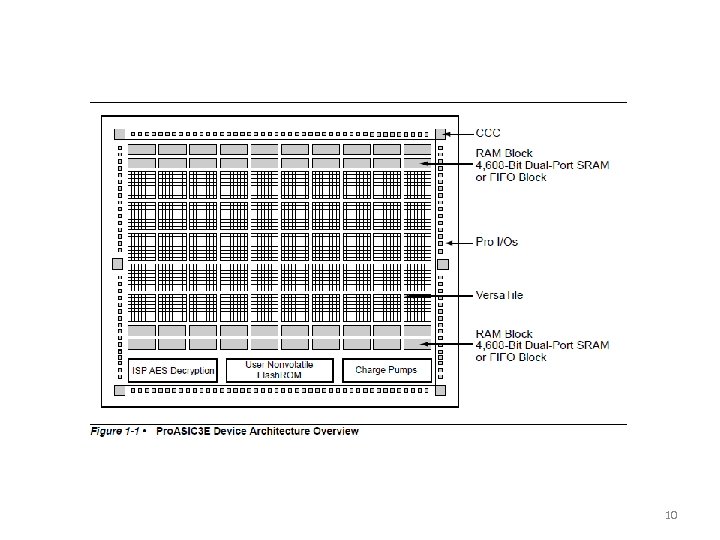

10

11

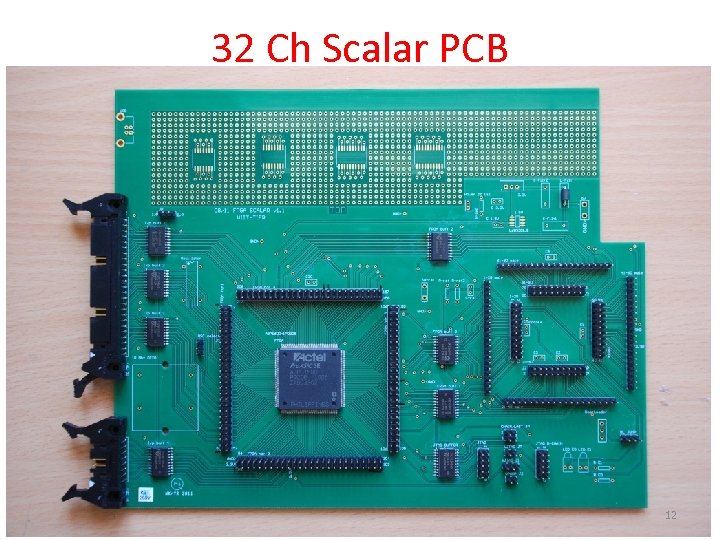

32 Ch Scalar PCB 12

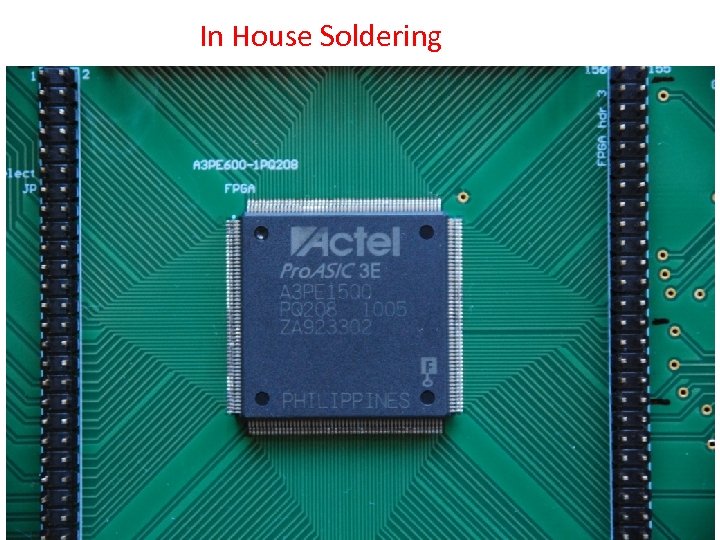

In House Soldering 13

Status 14 Board under test at VIIT GUI development for Linux Early January ready for test bench demonstration

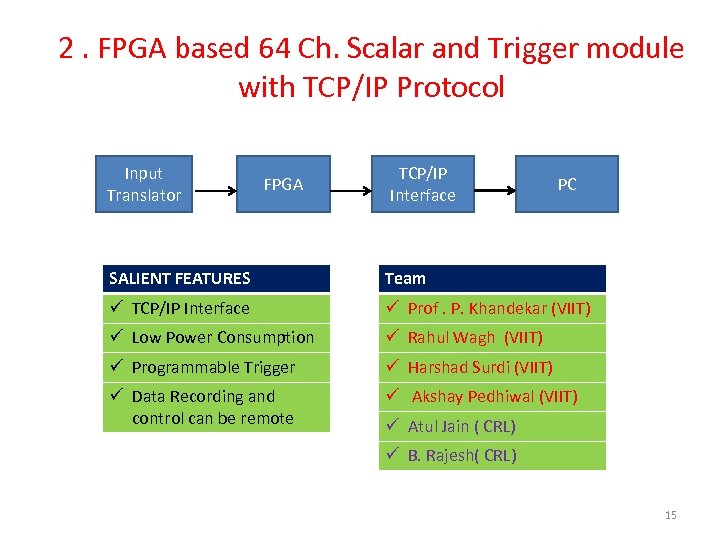

2. FPGA based 64 Ch. Scalar and Trigger module with TCP/IP Protocol Input Translator FPGA TCP/IP Interface PC SALIENT FEATURES Team ü TCP/IP Interface ü Prof. P. Khandekar (VIIT) ü Low Power Consumption ü Rahul Wagh (VIIT) ü Programmable Trigger ü Harshad Surdi (VIIT) ü Data Recording and control can be remote ü Akshay Pedhiwal (VIIT) ü Atul Jain ( CRL) ü B. Rajesh( CRL) 15

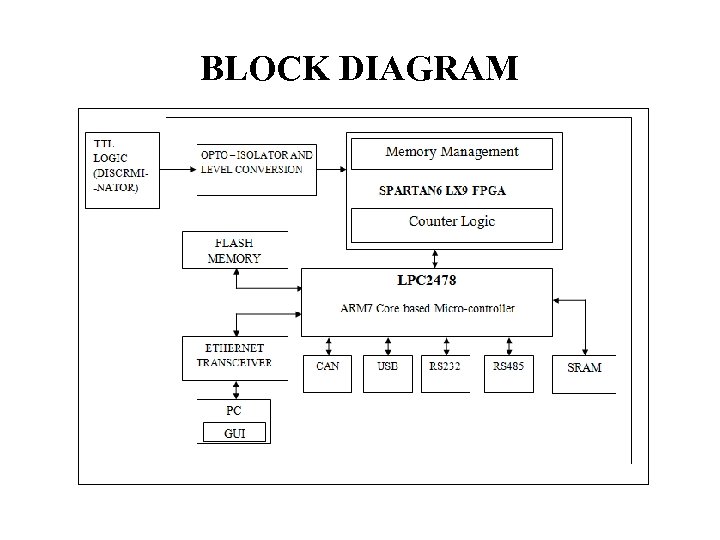

BLOCK DIAGRAM

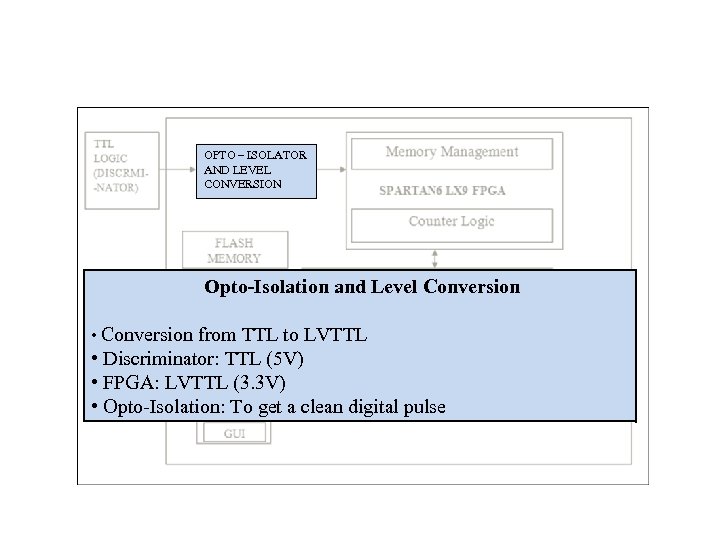

OPTO – ISOLATOR AND LEVEL CONVERSION Opto-Isolation and Level Conversion • Conversion from TTL to LVTTL • Discriminator: TTL (5 V) • FPGA: LVTTL (3. 3 V) • Opto-Isolation: To get a clean digital pulse

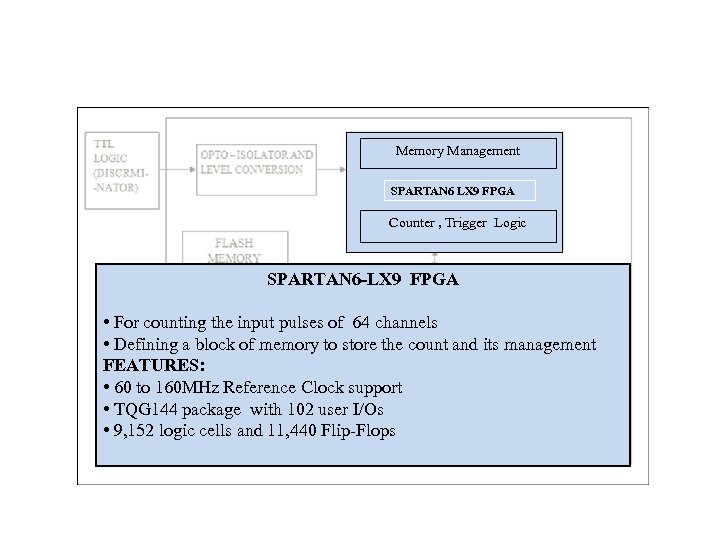

Memory Management SPARTAN 6 LX 9 FPGA Counter , Trigger Logic SPARTAN 6 -LX 9 FPGA • For counting the input pulses of 64 channels • Defining a block of memory to store the count and its management FEATURES: • 60 to 160 MHz Reference Clock support • TQG 144 package with 102 user I/Os • 9, 152 logic cells and 11, 440 Flip-Flops

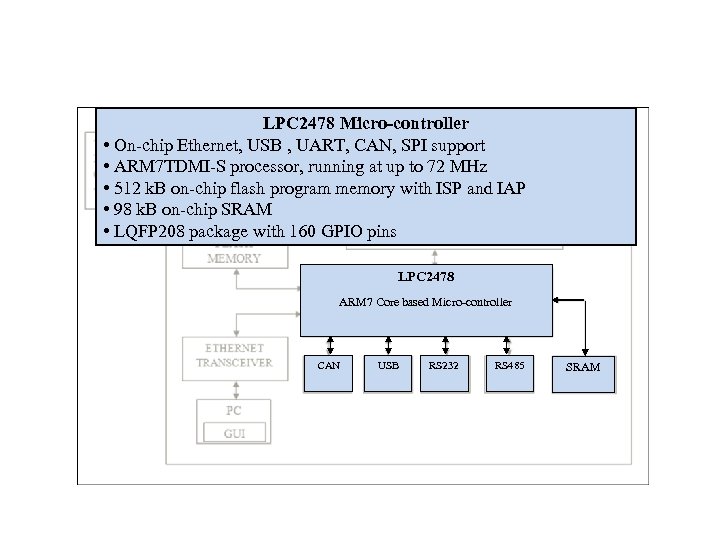

LPC 2478 Micro-controller • On-chip Ethernet, USB , UART, CAN, SPI support • ARM 7 TDMI-S processor, running at up to 72 MHz • 512 k. B on-chip flash program memory with ISP and IAP • 98 k. B on-chip SRAM • LQFP 208 package with 160 GPIO pins LPC 2478 ARM 7 Core based Micro-controller CAN USB RS 232 RS 485 SRAM

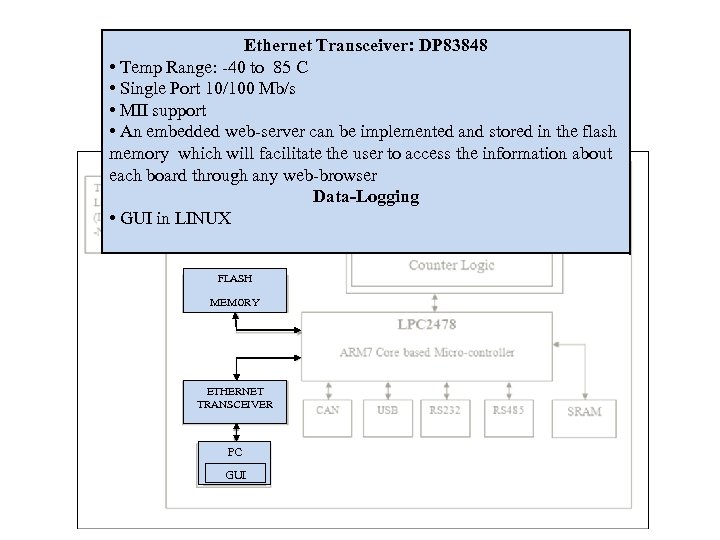

Ethernet Transceiver: DP 83848 • Temp Range: -40 to 85 C • Single Port 10/100 Mb/s • MII support • An embedded web-server can be implemented and stored in the flash memory which will facilitate the user to access the information about each board through any web-browser Data-Logging • GUI in LINUX FLASH MEMORY ETHERNET TRANSCEIVER PC GUI

Future Long term Applications 21 Scheme would be adopted for Designing compact and portable test benches Enhancing the monitoring of parameters Large DAQ to be installed at GRAPES-3 ( 4000 nos of Proportional Counters)

22

23

24

THANKS

3f2c772be2f6ebbe2dfcfeeb1525baef.ppt