c3174bd62458b844c7503aea367ebb47.ppt

- Количество слайдов: 43

Electronics for the m eg experiment • • Short introduction and status Trigger electronics DAQ electronics Slow Control Developments useful for other experiments 20. Feb. 2002, LTP

Electronics for the m eg experiment • • Short introduction and status Trigger electronics DAQ electronics Slow Control Developments useful for other experiments 20. Feb. 2002, LTP

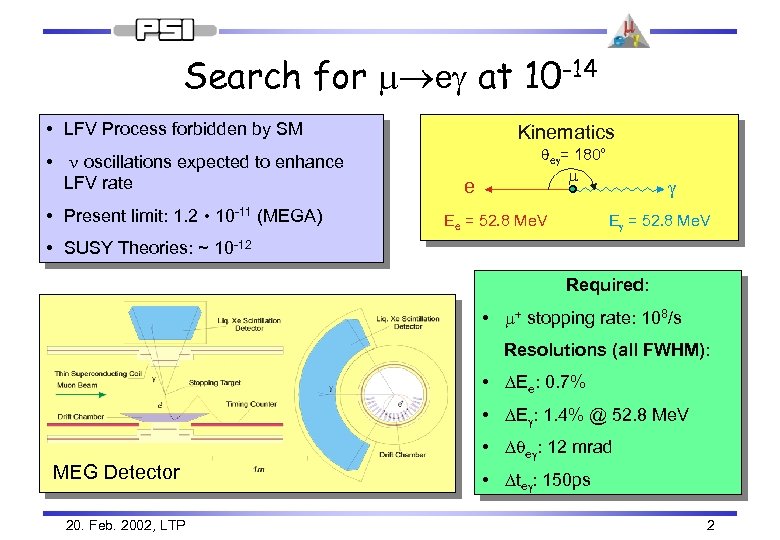

Search for m eg at 10 -14 • LFV Process forbidden by SM • n oscillations expected to enhance LFV rate • Present limit: 1. 2 • 10 -11 (MEGA) Kinematics qeg= 180° m e Ee = 52. 8 Me. V g Eg = 52. 8 Me. V • SUSY Theories: ~ 10 -12 Required: • m+ stopping rate: 108/s Resolutions (all FWHM): • DEe: 0. 7% • DEg: 1. 4% @ 52. 8 Me. V • Dqeg: 12 mrad MEG Detector 20. Feb. 2002, LTP • Dteg: 150 ps 2

Search for m eg at 10 -14 • LFV Process forbidden by SM • n oscillations expected to enhance LFV rate • Present limit: 1. 2 • 10 -11 (MEGA) Kinematics qeg= 180° m e Ee = 52. 8 Me. V g Eg = 52. 8 Me. V • SUSY Theories: ~ 10 -12 Required: • m+ stopping rate: 108/s Resolutions (all FWHM): • DEe: 0. 7% • DEg: 1. 4% @ 52. 8 Me. V • Dqeg: 12 mrad MEG Detector 20. Feb. 2002, LTP • Dteg: 150 ps 2

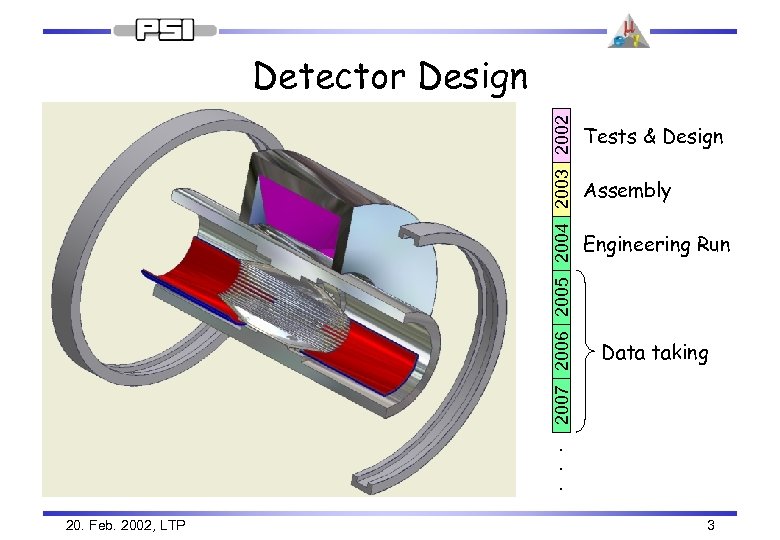

2007 2006 2005 2004 2003 2002 Detector Design Tests & Design Assembly Engineering Run Data taking . . . 20. Feb. 2002, LTP 3

2007 2006 2005 2004 2003 2002 Detector Design Tests & Design Assembly Engineering Run Data taking . . . 20. Feb. 2002, LTP 3

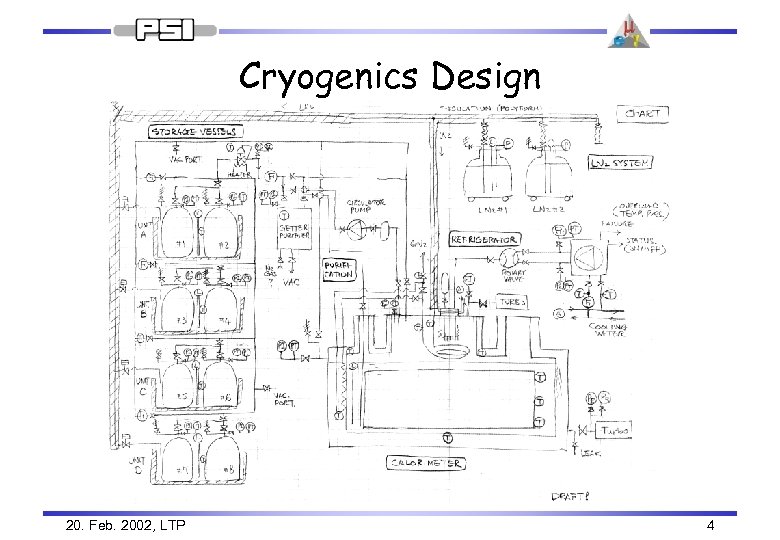

Cryogenics Design 20. Feb. 2002, LTP 4

Cryogenics Design 20. Feb. 2002, LTP 4

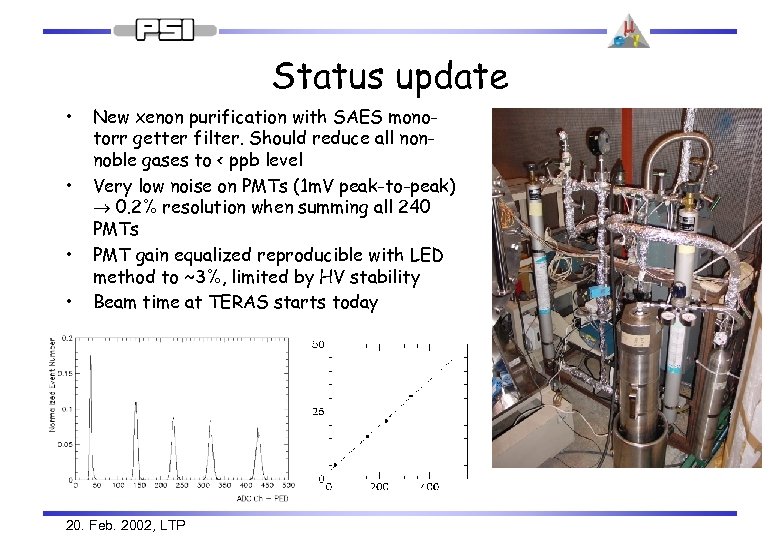

Status update • • New xenon purification with SAES monotorr getter filter. Should reduce all nonnoble gases to < ppb level Very low noise on PMTs (1 m. V peak-to-peak) 0. 2% resolution when summing all 240 PMTs PMT gain equalized reproducible with LED method to ~3%, limited by HV stability Beam time at TERAS starts today 20. Feb. 2002, LTP

Status update • • New xenon purification with SAES monotorr getter filter. Should reduce all nonnoble gases to < ppb level Very low noise on PMTs (1 m. V peak-to-peak) 0. 2% resolution when summing all 240 PMTs PMT gain equalized reproducible with LED method to ~3%, limited by HV stability Beam time at TERAS starts today 20. Feb. 2002, LTP

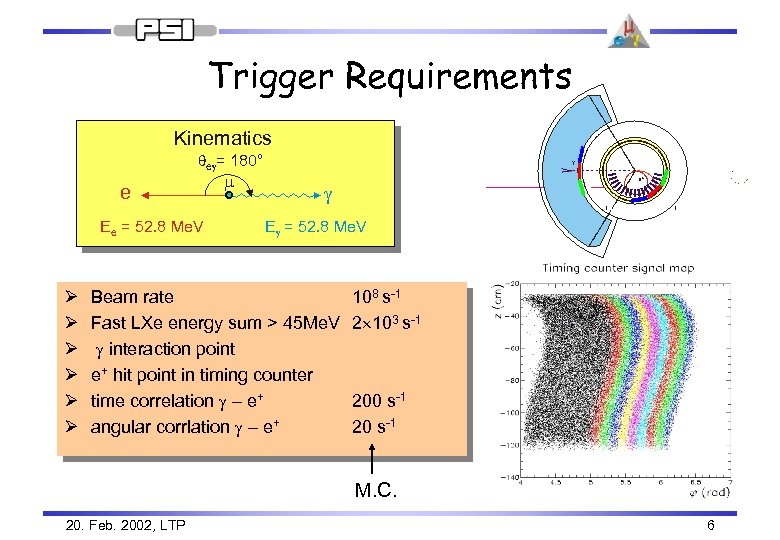

Trigger Requirements Kinematics qeg= 180° e Ee = 52. 8 Me. V Ø Ø Ø m g e+ g Eg = 52. 8 Me. V Beam rate Fast LXe energy sum > 45 Me. V g interaction point e+ hit point in timing counter time correlation g – e+ angular corrlation g – e+ 108 s-1 2 103 s-1 200 s-1 20 s-1 M. C. 20. Feb. 2002, LTP 6

Trigger Requirements Kinematics qeg= 180° e Ee = 52. 8 Me. V Ø Ø Ø m g e+ g Eg = 52. 8 Me. V Beam rate Fast LXe energy sum > 45 Me. V g interaction point e+ hit point in timing counter time correlation g – e+ angular corrlation g – e+ 108 s-1 2 103 s-1 200 s-1 20 s-1 M. C. 20. Feb. 2002, LTP 6

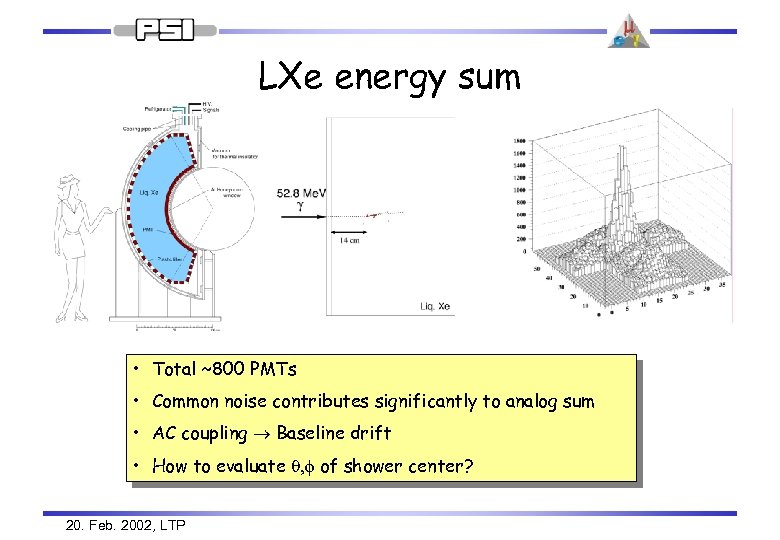

LXe energy sum • Total ~800 PMTs • Common noise contributes significantly to analog sum • AC coupling Baseline drift • How to evaluate q, f of shower center? 20. Feb. 2002, LTP

LXe energy sum • Total ~800 PMTs • Common noise contributes significantly to analog sum • AC coupling Baseline drift • How to evaluate q, f of shower center? 20. Feb. 2002, LTP

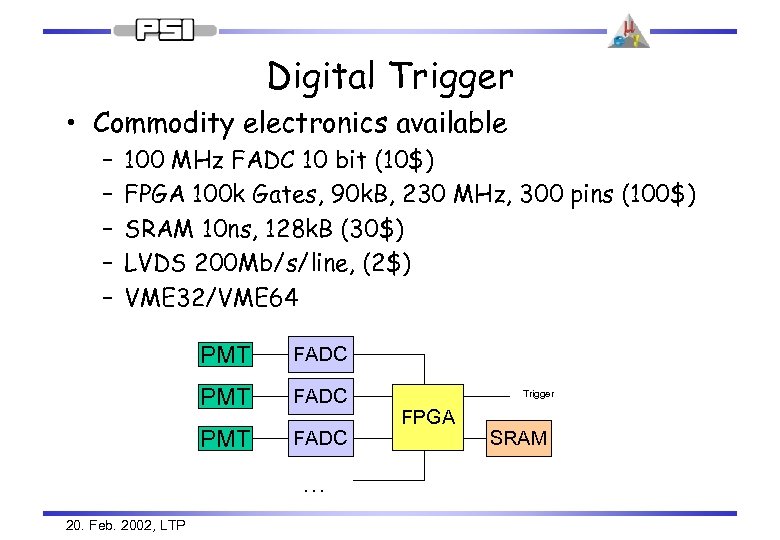

Digital Trigger • Commodity electronics available – – – 100 MHz FADC 10 bit (10$) FPGA 100 k Gates, 90 k. B, 230 MHz, 300 pins (100$) SRAM 10 ns, 128 k. B (30$) LVDS 200 Mb/s/line, (2$) VME 32/VME 64 PMT FADC … 20. Feb. 2002, LTP Trigger FPGA SRAM

Digital Trigger • Commodity electronics available – – – 100 MHz FADC 10 bit (10$) FPGA 100 k Gates, 90 k. B, 230 MHz, 300 pins (100$) SRAM 10 ns, 128 k. B (30$) LVDS 200 Mb/s/line, (2$) VME 32/VME 64 PMT FADC … 20. Feb. 2002, LTP Trigger FPGA SRAM

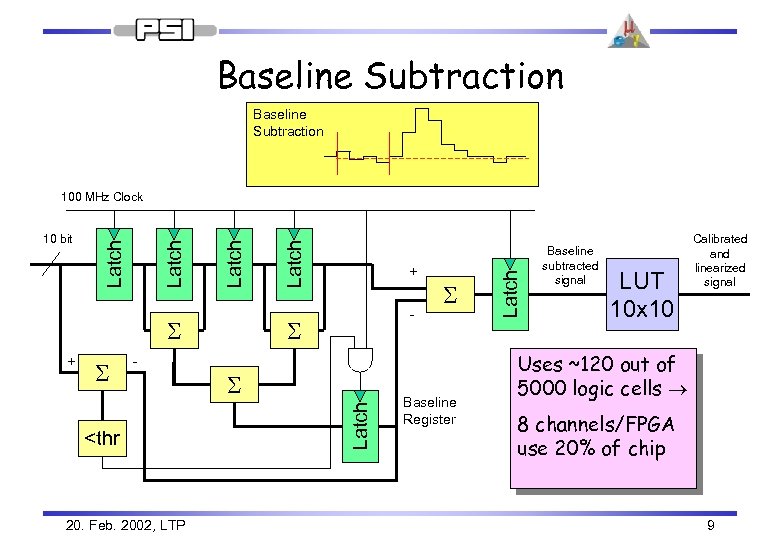

Baseline Subtraction S -

Baseline Subtraction S -

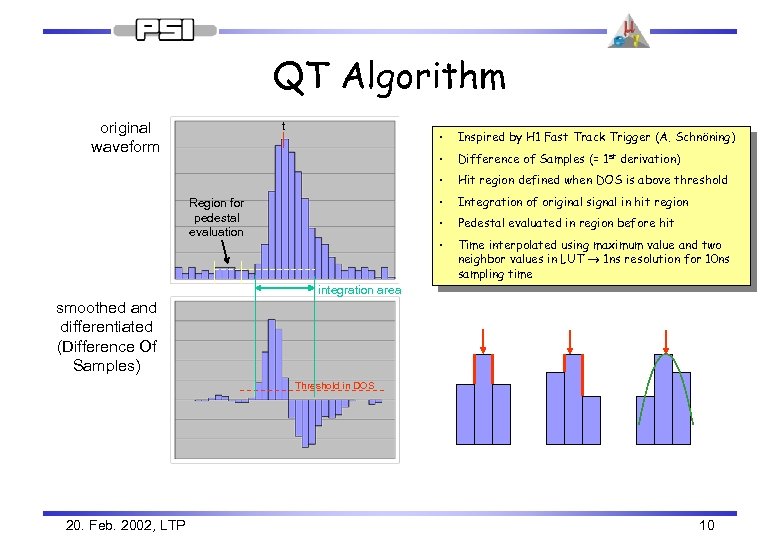

QT Algorithm original waveform t • • Difference of Samples (= 1 st derivation) • Hit region defined when DOS is above threshold • Integration of original signal in hit region • Pedestal evaluated in region before hit • Region for pedestal evaluation Inspired by H 1 Fast Track Trigger (A. Schnöning) Time interpolated using maximum value and two neighbor values in LUT 1 ns resolution for 10 ns sampling time integration area smoothed and differentiated (Difference Of Samples) Threshold in DOS 20. Feb. 2002, LTP 10

QT Algorithm original waveform t • • Difference of Samples (= 1 st derivation) • Hit region defined when DOS is above threshold • Integration of original signal in hit region • Pedestal evaluated in region before hit • Region for pedestal evaluation Inspired by H 1 Fast Track Trigger (A. Schnöning) Time interpolated using maximum value and two neighbor values in LUT 1 ns resolution for 10 ns sampling time integration area smoothed and differentiated (Difference Of Samples) Threshold in DOS 20. Feb. 2002, LTP 10

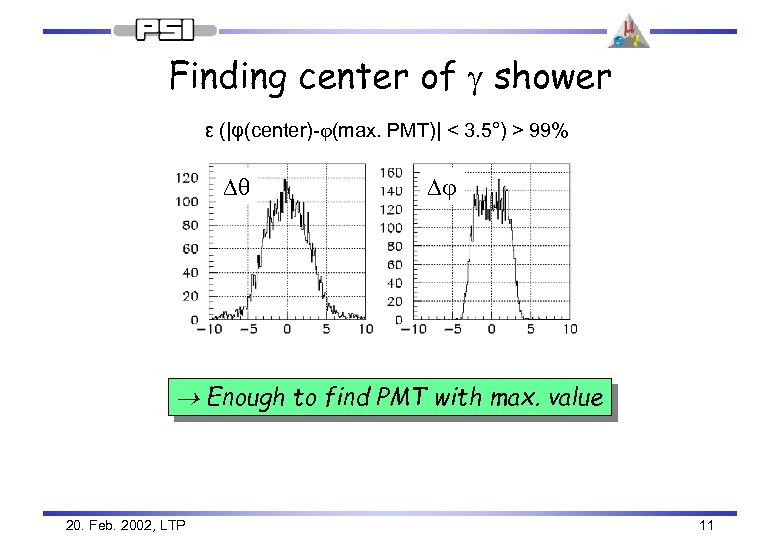

Finding center of g shower ε (|φ(center)-j(max. PMT)| < 3. 5°) > 99% Dq Dj Enough to find PMT with max. value 20. Feb. 2002, LTP 11

Finding center of g shower ε (|φ(center)-j(max. PMT)| < 3. 5°) > 99% Dq Dj Enough to find PMT with max. value 20. Feb. 2002, LTP 11

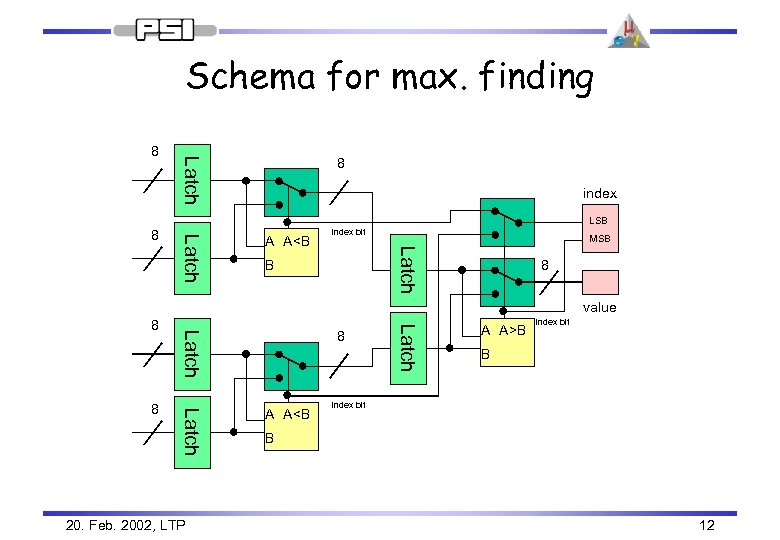

Schema for max. finding 8 Latch 8 index LSB A AB Index bit B 12

Schema for max. finding 8 Latch 8 index LSB A AB Index bit B 12

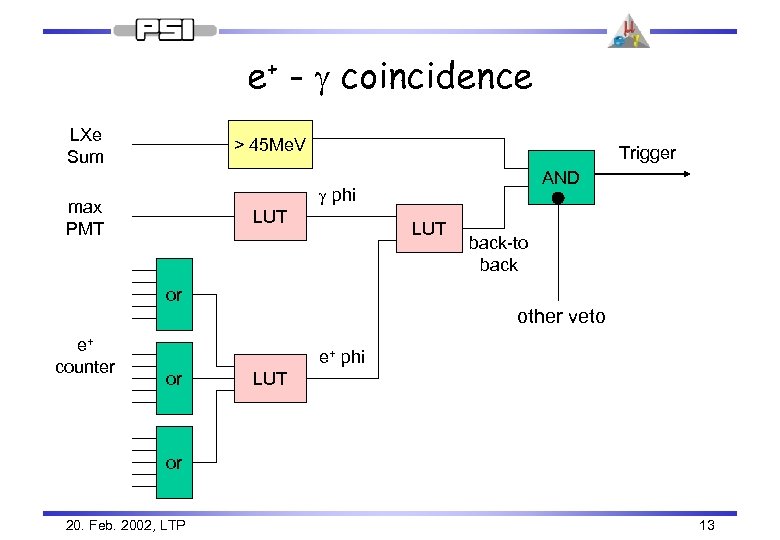

e+ - g coincidence LXe Sum > 45 Me. V Trigger AND g phi max PMT LUT back-to back or other veto e+ counter e+ phi or LUT or 20. Feb. 2002, LTP 13

e+ - g coincidence LXe Sum > 45 Me. V Trigger AND g phi max PMT LUT back-to back or other veto e+ counter e+ phi or LUT or 20. Feb. 2002, LTP 13

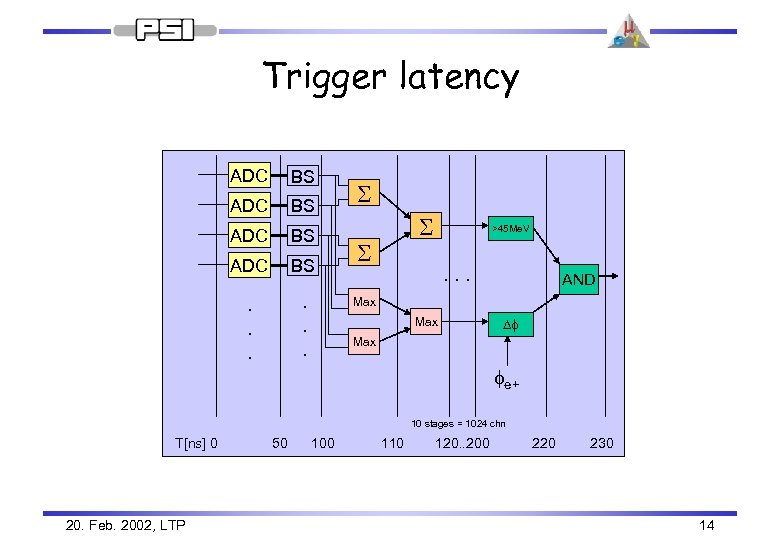

Trigger latency ADC BS . . . S S S >45 Me. V . . . AND Max Df Max fe+ 10 stages = 1024 chn T[ns] 0 20. Feb. 2002, LTP 50 100 110 120. . 200 220 230 14

Trigger latency ADC BS . . . S S S >45 Me. V . . . AND Max Df Max fe+ 10 stages = 1024 chn T[ns] 0 20. Feb. 2002, LTP 50 100 110 120. . 200 220 230 14

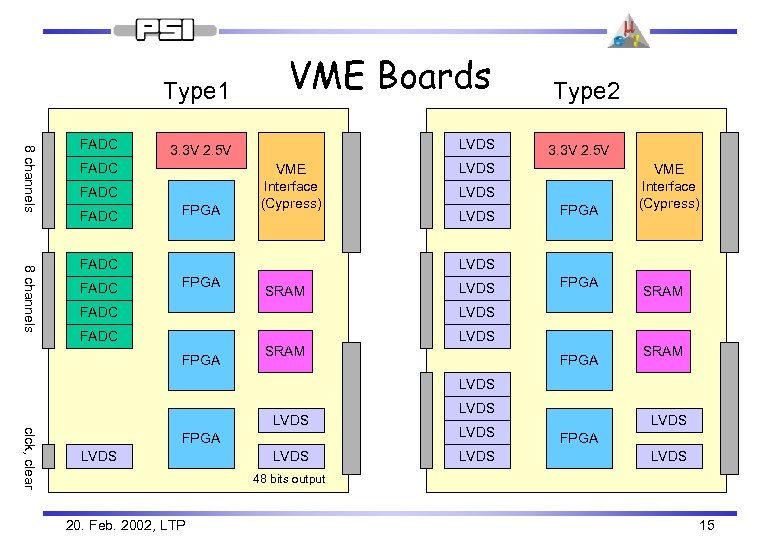

8 channels Type 1 FADC VME Boards 3. 3 V 2. 5 V LVDS FADC FPGA VME Interface (Cypress) 8 channels FADC Type 2 3. 3 V 2. 5 V LVDS FPGA VME Interface (Cypress) LVDS FPGA SRAM LVDS FADC LVDS SRAM LVDS FADC FPGA SRAM LVDS clck, clear LVDS FPGA LVDS LVDS FPGA LVDS 48 bits output 20. Feb. 2002, LTP 15

8 channels Type 1 FADC VME Boards 3. 3 V 2. 5 V LVDS FADC FPGA VME Interface (Cypress) 8 channels FADC Type 2 3. 3 V 2. 5 V LVDS FPGA VME Interface (Cypress) LVDS FPGA SRAM LVDS FADC LVDS SRAM LVDS FADC FPGA SRAM LVDS clck, clear LVDS FPGA LVDS LVDS FPGA LVDS 48 bits output 20. Feb. 2002, LTP 15

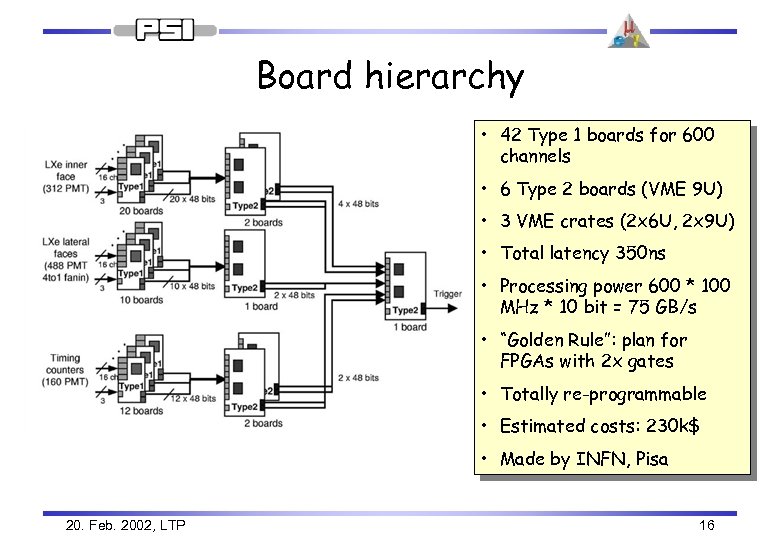

Board hierarchy • 42 Type 1 boards for 600 channels • 6 Type 2 boards (VME 9 U) • 3 VME crates (2 x 6 U, 2 x 9 U) • Total latency 350 ns • Processing power 600 * 100 MHz * 10 bit = 75 GB/s • “Golden Rule”: plan for FPGAs with 2 x gates • Totally re-programmable • Estimated costs: 230 k$ • Made by INFN, Pisa 20. Feb. 2002, LTP 16

Board hierarchy • 42 Type 1 boards for 600 channels • 6 Type 2 boards (VME 9 U) • 3 VME crates (2 x 6 U, 2 x 9 U) • Total latency 350 ns • Processing power 600 * 100 MHz * 10 bit = 75 GB/s • “Golden Rule”: plan for FPGAs with 2 x gates • Totally re-programmable • Estimated costs: 230 k$ • Made by INFN, Pisa 20. Feb. 2002, LTP 16

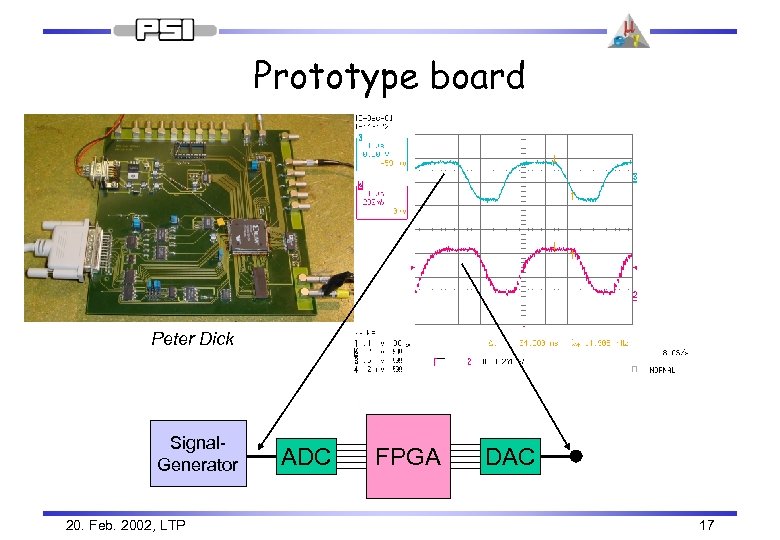

Prototype board Peter Dick Signal. Generator 20. Feb. 2002, LTP ADC FPGA DAC 17

Prototype board Peter Dick Signal. Generator 20. Feb. 2002, LTP ADC FPGA DAC 17

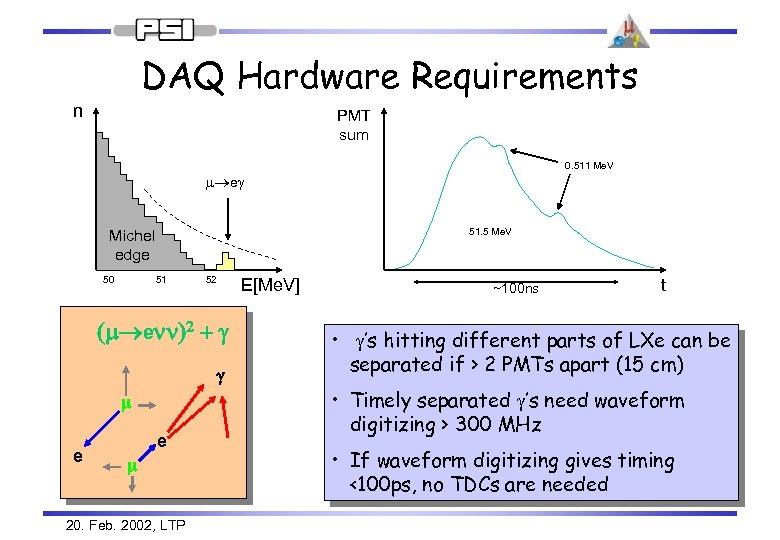

DAQ Hardware Requirements n PMT sum 0. 511 Me. V m eg 51. 5 Me. V Michel edge 50 51 52 E[Me. V] (m enn)2 + g g m e e m 20. Feb. 2002, LTP ~100 ns t • g’s hitting different parts of LXe can be separated if > 2 PMTs apart (15 cm) • Timely separated g’s need waveform digitizing > 300 MHz • If waveform digitizing gives timing <100 ps, no TDCs are needed

DAQ Hardware Requirements n PMT sum 0. 511 Me. V m eg 51. 5 Me. V Michel edge 50 51 52 E[Me. V] (m enn)2 + g g m e e m 20. Feb. 2002, LTP ~100 ns t • g’s hitting different parts of LXe can be separated if > 2 PMTs apart (15 cm) • Timely separated g’s need waveform digitizing > 300 MHz • If waveform digitizing gives timing <100 ps, no TDCs are needed

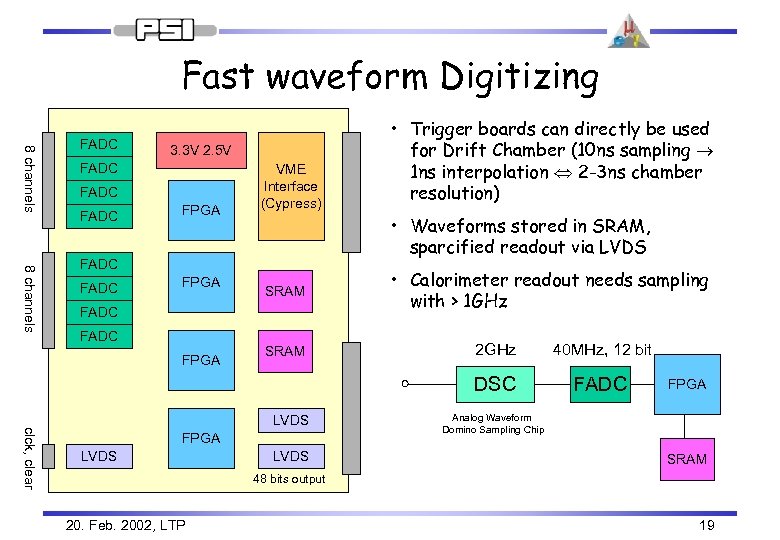

Fast waveform Digitizing 8 channels FADC 3. 3 V 2. 5 V FADC FPGA VME Interface (Cypress) • Waveforms stored in SRAM, sparcified readout via LVDS 8 channels FADC FPGA SRAM FADC • Trigger boards can directly be used for Drift Chamber (10 ns sampling 1 ns interpolation 2 -3 ns chamber resolution) • Calorimeter readout needs sampling with > 1 GHz SRAM clck, clear LVDS FPGA LVDS 2 GHz 40 MHz, 12 bit DSC FPGA FADC FPGA Analog Waveform Domino Sampling Chip SRAM 48 bits output 20. Feb. 2002, LTP 19

Fast waveform Digitizing 8 channels FADC 3. 3 V 2. 5 V FADC FPGA VME Interface (Cypress) • Waveforms stored in SRAM, sparcified readout via LVDS 8 channels FADC FPGA SRAM FADC • Trigger boards can directly be used for Drift Chamber (10 ns sampling 1 ns interpolation 2 -3 ns chamber resolution) • Calorimeter readout needs sampling with > 1 GHz SRAM clck, clear LVDS FPGA LVDS 2 GHz 40 MHz, 12 bit DSC FPGA FADC FPGA Analog Waveform Domino Sampling Chip SRAM 48 bits output 20. Feb. 2002, LTP 19

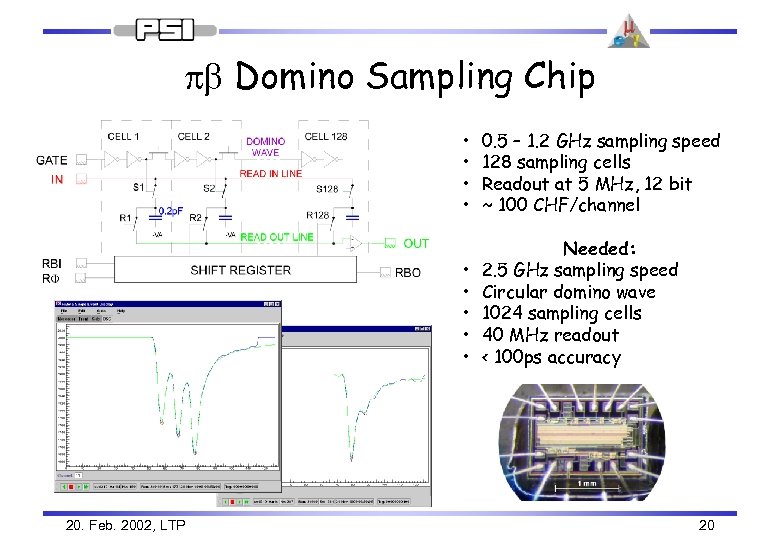

pb Domino Sampling Chip • • • 20. Feb. 2002, LTP 0. 5 – 1. 2 GHz sampling speed 128 sampling cells Readout at 5 MHz, 12 bit ~ 100 CHF/channel Needed: 2. 5 GHz sampling speed Circular domino wave 1024 sampling cells 40 MHz readout < 100 ps accuracy 20

pb Domino Sampling Chip • • • 20. Feb. 2002, LTP 0. 5 – 1. 2 GHz sampling speed 128 sampling cells Readout at 5 MHz, 12 bit ~ 100 CHF/channel Needed: 2. 5 GHz sampling speed Circular domino wave 1024 sampling cells 40 MHz readout < 100 ps accuracy 20

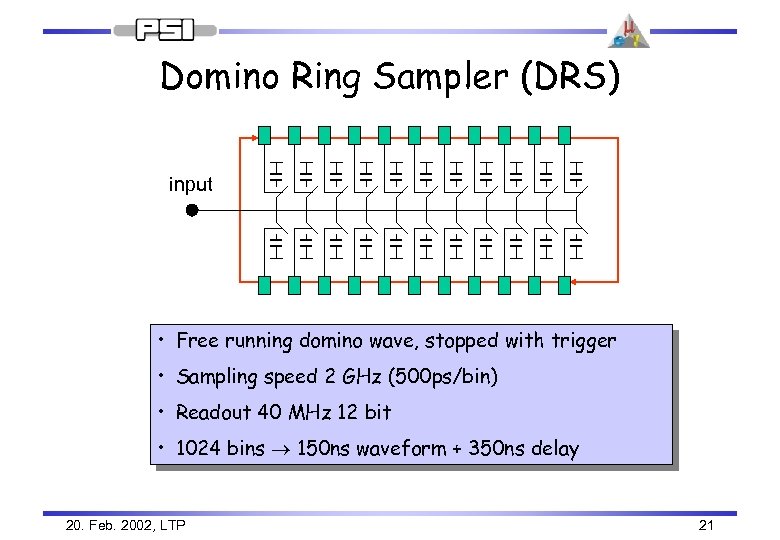

Domino Ring Sampler (DRS) input • Free running domino wave, stopped with trigger • Sampling speed 2 GHz (500 ps/bin) • Readout 40 MHz 12 bit • 1024 bins 150 ns waveform + 350 ns delay 20. Feb. 2002, LTP 21

Domino Ring Sampler (DRS) input • Free running domino wave, stopped with trigger • Sampling speed 2 GHz (500 ps/bin) • Readout 40 MHz 12 bit • 1024 bins 150 ns waveform + 350 ns delay 20. Feb. 2002, LTP 21

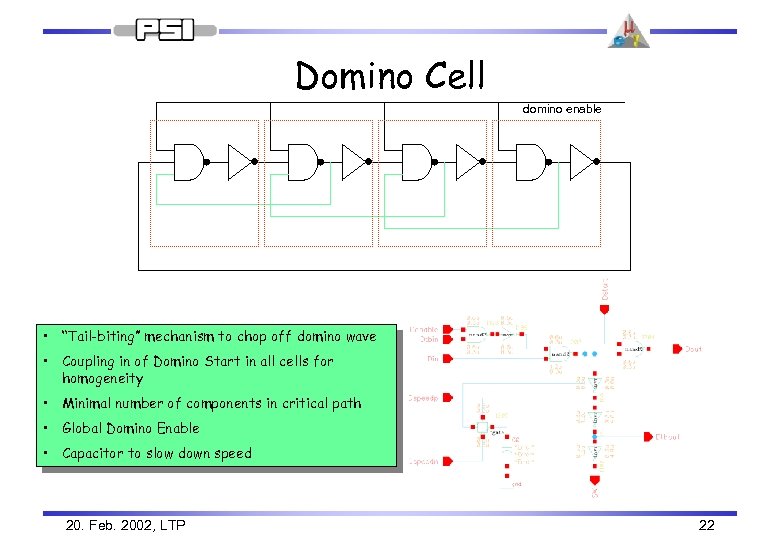

Domino Cell domino enable • “Tail-biting” mechanism to chop off domino wave • Coupling in of Domino Start in all cells for homogeneity • Minimal number of components in critical path • Global Domino Enable • Capacitor to slow down speed 20. Feb. 2002, LTP 22

Domino Cell domino enable • “Tail-biting” mechanism to chop off domino wave • Coupling in of Domino Start in all cells for homogeneity • Minimal number of components in critical path • Global Domino Enable • Capacitor to slow down speed 20. Feb. 2002, LTP 22

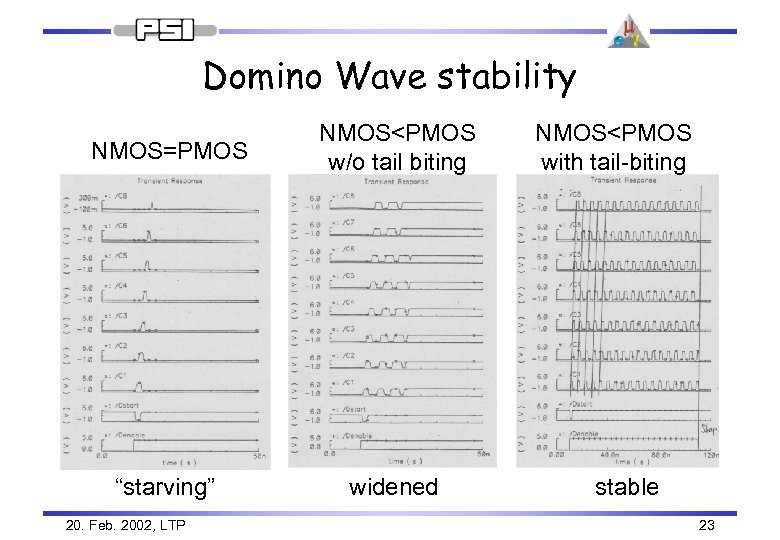

Domino Wave stability NMOS=PMOS NMOS

Domino Wave stability NMOS=PMOS NMOS

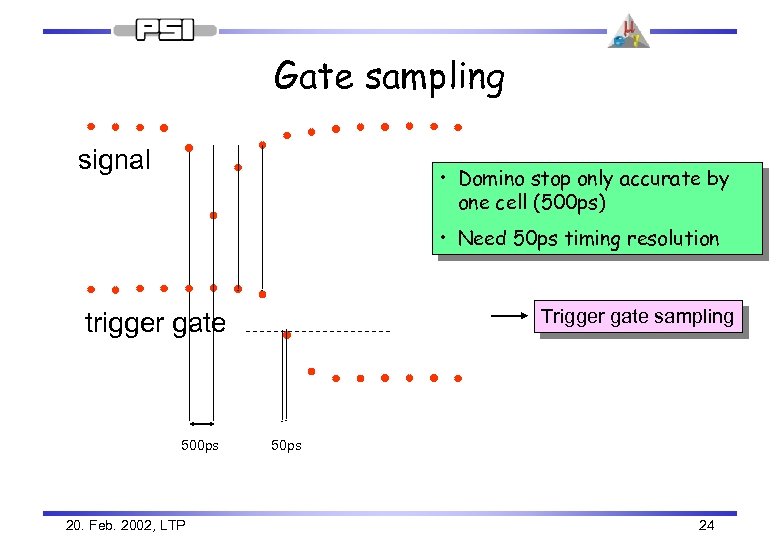

Gate sampling signal • Domino stop only accurate by one cell (500 ps) • Need 50 ps timing resolution Trigger gate sampling trigger gate 500 ps 20. Feb. 2002, LTP 50 ps 24

Gate sampling signal • Domino stop only accurate by one cell (500 ps) • Need 50 ps timing resolution Trigger gate sampling trigger gate 500 ps 20. Feb. 2002, LTP 50 ps 24

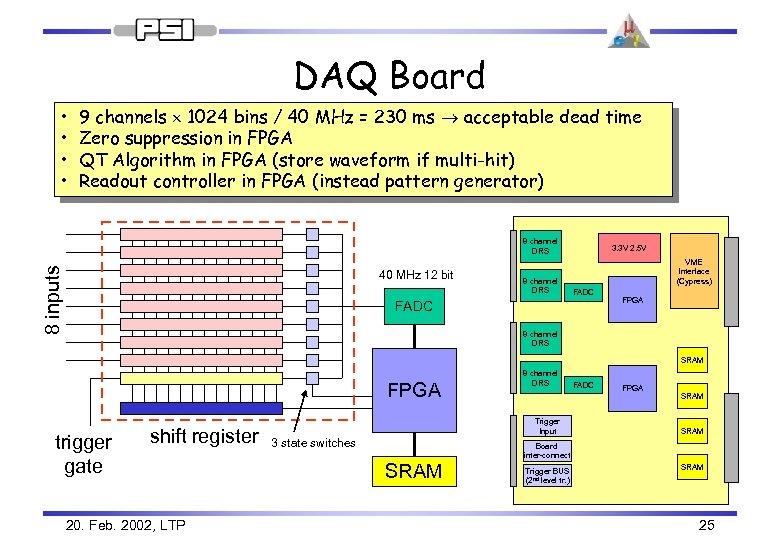

DAQ Board • • 9 channels 1024 bins / 40 MHz = 230 ms acceptable dead time Zero suppression in FPGA QT Algorithm in FPGA (store waveform if multi-hit) Readout controller in FPGA (instead pattern generator) 8 inputs 8 channel DRS 40 MHz 12 bit 8 channel DRS 3. 3 V 2. 5 V VME Interface (Cypress) FADC FPGA 8 channel DRS SRAM FPGA trigger gate shift register 20. Feb. 2002, LTP 8 channel DRS Trigger Input 3 state switches FADC FPGA SRAM Board inter-connect SRAM Trigger BUS (2 nd level tr. ) SRAM 25

DAQ Board • • 9 channels 1024 bins / 40 MHz = 230 ms acceptable dead time Zero suppression in FPGA QT Algorithm in FPGA (store waveform if multi-hit) Readout controller in FPGA (instead pattern generator) 8 inputs 8 channel DRS 40 MHz 12 bit 8 channel DRS 3. 3 V 2. 5 V VME Interface (Cypress) FADC FPGA 8 channel DRS SRAM FPGA trigger gate shift register 20. Feb. 2002, LTP 8 channel DRS Trigger Input 3 state switches FADC FPGA SRAM Board inter-connect SRAM Trigger BUS (2 nd level tr. ) SRAM 25

Status DRS • Simulation finished in AMS 0. 35 m process • Layout started • Switch to 0. 25 m process • First version summer ’ 02 • Readout with trigger prototype board • Costs per channel: ~25$ (board) + 6$ (chip) 20. Feb. 2002, LTP

Status DRS • Simulation finished in AMS 0. 35 m process • Layout started • Switch to 0. 25 m process • First version summer ’ 02 • Readout with trigger prototype board • Costs per channel: ~25$ (board) + 6$ (chip) 20. Feb. 2002, LTP

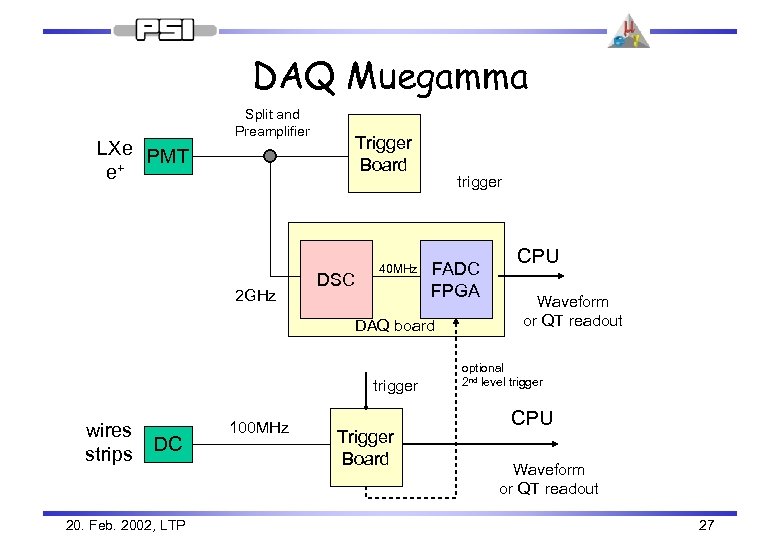

DAQ Muegamma LXe PMT e+ Split and Preamplifier 2 GHz Trigger Board DSC 40 MHz trigger FADC FPGA DAQ board trigger wires strips DC 20. Feb. 2002, LTP 100 MHz Trigger Board CPU Waveform or QT readout optional 2 nd level trigger CPU Waveform or QT readout 27

DAQ Muegamma LXe PMT e+ Split and Preamplifier 2 GHz Trigger Board DSC 40 MHz trigger FADC FPGA DAQ board trigger wires strips DC 20. Feb. 2002, LTP 100 MHz Trigger Board CPU Waveform or QT readout optional 2 nd level trigger CPU Waveform or QT readout 27

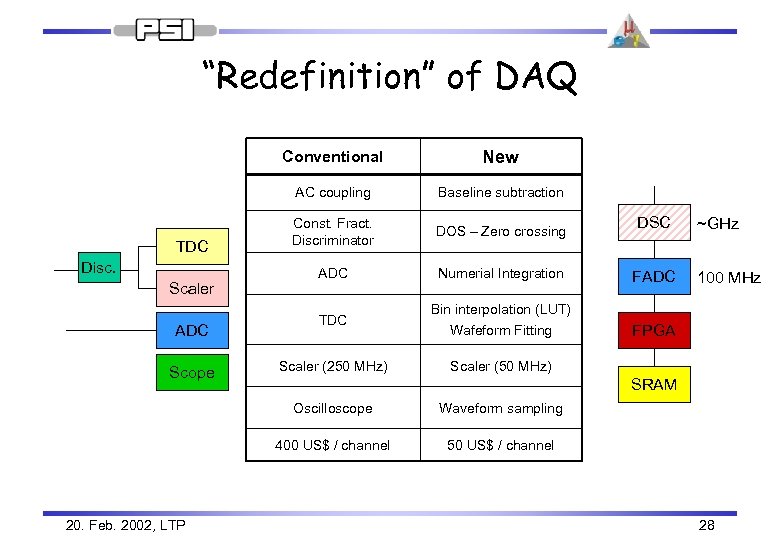

“Redefinition” of DAQ Conventional AC coupling TDC Disc. Scaler ADC Scope New Baseline subtraction Const. Fract. Discriminator DOS – Zero crossing ADC Numerial Integration FADC TDC Bin interpolation (LUT) Wafeform Fitting FPGA Scaler (250 MHz) Scaler (50 MHz) ~GHz 100 MHz SRAM Oscilloscope Waveform sampling 400 US$ / channel 20. Feb. 2002, LTP DSC 50 US$ / channel 28

“Redefinition” of DAQ Conventional AC coupling TDC Disc. Scaler ADC Scope New Baseline subtraction Const. Fract. Discriminator DOS – Zero crossing ADC Numerial Integration FADC TDC Bin interpolation (LUT) Wafeform Fitting FPGA Scaler (250 MHz) Scaler (50 MHz) ~GHz 100 MHz SRAM Oscilloscope Waveform sampling 400 US$ / channel 20. Feb. 2002, LTP DSC 50 US$ / channel 28

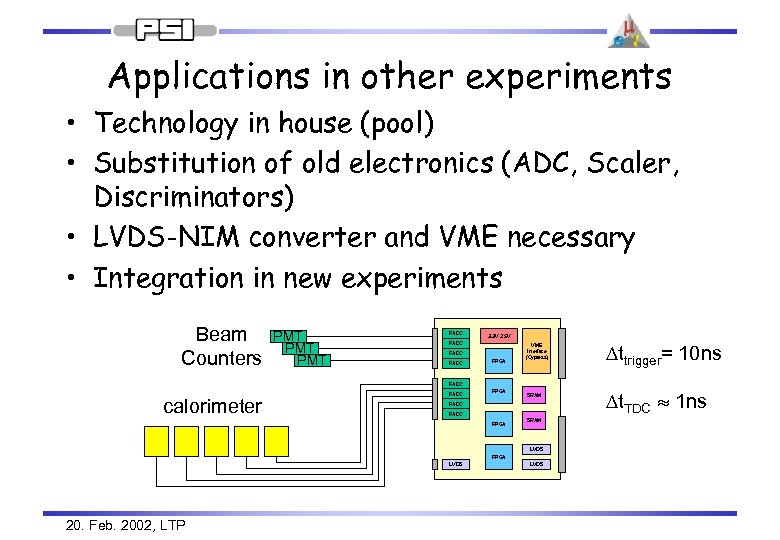

Applications in other experiments • Technology in house (pool) • Substitution of old electronics (ADC, Scaler, Discriminators) • LVDS-NIM converter and VME necessary • Integration in new experiments Beam Counters PMT PMT FADC 3. 3 V 2. 5 V FADC FPGA VME Interface (Cypress) Dttrigger= 10 ns FADC calorimeter FADC FPGA SRAM LVDS FPGA LVDS 20. Feb. 2002, LTP LVDS Dt. TDC 1 ns

Applications in other experiments • Technology in house (pool) • Substitution of old electronics (ADC, Scaler, Discriminators) • LVDS-NIM converter and VME necessary • Integration in new experiments Beam Counters PMT PMT FADC 3. 3 V 2. 5 V FADC FPGA VME Interface (Cypress) Dttrigger= 10 ns FADC calorimeter FADC FPGA SRAM LVDS FPGA LVDS 20. Feb. 2002, LTP LVDS Dt. TDC 1 ns

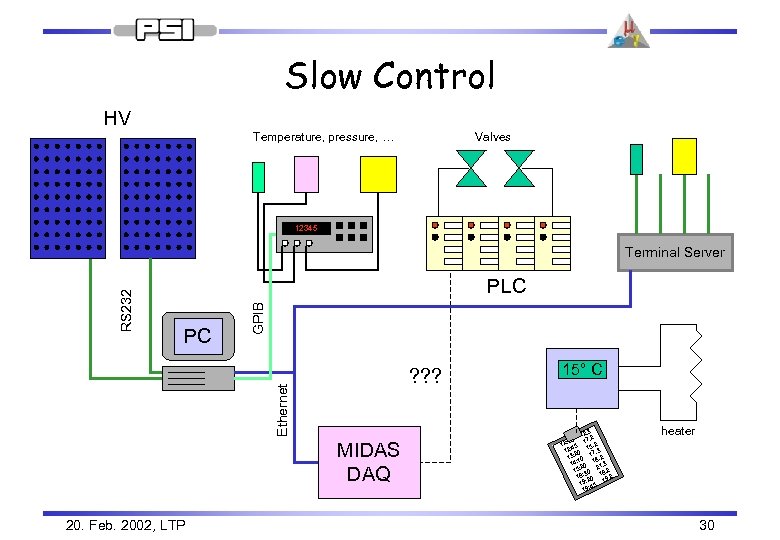

Slow Control HV Temperature, pressure, … Valves 12345 PLC ? ? ? Ethernet PC GPIB RS 232 Terminal Server MIDAS DAQ 20. Feb. 2002, LTP 15° C 3 12. 2 30 17. 2 12: 45 15. 3 12: 20 17. 2 13: 10 16. 3 14: 20 21. 2 15: 30 18. 2 18: 20 19. 19: 45 9: 1 heater 30

Slow Control HV Temperature, pressure, … Valves 12345 PLC ? ? ? Ethernet PC GPIB RS 232 Terminal Server MIDAS DAQ 20. Feb. 2002, LTP 15° C 3 12. 2 30 17. 2 12: 45 15. 3 12: 20 17. 2 13: 10 16. 3 14: 20 21. 2 15: 30 18. 2 18: 20 19. 19: 45 9: 1 heater 30

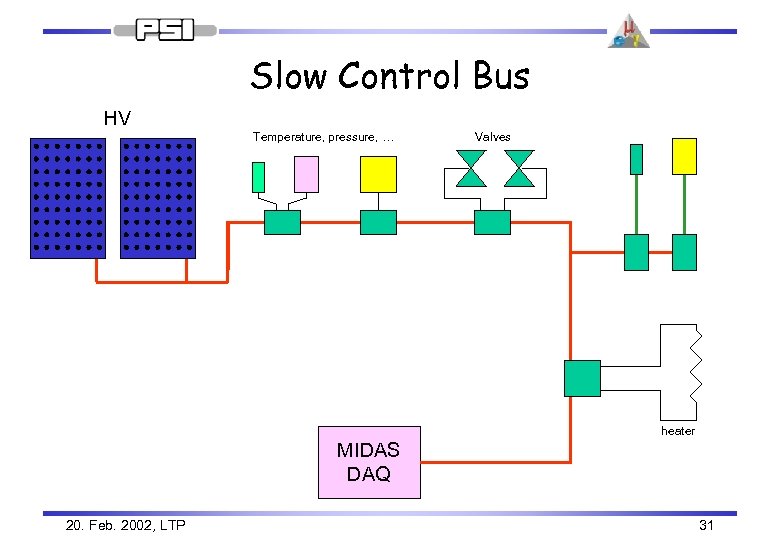

Slow Control Bus HV Temperature, pressure, … Valves heater MIDAS DAQ 20. Feb. 2002, LTP 31

Slow Control Bus HV Temperature, pressure, … Valves heater MIDAS DAQ 20. Feb. 2002, LTP 31

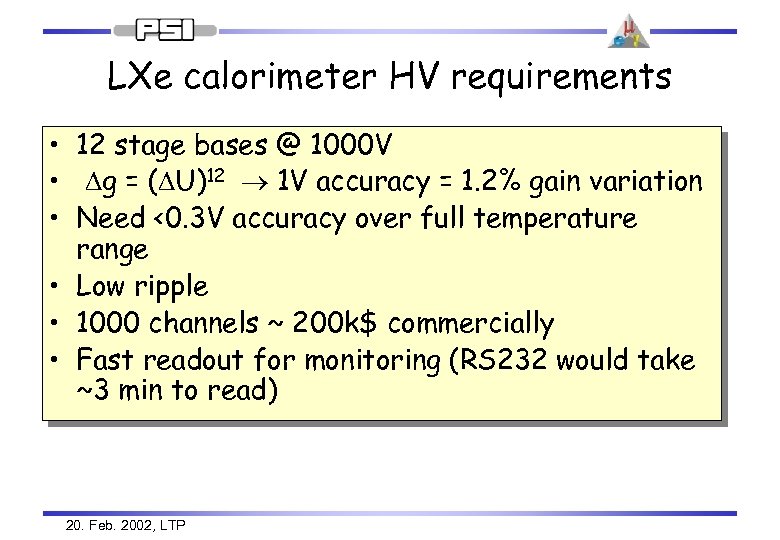

LXe calorimeter HV requirements • 12 stage bases @ 1000 V • Dg = (DU)12 1 V accuracy = 1. 2% gain variation • Need <0. 3 V accuracy over full temperature range • Low ripple • 1000 channels ~ 200 k$ commercially • Fast readout for monitoring (RS 232 would take ~3 min to read) 20. Feb. 2002, LTP

LXe calorimeter HV requirements • 12 stage bases @ 1000 V • Dg = (DU)12 1 V accuracy = 1. 2% gain variation • Need <0. 3 V accuracy over full temperature range • Low ripple • 1000 channels ~ 200 k$ commercially • Fast readout for monitoring (RS 232 would take ~3 min to read) 20. Feb. 2002, LTP

Field Bus Solutions • CAN, Profibus, LON available • Node with ADC ~100$ • Interoperatibility not guaranteed • Protocol overhead • Local CPU? User programmable? • How to integrate in HV (CAEN use CAENET) Reinhard Schmidt 20. Feb. 2002, LTP 33

Field Bus Solutions • CAN, Profibus, LON available • Node with ADC ~100$ • Interoperatibility not guaranteed • Protocol overhead • Local CPU? User programmable? • How to integrate in HV (CAEN use CAENET) Reinhard Schmidt 20. Feb. 2002, LTP 33

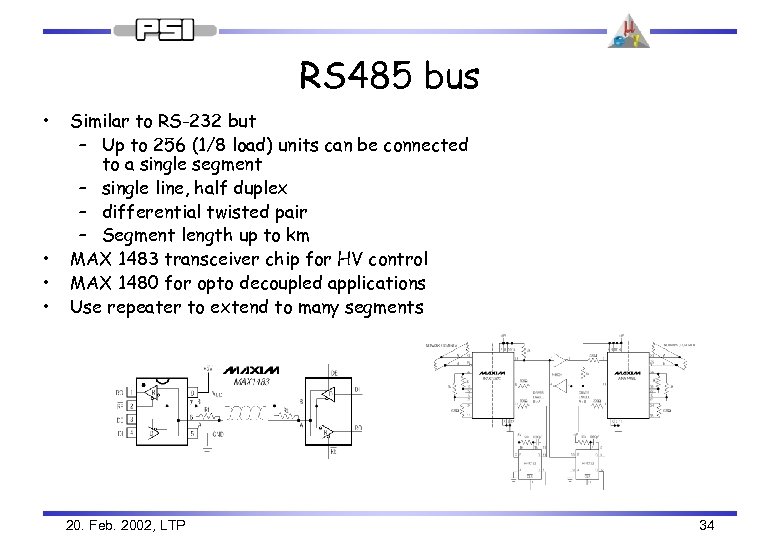

RS 485 bus • • Similar to RS-232 but – Up to 256 (1/8 load) units can be connected to a single segment – single line, half duplex – differential twisted pair – Segment length up to km MAX 1483 transceiver chip for HV control MAX 1480 for opto decoupled applications Use repeater to extend to many segments 20. Feb. 2002, LTP 34

RS 485 bus • • Similar to RS-232 but – Up to 256 (1/8 load) units can be connected to a single segment – single line, half duplex – differential twisted pair – Segment length up to km MAX 1483 transceiver chip for HV control MAX 1480 for opto decoupled applications Use repeater to extend to many segments 20. Feb. 2002, LTP 34

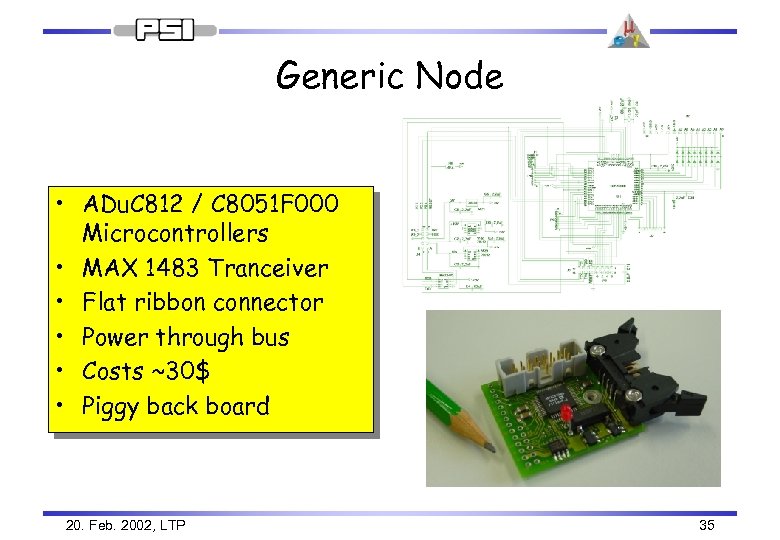

Generic Node • ADu. C 812 / C 8051 F 000 Microcontrollers • MAX 1483 Tranceiver • Flat ribbon connector • Power through bus • Costs ~30$ • Piggy back board 20. Feb. 2002, LTP 35

Generic Node • ADu. C 812 / C 8051 F 000 Microcontrollers • MAX 1483 Tranceiver • Flat ribbon connector • Power through bus • Costs ~30$ • Piggy back board 20. Feb. 2002, LTP 35

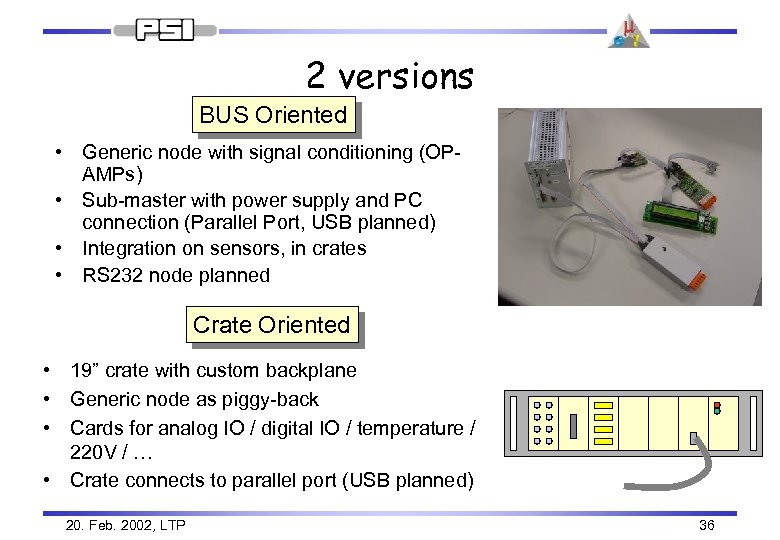

2 versions BUS Oriented • Generic node with signal conditioning (OPAMPs) • Sub-master with power supply and PC connection (Parallel Port, USB planned) • Integration on sensors, in crates • RS 232 node planned Crate Oriented • 19” crate with custom backplane • Generic node as piggy-back • Cards for analog IO / digital IO / temperature / 220 V / … • Crate connects to parallel port (USB planned) 20. Feb. 2002, LTP 36

2 versions BUS Oriented • Generic node with signal conditioning (OPAMPs) • Sub-master with power supply and PC connection (Parallel Port, USB planned) • Integration on sensors, in crates • RS 232 node planned Crate Oriented • 19” crate with custom backplane • Generic node as piggy-back • Cards for analog IO / digital IO / temperature / 220 V / … • Crate connects to parallel port (USB planned) 20. Feb. 2002, LTP 36

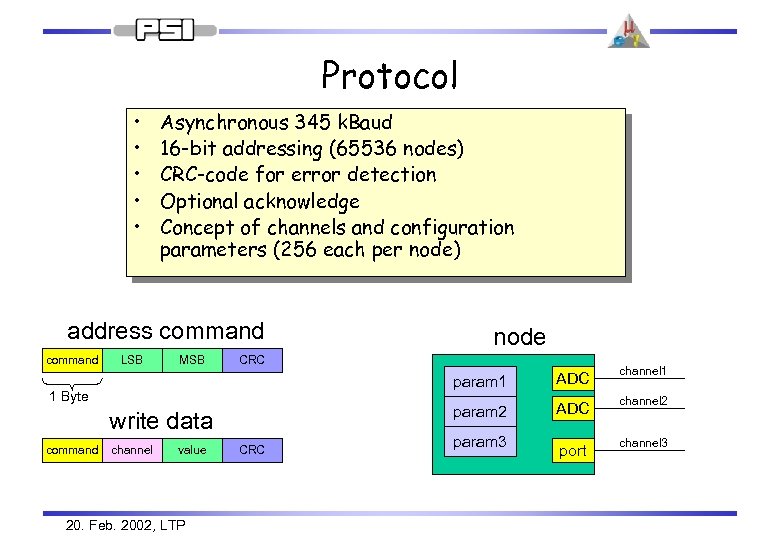

Protocol • • • Asynchronous 345 k. Baud 16 -bit addressing (65536 nodes) CRC-code for error detection Optional acknowledge Concept of channels and configuration parameters (256 each per node) address command LSB MSB CRC param 1 write data channel value 20. Feb. 2002, LTP CRC ADC channel 1 param 2 1 Byte command node ADC channel 2 port channel 3 param 3

Protocol • • • Asynchronous 345 k. Baud 16 -bit addressing (65536 nodes) CRC-code for error detection Optional acknowledge Concept of channels and configuration parameters (256 each per node) address command LSB MSB CRC param 1 write data channel value 20. Feb. 2002, LTP CRC ADC channel 1 param 2 1 Byte command node ADC channel 2 port channel 3 param 3

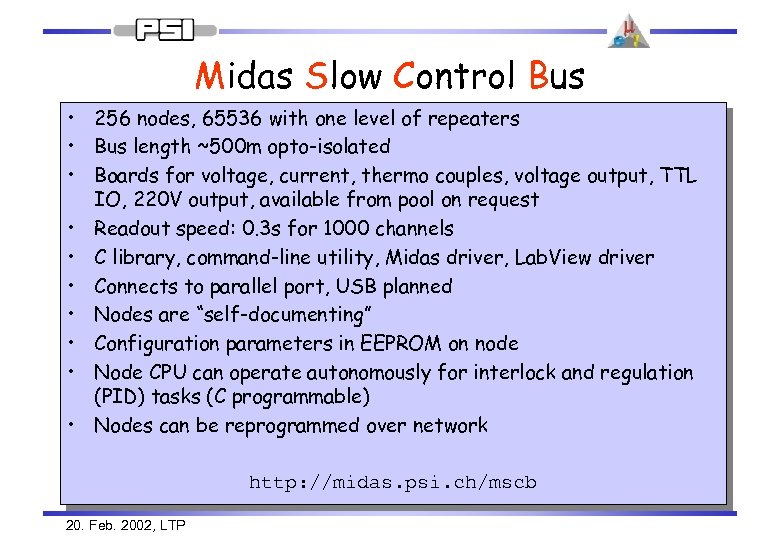

Midas Slow Control Bus • 256 nodes, 65536 with one level of repeaters • Bus length ~500 m opto-isolated • Boards for voltage, current, thermo couples, voltage output, TTL IO, 220 V output, available from pool on request • Readout speed: 0. 3 s for 1000 channels • C library, command-line utility, Midas driver, Lab. View driver • Connects to parallel port, USB planned • Nodes are “self-documenting” • Configuration parameters in EEPROM on node • Node CPU can operate autonomously for interlock and regulation (PID) tasks (C programmable) • Nodes can be reprogrammed over network http: //midas. psi. ch/mscb 20. Feb. 2002, LTP

Midas Slow Control Bus • 256 nodes, 65536 with one level of repeaters • Bus length ~500 m opto-isolated • Boards for voltage, current, thermo couples, voltage output, TTL IO, 220 V output, available from pool on request • Readout speed: 0. 3 s for 1000 channels • C library, command-line utility, Midas driver, Lab. View driver • Connects to parallel port, USB planned • Nodes are “self-documenting” • Configuration parameters in EEPROM on node • Node CPU can operate autonomously for interlock and regulation (PID) tasks (C programmable) • Nodes can be reprogrammed over network http: //midas. psi. ch/mscb 20. Feb. 2002, LTP

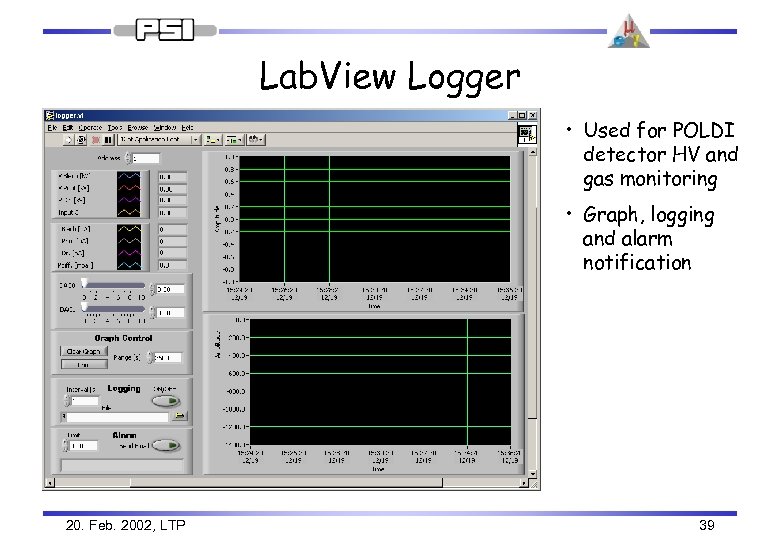

Lab. View Logger • Used for POLDI detector HV and gas monitoring • Graph, logging and alarm notification 20. Feb. 2002, LTP 39

Lab. View Logger • Used for POLDI detector HV and gas monitoring • Graph, logging and alarm notification 20. Feb. 2002, LTP 39

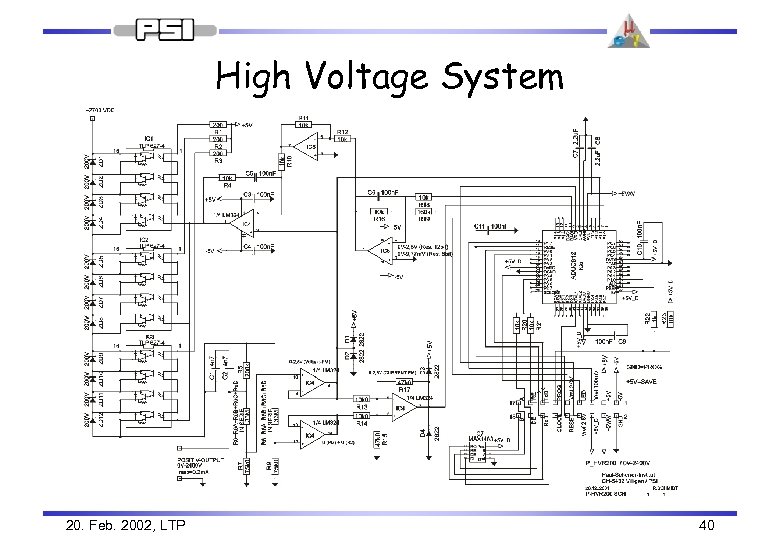

High Voltage System 20. Feb. 2002, LTP 40

High Voltage System 20. Feb. 2002, LTP 40

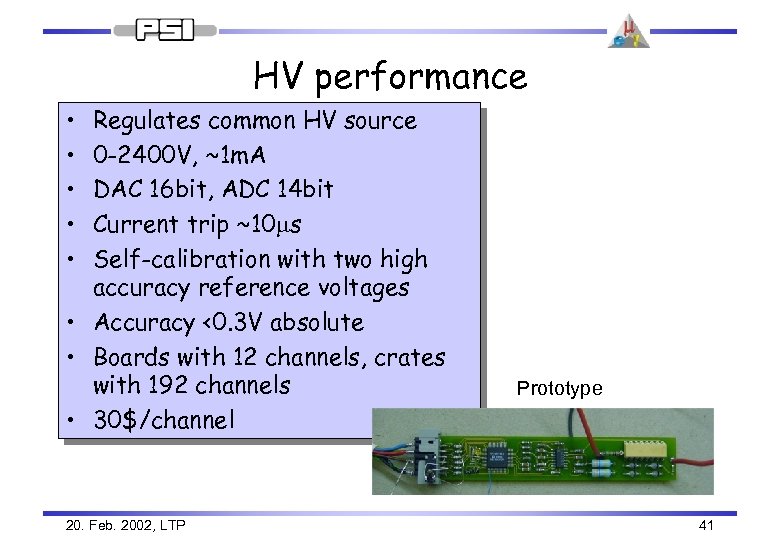

HV performance • • • Regulates common HV source 0 -2400 V, ~1 m. A DAC 16 bit, ADC 14 bit Current trip ~10 ms Self-calibration with two high accuracy reference voltages • Accuracy <0. 3 V absolute • Boards with 12 channels, crates with 192 channels • 30$/channel 20. Feb. 2002, LTP Prototype 41

HV performance • • • Regulates common HV source 0 -2400 V, ~1 m. A DAC 16 bit, ADC 14 bit Current trip ~10 ms Self-calibration with two high accuracy reference voltages • Accuracy <0. 3 V absolute • Boards with 12 channels, crates with 192 channels • 30$/channel 20. Feb. 2002, LTP Prototype 41

Conclusions • • Lots of new electronics for Muegamma Can be useful for other experiments Knowledge and support in-house Open to suggestions and modifications Credits to Reinhard Schmidt and Peter Dick 20. Feb. 2002, LTP

Conclusions • • Lots of new electronics for Muegamma Can be useful for other experiments Knowledge and support in-house Open to suggestions and modifications Credits to Reinhard Schmidt and Peter Dick 20. Feb. 2002, LTP

Muegamma Web Site Transparencies: http: //meg. psi. ch/doc/talks/s_ritt/feb 02_psi Cake: http: //kochbuch. unix-ag. uni-kl. de/bin/rezept? 17731 20. Feb. 2002, LTP 43

Muegamma Web Site Transparencies: http: //meg. psi. ch/doc/talks/s_ritt/feb 02_psi Cake: http: //kochbuch. unix-ag. uni-kl. de/bin/rezept? 17731 20. Feb. 2002, LTP 43