2b97b6927d53ebaf123bc802b4e06baa.ppt

- Количество слайдов: 14

Electronics and Data Acquisition system for prototype INO-ICAL detector A. Behere 1, V. B. Chandratre 1, S. D. Kalmani 2, N. K. Mondal 2, P. K. Mukhopadhyay 1, B. K. Nagesh 2, S. K. Rao 2, L. V. Reddy 2, M. N. Saraf 2, B. Satyanarayana 2, R. S. Shastrakar 1, R. R. Shinde 2, *S. S. Upadhya 2 1 Electronics Division, BARC, Mumbai ; 2 DHEP, TIFR, Mumbai. * email: upadhya@tifr. res. in l l Presented by Prof Vivek Datar, NPD, BARC OBJECTIVES: Feasibility study of INO prototype detector ( RPC ) of dimension 1 m 3 Fast development of electronics to study the detector performance Ø Ø Ø Ø 15 th Dec, 2007 Outline of Talk: Introduction Experimental set up Front end Analog Electronics Trigger logic Software Present configuration of Electronics setup Modules developed in-house Performance and Conclusion DAE-SNP 07 S. S. Upadhya 1

Electronics and Data Acquisition system for prototype INO-ICAL detector A. Behere 1, V. B. Chandratre 1, S. D. Kalmani 2, N. K. Mondal 2, P. K. Mukhopadhyay 1, B. K. Nagesh 2, S. K. Rao 2, L. V. Reddy 2, M. N. Saraf 2, B. Satyanarayana 2, R. S. Shastrakar 1, R. R. Shinde 2, *S. S. Upadhya 2 1 Electronics Division, BARC, Mumbai ; 2 DHEP, TIFR, Mumbai. * email: upadhya@tifr. res. in l l Presented by Prof Vivek Datar, NPD, BARC OBJECTIVES: Feasibility study of INO prototype detector ( RPC ) of dimension 1 m 3 Fast development of electronics to study the detector performance Ø Ø Ø Ø 15 th Dec, 2007 Outline of Talk: Introduction Experimental set up Front end Analog Electronics Trigger logic Software Present configuration of Electronics setup Modules developed in-house Performance and Conclusion DAE-SNP 07 S. S. Upadhya 1

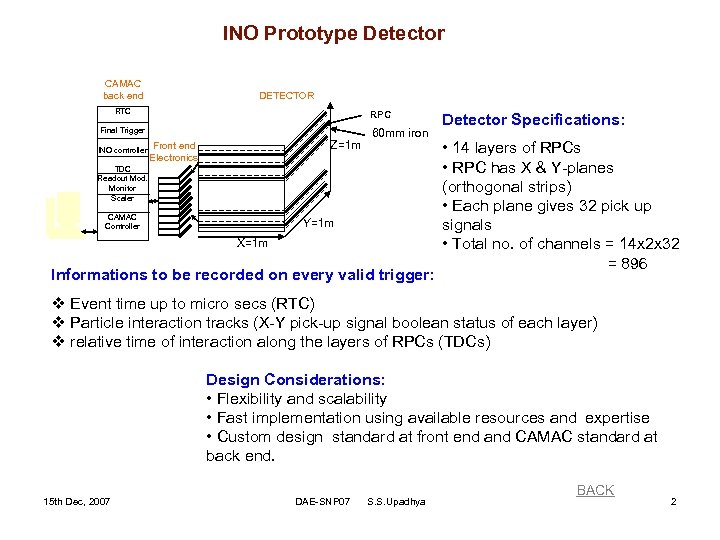

INO Prototype Detector CAMAC back end DETECTOR RTC RPC Final Trigger INO controller Z=1 m Front end Electronics 60 mm iron TDC Readout Mod. Monitor Scaler CAMAC Controller Y=1 m X=1 m Informations to be recorded on every valid trigger: Detector Specifications: • 14 layers of RPCs • RPC has X & Y-planes (orthogonal strips) • Each plane gives 32 pick up signals • Total no. of channels = 14 x 2 x 32 = 896 v Event time up to micro secs (RTC) v Particle interaction tracks (X-Y pick-up signal boolean status of each layer) v relative time of interaction along the layers of RPCs (TDCs) Design Considerations: • Flexibility and scalability • Fast implementation using available resources and expertise • Custom design standard at front end and CAMAC standard at back end. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 2

INO Prototype Detector CAMAC back end DETECTOR RTC RPC Final Trigger INO controller Z=1 m Front end Electronics 60 mm iron TDC Readout Mod. Monitor Scaler CAMAC Controller Y=1 m X=1 m Informations to be recorded on every valid trigger: Detector Specifications: • 14 layers of RPCs • RPC has X & Y-planes (orthogonal strips) • Each plane gives 32 pick up signals • Total no. of channels = 14 x 2 x 32 = 896 v Event time up to micro secs (RTC) v Particle interaction tracks (X-Y pick-up signal boolean status of each layer) v relative time of interaction along the layers of RPCs (TDCs) Design Considerations: • Flexibility and scalability • Fast implementation using available resources and expertise • Custom design standard at front end and CAMAC standard at back end. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 2

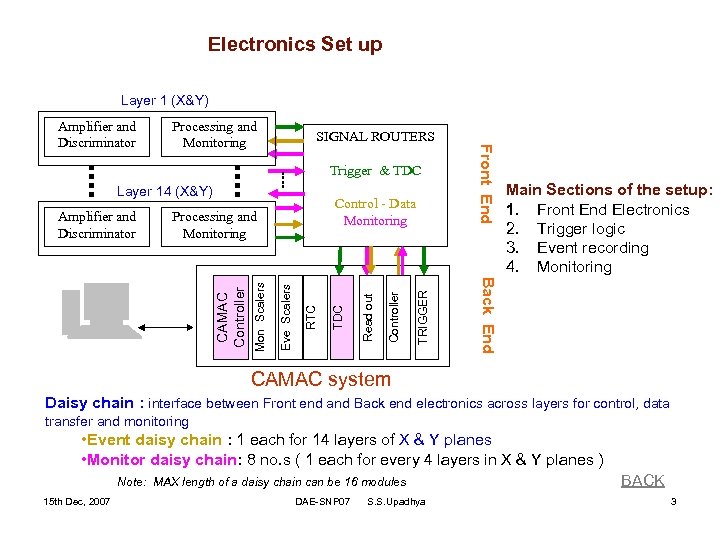

Electronics Set up Layer 1 (X&Y) Processing and Monitoring SIGNAL ROUTERS Trigger & TDC Layer 14 (X&Y) TRIGGER Controller Read out RTC Eve Scalers Mon Scalers Main Sections of the setup: 1. Front End Electronics 2. Trigger logic 3. Event recording 4. Monitoring Back End TDC Control - Data Monitoring Processing and Monitoring CAMAC Controller Amplifier and Discriminator Front End Amplifier and Discriminator CAMAC system Daisy chain : interface between Front end and Back end electronics across layers for control, data transfer and monitoring • Event daisy chain : 1 each for 14 layers of X & Y planes • Monitor daisy chain: 8 no. s ( 1 each for every 4 layers in X & Y planes ) Note: MAX length of a daisy chain can be 16 modules 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 3

Electronics Set up Layer 1 (X&Y) Processing and Monitoring SIGNAL ROUTERS Trigger & TDC Layer 14 (X&Y) TRIGGER Controller Read out RTC Eve Scalers Mon Scalers Main Sections of the setup: 1. Front End Electronics 2. Trigger logic 3. Event recording 4. Monitoring Back End TDC Control - Data Monitoring Processing and Monitoring CAMAC Controller Amplifier and Discriminator Front End Amplifier and Discriminator CAMAC system Daisy chain : interface between Front end and Back end electronics across layers for control, data transfer and monitoring • Event daisy chain : 1 each for 14 layers of X & Y planes • Monitor daisy chain: 8 no. s ( 1 each for every 4 layers in X & Y planes ) Note: MAX length of a daisy chain can be 16 modules 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 3

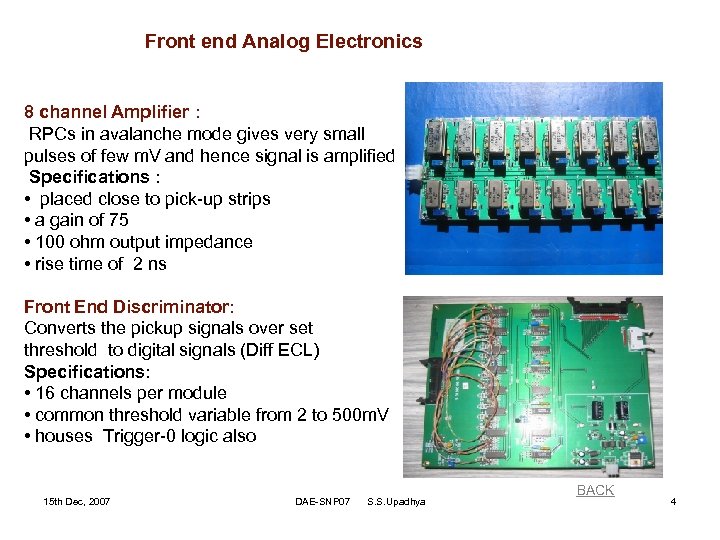

Front end Analog Electronics 8 channel Amplifier : RPCs in avalanche mode gives very small pulses of few m. V and hence signal is amplified Specifications : • placed close to pick-up strips • a gain of 75 • 100 ohm output impedance • rise time of 2 ns Front End Discriminator: Converts the pickup signals over set threshold to digital signals (Diff ECL) Specifications: • 16 channels per module • common threshold variable from 2 to 500 m. V • houses Trigger-0 logic also 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 4

Front end Analog Electronics 8 channel Amplifier : RPCs in avalanche mode gives very small pulses of few m. V and hence signal is amplified Specifications : • placed close to pick-up strips • a gain of 75 • 100 ohm output impedance • rise time of 2 ns Front End Discriminator: Converts the pickup signals over set threshold to digital signals (Diff ECL) Specifications: • 16 channels per module • common threshold variable from 2 to 500 m. V • houses Trigger-0 logic also 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 4

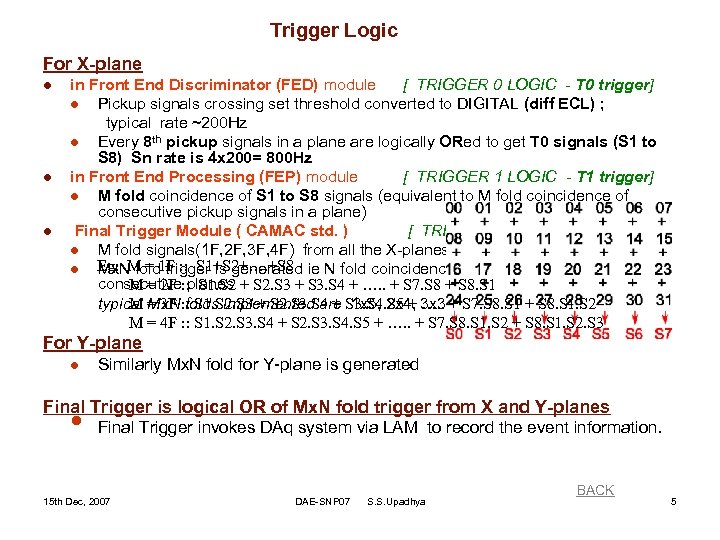

Trigger Logic For X-plane l l l in Front End Discriminator (FED) module [ TRIGGER 0 LOGIC - T 0 trigger] l Pickup signals crossing set threshold converted to DIGITAL (diff ECL) ; typical rate ~200 Hz l Every 8 th pickup signals in a plane are logically ORed to get T 0 signals (S 1 to S 8) Sn rate is 4 x 200= 800 Hz in Front End Processing (FEP) module [ TRIGGER 1 LOGIC - T 1 trigger] l M fold coincidence of S 1 to S 8 signals (equivalent to M fold coincidence of consecutive pickup signals in a plane) Final Trigger Module ( CAMAC std. ) [ TRIGGER 2 LOGIC - T 2 trigger ] l M fold signals(1 F, 2 F, 3 F, 4 F) from all the X-planes are the inputs (diff LVDS) Eg: M = 1 F : : S 1+S 2+…. +S 8 ie N fold coincidence of M fold (T 1) triggers from l Mx. N fold trigger is generated consecutive: : S 1. S 2 + S 2. S 3 + S 3. S 4 + …. . + S 7. S 8 + S 8. S 1 M = 2 F planes typical = 3 F : : S 1. S 2. S 3 + S 2. S 3. S 4 + S 3. S 4. S 5 + 3 x 3, +4 x 2 M Mx. N folds implemented are 1 x 5, 2 x 4, …. . S 7. S 8. S 1 + S 8. S 1. S 2 M = 4 F : : S 1. S 2. S 3. S 4 + S 2. S 3. S 4. S 5 + …. . + S 7. S 8. S 1. S 2 + S 8. S 1. S 2. S 3 For Y-plane l Similarly Mx. N fold for Y-plane is generated Final Trigger is logical OR of Mx. N fold trigger from X and Y-planes • Final Trigger invokes DAq system via LAM to record the event information. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 5

Trigger Logic For X-plane l l l in Front End Discriminator (FED) module [ TRIGGER 0 LOGIC - T 0 trigger] l Pickup signals crossing set threshold converted to DIGITAL (diff ECL) ; typical rate ~200 Hz l Every 8 th pickup signals in a plane are logically ORed to get T 0 signals (S 1 to S 8) Sn rate is 4 x 200= 800 Hz in Front End Processing (FEP) module [ TRIGGER 1 LOGIC - T 1 trigger] l M fold coincidence of S 1 to S 8 signals (equivalent to M fold coincidence of consecutive pickup signals in a plane) Final Trigger Module ( CAMAC std. ) [ TRIGGER 2 LOGIC - T 2 trigger ] l M fold signals(1 F, 2 F, 3 F, 4 F) from all the X-planes are the inputs (diff LVDS) Eg: M = 1 F : : S 1+S 2+…. +S 8 ie N fold coincidence of M fold (T 1) triggers from l Mx. N fold trigger is generated consecutive: : S 1. S 2 + S 2. S 3 + S 3. S 4 + …. . + S 7. S 8 + S 8. S 1 M = 2 F planes typical = 3 F : : S 1. S 2. S 3 + S 2. S 3. S 4 + S 3. S 4. S 5 + 3 x 3, +4 x 2 M Mx. N folds implemented are 1 x 5, 2 x 4, …. . S 7. S 8. S 1 + S 8. S 1. S 2 M = 4 F : : S 1. S 2. S 3. S 4 + S 2. S 3. S 4. S 5 + …. . + S 7. S 8. S 1. S 2 + S 8. S 1. S 2. S 3 For Y-plane l Similarly Mx. N fold for Y-plane is generated Final Trigger is logical OR of Mx. N fold trigger from X and Y-planes • Final Trigger invokes DAq system via LAM to record the event information. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 5

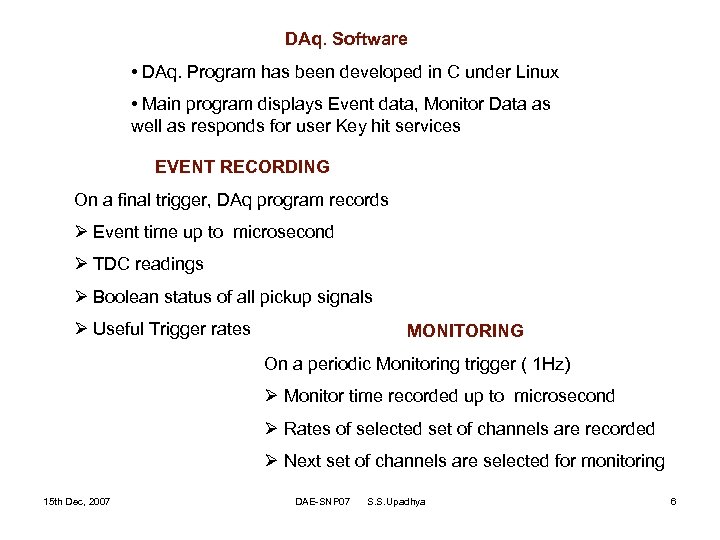

DAq. Software • DAq. Program has been developed in C under Linux • Main program displays Event data, Monitor Data as well as responds for user Key hit services EVENT RECORDING On a final trigger, DAq program records Ø Event time up to microsecond Ø TDC readings Ø Boolean status of all pickup signals Ø Useful Trigger rates MONITORING On a periodic Monitoring trigger ( 1 Hz) Ø Monitor time recorded up to microsecond Ø Rates of selected set of channels are recorded Ø Next set of channels are selected for monitoring 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 6

DAq. Software • DAq. Program has been developed in C under Linux • Main program displays Event data, Monitor Data as well as responds for user Key hit services EVENT RECORDING On a final trigger, DAq program records Ø Event time up to microsecond Ø TDC readings Ø Boolean status of all pickup signals Ø Useful Trigger rates MONITORING On a periodic Monitoring trigger ( 1 Hz) Ø Monitor time recorded up to microsecond Ø Rates of selected set of channels are recorded Ø Next set of channels are selected for monitoring 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 6

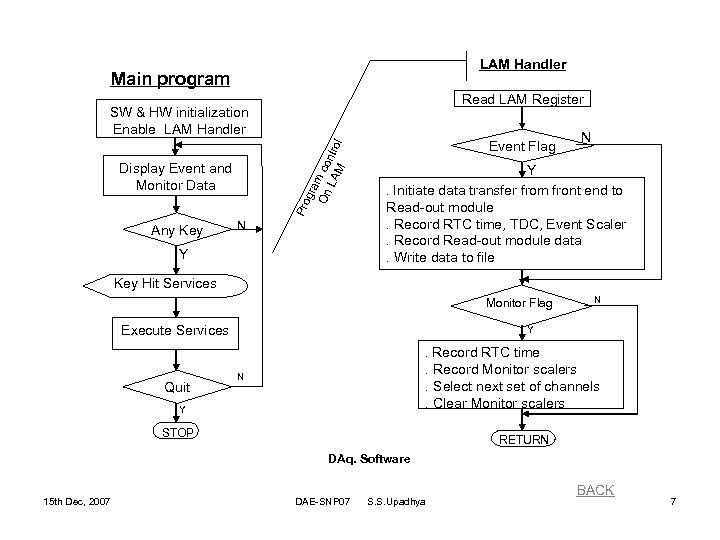

LAM Handler Main program Read LAM Register gra On m co LA ntro M l SW & HW initialization Enable LAM Handler Pro Display Event and Monitor Data Any Key N Y Event Flag N Y. Initiate data transfer from front end to Read-out module. Record RTC time, TDC, Event Scaler. Record Read-out module data. Write data to file Key Hit Services Monitor Flag Execute Services N Y . Record RTC time Quit . Record Monitor scalers. Select next set of channels. Clear Monitor scalers N Y STOP RETURN DAq. Software 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 7

LAM Handler Main program Read LAM Register gra On m co LA ntro M l SW & HW initialization Enable LAM Handler Pro Display Event and Monitor Data Any Key N Y Event Flag N Y. Initiate data transfer from front end to Read-out module. Record RTC time, TDC, Event Scaler. Record Read-out module data. Write data to file Key Hit Services Monitor Flag Execute Services N Y . Record RTC time Quit . Record Monitor scalers. Select next set of channels. Clear Monitor scalers N Y STOP RETURN DAq. Software 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya BACK 7

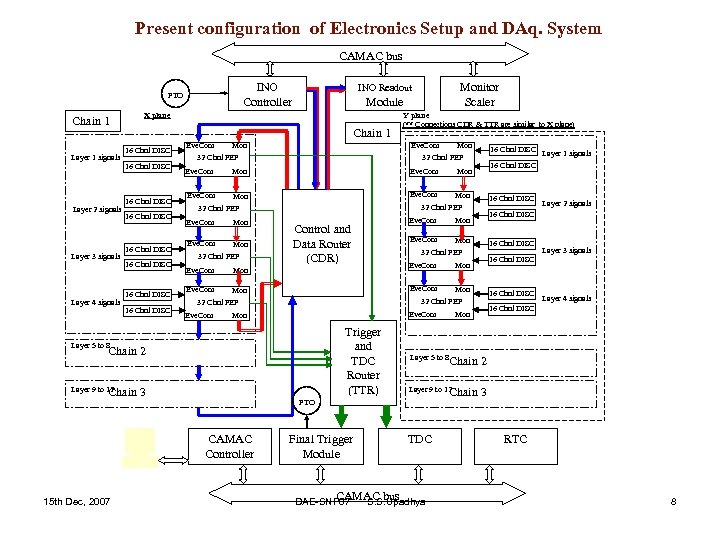

Present configuration of Electronics Setup and DAq. System CAMAC bus INO Controller FTO Layer 1 signals Layer 2 signals Layer 3 signals Layer 4 signals Module X plane Chain 1 16 Chnl DISC 16 Chnl DISC Eve. Com Mon 32 Chnl FEP Mon Eve. Com Mon 32 Chnl FEP Eve. Com Control and Data Router (CDR) Mon Eve. Com Mon 32 Chnl FEP 16 Chnl DISC Trigger and TDC Router (TTR) FTO Final Trigger Module 16 Chnl DISC Layer 4 signals 16 Chnl DISC Mon Layer 5 to 8 Chain 2 Layer 9 to 12 Chain TDC CAMAC bus S. S. Upadhya DAE-SNP 07 Layer 3 signals 16 Chnl DISC Mon Eve. Com Mon CAMAC Controller Mon Eve. Com Layer 2 signals 16 Chnl DISC Mon 32 Chnl FEP 3 16 Chnl DISC Eve. Com Mon Eve. Com Layer 1 signals 16 Chnl DISC Mon 32 Chnl FEP Chain 2 15 th Dec, 2007 16 Chnl DISC Eve. Com Layer 5 to 8 Layer 9 to 12 Chain Y plane (** Connections CDR & TTR are similar to X plane) Eve. Com Mon 32 Chnl FEP Eve. Com Monitor Scaler INO Readout 3 RTC 8

Present configuration of Electronics Setup and DAq. System CAMAC bus INO Controller FTO Layer 1 signals Layer 2 signals Layer 3 signals Layer 4 signals Module X plane Chain 1 16 Chnl DISC 16 Chnl DISC Eve. Com Mon 32 Chnl FEP Mon Eve. Com Mon 32 Chnl FEP Eve. Com Control and Data Router (CDR) Mon Eve. Com Mon 32 Chnl FEP 16 Chnl DISC Trigger and TDC Router (TTR) FTO Final Trigger Module 16 Chnl DISC Layer 4 signals 16 Chnl DISC Mon Layer 5 to 8 Chain 2 Layer 9 to 12 Chain TDC CAMAC bus S. S. Upadhya DAE-SNP 07 Layer 3 signals 16 Chnl DISC Mon Eve. Com Mon CAMAC Controller Mon Eve. Com Layer 2 signals 16 Chnl DISC Mon 32 Chnl FEP 3 16 Chnl DISC Eve. Com Mon Eve. Com Layer 1 signals 16 Chnl DISC Mon 32 Chnl FEP Chain 2 15 th Dec, 2007 16 Chnl DISC Eve. Com Layer 5 to 8 Layer 9 to 12 Chain Y plane (** Connections CDR & TTR are similar to X plane) Eve. Com Mon 32 Chnl FEP Eve. Com Monitor Scaler INO Readout 3 RTC 8

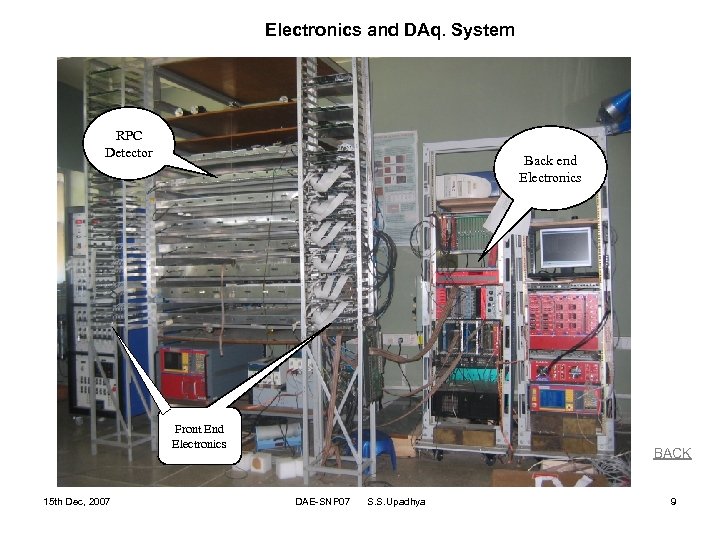

Electronics and DAq. System RPC Detector Back end Electronics Front End Electronics 15 th Dec, 2007 BACK DAE-SNP 07 S. S. Upadhya 9

Electronics and DAq. System RPC Detector Back end Electronics Front End Electronics 15 th Dec, 2007 BACK DAE-SNP 07 S. S. Upadhya 9

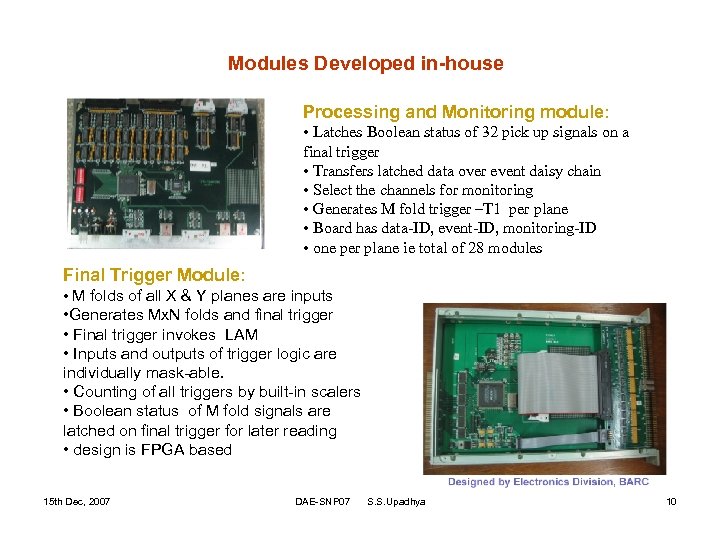

Modules Developed in-house Processing and Monitoring module: • Latches Boolean status of 32 pick up signals on a final trigger • Transfers latched data over event daisy chain • Select the channels for monitoring • Generates M fold trigger –T 1 per plane • Board has data-ID, event-ID, monitoring-ID • one per plane ie total of 28 modules Final Trigger Module: • M folds of all X & Y planes are inputs • Generates Mx. N folds and final trigger • Final trigger invokes LAM • Inputs and outputs of trigger logic are individually mask-able. • Counting of all triggers by built-in scalers • Boolean status of M fold signals are latched on final trigger for later reading • design is FPGA based 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 10

Modules Developed in-house Processing and Monitoring module: • Latches Boolean status of 32 pick up signals on a final trigger • Transfers latched data over event daisy chain • Select the channels for monitoring • Generates M fold trigger –T 1 per plane • Board has data-ID, event-ID, monitoring-ID • one per plane ie total of 28 modules Final Trigger Module: • M folds of all X & Y planes are inputs • Generates Mx. N folds and final trigger • Final trigger invokes LAM • Inputs and outputs of trigger logic are individually mask-able. • Counting of all triggers by built-in scalers • Boolean status of M fold signals are latched on final trigger for later reading • design is FPGA based 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 10

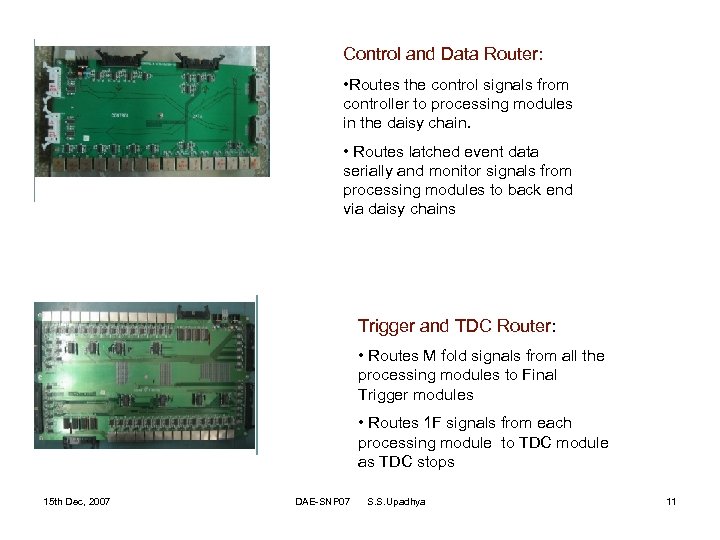

Control and Data Router: • Routes the control signals from controller to processing modules in the daisy chain. • Routes latched event data serially and monitor signals from processing modules to back end via daisy chains Trigger and TDC Router: • Routes M fold signals from all the processing modules to Final Trigger modules • Routes 1 F signals from each processing module to TDC module as TDC stops 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 11

Control and Data Router: • Routes the control signals from controller to processing modules in the daisy chain. • Routes latched event data serially and monitor signals from processing modules to back end via daisy chains Trigger and TDC Router: • Routes M fold signals from all the processing modules to Final Trigger modules • Routes 1 F signals from each processing module to TDC module as TDC stops 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 11

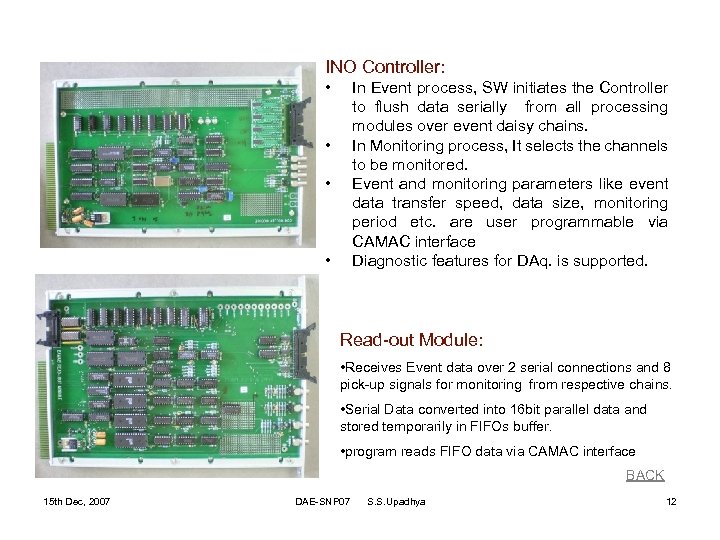

INO Controller: • In Event process, SW initiates the Controller to flush data serially from all processing modules over event daisy chains. In Monitoring process, It selects the channels to be monitored. Event and monitoring parameters like event data transfer speed, data size, monitoring period etc. are user programmable via CAMAC interface Diagnostic features for DAq. is supported. • • • Read-out Module: • Receives Event data over 2 serial connections and 8 pick-up signals for monitoring from respective chains. • Serial Data converted into 16 bit parallel data and stored temporarily in FIFOs buffer. • program reads FIFO data via CAMAC interface BACK 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 12

INO Controller: • In Event process, SW initiates the Controller to flush data serially from all processing modules over event daisy chains. In Monitoring process, It selects the channels to be monitored. Event and monitoring parameters like event data transfer speed, data size, monitoring period etc. are user programmable via CAMAC interface Diagnostic features for DAq. is supported. • • • Read-out Module: • Receives Event data over 2 serial connections and 8 pick-up signals for monitoring from respective chains. • Serial Data converted into 16 bit parallel data and stored temporarily in FIFOs buffer. • program reads FIFO data via CAMAC interface BACK 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 12

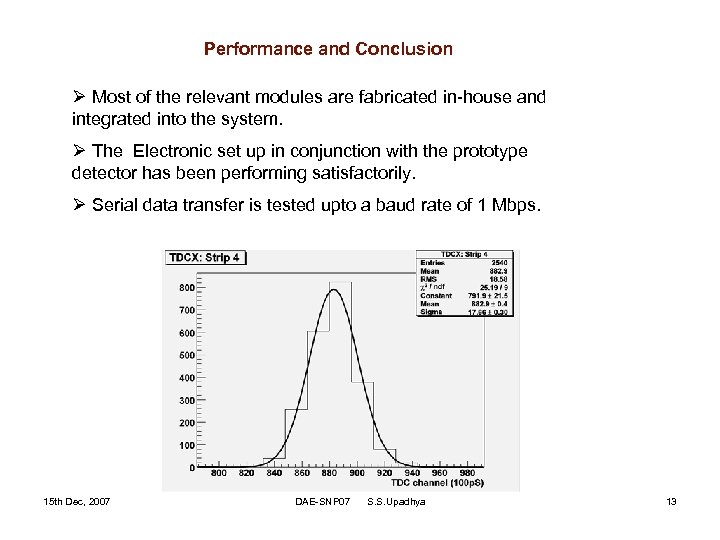

Performance and Conclusion Ø Most of the relevant modules are fabricated in-house and integrated into the system. Ø The Electronic set up in conjunction with the prototype detector has been performing satisfactorily. Ø Serial data transfer is tested upto a baud rate of 1 Mbps. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 13

Performance and Conclusion Ø Most of the relevant modules are fabricated in-house and integrated into the system. Ø The Electronic set up in conjunction with the prototype detector has been performing satisfactorily. Ø Serial data transfer is tested upto a baud rate of 1 Mbps. 15 th Dec, 2007 DAE-SNP 07 S. S. Upadhya 13

Electronics and Data Acquisition system for prototype INO-ICAL detector S. S. Upadhya , TIFR ( on behalf of INO collaboration ) l l OBJECTIVES: Feasibility study of INO prototype detector ( RPC ) of dimension 1 m 3 Fast development of electronics to study the detector performance Ø Ø Ø Ø 15 th Dec, 2007 Outline of Talk: Introduction Experimental set up Front end Analog Electronics Trigger logic Software Typical Electronics setup and DAq. System Modules developed in-house Performance and Conclusion DAE-SNP 07 S. S. Upadhya 16

Electronics and Data Acquisition system for prototype INO-ICAL detector S. S. Upadhya , TIFR ( on behalf of INO collaboration ) l l OBJECTIVES: Feasibility study of INO prototype detector ( RPC ) of dimension 1 m 3 Fast development of electronics to study the detector performance Ø Ø Ø Ø 15 th Dec, 2007 Outline of Talk: Introduction Experimental set up Front end Analog Electronics Trigger logic Software Typical Electronics setup and DAq. System Modules developed in-house Performance and Conclusion DAE-SNP 07 S. S. Upadhya 16