e7240aba72706ba6b5aa575b1d94880f.ppt

- Количество слайдов: 49

Electronics and DAQ system for INO-ICAL prototype detector (Presented by S. S. Upadhya, TIFR on behalf of INO collaboration) OBJECTIVE: l Feasibility study of INO prototype detector of dimension 1 m 3 ( glass RPC ) Which demanded Fast implementation of electronics to study its performance Outline of Talk: Ø Introduction Ø Electronics set up Ø Main Sections Ø Front End Electronics Ø Trigger logic Ø Back end Processing Ø Typical configuration & Modules developed Ø DAq. Software Ø Performance and results Ø VME transformation of DAQ 16 October, 2009 ASET talk - S. S. Upadhya

Electronics and DAQ system for INO-ICAL prototype detector (Presented by S. S. Upadhya, TIFR on behalf of INO collaboration) OBJECTIVE: l Feasibility study of INO prototype detector of dimension 1 m 3 ( glass RPC ) Which demanded Fast implementation of electronics to study its performance Outline of Talk: Ø Introduction Ø Electronics set up Ø Main Sections Ø Front End Electronics Ø Trigger logic Ø Back end Processing Ø Typical configuration & Modules developed Ø DAq. Software Ø Performance and results Ø VME transformation of DAQ 16 October, 2009 ASET talk - S. S. Upadhya

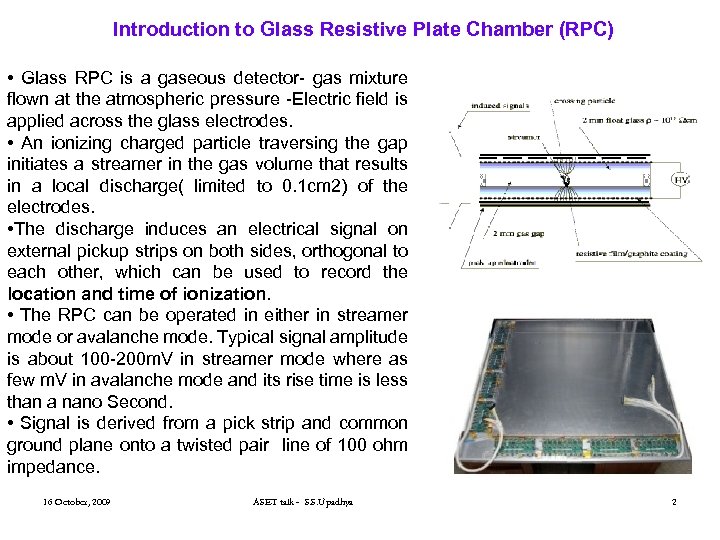

Introduction to Glass Resistive Plate Chamber (RPC) • Glass RPC is a gaseous detector- gas mixture flown at the atmospheric pressure -Electric field is applied across the glass electrodes. • An ionizing charged particle traversing the gap initiates a streamer in the gas volume that results in a local discharge( limited to 0. 1 cm 2) of the electrodes. • The discharge induces an electrical signal on external pickup strips on both sides, orthogonal to each other, which can be used to record the location and time of ionization. • The RPC can be operated in either in streamer mode or avalanche mode. Typical signal amplitude is about 100 -200 m. V in streamer mode where as few m. V in avalanche mode and its rise time is less than a nano Second. • Signal is derived from a pick strip and common ground plane onto a twisted pair line of 100 ohm impedance. 16 October, 2009 ASET talk - S. S. Upadhya 2

Introduction to Glass Resistive Plate Chamber (RPC) • Glass RPC is a gaseous detector- gas mixture flown at the atmospheric pressure -Electric field is applied across the glass electrodes. • An ionizing charged particle traversing the gap initiates a streamer in the gas volume that results in a local discharge( limited to 0. 1 cm 2) of the electrodes. • The discharge induces an electrical signal on external pickup strips on both sides, orthogonal to each other, which can be used to record the location and time of ionization. • The RPC can be operated in either in streamer mode or avalanche mode. Typical signal amplitude is about 100 -200 m. V in streamer mode where as few m. V in avalanche mode and its rise time is less than a nano Second. • Signal is derived from a pick strip and common ground plane onto a twisted pair line of 100 ohm impedance. 16 October, 2009 ASET talk - S. S. Upadhya 2

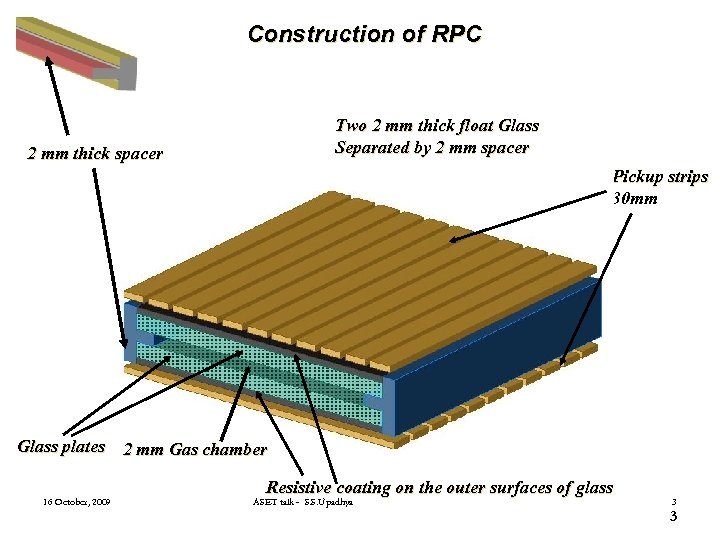

Construction of RPC Two 2 mm thick float Glass Separated by 2 mm spacer 2 mm thick spacer Pickup strips 30 mm Glass plates 2 mm Gas chamber 16 October, 2009 Resistive coating on the outer surfaces of glass ASET talk - S. S. Upadhya 3 3

Construction of RPC Two 2 mm thick float Glass Separated by 2 mm spacer 2 mm thick spacer Pickup strips 30 mm Glass plates 2 mm Gas chamber 16 October, 2009 Resistive coating on the outer surfaces of glass ASET talk - S. S. Upadhya 3 3

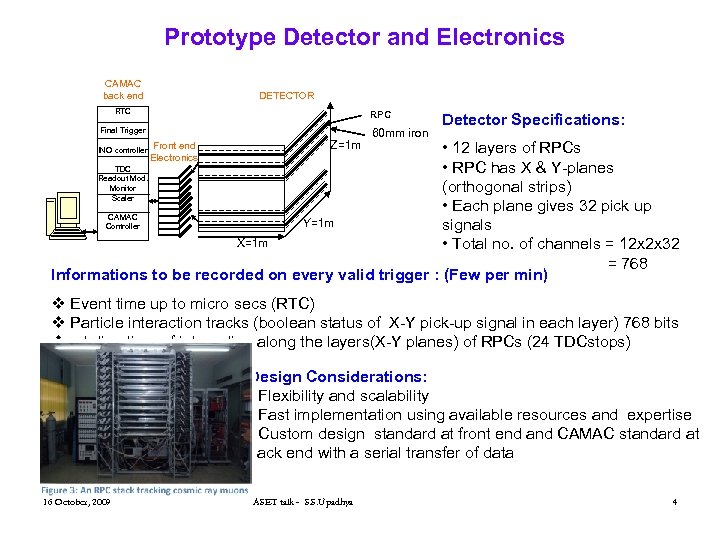

Prototype Detector and Electronics CAMAC back end DETECTOR RTC RPC Final Trigger Z=1 m 60 mm iron Detector Specifications: • 12 layers of RPCs TDC • RPC has X & Y-planes Readout Mod. Monitor (orthogonal strips) Scaler • Each plane gives 32 pick up CAMAC Y=1 m Controller signals X=1 m • Total no. of channels = 12 x 2 x 32 = 768 Informations to be recorded on every valid trigger : (Few per min) INO controller Front end Electronics v Event time up to micro secs (RTC) v Particle interaction tracks (boolean status of X-Y pick-up signal in each layer) 768 bits v relative time of interaction along the layers(X-Y planes) of RPCs (24 TDCstops) Design Considerations: • Flexibility and scalability • Fast implementation using available resources and expertise • Custom design standard at front end and CAMAC standard at back end with a serial transfer of data 16 October, 2009 ASET talk - S. S. Upadhya 4

Prototype Detector and Electronics CAMAC back end DETECTOR RTC RPC Final Trigger Z=1 m 60 mm iron Detector Specifications: • 12 layers of RPCs TDC • RPC has X & Y-planes Readout Mod. Monitor (orthogonal strips) Scaler • Each plane gives 32 pick up CAMAC Y=1 m Controller signals X=1 m • Total no. of channels = 12 x 2 x 32 = 768 Informations to be recorded on every valid trigger : (Few per min) INO controller Front end Electronics v Event time up to micro secs (RTC) v Particle interaction tracks (boolean status of X-Y pick-up signal in each layer) 768 bits v relative time of interaction along the layers(X-Y planes) of RPCs (24 TDCstops) Design Considerations: • Flexibility and scalability • Fast implementation using available resources and expertise • Custom design standard at front end and CAMAC standard at back end with a serial transfer of data 16 October, 2009 ASET talk - S. S. Upadhya 4

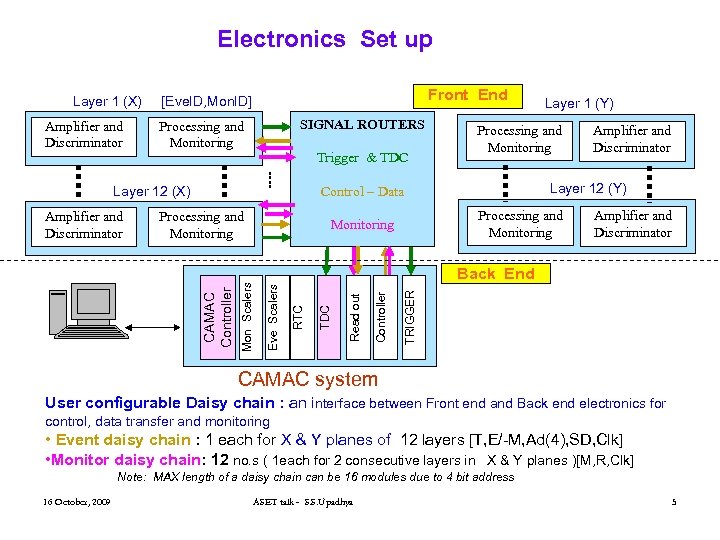

Electronics Set up SIGNAL ROUTERS Processing and Monitoring Trigger & TDC Layer 12 (X) Processing and Monitoring Amplifier and Discriminator Layer 12 (Y) Processing and Monitoring Amplifier and Discriminator TRIGGER Controller RTC Back End Eve Scalers Mon Scalers CAMAC Controller Amplifier and Discriminator Layer 1 (Y) Processing and Monitoring Control – Data Read out Amplifier and Discriminator Front End [Eve. ID, Mon. ID] TDC Layer 1 (X) CAMAC system User configurable Daisy chain : an interface between Front end and Back end electronics for control, data transfer and monitoring • Event daisy chain : 1 each for X & Y planes of 12 layers [T, E/-M, Ad(4), SD, Clk] • Monitor daisy chain: 12 no. s ( 1 each for 2 consecutive layers in X & Y planes )[M, R, Clk] Note: MAX length of a daisy chain can be 16 modules due to 4 bit address 16 October, 2009 ASET talk - S. S. Upadhya 5

Electronics Set up SIGNAL ROUTERS Processing and Monitoring Trigger & TDC Layer 12 (X) Processing and Monitoring Amplifier and Discriminator Layer 12 (Y) Processing and Monitoring Amplifier and Discriminator TRIGGER Controller RTC Back End Eve Scalers Mon Scalers CAMAC Controller Amplifier and Discriminator Layer 1 (Y) Processing and Monitoring Control – Data Read out Amplifier and Discriminator Front End [Eve. ID, Mon. ID] TDC Layer 1 (X) CAMAC system User configurable Daisy chain : an interface between Front end and Back end electronics for control, data transfer and monitoring • Event daisy chain : 1 each for X & Y planes of 12 layers [T, E/-M, Ad(4), SD, Clk] • Monitor daisy chain: 12 no. s ( 1 each for 2 consecutive layers in X & Y planes )[M, R, Clk] Note: MAX length of a daisy chain can be 16 modules due to 4 bit address 16 October, 2009 ASET talk - S. S. Upadhya 5

Main Sections of Electronics l Front End Electronics l l Trigger logic l l l Amplifier & Discriminator Processing and Monitoring Signal Routers Front end (Tigger-0 & 1) Back end (Final Trigger) Back end Processing l l Event process Monitor process 16 October, 2009 ASET talk - S. S. Upadhya 6

Main Sections of Electronics l Front End Electronics l l Trigger logic l l l Amplifier & Discriminator Processing and Monitoring Signal Routers Front end (Tigger-0 & 1) Back end (Final Trigger) Back end Processing l l Event process Monitor process 16 October, 2009 ASET talk - S. S. Upadhya 6

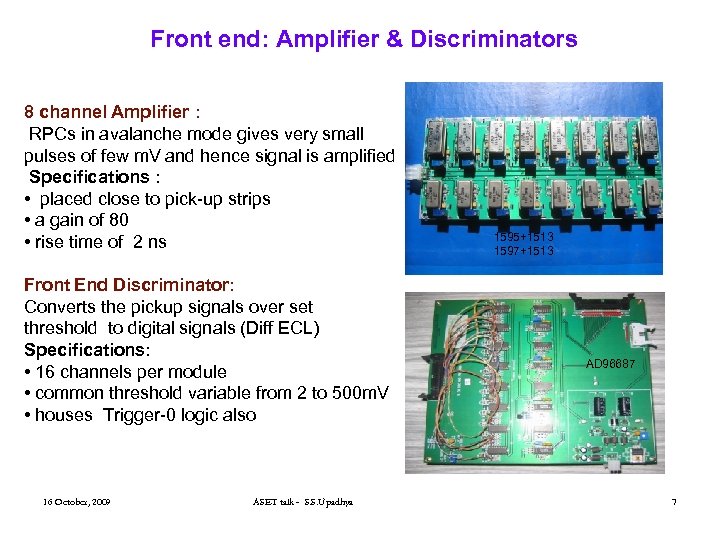

Front end: Amplifier & Discriminators 8 channel Amplifier : RPCs in avalanche mode gives very small pulses of few m. V and hence signal is amplified Specifications : • placed close to pick-up strips • a gain of 80 • rise time of 2 ns Front End Discriminator: Converts the pickup signals over set threshold to digital signals (Diff ECL) Specifications: • 16 channels per module • common threshold variable from 2 to 500 m. V • houses Trigger-0 logic also 16 October, 2009 ASET talk - S. S. Upadhya 1595+1513 1597+1513 AD 96687 7

Front end: Amplifier & Discriminators 8 channel Amplifier : RPCs in avalanche mode gives very small pulses of few m. V and hence signal is amplified Specifications : • placed close to pick-up strips • a gain of 80 • rise time of 2 ns Front End Discriminator: Converts the pickup signals over set threshold to digital signals (Diff ECL) Specifications: • 16 channels per module • common threshold variable from 2 to 500 m. V • houses Trigger-0 logic also 16 October, 2009 ASET talk - S. S. Upadhya 1595+1513 1597+1513 AD 96687 7

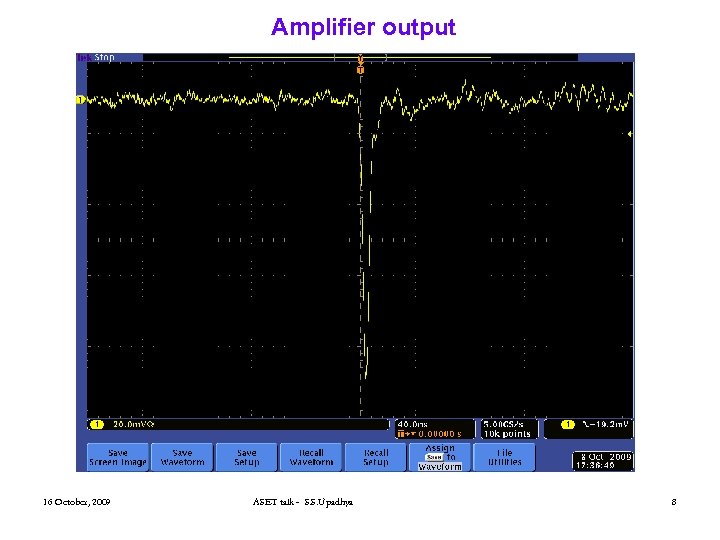

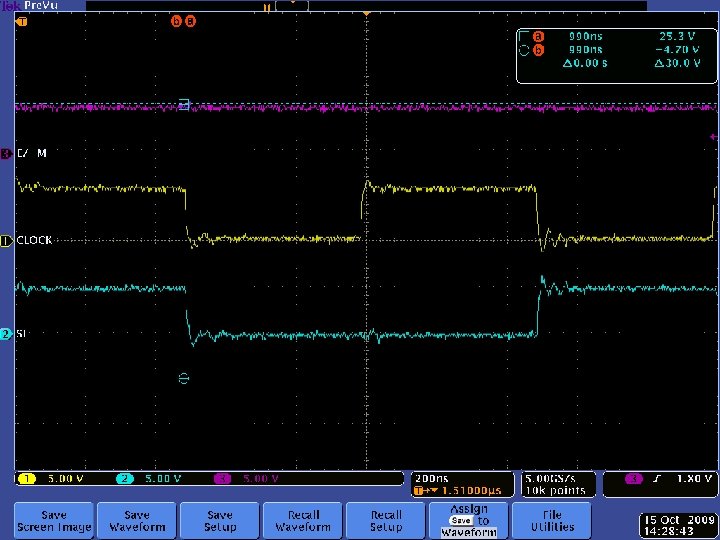

Amplifier output 16 October, 2009 ASET talk - S. S. Upadhya 8

Amplifier output 16 October, 2009 ASET talk - S. S. Upadhya 8

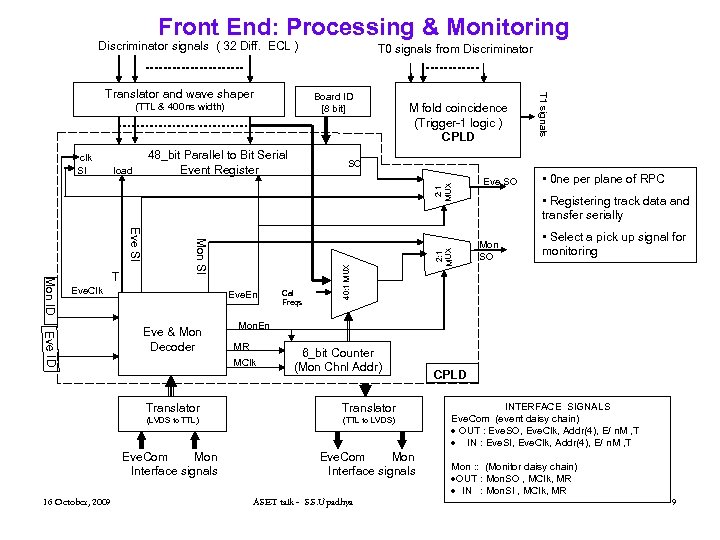

Front End: Processing & Monitoring Discriminator signals ( 32 Diff. ECL ) Board ID [8 bit] (TTL & 400 ns width) load 48_bit Parallel to Bit Serial Event Register SO Eve. En Eve ID Eve & Mon Decoder Cal Freqs MR 6_bit Counter (Mon Chnl Addr) Translator (LVDS to TTL) 16 October, 2009 Eve SO • 0 ne per plane of RPC • Registering track data and transfer serially Mon SO • Select a pick up signal for monitoring Mon. En MClk (TTL to LVDS) Eve. Com Mon Interface signals 2: 1 MUX Mon SI Eve SI Mon ID T Eve. Clk 40: 1 MUX 2: 1 MUX clk SI M fold coincidence (Trigger-1 logic ) CPLD T 1 signals Translator and wave shaper T 0 signals from Discriminator Eve. Com Mon Interface signals ASET talk - S. S. Upadhya CPLD INTERFACE SIGNALS Eve. Com (event daisy chain) · OUT : Eve. SO, Eve. Clk, Addr(4), E/ n. M , T · IN : Eve. SI, Eve. Clk, Addr(4), E/ n. M , T Mon : : (Monitor daisy chain) ·OUT : Mon. SO , MClk, MR · IN : Mon. SI , MClk, MR 9

Front End: Processing & Monitoring Discriminator signals ( 32 Diff. ECL ) Board ID [8 bit] (TTL & 400 ns width) load 48_bit Parallel to Bit Serial Event Register SO Eve. En Eve ID Eve & Mon Decoder Cal Freqs MR 6_bit Counter (Mon Chnl Addr) Translator (LVDS to TTL) 16 October, 2009 Eve SO • 0 ne per plane of RPC • Registering track data and transfer serially Mon SO • Select a pick up signal for monitoring Mon. En MClk (TTL to LVDS) Eve. Com Mon Interface signals 2: 1 MUX Mon SI Eve SI Mon ID T Eve. Clk 40: 1 MUX 2: 1 MUX clk SI M fold coincidence (Trigger-1 logic ) CPLD T 1 signals Translator and wave shaper T 0 signals from Discriminator Eve. Com Mon Interface signals ASET talk - S. S. Upadhya CPLD INTERFACE SIGNALS Eve. Com (event daisy chain) · OUT : Eve. SO, Eve. Clk, Addr(4), E/ n. M , T · IN : Eve. SI, Eve. Clk, Addr(4), E/ n. M , T Mon : : (Monitor daisy chain) ·OUT : Mon. SO , MClk, MR · IN : Mon. SI , MClk, MR 9

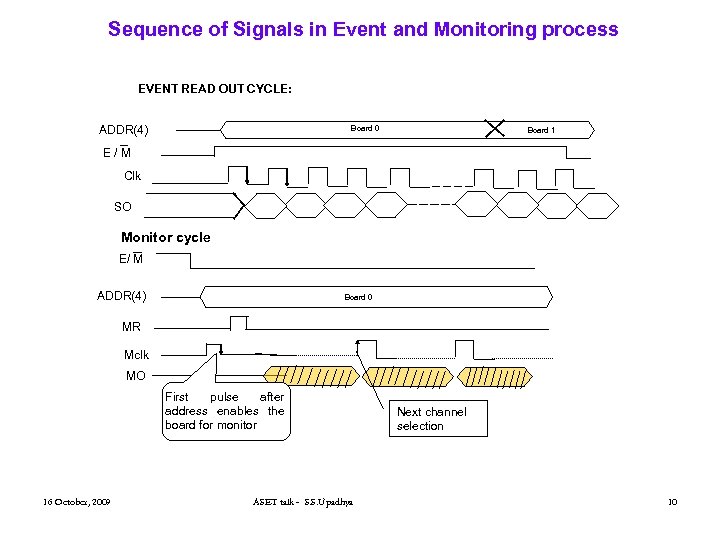

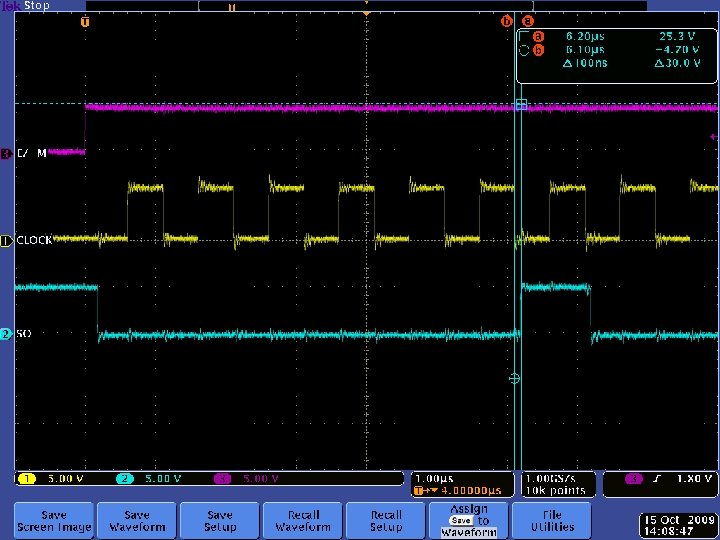

Sequence of Signals in Event and Monitoring process EVENT READ OUT CYCLE: ADDR(4) Board 0 Board 1 E/M Clk SO Monitor cycle E/ M ADDR(4) Board 0 MR Mclk MO First pulse after address enables the board for monitor 16 October, 2009 ASET talk - S. S. Upadhya Next channel selection 10

Sequence of Signals in Event and Monitoring process EVENT READ OUT CYCLE: ADDR(4) Board 0 Board 1 E/M Clk SO Monitor cycle E/ M ADDR(4) Board 0 MR Mclk MO First pulse after address enables the board for monitor 16 October, 2009 ASET talk - S. S. Upadhya Next channel selection 10

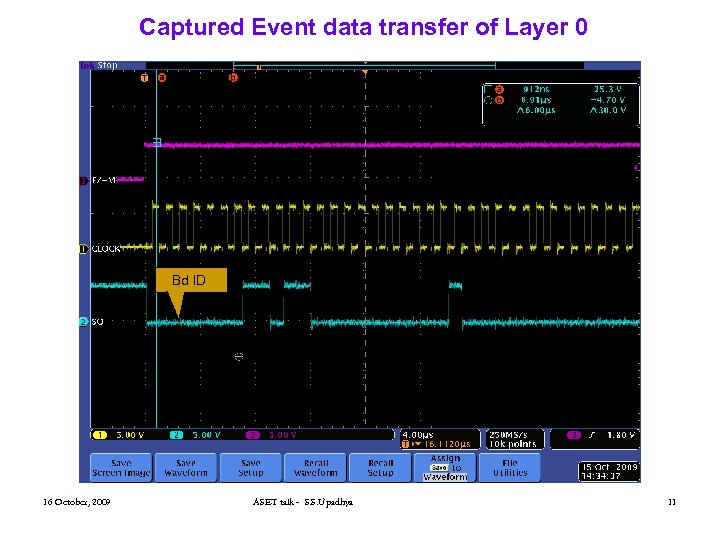

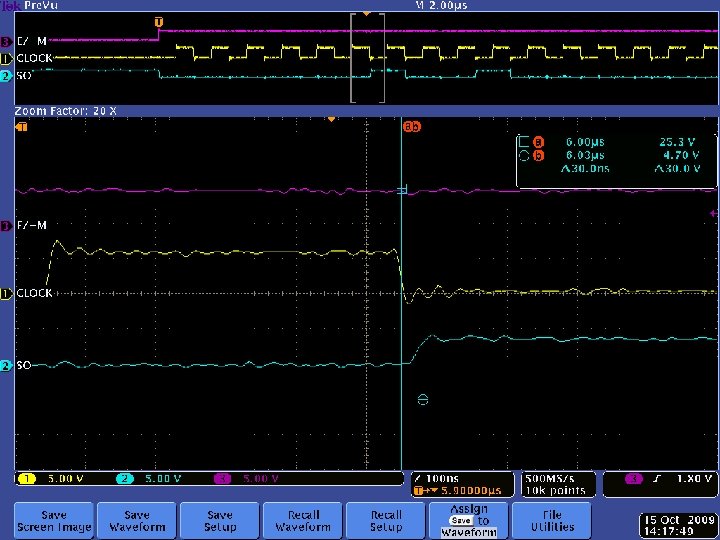

Captured Event data transfer of Layer 0 Bd ID 16 October, 2009 ASET talk - S. S. Upadhya 11

Captured Event data transfer of Layer 0 Bd ID 16 October, 2009 ASET talk - S. S. Upadhya 11

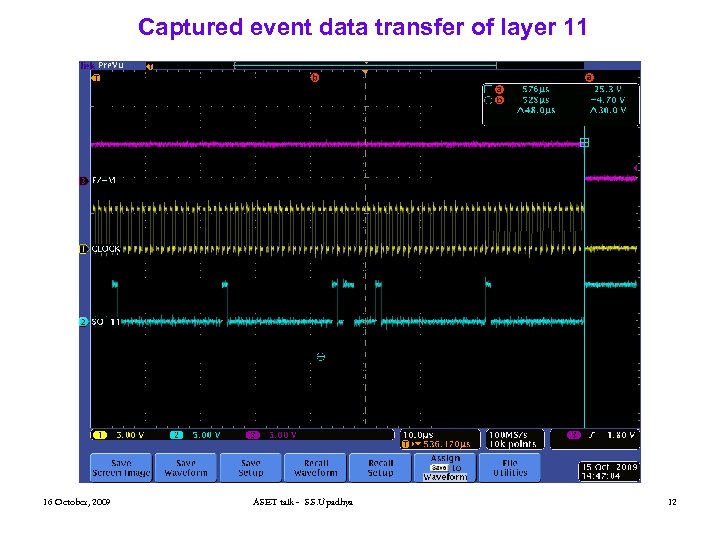

Captured event data transfer of layer 11 16 October, 2009 ASET talk - S. S. Upadhya 12

Captured event data transfer of layer 11 16 October, 2009 ASET talk - S. S. Upadhya 12

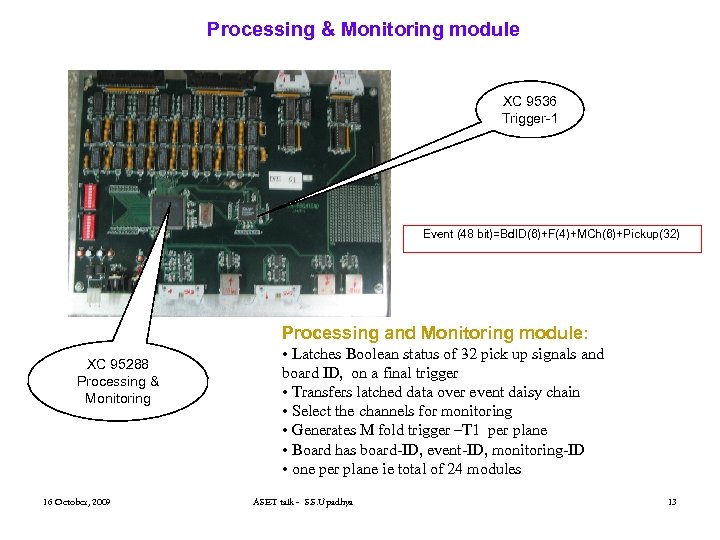

Processing & Monitoring module XC 9536 Trigger-1 Event (48 bit)=Bd. ID(6)+F(4)+MCh(6)+Pickup(32) Processing and Monitoring module: XC 95288 Processing & Monitoring 16 October, 2009 • Latches Boolean status of 32 pick up signals and board ID, on a final trigger • Transfers latched data over event daisy chain • Select the channels for monitoring • Generates M fold trigger –T 1 per plane • Board has board-ID, event-ID, monitoring-ID • one per plane ie total of 24 modules ASET talk - S. S. Upadhya 13

Processing & Monitoring module XC 9536 Trigger-1 Event (48 bit)=Bd. ID(6)+F(4)+MCh(6)+Pickup(32) Processing and Monitoring module: XC 95288 Processing & Monitoring 16 October, 2009 • Latches Boolean status of 32 pick up signals and board ID, on a final trigger • Transfers latched data over event daisy chain • Select the channels for monitoring • Generates M fold trigger –T 1 per plane • Board has board-ID, event-ID, monitoring-ID • one per plane ie total of 24 modules ASET talk - S. S. Upadhya 13

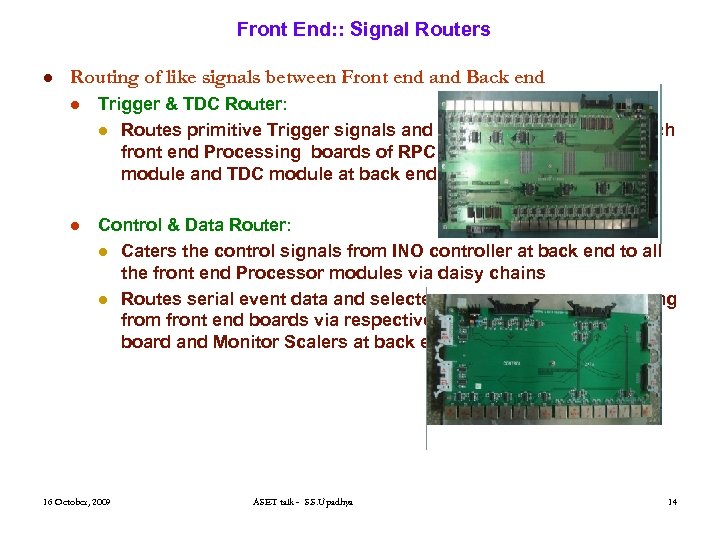

Front End: : Signal Routers l Routing of like signals between Front end and Back end l Trigger & TDC Router: l Routes primitive Trigger signals and TDC stop signals from each front end Processing boards of RPC planes to Final TRIGGER module and TDC module at back end CAMAC l Control & Data Router: l Caters the control signals from INO controller at back end to all the front end Processor modules via daisy chains l Routes serial event data and selected pick signals for monitoring from front end boards via respective daisy chains to Read out board and Monitor Scalers at back end. 16 October, 2009 ASET talk - S. S. Upadhya 14

Front End: : Signal Routers l Routing of like signals between Front end and Back end l Trigger & TDC Router: l Routes primitive Trigger signals and TDC stop signals from each front end Processing boards of RPC planes to Final TRIGGER module and TDC module at back end CAMAC l Control & Data Router: l Caters the control signals from INO controller at back end to all the front end Processor modules via daisy chains l Routes serial event data and selected pick signals for monitoring from front end boards via respective daisy chains to Read out board and Monitor Scalers at back end. 16 October, 2009 ASET talk - S. S. Upadhya 14

Trigger Logic (Mx. N fold) For X-planes l in Front End Discriminator (FED) module l l Pickup signals crossing set threshold converted to DIGITAL (diff ECL) ; typical rate ~200 Hz Every 8 th pickup signals in a plane are logically ORed to get T 0 signals (S 0 to S 7) Sn rate is 4 x 200= 800 Hz In Processing and Monitoring module l l [ TRIGGER 1 LOGIC -T 1 trigger] M fold coincidence of S 1 to S 8 signals (equivalent to M fold coincidence of consecutive pickup signals in a plane)- 1 F, 2 F, 3 F, 4 F Final Trigger Module ( CAMAC std. ) l [ TRIGGER 0 LOGIC - trigger] T 0 [ TRIGGER 2 LOGIC - trigger ] T 2 M fold signals(1 F, 2 F, 3 F, 4 F) from all the X-planes are the inputs (diff LVDS) Mx. N fold trigger is generated Eg: M = 1 F : : S 0+S 1+…. +S 7 ie N fold coincidence of M fold (T 1) triggers from consecutive planes M = 2 F : : S 0. S 1+S 1. S 2 + S 2. S 3 + S 3. S 4 + …. . + S 7. S 0 typical = 3 F : : S 0. S 1. S 2+S 1. S 2. S 3 are 1 x 5, 2 x 4, S 3. S 4. S 5 + …. . + S 7. S 0. S 1 M Mx. N folds implemented + S 2. S 3. S 4 + 3 x 3, 4 x 2 M = 4 F : : S 0. S 1. S 2. S 3+S 1. S 2. S 3. S 4 + S 2. S 3. S 4. S 5 + …. . + S 7. S 0. S 1. S 2 For Y-planes l Similarly Mx. N fold for Y-plane is generated Final Trigger is logical OR of Mx. N fold trigger from X and Y-planes • Final Trigger invokes DAq system via LAM to record the event BACK information. 16 October, 2009 ASET talk - S. S. Upadhya 15

Trigger Logic (Mx. N fold) For X-planes l in Front End Discriminator (FED) module l l Pickup signals crossing set threshold converted to DIGITAL (diff ECL) ; typical rate ~200 Hz Every 8 th pickup signals in a plane are logically ORed to get T 0 signals (S 0 to S 7) Sn rate is 4 x 200= 800 Hz In Processing and Monitoring module l l [ TRIGGER 1 LOGIC -T 1 trigger] M fold coincidence of S 1 to S 8 signals (equivalent to M fold coincidence of consecutive pickup signals in a plane)- 1 F, 2 F, 3 F, 4 F Final Trigger Module ( CAMAC std. ) l [ TRIGGER 0 LOGIC - trigger] T 0 [ TRIGGER 2 LOGIC - trigger ] T 2 M fold signals(1 F, 2 F, 3 F, 4 F) from all the X-planes are the inputs (diff LVDS) Mx. N fold trigger is generated Eg: M = 1 F : : S 0+S 1+…. +S 7 ie N fold coincidence of M fold (T 1) triggers from consecutive planes M = 2 F : : S 0. S 1+S 1. S 2 + S 2. S 3 + S 3. S 4 + …. . + S 7. S 0 typical = 3 F : : S 0. S 1. S 2+S 1. S 2. S 3 are 1 x 5, 2 x 4, S 3. S 4. S 5 + …. . + S 7. S 0. S 1 M Mx. N folds implemented + S 2. S 3. S 4 + 3 x 3, 4 x 2 M = 4 F : : S 0. S 1. S 2. S 3+S 1. S 2. S 3. S 4 + S 2. S 3. S 4. S 5 + …. . + S 7. S 0. S 1. S 2 For Y-planes l Similarly Mx. N fold for Y-plane is generated Final Trigger is logical OR of Mx. N fold trigger from X and Y-planes • Final Trigger invokes DAq system via LAM to record the event BACK information. 16 October, 2009 ASET talk - S. S. Upadhya 15

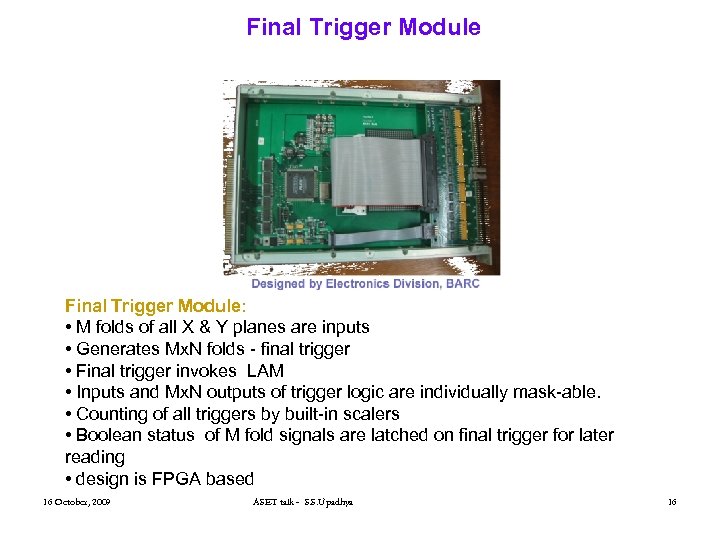

Final Trigger Module: • M folds of all X & Y planes are inputs • Generates Mx. N folds - final trigger • Final trigger invokes LAM • Inputs and Mx. N outputs of trigger logic are individually mask-able. • Counting of all triggers by built-in scalers • Boolean status of M fold signals are latched on final trigger for later reading • design is FPGA based 16 October, 2009 ASET talk - S. S. Upadhya 16

Final Trigger Module: • M folds of all X & Y planes are inputs • Generates Mx. N folds - final trigger • Final trigger invokes LAM • Inputs and Mx. N outputs of trigger logic are individually mask-able. • Counting of all triggers by built-in scalers • Boolean status of M fold signals are latched on final trigger for later reading • design is FPGA based 16 October, 2009 ASET talk - S. S. Upadhya 16

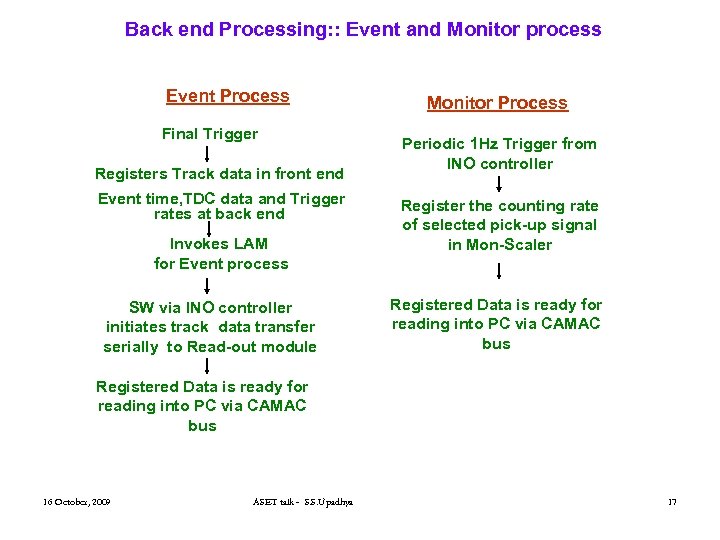

Back end Processing: : Event and Monitor process Event Process Final Trigger Registers Track data in front end Event time, TDC data and Trigger rates at back end Invokes LAM for Event process SW via INO controller initiates track data transfer serially to Read-out module Monitor Process Periodic 1 Hz Trigger from INO controller Register the counting rate of selected pick-up signal in Mon-Scaler Registered Data is ready for reading into PC via CAMAC bus 16 October, 2009 ASET talk - S. S. Upadhya 17

Back end Processing: : Event and Monitor process Event Process Final Trigger Registers Track data in front end Event time, TDC data and Trigger rates at back end Invokes LAM for Event process SW via INO controller initiates track data transfer serially to Read-out module Monitor Process Periodic 1 Hz Trigger from INO controller Register the counting rate of selected pick-up signal in Mon-Scaler Registered Data is ready for reading into PC via CAMAC bus 16 October, 2009 ASET talk - S. S. Upadhya 17

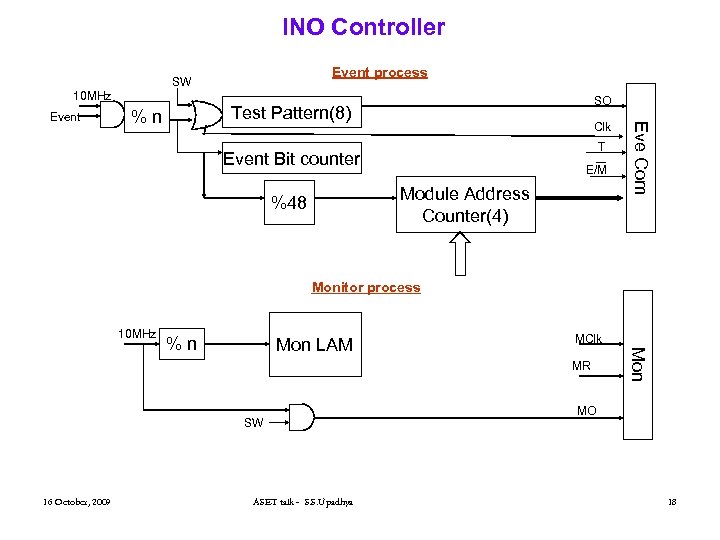

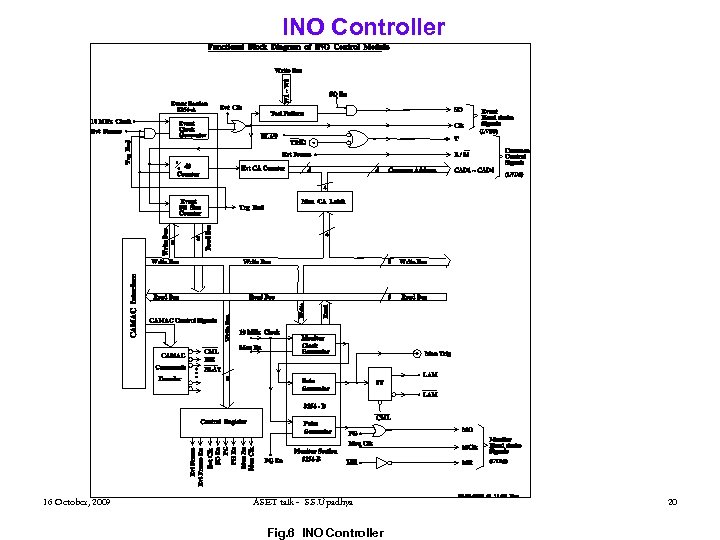

INO Controller 10 MHz SO Test Pattern(8) %n Clk T Event Bit counter E/M Module Address Counter(4) %48 Eve Com Event process SW Monitor process 10 MHz Mon LAM MClk MR SW 16 October, 2009 ASET talk - S. S. Upadhya Mon %n MO 18

INO Controller 10 MHz SO Test Pattern(8) %n Clk T Event Bit counter E/M Module Address Counter(4) %48 Eve Com Event process SW Monitor process 10 MHz Mon LAM MClk MR SW 16 October, 2009 ASET talk - S. S. Upadhya Mon %n MO 18

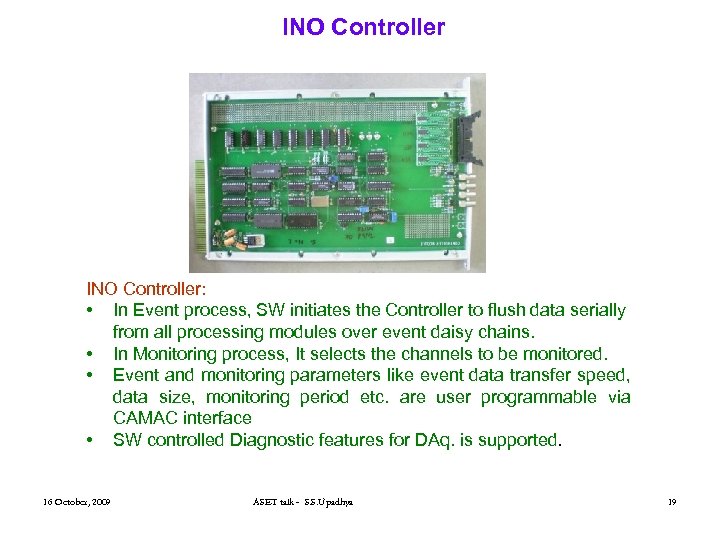

INO Controller: • In Event process, SW initiates the Controller to flush data serially from all processing modules over event daisy chains. • In Monitoring process, It selects the channels to be monitored. • Event and monitoring parameters like event data transfer speed, data size, monitoring period etc. are user programmable via CAMAC interface • SW controlled Diagnostic features for DAq. is supported. 16 October, 2009 ASET talk - S. S. Upadhya 19

INO Controller: • In Event process, SW initiates the Controller to flush data serially from all processing modules over event daisy chains. • In Monitoring process, It selects the channels to be monitored. • Event and monitoring parameters like event data transfer speed, data size, monitoring period etc. are user programmable via CAMAC interface • SW controlled Diagnostic features for DAq. is supported. 16 October, 2009 ASET talk - S. S. Upadhya 19

INO Controller 16 October, 2009 ASET talk - S. S. Upadhya Fig. 6 INO Controller 20

INO Controller 16 October, 2009 ASET talk - S. S. Upadhya Fig. 6 INO Controller 20

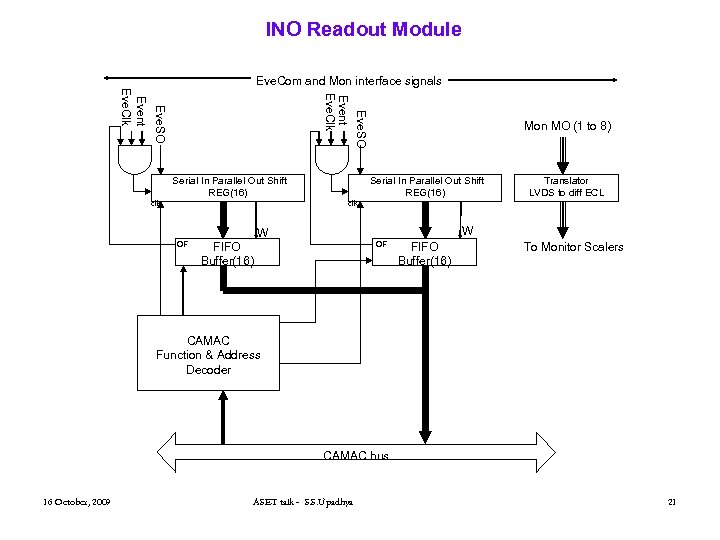

INO Readout Module Eve. Com and Mon interface signals Eve. SO Event Eve. Clk Serial In Parallel Out Shift REG(16) clk Mon MO (1 to 8) Serial In Parallel Out Shift REG(16) Translator LVDS to diff ECL clk OF FIFO Buffer(16) W W OF FIFO Buffer(16) To Monitor Scalers CAMAC Function & Address Decoder CAMAC bus 16 October, 2009 ASET talk - S. S. Upadhya 21

INO Readout Module Eve. Com and Mon interface signals Eve. SO Event Eve. Clk Serial In Parallel Out Shift REG(16) clk Mon MO (1 to 8) Serial In Parallel Out Shift REG(16) Translator LVDS to diff ECL clk OF FIFO Buffer(16) W W OF FIFO Buffer(16) To Monitor Scalers CAMAC Function & Address Decoder CAMAC bus 16 October, 2009 ASET talk - S. S. Upadhya 21

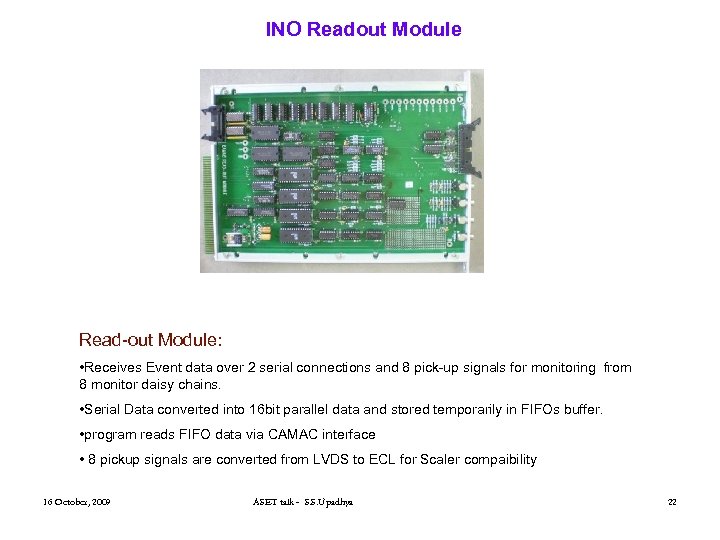

INO Readout Module Read-out Module: • Receives Event data over 2 serial connections and 8 pick-up signals for monitoring from 8 monitor daisy chains. • Serial Data converted into 16 bit parallel data and stored temporarily in FIFOs buffer. • program reads FIFO data via CAMAC interface • 8 pickup signals are converted from LVDS to ECL for Scaler compaibility 16 October, 2009 ASET talk - S. S. Upadhya 22

INO Readout Module Read-out Module: • Receives Event data over 2 serial connections and 8 pick-up signals for monitoring from 8 monitor daisy chains. • Serial Data converted into 16 bit parallel data and stored temporarily in FIFOs buffer. • program reads FIFO data via CAMAC interface • 8 pickup signals are converted from LVDS to ECL for Scaler compaibility 16 October, 2009 ASET talk - S. S. Upadhya 22

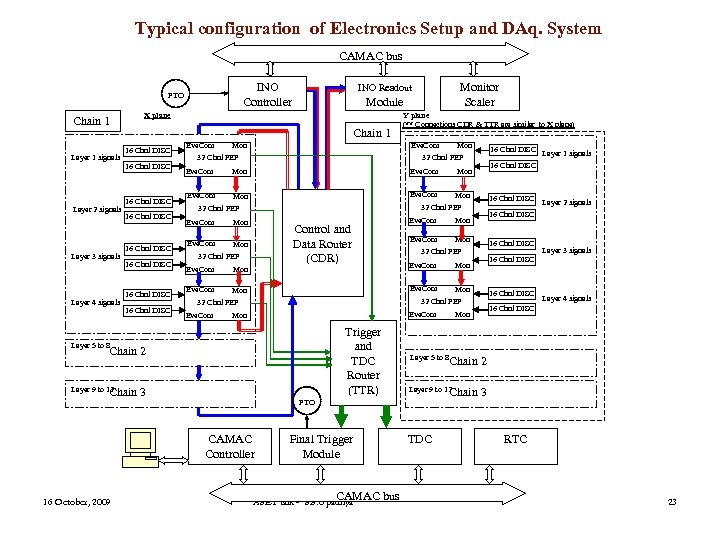

Typical configuration of Electronics Setup and DAq. System CAMAC bus INO Controller FTO Layer 1 signals Layer 2 signals Layer 3 signals Layer 4 signals Module X plane Chain 1 16 Chnl DISC 16 Chnl DISC Eve. Com Mon 32 Chnl FEP Mon Eve. Com Mon 32 Chnl FEP Eve. Com 16 Chnl DISC Layer 2 signals 16 Chnl DISC Mon Eve. Com Mon 32 Chnl FEP Eve. Com Mon 16 Chnl DISC Mon 32 Chnl FEP Eve. Com Mon Trigger and TDC Router (TTR) 3 Layer 4 signals 16 Chnl DISC Mon Chain 2 Layer 9 to 12 Chain Final Trigger Module CAMAC ASET talk - S. S. Upadhya 16 Chnl DISC Layer 5 to 8 FTO CAMAC Controller Layer 3 signals 16 Chnl DISC Mon Eve. Com Mon Eve. Com Control and Data Router (CDR) Layer 1 signals 16 Chnl DISC Mon 32 Chnl FEP Chain 2 16 October, 2009 16 Chnl DISC Eve. Com Layer 5 to 8 Layer 9 to 12 Chain Y plane (** Connections CDR & TTR are similar to X plane) Eve. Com Mon 32 Chnl FEP Eve. Com Monitor Scaler INO Readout TDC bus 3 RTC 23

Typical configuration of Electronics Setup and DAq. System CAMAC bus INO Controller FTO Layer 1 signals Layer 2 signals Layer 3 signals Layer 4 signals Module X plane Chain 1 16 Chnl DISC 16 Chnl DISC Eve. Com Mon 32 Chnl FEP Mon Eve. Com Mon 32 Chnl FEP Eve. Com 16 Chnl DISC Layer 2 signals 16 Chnl DISC Mon Eve. Com Mon 32 Chnl FEP Eve. Com Mon 16 Chnl DISC Mon 32 Chnl FEP Eve. Com Mon Trigger and TDC Router (TTR) 3 Layer 4 signals 16 Chnl DISC Mon Chain 2 Layer 9 to 12 Chain Final Trigger Module CAMAC ASET talk - S. S. Upadhya 16 Chnl DISC Layer 5 to 8 FTO CAMAC Controller Layer 3 signals 16 Chnl DISC Mon Eve. Com Mon Eve. Com Control and Data Router (CDR) Layer 1 signals 16 Chnl DISC Mon 32 Chnl FEP Chain 2 16 October, 2009 16 Chnl DISC Eve. Com Layer 5 to 8 Layer 9 to 12 Chain Y plane (** Connections CDR & TTR are similar to X plane) Eve. Com Mon 32 Chnl FEP Eve. Com Monitor Scaler INO Readout TDC bus 3 RTC 23

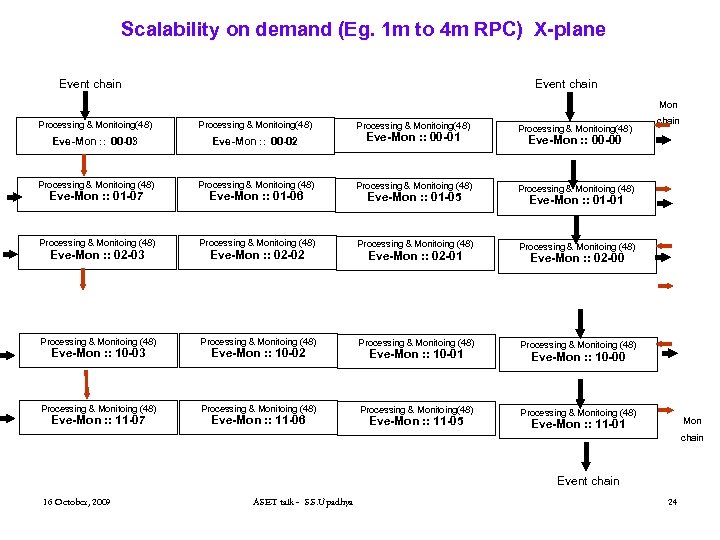

Scalability on demand (Eg. 1 m to 4 m RPC) X-plane Event chain Mon Processing & Monitoing(48) Eve-Mon : : 00 -03 Eve-Mon : : 00 -02 Eve-Mon : : 00 -01 Processing & Monitoing (48) Eve-Mon : : 01 -07 Processing & Monitoing (48) Eve-Mon : : 02 -03 Processing & Monitoing (48) Eve-Mon : : 10 -03 Processing & Monitoing (48) Eve-Mon : : 11 -07 Eve-Mon : : 01 -06 Processing & Monitoing (48) Eve-Mon : : 02 -02 Processing & Monitoing (48) Eve-Mon : : 10 -02 Processing & Monitoing (48) Eve-Mon : : 11 -06 Processing & Monitoing(48) Eve-Mon : : 01 -05 Processing & Monitoing (48) Eve-Mon : : 02 -01 Processing & Monitoing (48) Eve-Mon : : 10 -01 Processing & Monitoing(48) Eve-Mon : : 11 -05 Processing & Monitoing(48) chain Eve-Mon : : 00 -00 Processing & Monitoing (48) Eve-Mon : : 01 -01 Processing & Monitoing (48) Eve-Mon : : 02 -00 Processing & Monitoing (48) Eve-Mon : : 10 -00 Processing & Monitoing (48) Mon Eve-Mon : : 11 -01 chain Event chain 16 October, 2009 ASET talk - S. S. Upadhya 24

Scalability on demand (Eg. 1 m to 4 m RPC) X-plane Event chain Mon Processing & Monitoing(48) Eve-Mon : : 00 -03 Eve-Mon : : 00 -02 Eve-Mon : : 00 -01 Processing & Monitoing (48) Eve-Mon : : 01 -07 Processing & Monitoing (48) Eve-Mon : : 02 -03 Processing & Monitoing (48) Eve-Mon : : 10 -03 Processing & Monitoing (48) Eve-Mon : : 11 -07 Eve-Mon : : 01 -06 Processing & Monitoing (48) Eve-Mon : : 02 -02 Processing & Monitoing (48) Eve-Mon : : 10 -02 Processing & Monitoing (48) Eve-Mon : : 11 -06 Processing & Monitoing(48) Eve-Mon : : 01 -05 Processing & Monitoing (48) Eve-Mon : : 02 -01 Processing & Monitoing (48) Eve-Mon : : 10 -01 Processing & Monitoing(48) Eve-Mon : : 11 -05 Processing & Monitoing(48) chain Eve-Mon : : 00 -00 Processing & Monitoing (48) Eve-Mon : : 01 -01 Processing & Monitoing (48) Eve-Mon : : 02 -00 Processing & Monitoing (48) Eve-Mon : : 10 -00 Processing & Monitoing (48) Mon Eve-Mon : : 11 -01 chain Event chain 16 October, 2009 ASET talk - S. S. Upadhya 24

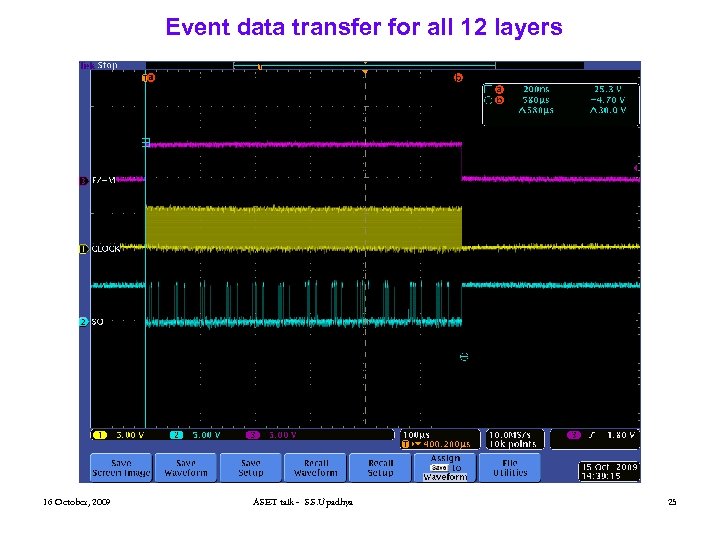

Event data transfer for all 12 layers 16 October, 2009 ASET talk - S. S. Upadhya 25

Event data transfer for all 12 layers 16 October, 2009 ASET talk - S. S. Upadhya 25

DAq. Software • DAq. Program has been developed in C under Linux • Main program displays Event data, Monitor Data as well it responds to user Key hit services EVENT RECORDING On a Event process, program records Ø Event time up to microsecond Ø 24 TDC readings Ø Boolean status of all pickup signals Ø Useful Trigger rates MONITORING On a periodic Monitoring trigger ( 1 Hz) Ø Monitor time recorded up to microsecond Ø Rates of selected set of channels are recorded Ø Next set of channels are selected for monitoring 16 October, 2009 ASET talk - S. S. Upadhya 26

DAq. Software • DAq. Program has been developed in C under Linux • Main program displays Event data, Monitor Data as well it responds to user Key hit services EVENT RECORDING On a Event process, program records Ø Event time up to microsecond Ø 24 TDC readings Ø Boolean status of all pickup signals Ø Useful Trigger rates MONITORING On a periodic Monitoring trigger ( 1 Hz) Ø Monitor time recorded up to microsecond Ø Rates of selected set of channels are recorded Ø Next set of channels are selected for monitoring 16 October, 2009 ASET talk - S. S. Upadhya 26

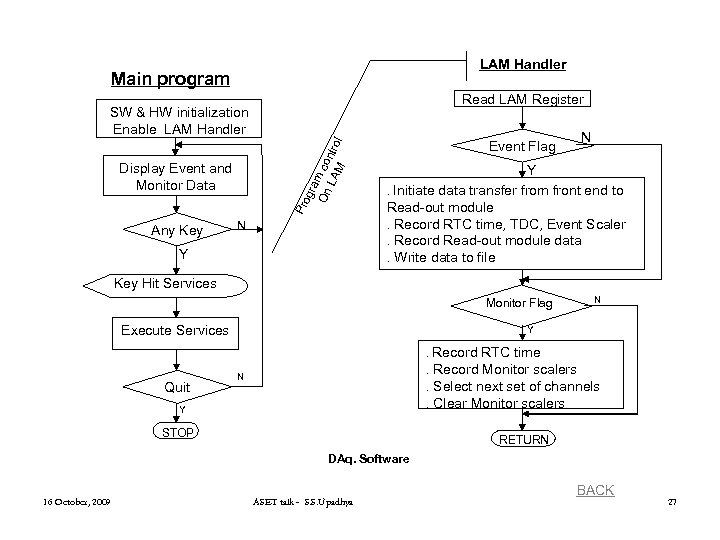

LAM Handler Main program Read LAM Register gra On m co LA ntro M l SW & HW initialization Enable LAM Handler Pro Display Event and Monitor Data Any Key N Y Event Flag N Y. Initiate data transfer from front end to Read-out module. Record RTC time, TDC, Event Scaler. Record Read-out module data. Write data to file Key Hit Services Monitor Flag Execute Services N Y . Record RTC time Quit . Record Monitor scalers. Select next set of channels. Clear Monitor scalers N Y STOP RETURN DAq. Software 16 October, 2009 ASET talk - S. S. Upadhya BACK 27

LAM Handler Main program Read LAM Register gra On m co LA ntro M l SW & HW initialization Enable LAM Handler Pro Display Event and Monitor Data Any Key N Y Event Flag N Y. Initiate data transfer from front end to Read-out module. Record RTC time, TDC, Event Scaler. Record Read-out module data. Write data to file Key Hit Services Monitor Flag Execute Services N Y . Record RTC time Quit . Record Monitor scalers. Select next set of channels. Clear Monitor scalers N Y STOP RETURN DAq. Software 16 October, 2009 ASET talk - S. S. Upadhya BACK 27

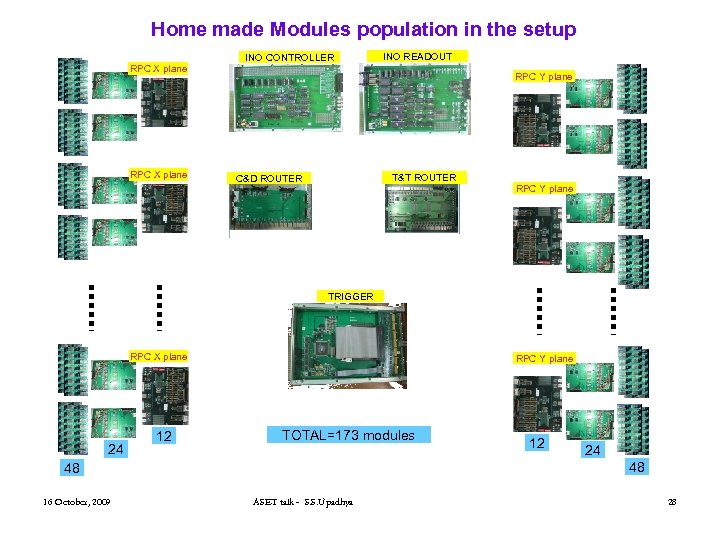

Home made Modules population in the setup INO CONTROLLER INO READOUT RPC X plane RPC Y plane T&T ROUTER C&D ROUTER RPC Y plane TRIGGER RPC X plane 24 12 RPC Y plane TOTAL=173 modules 24 48 48 16 October, 2009 12 ASET talk - S. S. Upadhya 28

Home made Modules population in the setup INO CONTROLLER INO READOUT RPC X plane RPC Y plane T&T ROUTER C&D ROUTER RPC Y plane TRIGGER RPC X plane 24 12 RPC Y plane TOTAL=173 modules 24 48 48 16 October, 2009 12 ASET talk - S. S. Upadhya 28

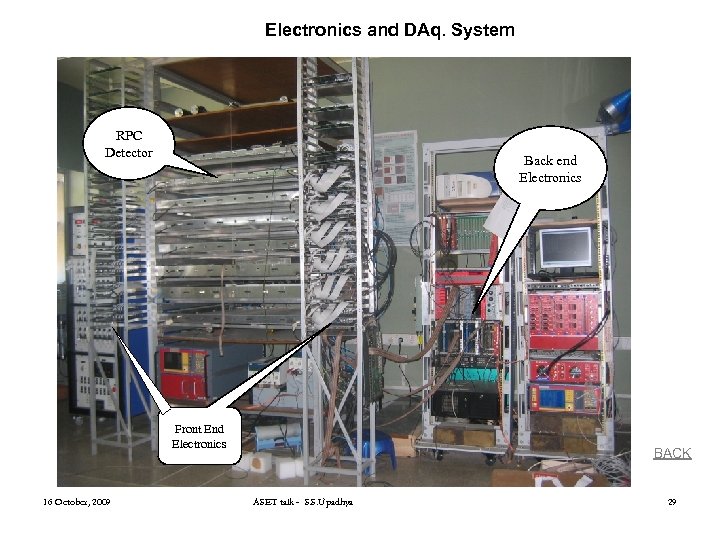

Electronics and DAq. System RPC Detector Back end Electronics Front End Electronics 16 October, 2009 BACK ASET talk - S. S. Upadhya 29

Electronics and DAq. System RPC Detector Back end Electronics Front End Electronics 16 October, 2009 BACK ASET talk - S. S. Upadhya 29

16 October, 2009 ASET talk - S. S. Upadhya 30

16 October, 2009 ASET talk - S. S. Upadhya 30

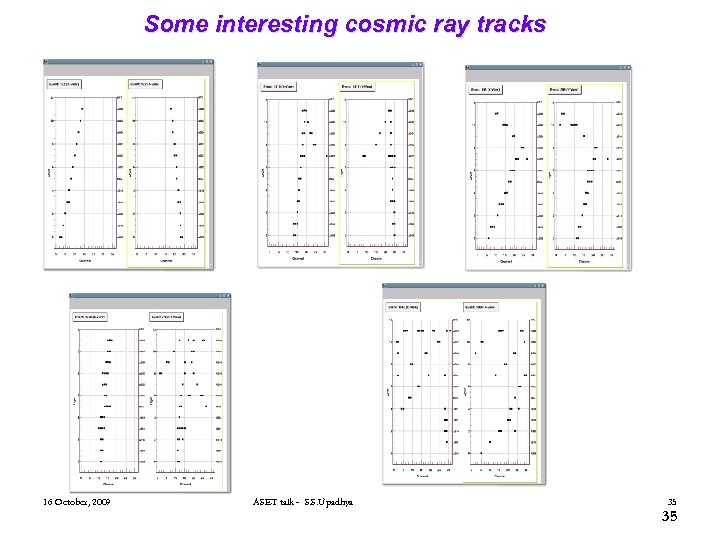

Some interesting cosmic ray tracks 16 October, 2009 ASET talk - S. S. Upadhya 35 35

Some interesting cosmic ray tracks 16 October, 2009 ASET talk - S. S. Upadhya 35 35

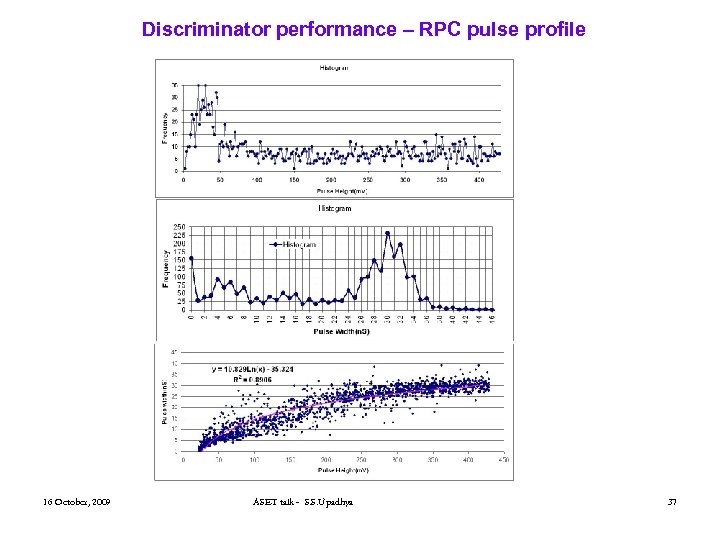

Discriminator performance – RPC pulse profile 16 October, 2009 ASET talk - S. S. Upadhya 37

Discriminator performance – RPC pulse profile 16 October, 2009 ASET talk - S. S. Upadhya 37

Histogram of Noise rate of pickup Chnl, Cal & Fold 16 October, 2009 ASET talk - S. S. Upadhya 38

Histogram of Noise rate of pickup Chnl, Cal & Fold 16 October, 2009 ASET talk - S. S. Upadhya 38

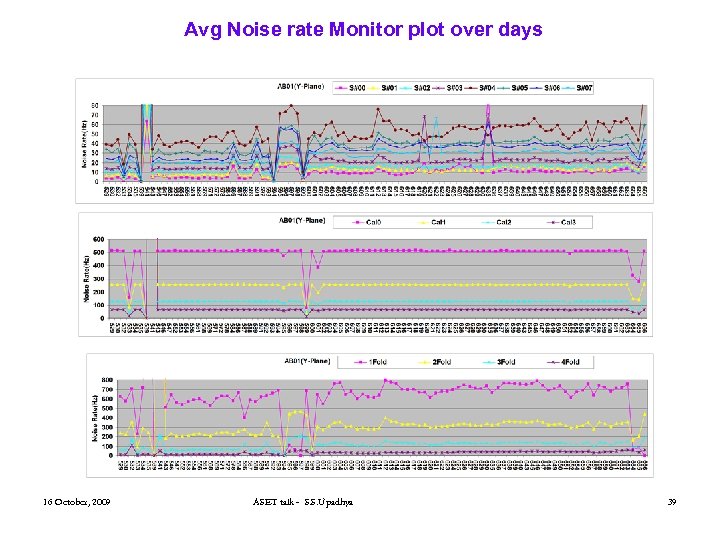

Avg Noise rate Monitor plot over days 16 October, 2009 ASET talk - S. S. Upadhya 39

Avg Noise rate Monitor plot over days 16 October, 2009 ASET talk - S. S. Upadhya 39

Histogram of Avg Noise rate over days 16 October, 2009 ASET talk - S. S. Upadhya 40

Histogram of Avg Noise rate over days 16 October, 2009 ASET talk - S. S. Upadhya 40

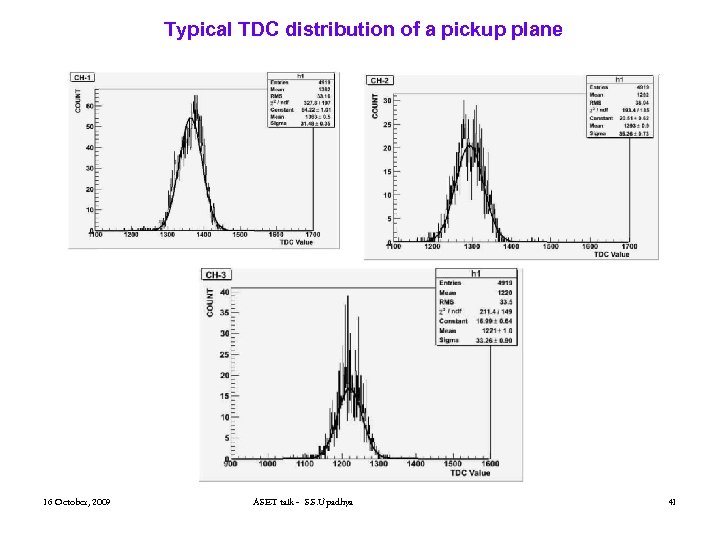

Typical TDC distribution of a pickup plane 16 October, 2009 ASET talk - S. S. Upadhya 41

Typical TDC distribution of a pickup plane 16 October, 2009 ASET talk - S. S. Upadhya 41

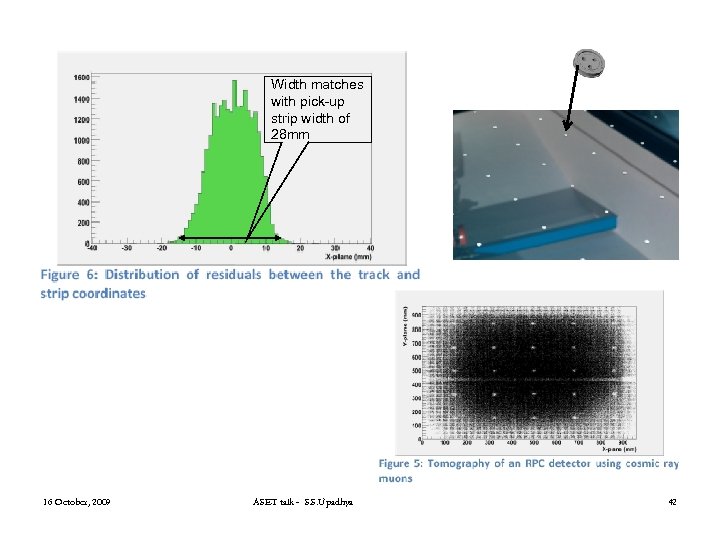

Width matches with pick-up strip width of 28 mm 16 October, 2009 ASET talk - S. S. Upadhya 42

Width matches with pick-up strip width of 28 mm 16 October, 2009 ASET talk - S. S. Upadhya 42

16 October, 2009 ASET talk - S. S. Upadhya 43

16 October, 2009 ASET talk - S. S. Upadhya 43

16 October, 2009 ASET talk - S. S. Upadhya 44

16 October, 2009 ASET talk - S. S. Upadhya 44

16 October, 2009 ASET talk - S. S. Upadhya 45

16 October, 2009 ASET talk - S. S. Upadhya 45

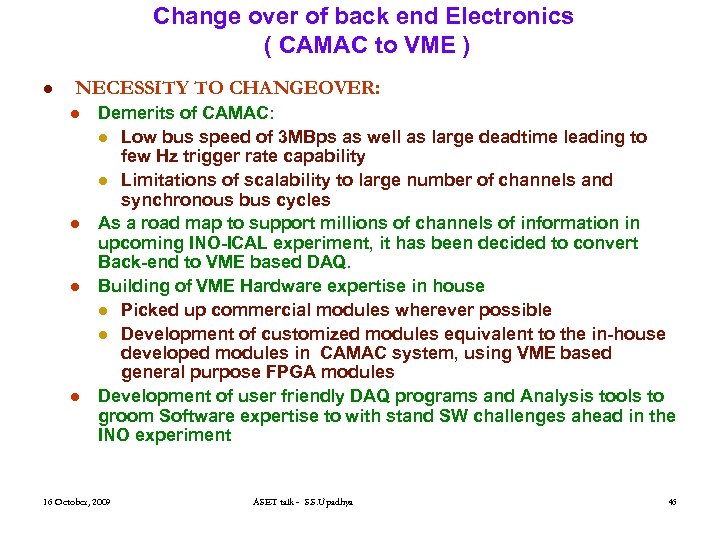

Change over of back end Electronics ( CAMAC to VME ) l NECESSITY TO CHANGEOVER: l l Demerits of CAMAC: l Low bus speed of 3 MBps as well as large deadtime leading to few Hz trigger rate capability l Limitations of scalability to large number of channels and synchronous bus cycles As a road map to support millions of channels of information in upcoming INO-ICAL experiment, it has been decided to convert Back-end to VME based DAQ. Building of VME Hardware expertise in house l Picked up commercial modules wherever possible l Development of customized modules equivalent to the in-house developed modules in CAMAC system, using VME based general purpose FPGA modules Development of user friendly DAQ programs and Analysis tools to groom Software expertise to with stand SW challenges ahead in the INO experiment 16 October, 2009 ASET talk - S. S. Upadhya 46

Change over of back end Electronics ( CAMAC to VME ) l NECESSITY TO CHANGEOVER: l l Demerits of CAMAC: l Low bus speed of 3 MBps as well as large deadtime leading to few Hz trigger rate capability l Limitations of scalability to large number of channels and synchronous bus cycles As a road map to support millions of channels of information in upcoming INO-ICAL experiment, it has been decided to convert Back-end to VME based DAQ. Building of VME Hardware expertise in house l Picked up commercial modules wherever possible l Development of customized modules equivalent to the in-house developed modules in CAMAC system, using VME based general purpose FPGA modules Development of user friendly DAQ programs and Analysis tools to groom Software expertise to with stand SW challenges ahead in the INO experiment 16 October, 2009 ASET talk - S. S. Upadhya 46

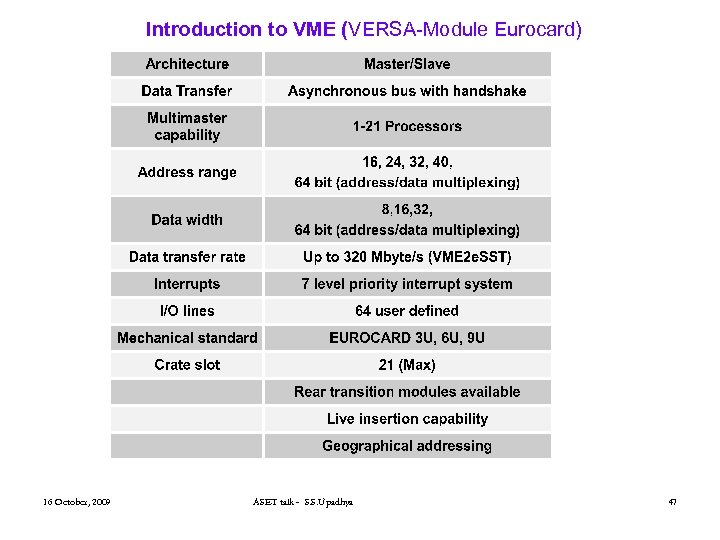

Introduction to VME (VERSA-Module Eurocard) 16 October, 2009 ASET talk - S. S. Upadhya 47

Introduction to VME (VERSA-Module Eurocard) 16 October, 2009 ASET talk - S. S. Upadhya 47

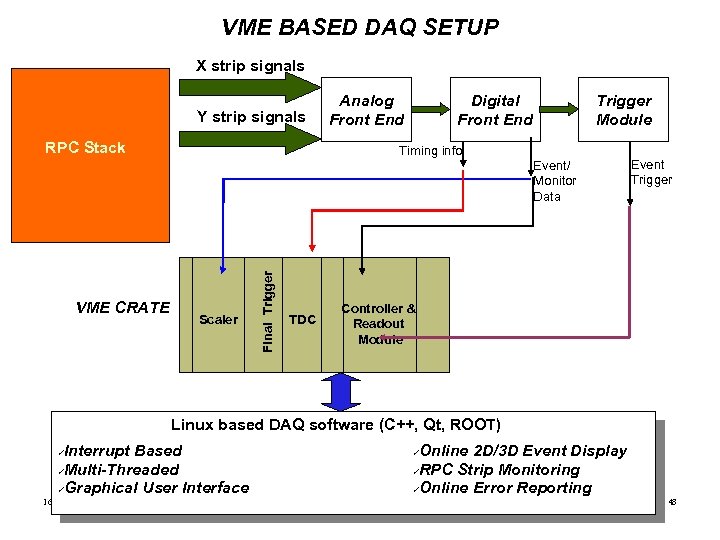

VME BASED DAQ SETUP X strip signals Y strip signals Analog Front End RPC Stack Digital Front End Trigger Module Timing info VME CRATE Scaler Final Trigger Event/ Monitor Data TDC Event Trigger Controller & Readout Module Linux based DAQ software (C++, Qt, ROOT) Interrupt Based Multi-Threaded Graphical User Interface 16 October, 2009 Online 2 D/3 D Event Display RPC Strip Monitoring Online Error Reporting ASET talk - S. S. Upadhya 48

VME BASED DAQ SETUP X strip signals Y strip signals Analog Front End RPC Stack Digital Front End Trigger Module Timing info VME CRATE Scaler Final Trigger Event/ Monitor Data TDC Event Trigger Controller & Readout Module Linux based DAQ software (C++, Qt, ROOT) Interrupt Based Multi-Threaded Graphical User Interface 16 October, 2009 Online 2 D/3 D Event Display RPC Strip Monitoring Online Error Reporting ASET talk - S. S. Upadhya 48

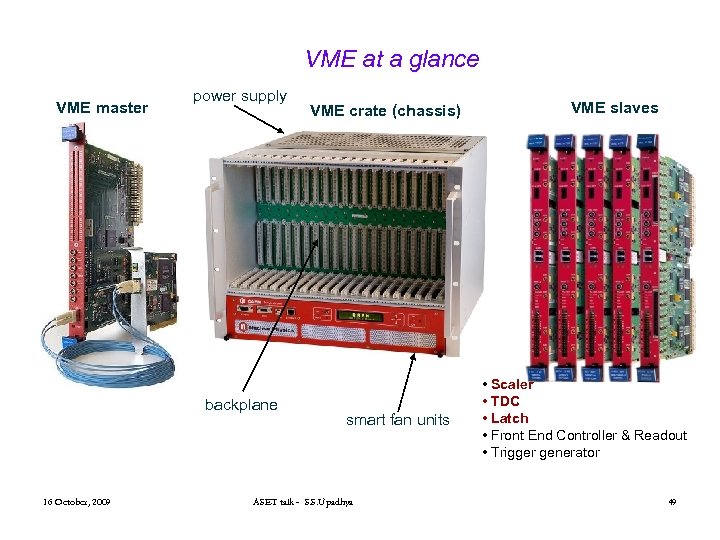

VME at a glance VME master power supply backplane 16 October, 2009 VME crate (chassis) smart fan units ASET talk - S. S. Upadhya VME slaves • Scaler • TDC • Latch • Front End Controller & Readout • Trigger generator 49

VME at a glance VME master power supply backplane 16 October, 2009 VME crate (chassis) smart fan units ASET talk - S. S. Upadhya VME slaves • Scaler • TDC • Latch • Front End Controller & Readout • Trigger generator 49

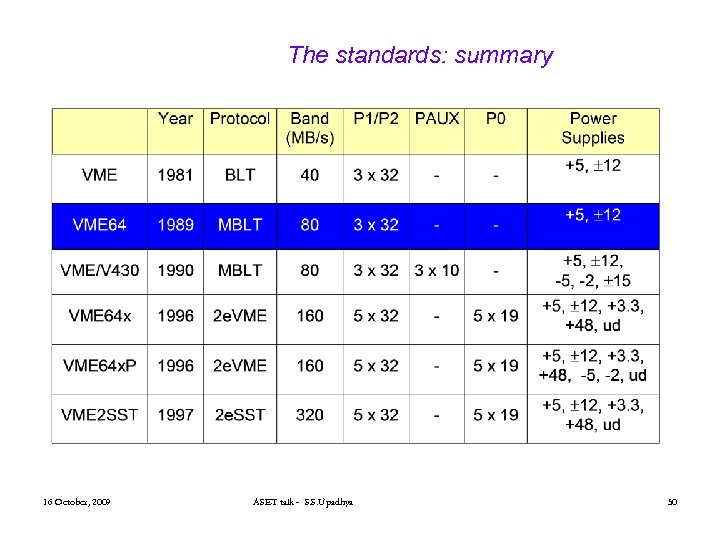

The standards: summary 16 October, 2009 ASET talk - S. S. Upadhya 50

The standards: summary 16 October, 2009 ASET talk - S. S. Upadhya 50

INO team at RPC lab Thank you 16 October, 2009 ASET talk - S. S. Upadhya 51 51

INO team at RPC lab Thank you 16 October, 2009 ASET talk - S. S. Upadhya 51 51

16 October, 2009 ASET talk - S. S. Upadhya 65

16 October, 2009 ASET talk - S. S. Upadhya 65

16 October, 2009 ASET talk - S. S. Upadhya 66

16 October, 2009 ASET talk - S. S. Upadhya 66

16 October, 2009 ASET talk - S. S. Upadhya 67

16 October, 2009 ASET talk - S. S. Upadhya 67