47fbb8968eb754d356cba4a3af22366d.ppt

- Количество слайдов: 18

Electrical Engineering Department, Technion, Haifa, Israel Automatic Hardware-Efficient So. C Integration by Qo. S Network on Chip Evgeny Bolotin, Arkadiy Morgenshtein, Israel Cidon, Ran Ginosar, Avinoam Kolodny QNo. C Research Group, Electrical Engineering Department Technion – Israel Institute of Technology Haifa, Israel 1 Evgeny Bolotin – ICECS 2004

Electrical Engineering Department, Technion, Haifa, Israel Automatic Hardware-Efficient So. C Integration by Qo. S Network on Chip Evgeny Bolotin, Arkadiy Morgenshtein, Israel Cidon, Ran Ginosar, Avinoam Kolodny QNo. C Research Group, Electrical Engineering Department Technion – Israel Institute of Technology Haifa, Israel 1 Evgeny Bolotin – ICECS 2004

Outline • Introduction: So. C Integration Challenge • No. C Concept and QNo. C Architecture • So. C Automatic Integration by QNo. C • Summary 2 Evgeny Bolotin – ICECS 2004

Outline • Introduction: So. C Integration Challenge • No. C Concept and QNo. C Architecture • So. C Automatic Integration by QNo. C • Summary 2 Evgeny Bolotin – ICECS 2004

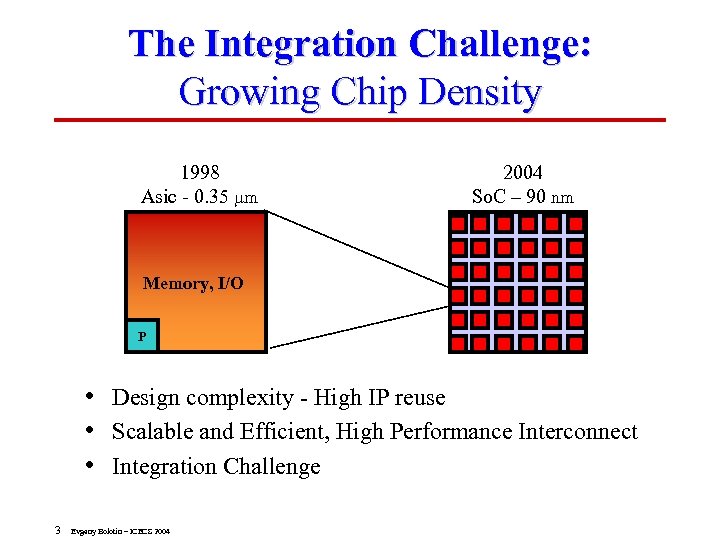

The Integration Challenge: Growing Chip Density 1998 Asic - 0. 35 mm 2004 So. C – 90 nm Memory, I/O P • Design complexity - High IP reuse • Scalable and Efficient, High Performance Interconnect • Integration Challenge 3 Evgeny Bolotin – ICECS 2004

The Integration Challenge: Growing Chip Density 1998 Asic - 0. 35 mm 2004 So. C – 90 nm Memory, I/O P • Design complexity - High IP reuse • Scalable and Efficient, High Performance Interconnect • Integration Challenge 3 Evgeny Bolotin – ICECS 2004

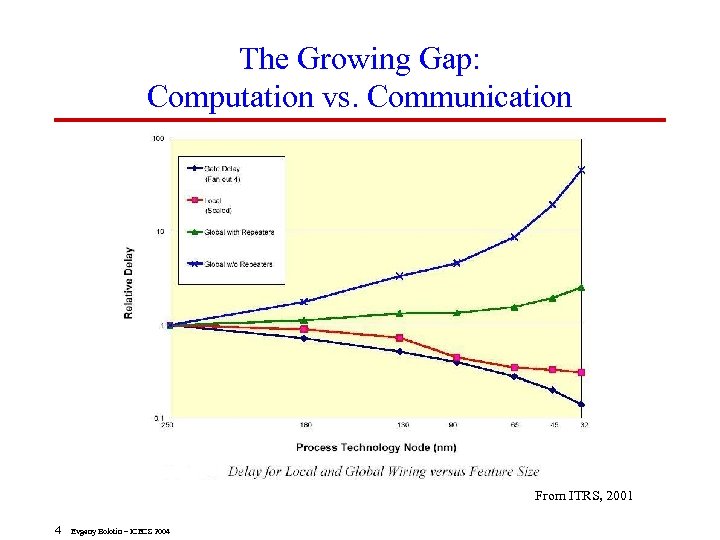

The Growing Gap: Computation vs. Communication From ITRS, 2001 4 Evgeny Bolotin – ICECS 2004

The Growing Gap: Computation vs. Communication From ITRS, 2001 4 Evgeny Bolotin – ICECS 2004

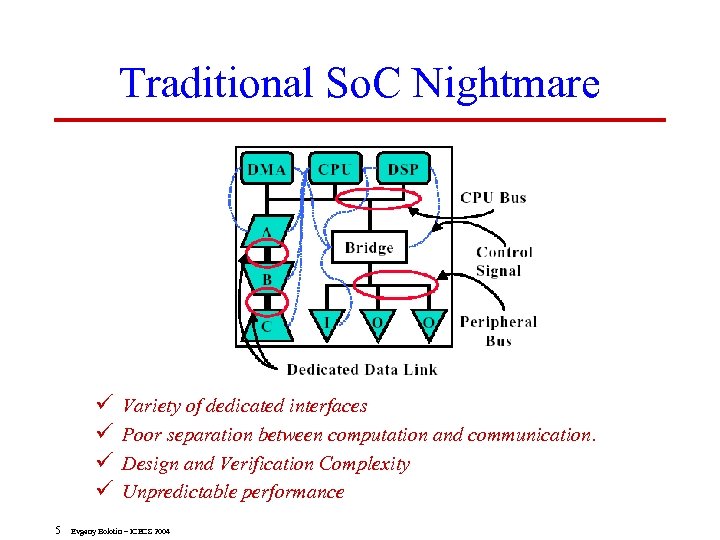

Traditional So. C Nightmare ü ü 5 Variety of dedicated interfaces Poor separation between computation and communication. Design and Verification Complexity Unpredictable performance Evgeny Bolotin – ICECS 2004

Traditional So. C Nightmare ü ü 5 Variety of dedicated interfaces Poor separation between computation and communication. Design and Verification Complexity Unpredictable performance Evgeny Bolotin – ICECS 2004

Solution – Network on Chip (No. C) • Scalability • Concurrency, effective spatial reuse of resources • Higher bandwidth • Higher levels of abstraction • Modularity – Productivity Improvement Easier So. C Integration! 6 Evgeny Bolotin – ICECS 2004

Solution – Network on Chip (No. C) • Scalability • Concurrency, effective spatial reuse of resources • Higher bandwidth • Higher levels of abstraction • Modularity – Productivity Improvement Easier So. C Integration! 6 Evgeny Bolotin – ICECS 2004

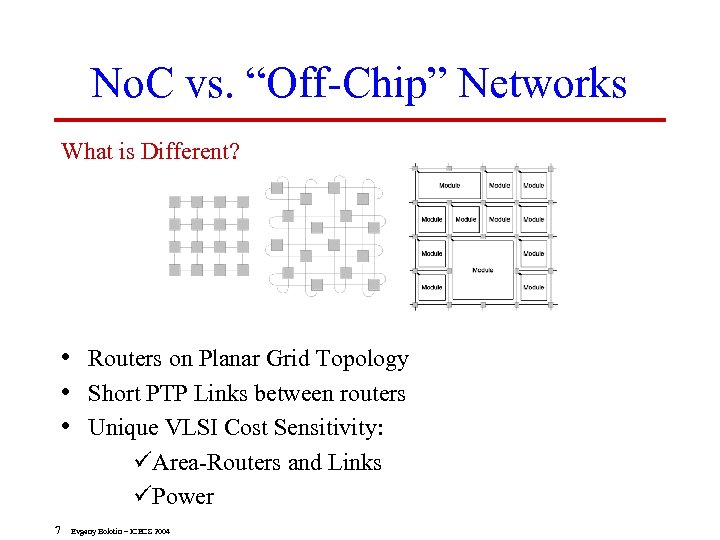

No. C vs. “Off-Chip” Networks What is Different? • Routers on Planar Grid Topology • Short PTP Links between routers • Unique VLSI Cost Sensitivity: üArea-Routers and Links üPower 7 Evgeny Bolotin – ICECS 2004

No. C vs. “Off-Chip” Networks What is Different? • Routers on Planar Grid Topology • Short PTP Links between routers • Unique VLSI Cost Sensitivity: üArea-Routers and Links üPower 7 Evgeny Bolotin – ICECS 2004

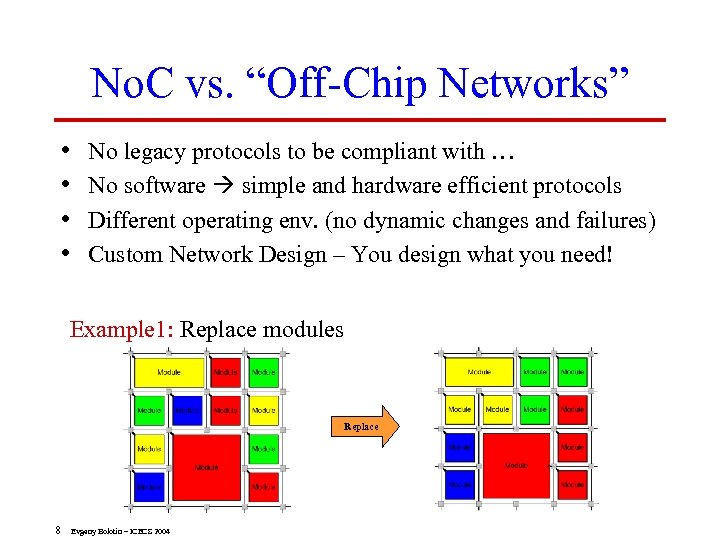

No. C vs. “Off-Chip Networks” • • No legacy protocols to be compliant with … No software simple and hardware efficient protocols Different operating env. (no dynamic changes and failures) Custom Network Design – You design what you need! Example 1: Replace modules Replace 8 Evgeny Bolotin – ICECS 2004

No. C vs. “Off-Chip Networks” • • No legacy protocols to be compliant with … No software simple and hardware efficient protocols Different operating env. (no dynamic changes and failures) Custom Network Design – You design what you need! Example 1: Replace modules Replace 8 Evgeny Bolotin – ICECS 2004

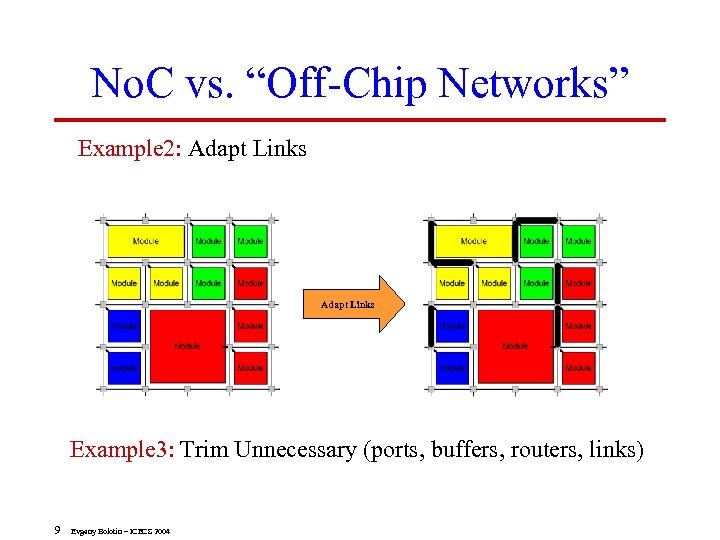

No. C vs. “Off-Chip Networks” Example 2: Adapt Links Example 3: Trim Unnecessary (ports, buffers, routers, links) 9 Evgeny Bolotin – ICECS 2004

No. C vs. “Off-Chip Networks” Example 2: Adapt Links Example 3: Trim Unnecessary (ports, buffers, routers, links) 9 Evgeny Bolotin – ICECS 2004

QNo. C: Qo. S No. C Define Service Levels (SLs): • Signaling • Real-Time • Read/Write (RD/WR) • Block-Transfer ü Different Qo. S for each SL 10 Evgeny Bolotin – ICECS 2004

QNo. C: Qo. S No. C Define Service Levels (SLs): • Signaling • Real-Time • Read/Write (RD/WR) • Block-Transfer ü Different Qo. S for each SL 10 Evgeny Bolotin – ICECS 2004

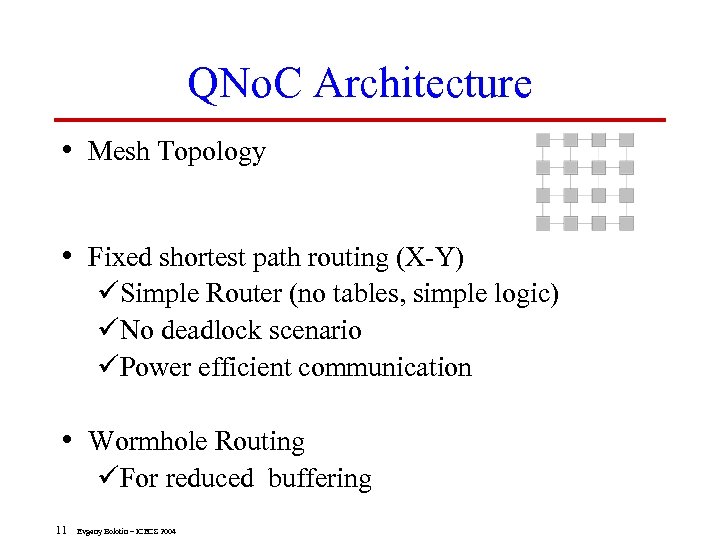

QNo. C Architecture • Mesh Topology • Fixed shortest path routing (X-Y) üSimple Router (no tables, simple logic) üNo deadlock scenario üPower efficient communication • Wormhole Routing üFor reduced buffering 11 Evgeny Bolotin – ICECS 2004

QNo. C Architecture • Mesh Topology • Fixed shortest path routing (X-Y) üSimple Router (no tables, simple logic) üNo deadlock scenario üPower efficient communication • Wormhole Routing üFor reduced buffering 11 Evgeny Bolotin – ICECS 2004

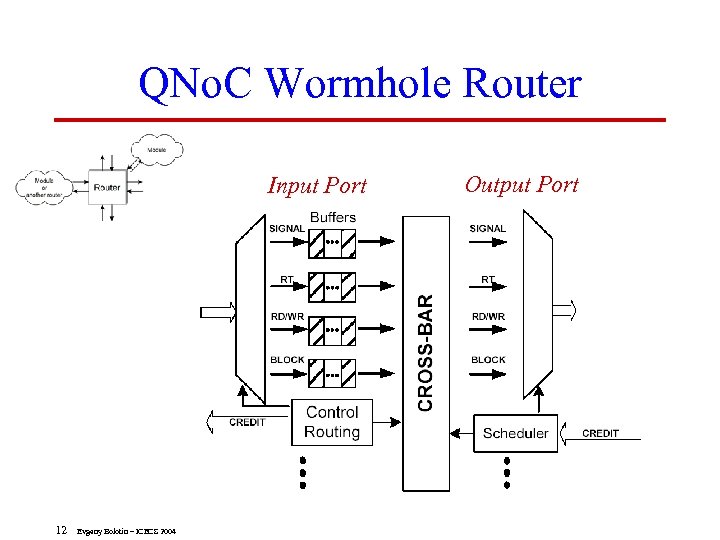

QNo. C Wormhole Router Input Port 12 Evgeny Bolotin – ICECS 2004 Output Port

QNo. C Wormhole Router Input Port 12 Evgeny Bolotin – ICECS 2004 Output Port

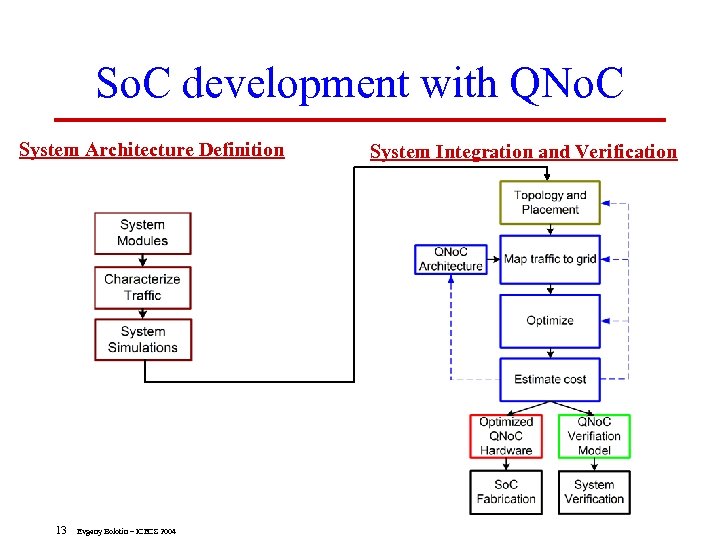

So. C development with QNo. C System Architecture Definition 13 Evgeny Bolotin – ICECS 2004 System Integration and Verification

So. C development with QNo. C System Architecture Definition 13 Evgeny Bolotin – ICECS 2004 System Integration and Verification

Integration Automation Tools QNo. C Placement and Topology Generation • • • 14 Analyzes System Modules and Traffic Derives No. C Topology and Module Placement Minimizes Spatial Traffic Density For Lower Area and Power Evgeny Bolotin – ICECS 2004

Integration Automation Tools QNo. C Placement and Topology Generation • • • 14 Analyzes System Modules and Traffic Derives No. C Topology and Module Placement Minimizes Spatial Traffic Density For Lower Area and Power Evgeny Bolotin – ICECS 2004

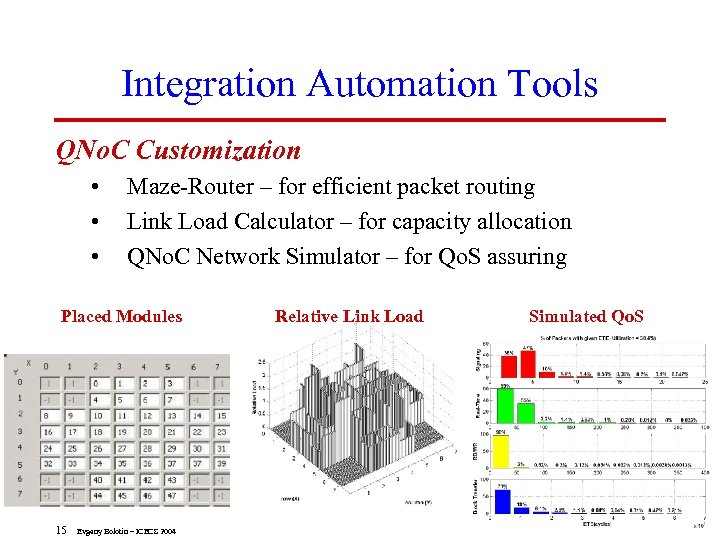

Integration Automation Tools QNo. C Customization • • • Maze-Router – for efficient packet routing Link Load Calculator – for capacity allocation QNo. C Network Simulator – for Qo. S assuring Placed Modules 15 Evgeny Bolotin – ICECS 2004 Relative Link Load Simulated Qo. S

Integration Automation Tools QNo. C Customization • • • Maze-Router – for efficient packet routing Link Load Calculator – for capacity allocation QNo. C Network Simulator – for Qo. S assuring Placed Modules 15 Evgeny Bolotin – ICECS 2004 Relative Link Load Simulated Qo. S

Integration Automation Tools Automatic Hardware Generation • Use calculated QNo. C parameters and QNo. C VHDL templates library • Create Synthesizable VHDL description of QNo. C • Including • Module wrappers • Synchronization and SER/DES circuitry • Routing logic and tables System Verification • QNo. C verification models • For hardware and system simulations 16 Evgeny Bolotin – ICECS 2004

Integration Automation Tools Automatic Hardware Generation • Use calculated QNo. C parameters and QNo. C VHDL templates library • Create Synthesizable VHDL description of QNo. C • Including • Module wrappers • Synchronization and SER/DES circuitry • Routing logic and tables System Verification • QNo. C verification models • For hardware and system simulations 16 Evgeny Bolotin – ICECS 2004

Summary • So. C Integration Challenge • No. C Concept • QNo. C Architecture • So. C Integration by QNo. C • Automatic Integration Tools 17 Evgeny Bolotin – ICECS 2004

Summary • So. C Integration Challenge • No. C Concept • QNo. C Architecture • So. C Integration by QNo. C • Automatic Integration Tools 17 Evgeny Bolotin – ICECS 2004

More Info: www. ee. technion. ac. il/qnoc 18 Evgeny Bolotin – ICECS 2004

More Info: www. ee. technion. ac. il/qnoc 18 Evgeny Bolotin – ICECS 2004