894b38d62c8af6bc7008c0db5a0edc37.ppt

- Количество слайдов: 30

EE (CE) 6304 Computer Architecture Lecture #7 (9/20/17) Yiorgos Makris Professor Department of Electrical Engineering University of Texas at Dallas Course Web-site: http: //www. utdallas. edu/~gxm 112130/EE 6304 FA 17

EE (CE) 6304 Computer Architecture Lecture #7 (9/20/17) Yiorgos Makris Professor Department of Electrical Engineering University of Texas at Dallas Course Web-site: http: //www. utdallas. edu/~gxm 112130/EE 6304 FA 17

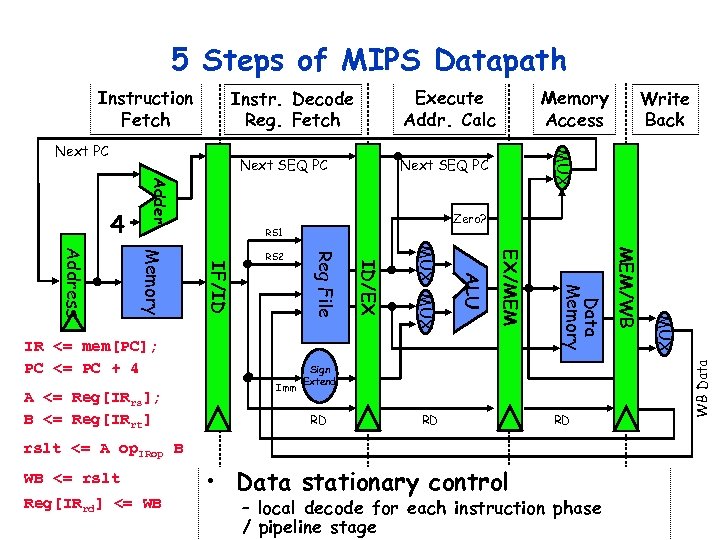

5 Steps of MIPS Datapath Execute Addr. Calc Instr. Decode Reg. Fetch Next SEQ PC Adder 4 Zero? RS 1 RD RD RD rslt <= A op. IRop B WB <= rslt Reg[IRrd] <= WB • Data stationary control – local decode for each instruction phase / pipeline stage MUX Sign Extend MEM/WB Data Memory EX/MEM ALU Imm MUX A <= Reg[IRrs]; B <= Reg[IRrt] ID/EX IR <= mem[PC]; PC <= PC + 4 Reg File IF/ID Memory Address RS 2 Write Back MUX Next PC Memory Access WB Data Instruction Fetch

5 Steps of MIPS Datapath Execute Addr. Calc Instr. Decode Reg. Fetch Next SEQ PC Adder 4 Zero? RS 1 RD RD RD rslt <= A op. IRop B WB <= rslt Reg[IRrd] <= WB • Data stationary control – local decode for each instruction phase / pipeline stage MUX Sign Extend MEM/WB Data Memory EX/MEM ALU Imm MUX A <= Reg[IRrs]; B <= Reg[IRrt] ID/EX IR <= mem[PC]; PC <= PC + 4 Reg File IF/ID Memory Address RS 2 Write Back MUX Next PC Memory Access WB Data Instruction Fetch

Impact of Hazards on Performance Software Scheduling around Hazards Out-of-order Scheduling

Impact of Hazards on Performance Software Scheduling around Hazards Out-of-order Scheduling

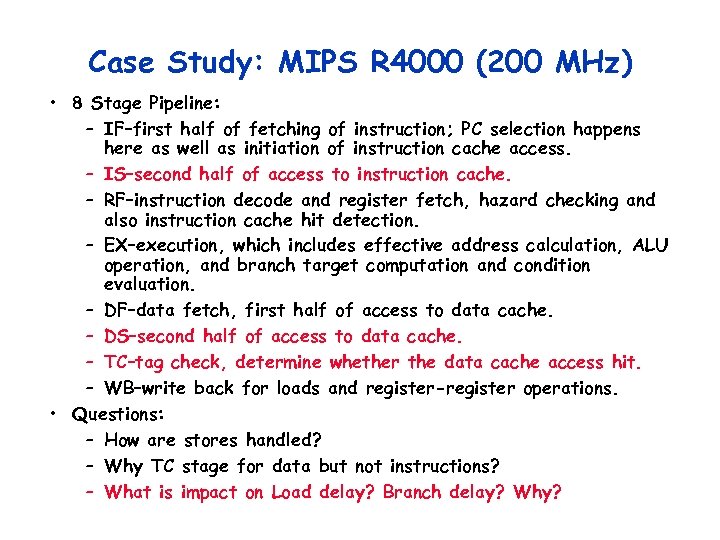

Case Study: MIPS R 4000 (200 MHz) • 8 Stage Pipeline: – IF–first half of fetching of instruction; PC selection happens here as well as initiation of instruction cache access. – IS–second half of access to instruction cache. – RF–instruction decode and register fetch, hazard checking and also instruction cache hit detection. – EX–execution, which includes effective address calculation, ALU operation, and branch target computation and condition evaluation. – DF–data fetch, first half of access to data cache. – DS–second half of access to data cache. – TC–tag check, determine whether the data cache access hit. – WB–write back for loads and register-register operations. • Questions: – How are stores handled? – Why TC stage for data but not instructions? – What is impact on Load delay? Branch delay? Why?

Case Study: MIPS R 4000 (200 MHz) • 8 Stage Pipeline: – IF–first half of fetching of instruction; PC selection happens here as well as initiation of instruction cache access. – IS–second half of access to instruction cache. – RF–instruction decode and register fetch, hazard checking and also instruction cache hit detection. – EX–execution, which includes effective address calculation, ALU operation, and branch target computation and condition evaluation. – DF–data fetch, first half of access to data cache. – DS–second half of access to data cache. – TC–tag check, determine whether the data cache access hit. – WB–write back for loads and register-register operations. • Questions: – How are stores handled? – Why TC stage for data but not instructions? – What is impact on Load delay? Branch delay? Why?

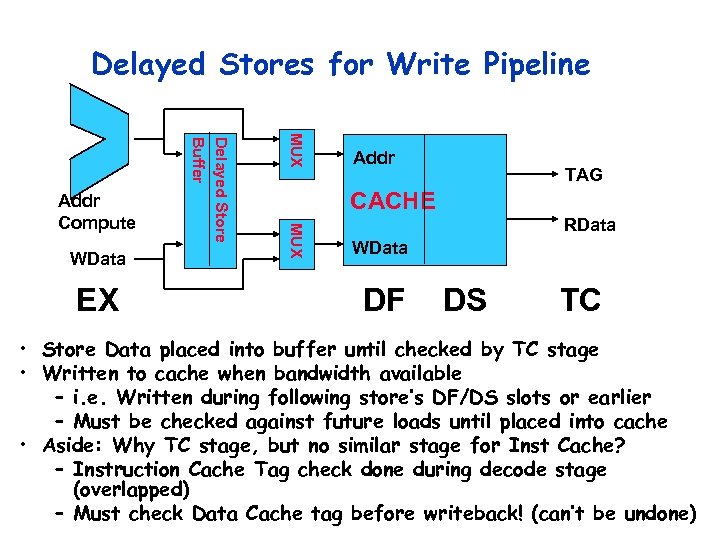

Delayed Stores for Write Pipeline TAG CACHE MUX EX MUX WData Delayed Store Buffer Addr Compute Addr RData WData DF DS TC • Store Data placed into buffer until checked by TC stage • Written to cache when bandwidth available – i. e. Written during following store’s DF/DS slots or earlier – Must be checked against future loads until placed into cache • Aside: Why TC stage, but no similar stage for Inst Cache? – Instruction Cache Tag check done during decode stage (overlapped) – Must check Data Cache tag before writeback! (can’t be undone)

Delayed Stores for Write Pipeline TAG CACHE MUX EX MUX WData Delayed Store Buffer Addr Compute Addr RData WData DF DS TC • Store Data placed into buffer until checked by TC stage • Written to cache when bandwidth available – i. e. Written during following store’s DF/DS slots or earlier – Must be checked against future loads until placed into cache • Aside: Why TC stage, but no similar stage for Inst Cache? – Instruction Cache Tag check done during decode stage (overlapped) – Must check Data Cache tag before writeback! (can’t be undone)

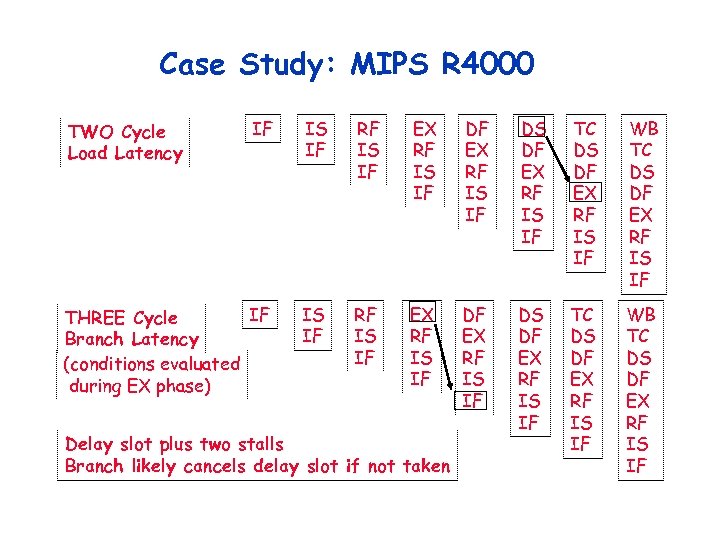

Case Study: MIPS R 4000 IF IS IF RF IS IF EX RF IS IF DS DF EX RF IS IF TC DS DF EX RF IS IF WB TC DS DF EX RF IS IF IF THREE Cycle Branch Latency (conditions evaluated during EX phase) IS IF RF IS IF EX RF IS IF DS DF EX RF IS IF TC DS DF EX RF IS IF WB TC DS DF EX RF IS IF TWO Cycle Load Latency Delay slot plus two stalls Branch likely cancels delay slot if not taken

Case Study: MIPS R 4000 IF IS IF RF IS IF EX RF IS IF DS DF EX RF IS IF TC DS DF EX RF IS IF WB TC DS DF EX RF IS IF IF THREE Cycle Branch Latency (conditions evaluated during EX phase) IS IF RF IS IF EX RF IS IF DS DF EX RF IS IF TC DS DF EX RF IS IF WB TC DS DF EX RF IS IF TWO Cycle Load Latency Delay slot plus two stalls Branch likely cancels delay slot if not taken

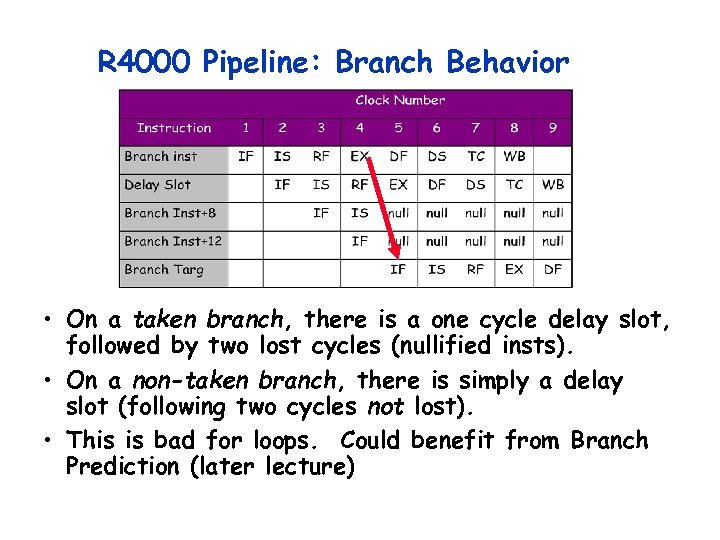

R 4000 Pipeline: Branch Behavior • On a taken branch, there is a one cycle delay slot, followed by two lost cycles (nullified insts). • On a non-taken branch, there is simply a delay slot (following two cycles not lost). • This is bad for loops. Could benefit from Branch Prediction (later lecture)

R 4000 Pipeline: Branch Behavior • On a taken branch, there is a one cycle delay slot, followed by two lost cycles (nullified insts). • On a non-taken branch, there is simply a delay slot (following two cycles not lost). • This is bad for loops. Could benefit from Branch Prediction (later lecture)

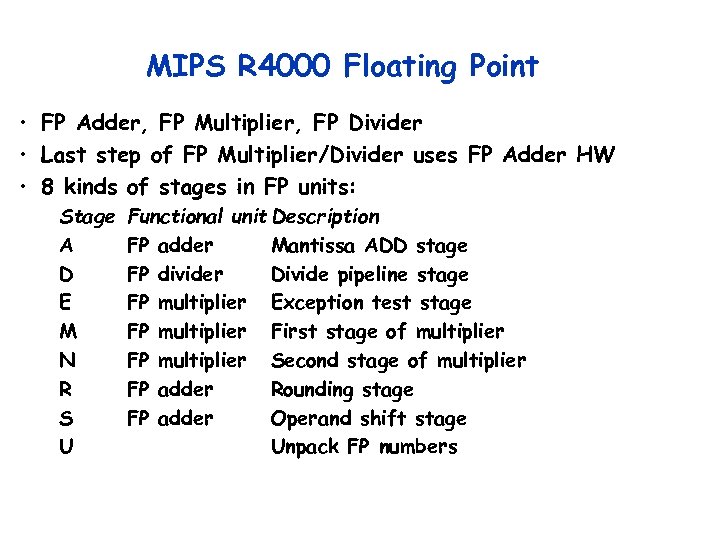

MIPS R 4000 Floating Point • FP Adder, FP Multiplier, FP Divider • Last step of FP Multiplier/Divider uses FP Adder HW • 8 kinds of stages in FP units: Stage A D E M N R S U Functional unit Description FP adder Mantissa ADD stage FP divider Divide pipeline stage FP multiplier Exception test stage FP multiplier First stage of multiplier FP multiplier Second stage of multiplier FP adder Rounding stage FP adder Operand shift stage Unpack FP numbers

MIPS R 4000 Floating Point • FP Adder, FP Multiplier, FP Divider • Last step of FP Multiplier/Divider uses FP Adder HW • 8 kinds of stages in FP units: Stage A D E M N R S U Functional unit Description FP adder Mantissa ADD stage FP divider Divide pipeline stage FP multiplier Exception test stage FP multiplier First stage of multiplier FP multiplier Second stage of multiplier FP adder Rounding stage FP adder Operand shift stage Unpack FP numbers

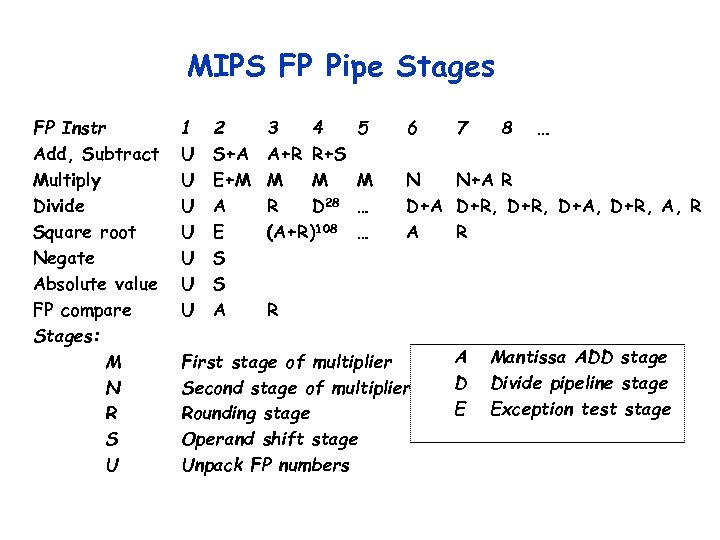

MIPS FP Pipe Stages FP Instr Add, Subtract Multiply Divide Square root Negate Absolute value FP compare Stages: M N R S U 1 U U U U 2 S+A E+M A E S S A 3 4 A+R R+S M M R D 28 (A+R)108 5 6 7 8 … M … … N N+A R D+A D+R, D+A, D+R, A, R A R R First stage of multiplier Second stage of multiplier Rounding stage Operand shift stage Unpack FP numbers A D E Mantissa ADD stage Divide pipeline stage Exception test stage

MIPS FP Pipe Stages FP Instr Add, Subtract Multiply Divide Square root Negate Absolute value FP compare Stages: M N R S U 1 U U U U 2 S+A E+M A E S S A 3 4 A+R R+S M M R D 28 (A+R)108 5 6 7 8 … M … … N N+A R D+A D+R, D+A, D+R, A, R A R R First stage of multiplier Second stage of multiplier Rounding stage Operand shift stage Unpack FP numbers A D E Mantissa ADD stage Divide pipeline stage Exception test stage

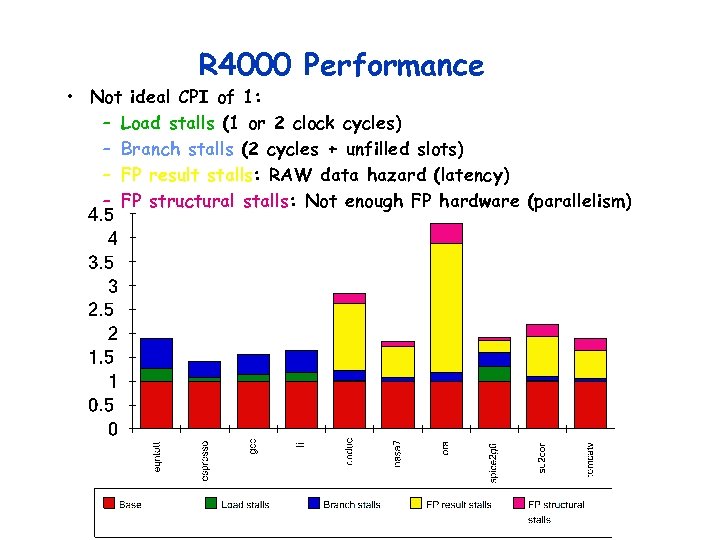

R 4000 Performance • Not ideal CPI of 1: – Load stalls (1 or 2 clock cycles) – Branch stalls (2 cycles + unfilled slots) – FP result stalls: RAW data hazard (latency) – FP structural stalls: Not enough FP hardware (parallelism)

R 4000 Performance • Not ideal CPI of 1: – Load stalls (1 or 2 clock cycles) – Branch stalls (2 cycles + unfilled slots) – FP result stalls: RAW data hazard (latency) – FP structural stalls: Not enough FP hardware (parallelism)

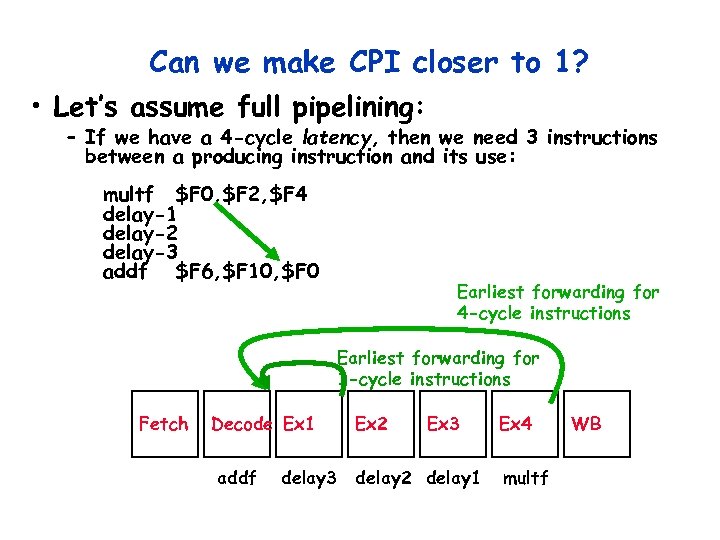

Can we make CPI closer to 1? • Let’s assume full pipelining: – If we have a 4 -cycle latency, then we need 3 instructions between a producing instruction and its use: multf $F 0, $F 2, $F 4 delay-1 delay-2 delay-3 addf $F 6, $F 10, $F 0 Earliest forwarding for 4 -cycle instructions Earliest forwarding for 1 -cycle instructions Fetch Decode Ex 1 addf Ex 2 Ex 3 delay 2 delay 1 Ex 4 multf WB

Can we make CPI closer to 1? • Let’s assume full pipelining: – If we have a 4 -cycle latency, then we need 3 instructions between a producing instruction and its use: multf $F 0, $F 2, $F 4 delay-1 delay-2 delay-3 addf $F 6, $F 10, $F 0 Earliest forwarding for 4 -cycle instructions Earliest forwarding for 1 -cycle instructions Fetch Decode Ex 1 addf Ex 2 Ex 3 delay 2 delay 1 Ex 4 multf WB

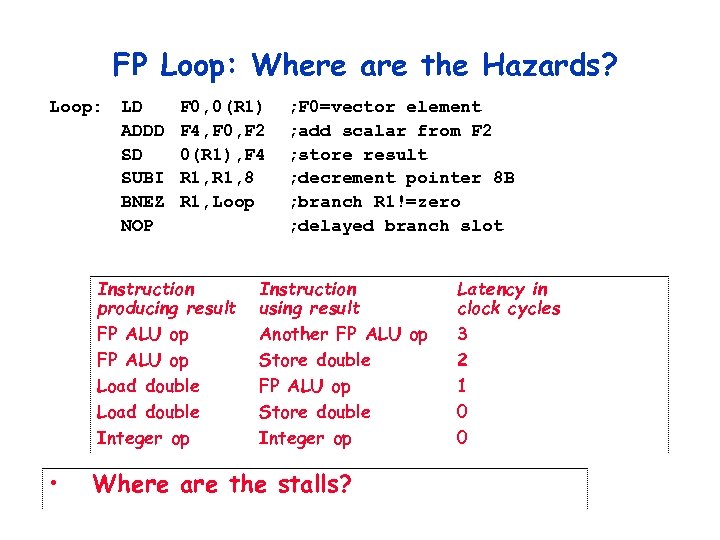

FP Loop: Where are the Hazards? Loop: LD ADDD SD SUBI BNEZ NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 R 1, 8 R 1, Loop Instruction producing result FP ALU op Load double Integer op • ; F 0=vector element ; add scalar from F 2 ; store result ; decrement pointer 8 B ; branch R 1!=zero ; delayed branch slot Instruction using result Another FP ALU op Store double Integer op Where are the stalls? Latency in clock cycles 3 2 1 0 0

FP Loop: Where are the Hazards? Loop: LD ADDD SD SUBI BNEZ NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 R 1, 8 R 1, Loop Instruction producing result FP ALU op Load double Integer op • ; F 0=vector element ; add scalar from F 2 ; store result ; decrement pointer 8 B ; branch R 1!=zero ; delayed branch slot Instruction using result Another FP ALU op Store double Integer op Where are the stalls? Latency in clock cycles 3 2 1 0 0

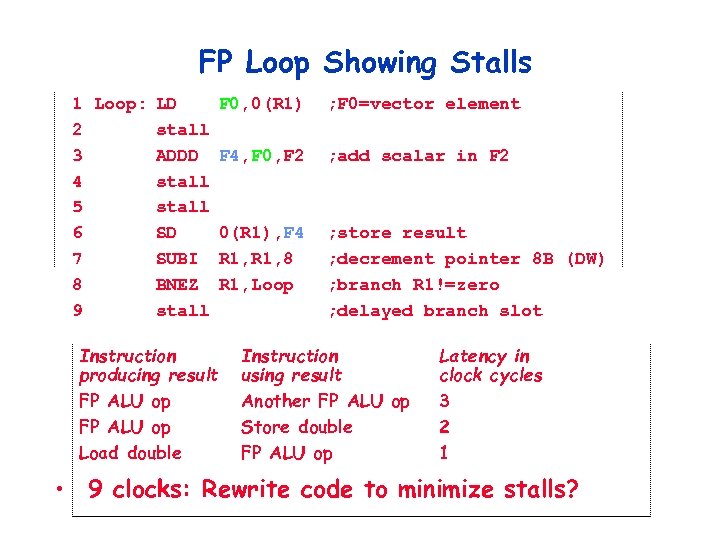

FP Loop Showing Stalls 1 Loop: LD F 0, 0(R 1) 2 stall 3 ADDD F 4, F 0, F 2 4 stall 5 stall 6 SD 0(R 1), F 4 7 SUBI R 1, 8 8 BNEZ R 1, Loop 9 stall Instruction producing result FP ALU op Load double ; F 0=vector element ; add scalar in F 2 ; store result ; decrement pointer 8 B (DW) ; branch R 1!=zero ; delayed branch slot Instruction using result Another FP ALU op Store double FP ALU op Latency in clock cycles 3 2 1 • 9 clocks: Rewrite code to minimize stalls?

FP Loop Showing Stalls 1 Loop: LD F 0, 0(R 1) 2 stall 3 ADDD F 4, F 0, F 2 4 stall 5 stall 6 SD 0(R 1), F 4 7 SUBI R 1, 8 8 BNEZ R 1, Loop 9 stall Instruction producing result FP ALU op Load double ; F 0=vector element ; add scalar in F 2 ; store result ; decrement pointer 8 B (DW) ; branch R 1!=zero ; delayed branch slot Instruction using result Another FP ALU op Store double FP ALU op Latency in clock cycles 3 2 1 • 9 clocks: Rewrite code to minimize stalls?

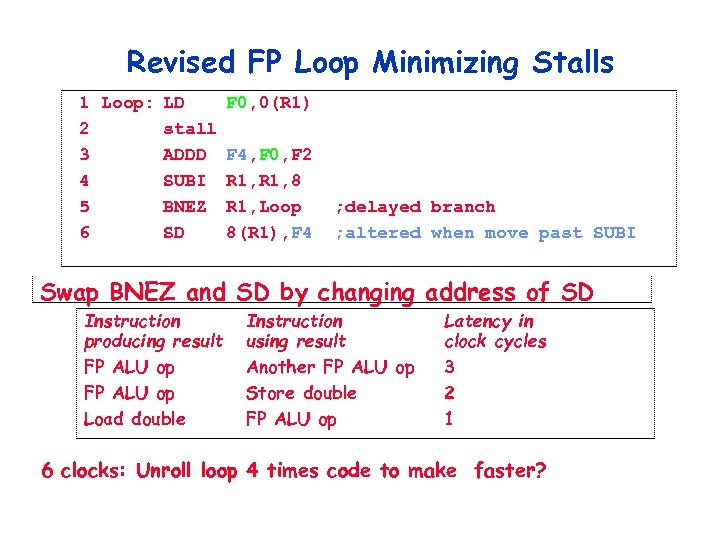

Revised FP Loop Minimizing Stalls 1 Loop: LD F 0, 0(R 1) 2 stall 3 ADDD F 4, F 0, F 2 4 SUBI R 1, 8 5 BNEZ R 1, Loop 6 SD 8(R 1), F 4 ; delayed branch ; altered when move past SUBI Swap BNEZ and SD by changing address of SD Instruction producing result FP ALU op Load double Instruction using result Another FP ALU op Store double FP ALU op Latency in clock cycles 3 2 1 6 clocks: Unroll loop 4 times code to make faster?

Revised FP Loop Minimizing Stalls 1 Loop: LD F 0, 0(R 1) 2 stall 3 ADDD F 4, F 0, F 2 4 SUBI R 1, 8 5 BNEZ R 1, Loop 6 SD 8(R 1), F 4 ; delayed branch ; altered when move past SUBI Swap BNEZ and SD by changing address of SD Instruction producing result FP ALU op Load double Instruction using result Another FP ALU op Store double FP ALU op Latency in clock cycles 3 2 1 6 clocks: Unroll loop 4 times code to make faster?

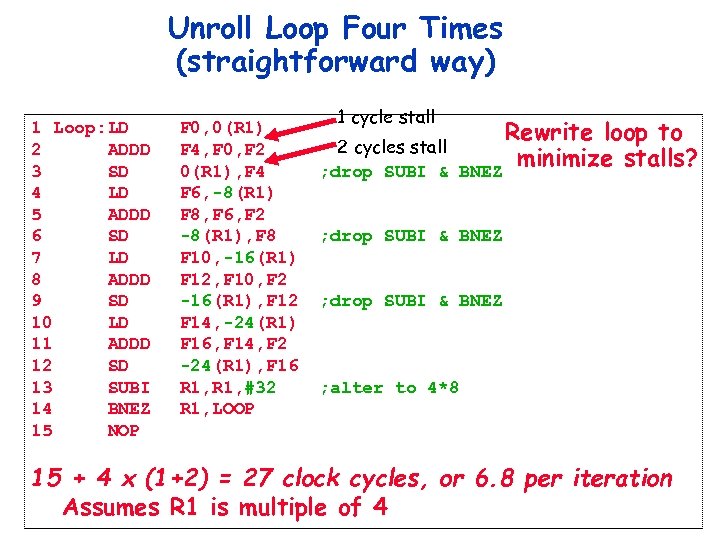

Unroll Loop Four Times (straightforward way) 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 6, -8(R 1) F 8, F 6, F 2 -8(R 1), F 8 F 10, -16(R 1) F 12, F 10, F 2 -16(R 1), F 12 F 14, -24(R 1) F 16, F 14, F 2 -24(R 1), F 16 R 1, #32 R 1, LOOP 1 cycle stall 2 cycles stall ; drop SUBI & Rewrite loop to minimize stalls? BNEZ ; drop SUBI & BNEZ ; alter to 4*8 15 + 4 x (1+2) = 27 clock cycles, or 6. 8 per iteration Assumes R 1 is multiple of 4

Unroll Loop Four Times (straightforward way) 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 6, -8(R 1) F 8, F 6, F 2 -8(R 1), F 8 F 10, -16(R 1) F 12, F 10, F 2 -16(R 1), F 12 F 14, -24(R 1) F 16, F 14, F 2 -24(R 1), F 16 R 1, #32 R 1, LOOP 1 cycle stall 2 cycles stall ; drop SUBI & Rewrite loop to minimize stalls? BNEZ ; drop SUBI & BNEZ ; alter to 4*8 15 + 4 x (1+2) = 27 clock cycles, or 6. 8 per iteration Assumes R 1 is multiple of 4

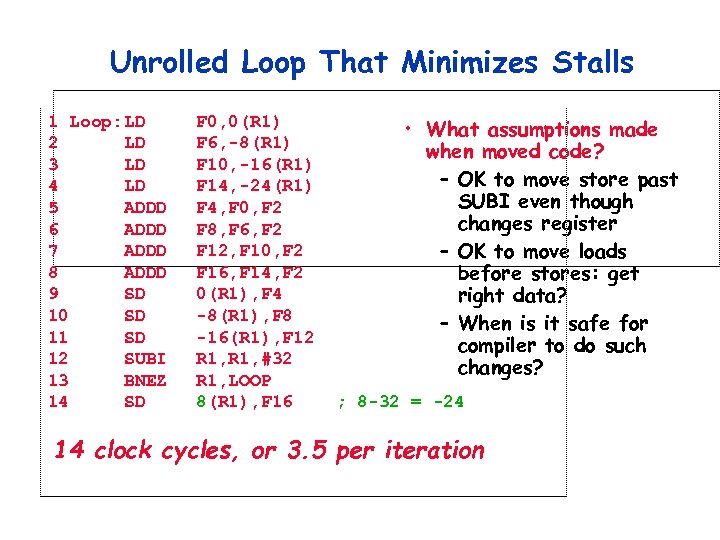

Unrolled Loop That Minimizes Stalls 1 Loop: LD 2 LD 3 LD 4 LD 5 ADDD 6 ADDD 7 ADDD 8 ADDD 9 SD 10 SD 11 SD 12 SUBI 13 BNEZ 14 SD F 0, 0(R 1) F 6, -8(R 1) F 10, -16(R 1) F 14, -24(R 1) F 4, F 0, F 2 F 8, F 6, F 2 F 12, F 10, F 2 F 16, F 14, F 2 0(R 1), F 4 -8(R 1), F 8 -16(R 1), F 12 R 1, #32 R 1, LOOP 8(R 1), F 16 • What assumptions made when moved code? – OK to move store past SUBI even though changes register – OK to move loads before stores: get right data? – When is it safe for compiler to do such changes? ; 8 -32 = -24 14 clock cycles, or 3. 5 per iteration

Unrolled Loop That Minimizes Stalls 1 Loop: LD 2 LD 3 LD 4 LD 5 ADDD 6 ADDD 7 ADDD 8 ADDD 9 SD 10 SD 11 SD 12 SUBI 13 BNEZ 14 SD F 0, 0(R 1) F 6, -8(R 1) F 10, -16(R 1) F 14, -24(R 1) F 4, F 0, F 2 F 8, F 6, F 2 F 12, F 10, F 2 F 16, F 14, F 2 0(R 1), F 4 -8(R 1), F 8 -16(R 1), F 12 R 1, #32 R 1, LOOP 8(R 1), F 16 • What assumptions made when moved code? – OK to move store past SUBI even though changes register – OK to move loads before stores: get right data? – When is it safe for compiler to do such changes? ; 8 -32 = -24 14 clock cycles, or 3. 5 per iteration

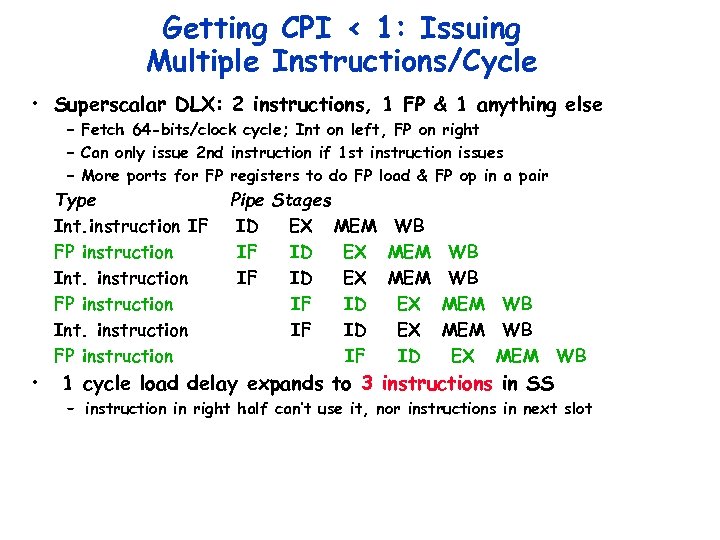

Getting CPI < 1: Issuing Multiple Instructions/Cycle • Superscalar DLX: 2 instructions, 1 FP & 1 anything else – Fetch 64 -bits/clock cycle; Int on left, FP on right – Can only issue 2 nd instruction if 1 st instruction issues – More ports for FP registers to do FP load & FP op in a pair Type Int. instruction IF FP instruction Int. instruction FP instruction • Pipe Stages ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB 1 cycle load delay expands to 3 instructions in SS – instruction in right half can’t use it, nor instructions in next slot

Getting CPI < 1: Issuing Multiple Instructions/Cycle • Superscalar DLX: 2 instructions, 1 FP & 1 anything else – Fetch 64 -bits/clock cycle; Int on left, FP on right – Can only issue 2 nd instruction if 1 st instruction issues – More ports for FP registers to do FP load & FP op in a pair Type Int. instruction IF FP instruction Int. instruction FP instruction • Pipe Stages ID EX MEM WB IF ID EX MEM WB IF ID EX MEM WB 1 cycle load delay expands to 3 instructions in SS – instruction in right half can’t use it, nor instructions in next slot

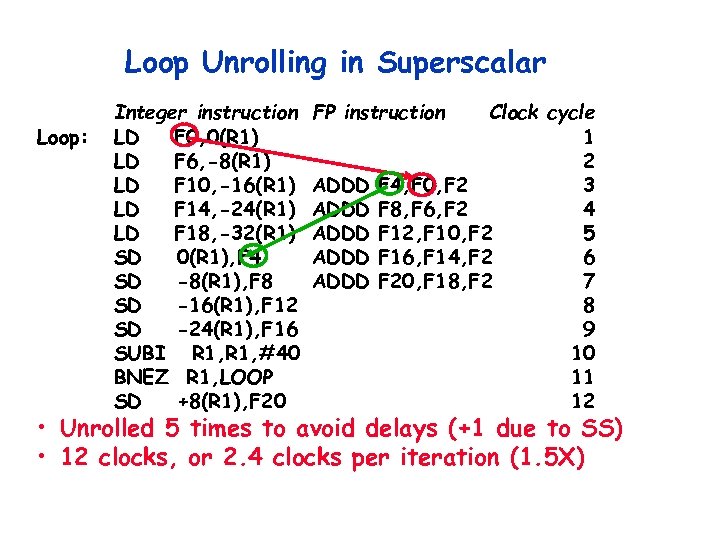

Loop Unrolling in Superscalar Loop: Integer instruction LD F 0, 0(R 1) LD F 6, -8(R 1) LD F 10, -16(R 1) LD F 14, -24(R 1) LD F 18, -32(R 1) SD 0(R 1), F 4 SD -8(R 1), F 8 SD -16(R 1), F 12 SD -24(R 1), F 16 SUBI R 1, #40 BNEZ R 1, LOOP SD +8(R 1), F 20 FP instruction ADDD ADDD Clock cycle 1 2 F 4, F 0, F 2 3 F 8, F 6, F 2 4 F 12, F 10, F 2 5 F 16, F 14, F 2 6 F 20, F 18, F 2 7 8 9 10 11 12 • Unrolled 5 times to avoid delays (+1 due to SS) • 12 clocks, or 2. 4 clocks per iteration (1. 5 X)

Loop Unrolling in Superscalar Loop: Integer instruction LD F 0, 0(R 1) LD F 6, -8(R 1) LD F 10, -16(R 1) LD F 14, -24(R 1) LD F 18, -32(R 1) SD 0(R 1), F 4 SD -8(R 1), F 8 SD -16(R 1), F 12 SD -24(R 1), F 16 SUBI R 1, #40 BNEZ R 1, LOOP SD +8(R 1), F 20 FP instruction ADDD ADDD Clock cycle 1 2 F 4, F 0, F 2 3 F 8, F 6, F 2 4 F 12, F 10, F 2 5 F 16, F 14, F 2 6 F 20, F 18, F 2 7 8 9 10 11 12 • Unrolled 5 times to avoid delays (+1 due to SS) • 12 clocks, or 2. 4 clocks per iteration (1. 5 X)

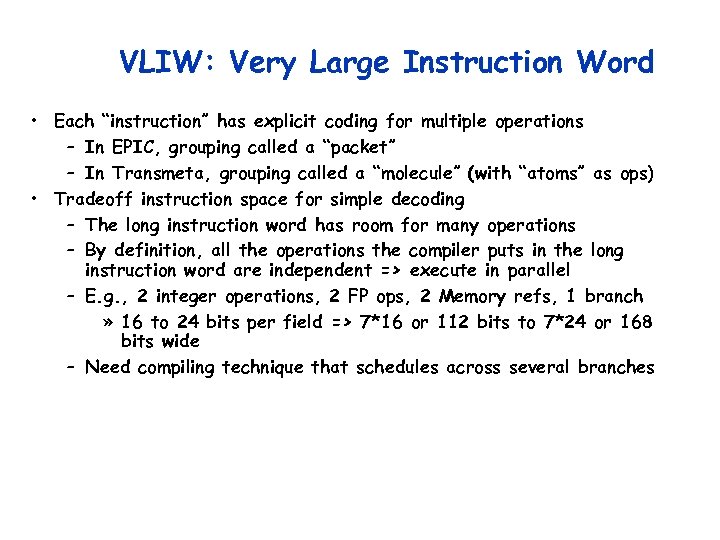

VLIW: Very Large Instruction Word • Each “instruction” has explicit coding for multiple operations – In EPIC, grouping called a “packet” – In Transmeta, grouping called a “molecule” (with “atoms” as ops) • Tradeoff instruction space for simple decoding – The long instruction word has room for many operations – By definition, all the operations the compiler puts in the long instruction word are independent => execute in parallel – E. g. , 2 integer operations, 2 FP ops, 2 Memory refs, 1 branch » 16 to 24 bits per field => 7*16 or 112 bits to 7*24 or 168 bits wide – Need compiling technique that schedules across several branches

VLIW: Very Large Instruction Word • Each “instruction” has explicit coding for multiple operations – In EPIC, grouping called a “packet” – In Transmeta, grouping called a “molecule” (with “atoms” as ops) • Tradeoff instruction space for simple decoding – The long instruction word has room for many operations – By definition, all the operations the compiler puts in the long instruction word are independent => execute in parallel – E. g. , 2 integer operations, 2 FP ops, 2 Memory refs, 1 branch » 16 to 24 bits per field => 7*16 or 112 bits to 7*24 or 168 bits wide – Need compiling technique that schedules across several branches

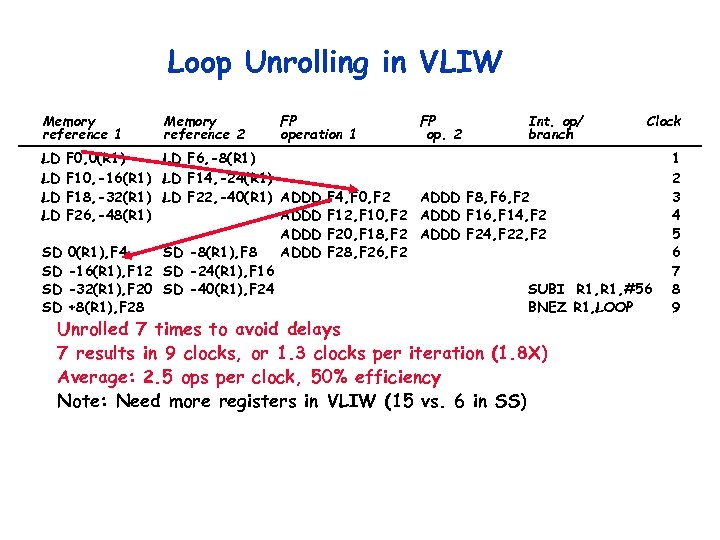

Loop Unrolling in VLIW Memory reference 1 Memory reference 2 FP operation 1 FP op. 2 Int. op/ branch LD LD Clock F 0, 0(R 1) LD F 6, -8(R 1) F 10, -16(R 1) LD F 14, -24(R 1) F 18, -32(R 1) LD F 22, -40(R 1) ADDD F 4, F 0, F 2 ADDD F 8, F 6, F 26, -48(R 1) ADDD F 12, F 10, F 2 ADDD F 16, F 14, F 2 ADDD F 20, F 18, F 2 ADDD F 24, F 22, F 2 SD 0(R 1), F 4 SD -8(R 1), F 8 ADDD F 28, F 26, F 2 SD -16(R 1), F 12 SD -24(R 1), F 16 SD -32(R 1), F 20 SD -40(R 1), F 24 SUBI R 1, #56 SD +8(R 1), F 28 BNEZ R 1, LOOP Unrolled 7 times to avoid delays 7 results in 9 clocks, or 1. 3 clocks per iteration (1. 8 X) Average: 2. 5 ops per clock, 50% efficiency Note: Need more registers in VLIW (15 vs. 6 in SS) 1 2 3 4 5 6 7 8 9

Loop Unrolling in VLIW Memory reference 1 Memory reference 2 FP operation 1 FP op. 2 Int. op/ branch LD LD Clock F 0, 0(R 1) LD F 6, -8(R 1) F 10, -16(R 1) LD F 14, -24(R 1) F 18, -32(R 1) LD F 22, -40(R 1) ADDD F 4, F 0, F 2 ADDD F 8, F 6, F 26, -48(R 1) ADDD F 12, F 10, F 2 ADDD F 16, F 14, F 2 ADDD F 20, F 18, F 2 ADDD F 24, F 22, F 2 SD 0(R 1), F 4 SD -8(R 1), F 8 ADDD F 28, F 26, F 2 SD -16(R 1), F 12 SD -24(R 1), F 16 SD -32(R 1), F 20 SD -40(R 1), F 24 SUBI R 1, #56 SD +8(R 1), F 28 BNEZ R 1, LOOP Unrolled 7 times to avoid delays 7 results in 9 clocks, or 1. 3 clocks per iteration (1. 8 X) Average: 2. 5 ops per clock, 50% efficiency Note: Need more registers in VLIW (15 vs. 6 in SS) 1 2 3 4 5 6 7 8 9

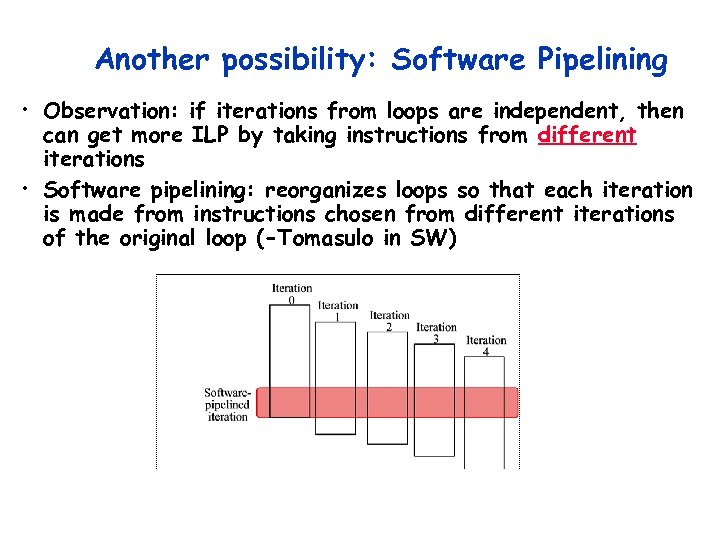

Another possibility: Software Pipelining • Observation: if iterations from loops are independent, then can get more ILP by taking instructions from different iterations • Software pipelining: reorganizes loops so that each iteration is made from instructions chosen from different iterations of the original loop ( Tomasulo in SW)

Another possibility: Software Pipelining • Observation: if iterations from loops are independent, then can get more ILP by taking instructions from different iterations • Software pipelining: reorganizes loops so that each iteration is made from instructions chosen from different iterations of the original loop ( Tomasulo in SW)

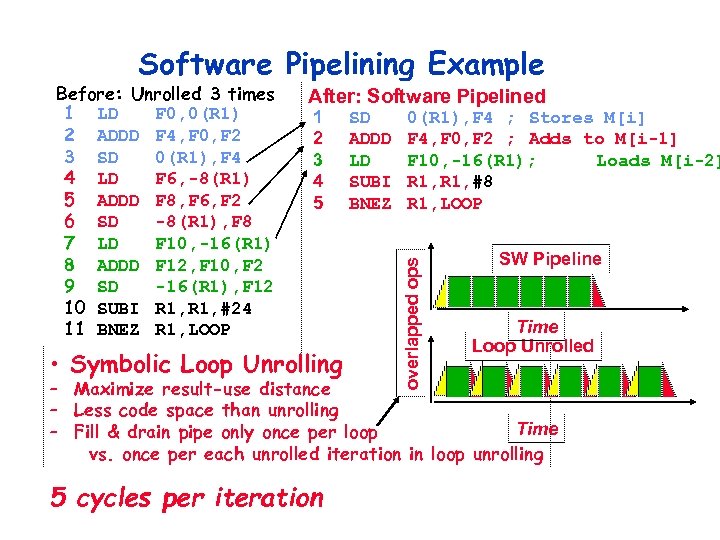

Software Pipelining Example After: Software Pipelined 1 2 3 4 5 • Symbolic Loop Unrolling SD ADDD LD SUBI BNEZ 0(R 1), F 4 ; Stores M[i] F 4, F 0, F 2 ; Adds to M[i-1] F 10, -16(R 1); Loads M[i-2] R 1, #8 R 1, LOOP overlapped ops Before: Unrolled 3 times 1 LD F 0, 0(R 1) 2 ADDD F 4, F 0, F 2 3 SD 0(R 1), F 4 4 LD F 6, -8(R 1) 5 ADDD F 8, F 6, F 2 6 SD -8(R 1), F 8 7 LD F 10, -16(R 1) 8 ADDD F 12, F 10, F 2 9 SD -16(R 1), F 12 10 SUBI R 1, #24 11 BNEZ R 1, LOOP SW Pipeline Time Loop Unrolled – Maximize result-use distance – Less code space than unrolling Time – Fill & drain pipe only once per loop vs. once per each unrolled iteration in loop unrolling 5 cycles per iteration

Software Pipelining Example After: Software Pipelined 1 2 3 4 5 • Symbolic Loop Unrolling SD ADDD LD SUBI BNEZ 0(R 1), F 4 ; Stores M[i] F 4, F 0, F 2 ; Adds to M[i-1] F 10, -16(R 1); Loads M[i-2] R 1, #8 R 1, LOOP overlapped ops Before: Unrolled 3 times 1 LD F 0, 0(R 1) 2 ADDD F 4, F 0, F 2 3 SD 0(R 1), F 4 4 LD F 6, -8(R 1) 5 ADDD F 8, F 6, F 2 6 SD -8(R 1), F 8 7 LD F 10, -16(R 1) 8 ADDD F 12, F 10, F 2 9 SD -16(R 1), F 12 10 SUBI R 1, #24 11 BNEZ R 1, LOOP SW Pipeline Time Loop Unrolled – Maximize result-use distance – Less code space than unrolling Time – Fill & drain pipe only once per loop vs. once per each unrolled iteration in loop unrolling 5 cycles per iteration

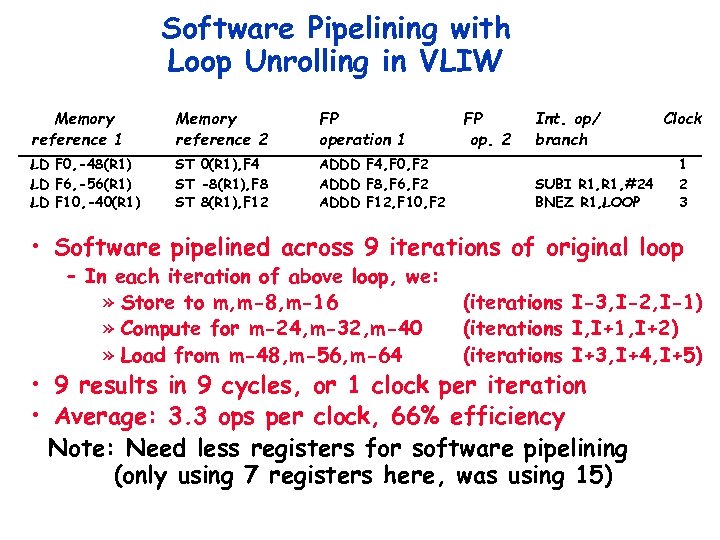

Software Pipelining with Loop Unrolling in VLIW Memory reference 1 Memory reference 2 FP operation 1 LD F 0, -48(R 1) LD F 6, -56(R 1) LD F 10, -40(R 1) ST 0(R 1), F 4 ST -8(R 1), F 8 ST 8(R 1), F 12 ADDD F 4, F 0, F 2 ADDD F 8, F 6, F 2 ADDD F 12, F 10, F 2 FP op. 2 Int. op/ branch SUBI R 1, #24 BNEZ R 1, LOOP Clock 1 2 3 • Software pipelined across 9 iterations of original loop – In each iteration of above loop, we: » Store to m, m-8, m-16 » Compute for m-24, m-32, m-40 » Load from m-48, m-56, m-64 (iterations I-3, I-2, I-1) (iterations I, I+1, I+2) (iterations I+3, I+4, I+5) • 9 results in 9 cycles, or 1 clock per iteration • Average: 3. 3 ops per clock, 66% efficiency Note: Need less registers for software pipelining (only using 7 registers here, was using 15)

Software Pipelining with Loop Unrolling in VLIW Memory reference 1 Memory reference 2 FP operation 1 LD F 0, -48(R 1) LD F 6, -56(R 1) LD F 10, -40(R 1) ST 0(R 1), F 4 ST -8(R 1), F 8 ST 8(R 1), F 12 ADDD F 4, F 0, F 2 ADDD F 8, F 6, F 2 ADDD F 12, F 10, F 2 FP op. 2 Int. op/ branch SUBI R 1, #24 BNEZ R 1, LOOP Clock 1 2 3 • Software pipelined across 9 iterations of original loop – In each iteration of above loop, we: » Store to m, m-8, m-16 » Compute for m-24, m-32, m-40 » Load from m-48, m-56, m-64 (iterations I-3, I-2, I-1) (iterations I, I+1, I+2) (iterations I+3, I+4, I+5) • 9 results in 9 cycles, or 1 clock per iteration • Average: 3. 3 ops per clock, 66% efficiency Note: Need less registers for software pipelining (only using 7 registers here, was using 15)

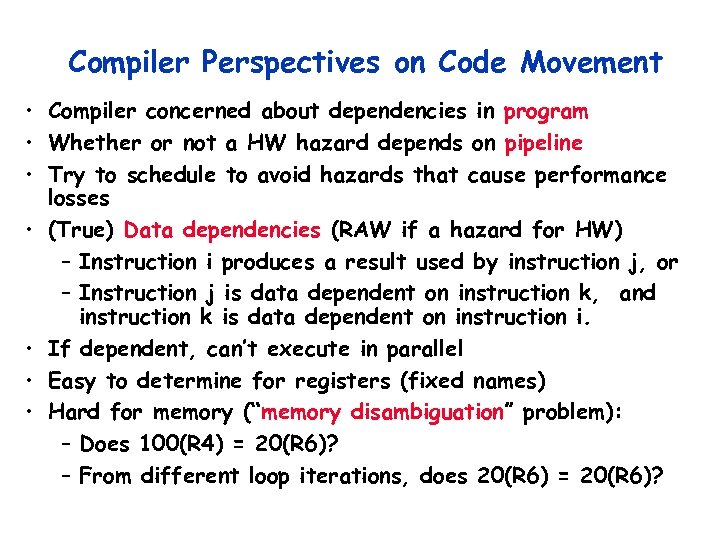

Compiler Perspectives on Code Movement • Compiler concerned about dependencies in program • Whether or not a HW hazard depends on pipeline • Try to schedule to avoid hazards that cause performance losses • (True) Data dependencies (RAW if a hazard for HW) – Instruction i produces a result used by instruction j, or – Instruction j is data dependent on instruction k, and instruction k is data dependent on instruction i. • If dependent, can’t execute in parallel • Easy to determine for registers (fixed names) • Hard for memory (“memory disambiguation” problem): – Does 100(R 4) = 20(R 6)? – From different loop iterations, does 20(R 6) = 20(R 6)?

Compiler Perspectives on Code Movement • Compiler concerned about dependencies in program • Whether or not a HW hazard depends on pipeline • Try to schedule to avoid hazards that cause performance losses • (True) Data dependencies (RAW if a hazard for HW) – Instruction i produces a result used by instruction j, or – Instruction j is data dependent on instruction k, and instruction k is data dependent on instruction i. • If dependent, can’t execute in parallel • Easy to determine for registers (fixed names) • Hard for memory (“memory disambiguation” problem): – Does 100(R 4) = 20(R 6)? – From different loop iterations, does 20(R 6) = 20(R 6)?

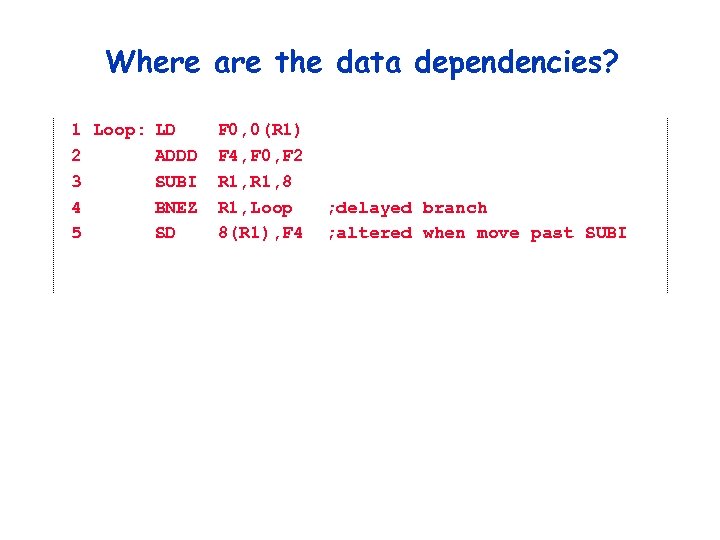

Where are the data dependencies? 1 Loop: LD 2 ADDD 3 SUBI 4 BNEZ 5 SD F 0, 0(R 1) F 4, F 0, F 2 R 1, 8 R 1, Loop 8(R 1), F 4 ; delayed branch ; altered when move past SUBI

Where are the data dependencies? 1 Loop: LD 2 ADDD 3 SUBI 4 BNEZ 5 SD F 0, 0(R 1) F 4, F 0, F 2 R 1, 8 R 1, Loop 8(R 1), F 4 ; delayed branch ; altered when move past SUBI

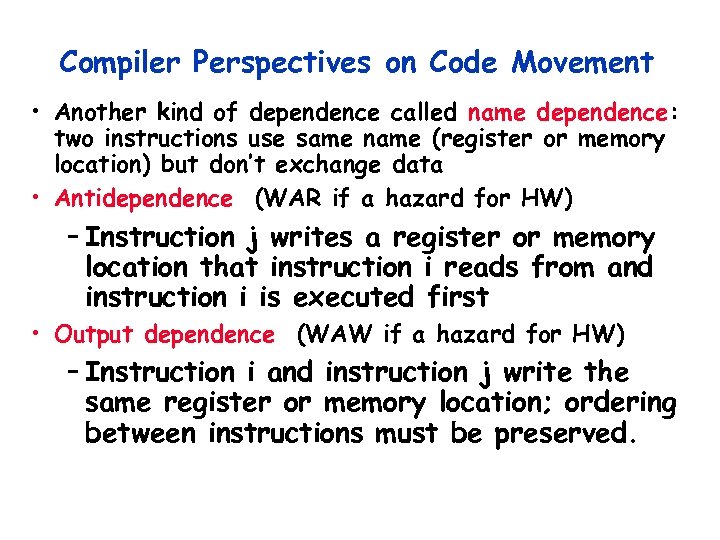

Compiler Perspectives on Code Movement • Another kind of dependence called name dependence: two instructions use same name (register or memory location) but don’t exchange data • Antidependence (WAR if a hazard for HW) – Instruction j writes a register or memory location that instruction i reads from and instruction i is executed first • Output dependence (WAW if a hazard for HW) – Instruction i and instruction j write the same register or memory location; ordering between instructions must be preserved.

Compiler Perspectives on Code Movement • Another kind of dependence called name dependence: two instructions use same name (register or memory location) but don’t exchange data • Antidependence (WAR if a hazard for HW) – Instruction j writes a register or memory location that instruction i reads from and instruction i is executed first • Output dependence (WAW if a hazard for HW) – Instruction i and instruction j write the same register or memory location; ordering between instructions must be preserved.

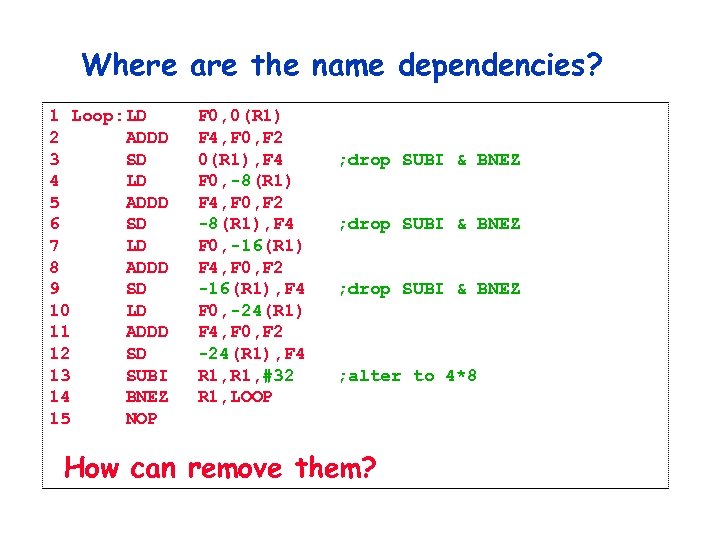

Where are the name dependencies? 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 0, -8(R 1) F 4, F 0, F 2 -8(R 1), F 4 F 0, -16(R 1) F 4, F 0, F 2 -16(R 1), F 4 F 0, -24(R 1) F 4, F 0, F 2 -24(R 1), F 4 R 1, #32 R 1, LOOP ; drop SUBI & BNEZ ; alter to 4*8 How can remove them?

Where are the name dependencies? 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 0, -8(R 1) F 4, F 0, F 2 -8(R 1), F 4 F 0, -16(R 1) F 4, F 0, F 2 -16(R 1), F 4 F 0, -24(R 1) F 4, F 0, F 2 -24(R 1), F 4 R 1, #32 R 1, LOOP ; drop SUBI & BNEZ ; alter to 4*8 How can remove them?

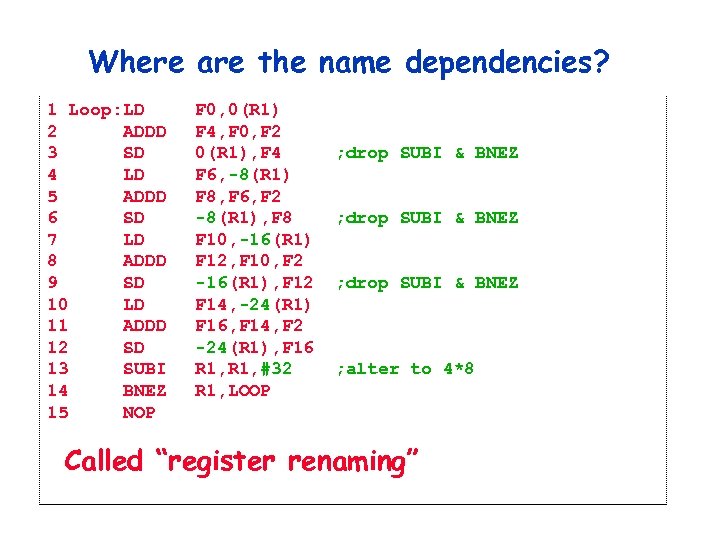

Where are the name dependencies? 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 6, -8(R 1) F 8, F 6, F 2 -8(R 1), F 8 F 10, -16(R 1) F 12, F 10, F 2 -16(R 1), F 12 F 14, -24(R 1) F 16, F 14, F 2 -24(R 1), F 16 R 1, #32 R 1, LOOP ; drop SUBI & BNEZ ; alter to 4*8 Called “register renaming”

Where are the name dependencies? 1 Loop: LD 2 ADDD 3 SD 4 LD 5 ADDD 6 SD 7 LD 8 ADDD 9 SD 10 LD 11 ADDD 12 SD 13 SUBI 14 BNEZ 15 NOP F 0, 0(R 1) F 4, F 0, F 2 0(R 1), F 4 F 6, -8(R 1) F 8, F 6, F 2 -8(R 1), F 8 F 10, -16(R 1) F 12, F 10, F 2 -16(R 1), F 12 F 14, -24(R 1) F 16, F 14, F 2 -24(R 1), F 16 R 1, #32 R 1, LOOP ; drop SUBI & BNEZ ; alter to 4*8 Called “register renaming”

Compiler Perspectives on Code Movement • Name Dependencies are Hard to discover for Memory Accesses – Does 100(R 4) = 20(R 6)? – From different loop iterations, does 20(R 6) = 20(R 6)? • Our example required compiler to know that if R 1 doesn’t change then: 0(R 1) -8(R 1) -16(R 1) -24(R 1) There were no dependencies between some loads and stores so they could be moved by each other

Compiler Perspectives on Code Movement • Name Dependencies are Hard to discover for Memory Accesses – Does 100(R 4) = 20(R 6)? – From different loop iterations, does 20(R 6) = 20(R 6)? • Our example required compiler to know that if R 1 doesn’t change then: 0(R 1) -8(R 1) -16(R 1) -24(R 1) There were no dependencies between some loads and stores so they could be moved by each other

Compiler Perspectives on Code Movement • Final kind of dependence called control dependence. Example: if p 1 {S 1; }; if p 2 {S 2; }; S 1 is control dependent on p 1 and S 2 is control dependent on p 2 but not on p 1. • Two (obvious? ) constraints on control dependences: – An instruction that is control dependent on a branch cannot be moved before the branch. – An instruction that is not control dependent on a branch cannot be moved to after the branch • Control dependencies relaxed to get parallelism: – Can occasionally move dependent loads before branch to get early start on cache miss – get same effect if preserve order of exceptions (address in register checked by branch before use) and data flow (value in register depends on branch)

Compiler Perspectives on Code Movement • Final kind of dependence called control dependence. Example: if p 1 {S 1; }; if p 2 {S 2; }; S 1 is control dependent on p 1 and S 2 is control dependent on p 2 but not on p 1. • Two (obvious? ) constraints on control dependences: – An instruction that is control dependent on a branch cannot be moved before the branch. – An instruction that is not control dependent on a branch cannot be moved to after the branch • Control dependencies relaxed to get parallelism: – Can occasionally move dependent loads before branch to get early start on cache miss – get same effect if preserve order of exceptions (address in register checked by branch before use) and data flow (value in register depends on branch)