5d701d840744af3dfa30944a8c2464f0.ppt

- Количество слайдов: 34

EE 382 V Spring 2015 VLSI Physical Design Automation Lecture 1. Introduction Prof. David Z. Pan dpan@ece. utexas. edu Office: POB 5. 434 3/18/2018 1

EE 382 V Spring 2015 VLSI Physical Design Automation Lecture 1. Introduction Prof. David Z. Pan dpan@ece. utexas. edu Office: POB 5. 434 3/18/2018 1

What is this course for? 1. Understandable to everyone 2. Understandable to intended audience 3. Understandable to experts only, such as the speaker 4. Understandable to nobody, including the speaker 3/18/2018 2

What is this course for? 1. Understandable to everyone 2. Understandable to intended audience 3. Understandable to experts only, such as the speaker 4. Understandable to nobody, including the speaker 3/18/2018 2

Intended Audience • VLSI CAD (also known as EDA – electronic design automation) students, in particular for chip implementation (physical design) • Circuit designers to understand how tools work behind the scene • Process engineers to tune process that is more circuit/physical design friendly • Mathematical/Computer Science majors who want to find tough problems to solve – Lots of VLSI physical design problems can be formulated into combinatorial optimization problems – Actually, most CAD problems are NP-complete -> heuristics 3/18/2018 3

Intended Audience • VLSI CAD (also known as EDA – electronic design automation) students, in particular for chip implementation (physical design) • Circuit designers to understand how tools work behind the scene • Process engineers to tune process that is more circuit/physical design friendly • Mathematical/Computer Science majors who want to find tough problems to solve – Lots of VLSI physical design problems can be formulated into combinatorial optimization problems – Actually, most CAD problems are NP-complete -> heuristics 3/18/2018 3

Course Objectives a Obtain a general understanding of IC designs. a Understand the process of VLSI layout design a Study the basic algorithms used in layout design of VLSI circuits. a Learn about the physical design automation techniques used in the best-known academic and commercial layout systems. a Get know recent research topics and problems. 3/18/2018 4

Course Objectives a Obtain a general understanding of IC designs. a Understand the process of VLSI layout design a Study the basic algorithms used in layout design of VLSI circuits. a Learn about the physical design automation techniques used in the best-known academic and commercial layout systems. a Get know recent research topics and problems. 3/18/2018 4

Course Logistics • Lecture Hours: MW 9: 00 -10: 30 am; Location: SZB 380 • Instructor: David Pan – Email: dpan@ece. utexas. edu (best way to reach me) – Office: POB 5. 434 – OH: MW 1: 30 -2: 30 pm & by appointment. • TA: Subhendu Roy, OH on T/Th 2 -4 pm • Class web page – http: //www. ece. utexas. edu/~dpan/EE 382 V_PDA • Prerequisites – Basic understand of algorithms (EE 360 C) – Basic understand of VLSI (EE 460 R) – or consent of instructor 3/18/2018 5

Course Logistics • Lecture Hours: MW 9: 00 -10: 30 am; Location: SZB 380 • Instructor: David Pan – Email: dpan@ece. utexas. edu (best way to reach me) – Office: POB 5. 434 – OH: MW 1: 30 -2: 30 pm & by appointment. • TA: Subhendu Roy, OH on T/Th 2 -4 pm • Class web page – http: //www. ece. utexas. edu/~dpan/EE 382 V_PDA • Prerequisites – Basic understand of algorithms (EE 360 C) – Basic understand of VLSI (EE 460 R) – or consent of instructor 3/18/2018 5

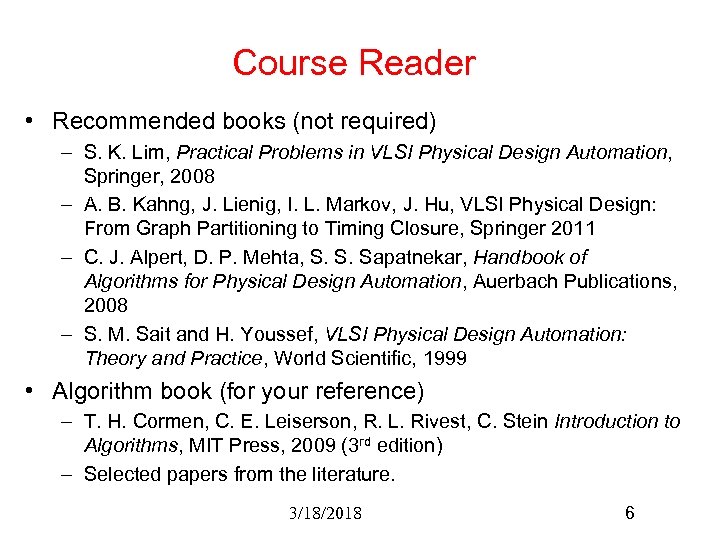

Course Reader • Recommended books (not required) – S. K. Lim, Practical Problems in VLSI Physical Design Automation, Springer, 2008 – A. B. Kahng, J. Lienig, I. L. Markov, J. Hu, VLSI Physical Design: From Graph Partitioning to Timing Closure, Springer 2011 – C. J. Alpert, D. P. Mehta, S. S. Sapatnekar, Handbook of Algorithms for Physical Design Automation, Auerbach Publications, 2008 – S. M. Sait and H. Youssef, VLSI Physical Design Automation: Theory and Practice, World Scientific, 1999 • Algorithm book (for your reference) – T. H. Cormen, C. E. Leiserson, R. L. Rivest, C. Stein Introduction to Algorithms, MIT Press, 2009 (3 rd edition) – Selected papers from the literature. 3/18/2018 6

Course Reader • Recommended books (not required) – S. K. Lim, Practical Problems in VLSI Physical Design Automation, Springer, 2008 – A. B. Kahng, J. Lienig, I. L. Markov, J. Hu, VLSI Physical Design: From Graph Partitioning to Timing Closure, Springer 2011 – C. J. Alpert, D. P. Mehta, S. S. Sapatnekar, Handbook of Algorithms for Physical Design Automation, Auerbach Publications, 2008 – S. M. Sait and H. Youssef, VLSI Physical Design Automation: Theory and Practice, World Scientific, 1999 • Algorithm book (for your reference) – T. H. Cormen, C. E. Leiserson, R. L. Rivest, C. Stein Introduction to Algorithms, MIT Press, 2009 (3 rd edition) – Selected papers from the literature. 3/18/2018 6

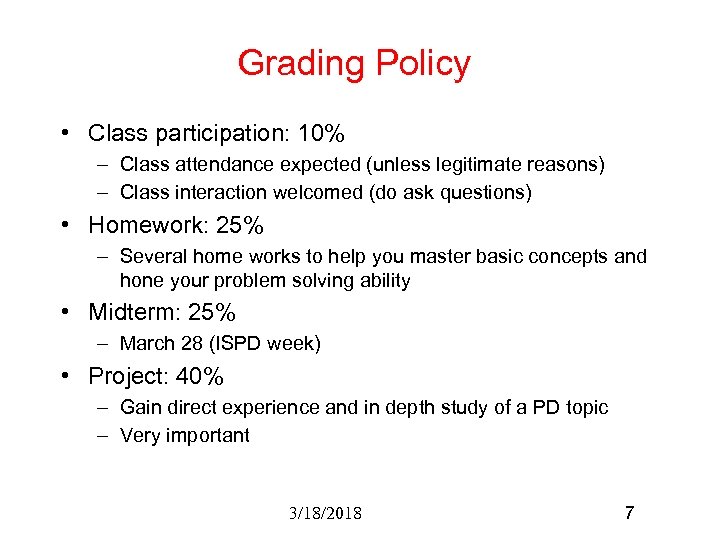

Grading Policy • Class participation: 10% – Class attendance expected (unless legitimate reasons) – Class interaction welcomed (do ask questions) • Homework: 25% – Several home works to help you master basic concepts and hone your problem solving ability • Midterm: 25% – March 28 (ISPD week) • Project: 40% – Gain direct experience and in depth study of a PD topic – Very important 3/18/2018 7

Grading Policy • Class participation: 10% – Class attendance expected (unless legitimate reasons) – Class interaction welcomed (do ask questions) • Homework: 25% – Several home works to help you master basic concepts and hone your problem solving ability • Midterm: 25% – March 28 (ISPD week) • Project: 40% – Gain direct experience and in depth study of a PD topic – Very important 3/18/2018 7

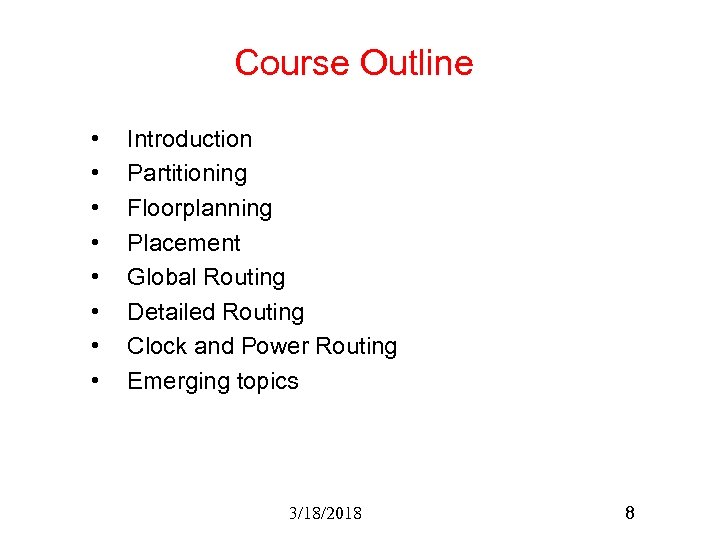

Course Outline • • Introduction Partitioning Floorplanning Placement Global Routing Detailed Routing Clock and Power Routing Emerging topics 3/18/2018 8

Course Outline • • Introduction Partitioning Floorplanning Placement Global Routing Detailed Routing Clock and Power Routing Emerging topics 3/18/2018 8

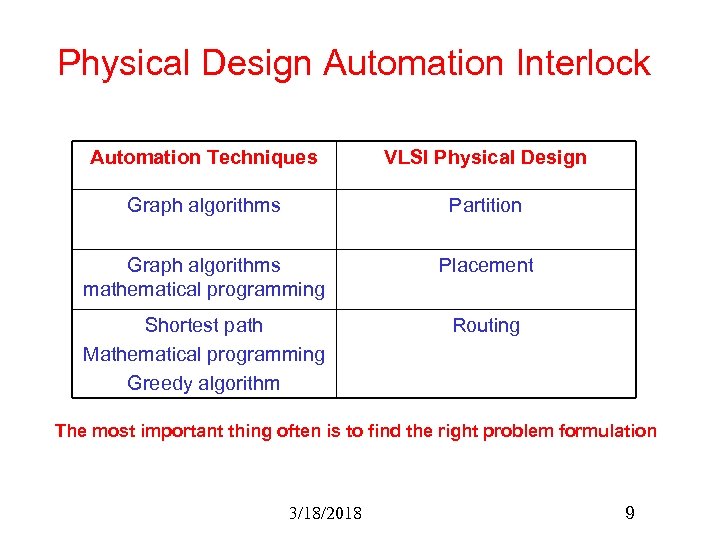

Physical Design Automation Interlock Automation Techniques VLSI Physical Design Graph algorithms Partition Graph algorithms mathematical programming Placement Shortest path Mathematical programming Greedy algorithm Routing The most important thing often is to find the right problem formulation 3/18/2018 9

Physical Design Automation Interlock Automation Techniques VLSI Physical Design Graph algorithms Partition Graph algorithms mathematical programming Placement Shortest path Mathematical programming Greedy algorithm Routing The most important thing often is to find the right problem formulation 3/18/2018 9

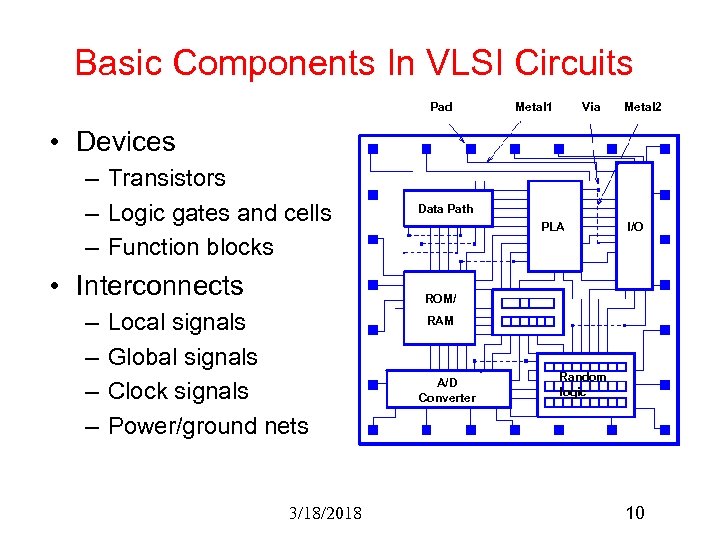

Basic Components In VLSI Circuits Pad Metal 1 Via Metal 2 • Devices – Transistors – Logic gates and cells – Function blocks • Interconnects – – Data Path PLA I/O ROM/ Local signals Global signals Clock signals Power/ground nets 3/18/2018 RAM A/D Converter Random logic 10

Basic Components In VLSI Circuits Pad Metal 1 Via Metal 2 • Devices – Transistors – Logic gates and cells – Function blocks • Interconnects – – Data Path PLA I/O ROM/ Local signals Global signals Clock signals Power/ground nets 3/18/2018 RAM A/D Converter Random logic 10

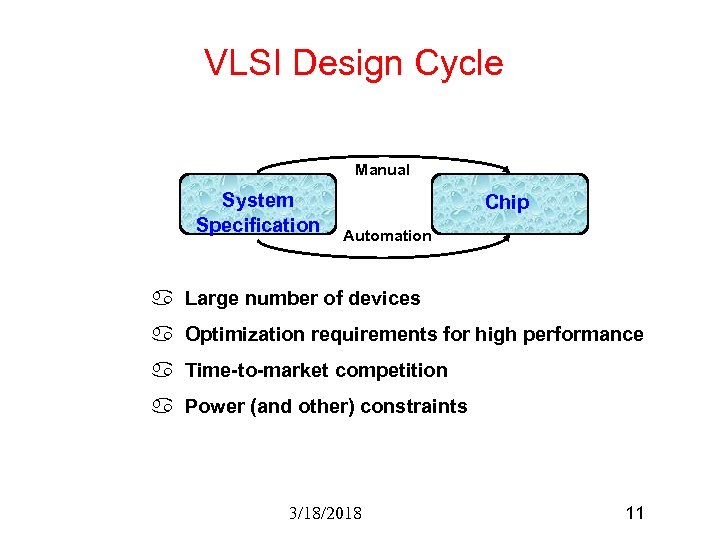

VLSI Design Cycle Manual System Specification Chip Automation a Large number of devices a Optimization requirements for high performance a Time-to-market competition a Power (and other) constraints 3/18/2018 11

VLSI Design Cycle Manual System Specification Chip Automation a Large number of devices a Optimization requirements for high performance a Time-to-market competition a Power (and other) constraints 3/18/2018 11

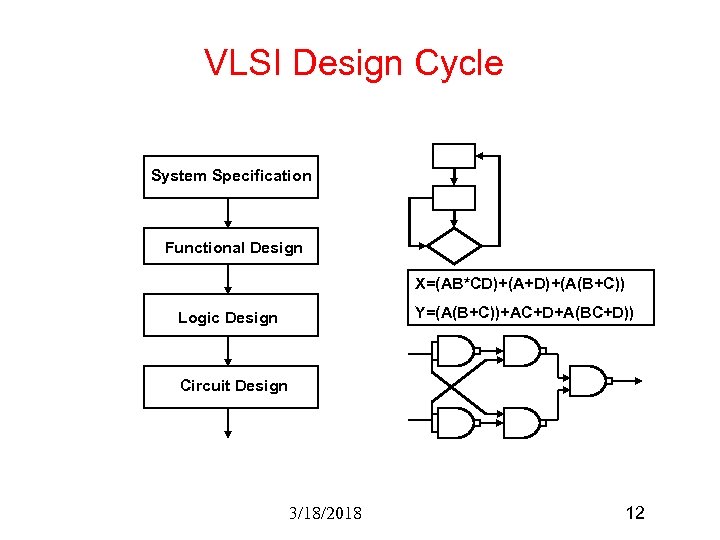

VLSI Design Cycle System Specification Functional Design X=(AB*CD)+(A+D)+(A(B+C)) Y=(A(B+C))+AC+D+A(BC+D)) Logic Design Circuit Design 3/18/2018 12

VLSI Design Cycle System Specification Functional Design X=(AB*CD)+(A+D)+(A(B+C)) Y=(A(B+C))+AC+D+A(BC+D)) Logic Design Circuit Design 3/18/2018 12

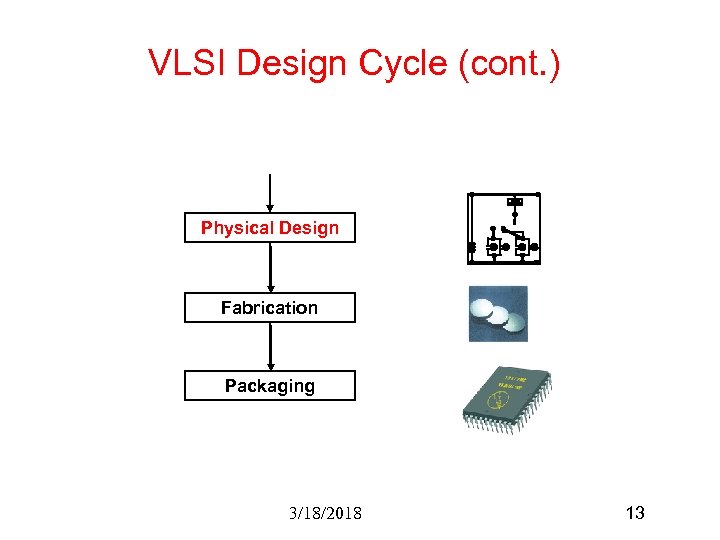

VLSI Design Cycle (cont. ) Physical Design Fabrication Packaging 3/18/2018 13

VLSI Design Cycle (cont. ) Physical Design Fabrication Packaging 3/18/2018 13

Physical Design Physical design converts a circuit description into a geometric description. This description is used to manufacture a chip. Conventional physical design cycle consists of 1 Partitioning 2 Floorplanning 3 Placement 4 Routing 5 Compaction 3/18/2018 14

Physical Design Physical design converts a circuit description into a geometric description. This description is used to manufacture a chip. Conventional physical design cycle consists of 1 Partitioning 2 Floorplanning 3 Placement 4 Routing 5 Compaction 3/18/2018 14

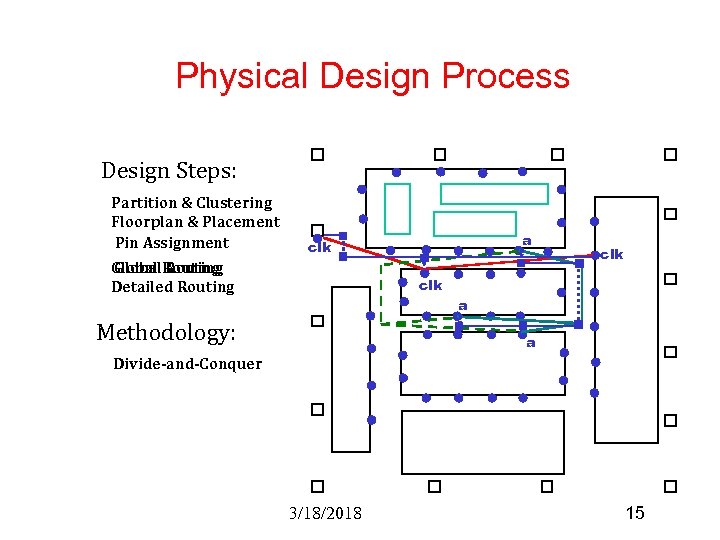

Physical Design Process Design Steps: Partition & Clustering Floorplan & Placement Pin Assignment a clk Global Routing Detailed Routing clk a Methodology: a Divide-and-Conquer 3/18/2018 15

Physical Design Process Design Steps: Partition & Clustering Floorplan & Placement Pin Assignment a clk Global Routing Detailed Routing clk a Methodology: a Divide-and-Conquer 3/18/2018 15

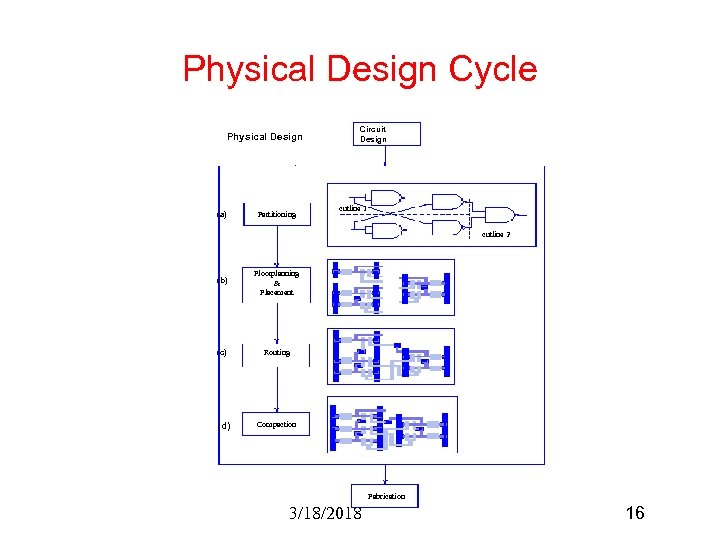

Physical Design Cycle Physical Design (a) Partitioning Circuit Design cutline 1 cutline 2 (b) Floorplanning & Placement (c) Routing (d) Compaction Fabrication 3/18/2018 16

Physical Design Cycle Physical Design (a) Partitioning Circuit Design cutline 1 cutline 2 (b) Floorplanning & Placement (c) Routing (d) Compaction Fabrication 3/18/2018 16

Complexities of Physical Design a More than 100 million transistors a Performance driven designs a Power-constrained designs a Time-to-Market Design cycle …. . . High performance, high cost 3/18/2018 17

Complexities of Physical Design a More than 100 million transistors a Performance driven designs a Power-constrained designs a Time-to-Market Design cycle …. . . High performance, high cost 3/18/2018 17

History 101 of Physical Design • • • Born in early 60’s (board layout) Passed teenage in 70’s (standard cell place and route) Entered early adulthood in 80’s (over-the-cell routing) Declared dead in late 80’s !!! Found alive and kicking in 90’s Physical Design (PD) has become a dominant force in the overall design cycle – Due to the deep submicron scaling – Expand vertically with logic synthesis and interconnect optimization, analysis…. => Design closure! – IC “Implementation” tool is about 1/3 of the overall EDA market 3/18/2018 18

History 101 of Physical Design • • • Born in early 60’s (board layout) Passed teenage in 70’s (standard cell place and route) Entered early adulthood in 80’s (over-the-cell routing) Declared dead in late 80’s !!! Found alive and kicking in 90’s Physical Design (PD) has become a dominant force in the overall design cycle – Due to the deep submicron scaling – Expand vertically with logic synthesis and interconnect optimization, analysis…. => Design closure! – IC “Implementation” tool is about 1/3 of the overall EDA market 3/18/2018 18

Why Physical Design still Relevant? • Many existing solutions are still very suboptimal – E. g. , placement • Interconnect dominates – No physical layout, no accurate interconnect • More new physical and manufacturing effects pop up – Crosstalk noise, … – Manufacturability, reliability, … • More vertical integration needed • Physical design is the KEY linking step between higher level optimization and lower level modeling 3/18/2018 19

Why Physical Design still Relevant? • Many existing solutions are still very suboptimal – E. g. , placement • Interconnect dominates – No physical layout, no accurate interconnect • More new physical and manufacturing effects pop up – Crosstalk noise, … – Manufacturability, reliability, … • More vertical integration needed • Physical design is the KEY linking step between higher level optimization and lower level modeling 3/18/2018 19

PD Courses in Context • This course is on core physical design (that covers every major step in details) • More basics • Different from my other graduate course “Optimization Issues of VLSI CAD” • More crosscutting topics, such as DFM, interconnect, low power, reliability … 3/18/2018 20

PD Courses in Context • This course is on core physical design (that covers every major step in details) • More basics • Different from my other graduate course “Optimization Issues of VLSI CAD” • More crosscutting topics, such as DFM, interconnect, low power, reliability … 3/18/2018 20

Moore’s Law • The minimum transistor feature size decreases by 0. 7 X every three years (Electronics Magazine, Vol. 38, April 1965) • Consequences of smaller transistors: – Faster transistor switching – More transistors per chip • True for almost 50 years! • This year is Moore’s Law’s 50 th anniversary! • More Moore, but facing lots of red brick walls – Need smarter and more powerful CAD tools than ever 3/18/2018 21

Moore’s Law • The minimum transistor feature size decreases by 0. 7 X every three years (Electronics Magazine, Vol. 38, April 1965) • Consequences of smaller transistors: – Faster transistor switching – More transistors per chip • True for almost 50 years! • This year is Moore’s Law’s 50 th anniversary! • More Moore, but facing lots of red brick walls – Need smarter and more powerful CAD tools than ever 3/18/2018 21

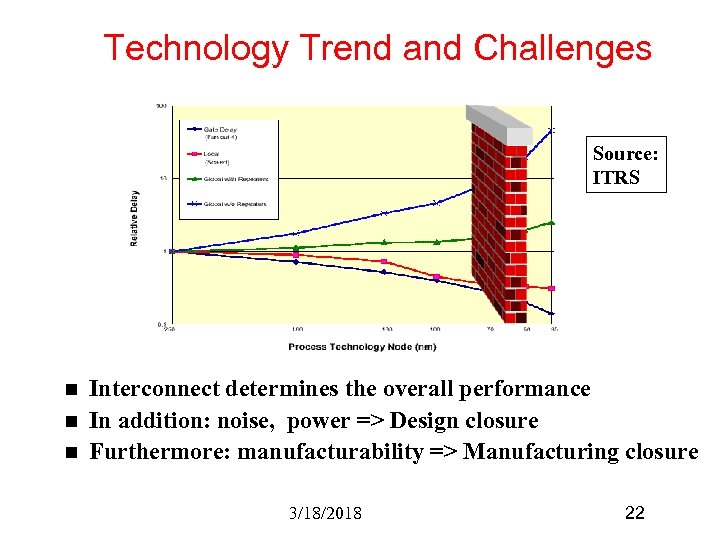

Technology Trend and Challenges Source: ITRS n n n Interconnect determines the overall performance In addition: noise, power => Design closure Furthermore: manufacturability => Manufacturing closure 3/18/2018 22

Technology Trend and Challenges Source: ITRS n n n Interconnect determines the overall performance In addition: noise, power => Design closure Furthermore: manufacturability => Manufacturing closure 3/18/2018 22

Placement Challenge • Placement, to large extend, determines the overall interconnect • If it sucks, no matter how well you interconnect optimization engine works, the design will suck • Placement is a very old problem, but still have lots of room for improvement – Mixed-size (large macro blocks and small standard cells) – Optimality study shows that placement still a bottleneck – Not even to mention performance driven, and coupled with buffering, interconnect optimizations, and so on 3/18/2018 23

Placement Challenge • Placement, to large extend, determines the overall interconnect • If it sucks, no matter how well you interconnect optimization engine works, the design will suck • Placement is a very old problem, but still have lots of room for improvement – Mixed-size (large macro blocks and small standard cells) – Optimality study shows that placement still a bottleneck – Not even to mention performance driven, and coupled with buffering, interconnect optimizations, and so on 3/18/2018 23

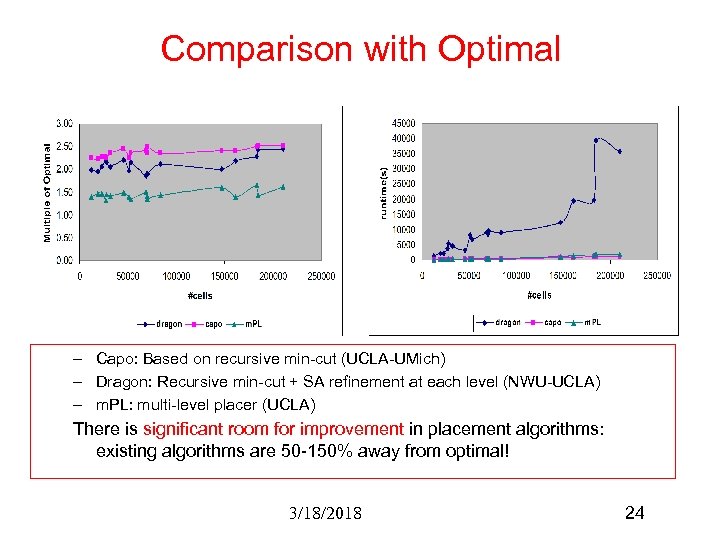

Comparison with Optimal – Capo: Based on recursive min-cut (UCLA-UMich) – Dragon: Recursive min-cut + SA refinement at each level (NWU-UCLA) – m. PL: multi-level placer (UCLA) There is significant room for improvement in placement algorithms: existing algorithms are 50 -150% away from optimal! 3/18/2018 24

Comparison with Optimal – Capo: Based on recursive min-cut (UCLA-UMich) – Dragon: Recursive min-cut + SA refinement at each level (NWU-UCLA) – m. PL: multi-level placer (UCLA) There is significant room for improvement in placement algorithms: existing algorithms are 50 -150% away from optimal! 3/18/2018 24

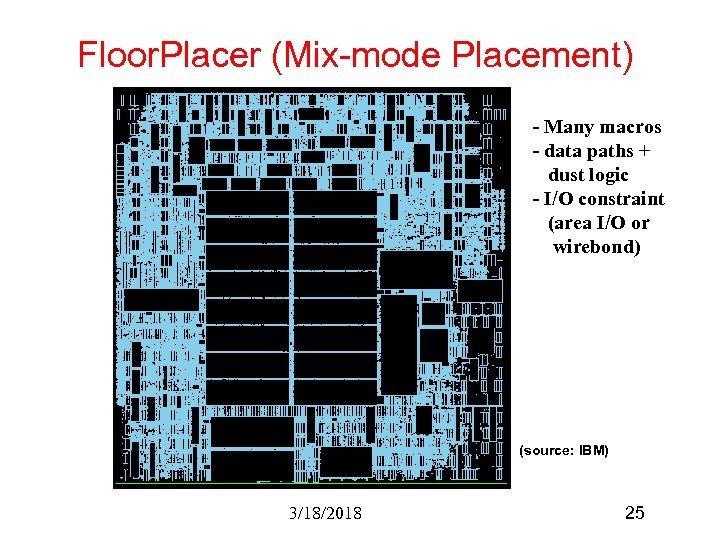

Floor. Placer (Mix-mode Placement) - Many macros - data paths + dust logic - I/O constraint (area I/O or wirebond) (source: IBM) 3/18/2018 25

Floor. Placer (Mix-mode Placement) - Many macros - data paths + dust logic - I/O constraint (area I/O or wirebond) (source: IBM) 3/18/2018 25

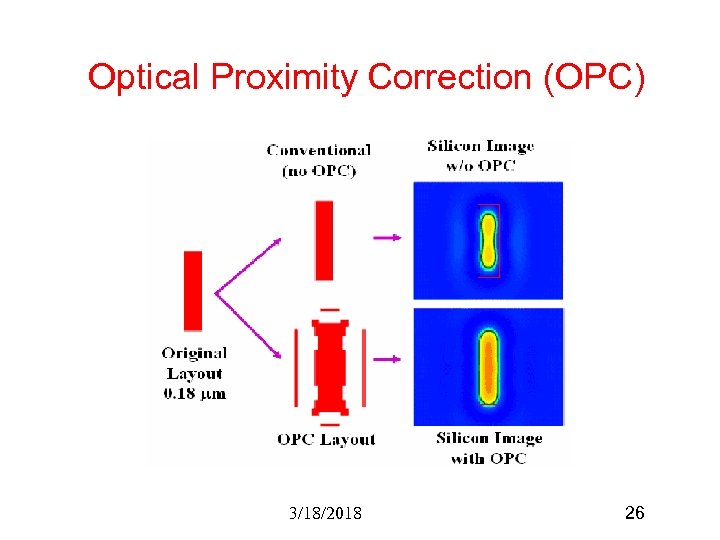

Optical Proximity Correction (OPC) 3/18/2018 26

Optical Proximity Correction (OPC) 3/18/2018 26

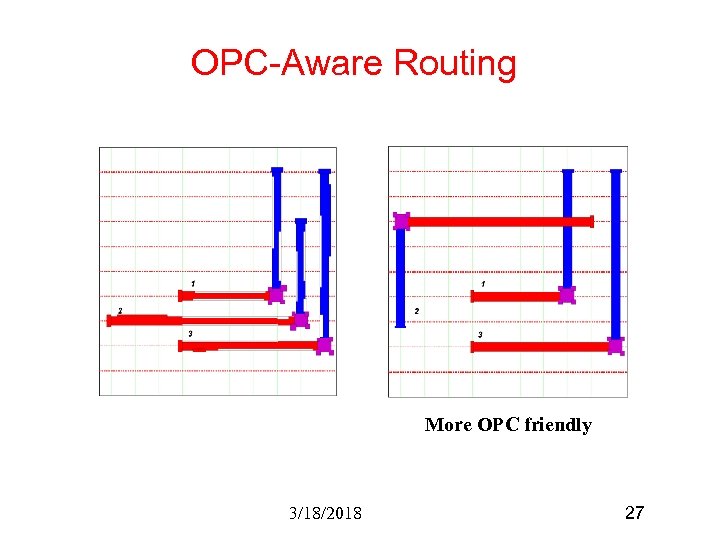

OPC-Aware Routing More OPC friendly 3/18/2018 27

OPC-Aware Routing More OPC friendly 3/18/2018 27

Class Project • Three types – Literature survey (one person): at most 80% out of 40% for the total project grade – Implementation/comparison of existing PD algorithms (typically 2 -person team) – Explore new ideas (typically 2 -person team) • Project and term paper outline – – – Introduction and motivation Problem statement and/or formulation Previous works (exhaustive search) Your approach (new ideas) Experimental results (implement your idea and show it works or explain why if it does not) – Summary, conclusion and future work 3/18/2018 28

Class Project • Three types – Literature survey (one person): at most 80% out of 40% for the total project grade – Implementation/comparison of existing PD algorithms (typically 2 -person team) – Explore new ideas (typically 2 -person team) • Project and term paper outline – – – Introduction and motivation Problem statement and/or formulation Previous works (exhaustive search) Your approach (new ideas) Experimental results (implement your idea and show it works or explain why if it does not) – Summary, conclusion and future work 3/18/2018 28

Class Project • Rough milestones for class project – Proposal by Feb. 18: • Project team and initial proposal on what topic to work on – First report by Mar. 11 (before spring break): • Project proposal with initial literature review • And your ideas, plan of attack, and framework – Second report by April 15 • Comprehensive literature review • Initial implementation results or findings – Final project report and presentation • TBD, around the final week – Conference submission deadlines in Spring 2015 • ICCAD deadline (abstract: April 17; full paper: April 24) • ASPDAC deadline (around early July) 3/18/2018 29

Class Project • Rough milestones for class project – Proposal by Feb. 18: • Project team and initial proposal on what topic to work on – First report by Mar. 11 (before spring break): • Project proposal with initial literature review • And your ideas, plan of attack, and framework – Second report by April 15 • Comprehensive literature review • Initial implementation results or findings – Final project report and presentation • TBD, around the final week – Conference submission deadlines in Spring 2015 • ICCAD deadline (abstract: April 17; full paper: April 24) • ASPDAC deadline (around early July) 3/18/2018 29

Class Project • Possible topics – ISPD 2015 Contest topics: www. ispd. cc – ICCAD 2014 Contest topics: www. iccad. com – Suggest your own research topics • We will talk more later 3/18/2018 30

Class Project • Possible topics – ISPD 2015 Contest topics: www. ispd. cc – ICCAD 2014 Contest topics: www. iccad. com – Suggest your own research topics • We will talk more later 3/18/2018 30

Some Previous Class Projects • A. Rajaram, D. Z. Pan and J. Hu, "Improved Algorithms for Link Based Non-tree Clock Network for Skew Variability Reduction", Proc. International Symposium on Physical Design (ISPD), San Francisco, CA, April 2005. • M. Cho, S. Ahmed and D. Z. Pan, "TACO: Temperature Aware Clock Optimization", Proc. ACM/IEEE Int'l Conference on Computer-Aided Design (ICCAD), November, 2005 (covered by EE Times on June 19, 2006) • Avijit Dutta, Jinkyu Lee and David Z. Pan, “Partial Functional Manipulation Based Wirelength Minimization”, Proc. International Conference on Computer Design (ICCD), Oct. 2006 • Samuel I. Ward et. al. , "Keep it Straight: Teaching Placement how to Better Handle Designs with Datapaths", Proc. ACM International Symposium on Physical Design (ISPD), Napa Valley, CA, March, 2012 (Nominated for Best Paper Award) 3/18/2018 31

Some Previous Class Projects • A. Rajaram, D. Z. Pan and J. Hu, "Improved Algorithms for Link Based Non-tree Clock Network for Skew Variability Reduction", Proc. International Symposium on Physical Design (ISPD), San Francisco, CA, April 2005. • M. Cho, S. Ahmed and D. Z. Pan, "TACO: Temperature Aware Clock Optimization", Proc. ACM/IEEE Int'l Conference on Computer-Aided Design (ICCAD), November, 2005 (covered by EE Times on June 19, 2006) • Avijit Dutta, Jinkyu Lee and David Z. Pan, “Partial Functional Manipulation Based Wirelength Minimization”, Proc. International Conference on Computer Design (ICCD), Oct. 2006 • Samuel I. Ward et. al. , "Keep it Straight: Teaching Placement how to Better Handle Designs with Datapaths", Proc. ACM International Symposium on Physical Design (ISPD), Napa Valley, CA, March, 2012 (Nominated for Best Paper Award) 3/18/2018 31

Resources • Please check the web site for a set of references, papers and links (will be updated frequently) – – – EE Times (www. eetimes. com) for recent trend/development IEEE Explorer ACM Digital Library Google Scholar …… • MOOC! – If you need to make up some knowledge (e. g. , Cormen’s algorithm book/class) 3/18/2018 32

Resources • Please check the web site for a set of references, papers and links (will be updated frequently) – – – EE Times (www. eetimes. com) for recent trend/development IEEE Explorer ACM Digital Library Google Scholar …… • MOOC! – If you need to make up some knowledge (e. g. , Cormen’s algorithm book/class) 3/18/2018 32

VLSI CAD Conferences • Strong in Physical Design – – DAC: Design Automation Conference ICCAD: Int’l Conference on Computer-Aided Design ASP-DAC: Asia & South Pacific Design Automation Conference ISPD: Int’l Symposium on Physical Design • Other Conferences – – – DATE: Design Automation and Test in Europe ISLPED: Int’l Symposium on Low Power Electronics & Design ISQED: Int’l Symposium on Quality Electronic Design ISCAS: Int’l Symposium on Circuits and Systems ICCD: Int’l Conference on Computer Design …… 3/18/2018 33

VLSI CAD Conferences • Strong in Physical Design – – DAC: Design Automation Conference ICCAD: Int’l Conference on Computer-Aided Design ASP-DAC: Asia & South Pacific Design Automation Conference ISPD: Int’l Symposium on Physical Design • Other Conferences – – – DATE: Design Automation and Test in Europe ISLPED: Int’l Symposium on Low Power Electronics & Design ISQED: Int’l Symposium on Quality Electronic Design ISCAS: Int’l Symposium on Circuits and Systems ICCD: Int’l Conference on Computer Design …… 3/18/2018 33

VLSI/CAD Related Journals • IEEE TCAD – IEEE Transactions on CAD of Integrated Circuits and Systems • IEEE TVLSI – IEEE Transactions on VLSI Systems • ACM TODAES – ACM Transactions on Design Automation of Electronic Systems • IEEE TCAS (I and II) – IEEE Transactions on Circuits and Systems • Integration, the VLSI Journal 3/18/2018 34

VLSI/CAD Related Journals • IEEE TCAD – IEEE Transactions on CAD of Integrated Circuits and Systems • IEEE TVLSI – IEEE Transactions on VLSI Systems • ACM TODAES – ACM Transactions on Design Automation of Electronic Systems • IEEE TCAS (I and II) – IEEE Transactions on Circuits and Systems • Integration, the VLSI Journal 3/18/2018 34