afc34da9f967348b7e9558c528be76d6.ppt

- Количество слайдов: 40

ECOE 560 Design Methodologies and Tools for Software/Hardware Systems Spring 2006 Serdar Taşıran

ECOE 560 Design Methodologies and Tools for Software/Hardware Systems Spring 2006 Serdar Taşıran

Outline of today’s lecture n What is a software/hardware (embedded) system? n n n 2 Examples Characteristics The design problem Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Outline of today’s lecture n What is a software/hardware (embedded) system? n n n 2 Examples Characteristics The design problem Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Definition n n Embedded system: any device that includes a programmable computer but is not itself a generalpurpose computer. Take advantage of application characteristics to optimize the design: n 3 don’t need all the general-purpose bells and whistles. ECOE 560, Spring 2006

Definition n n Embedded system: any device that includes a programmable computer but is not itself a generalpurpose computer. Take advantage of application characteristics to optimize the design: n 3 don’t need all the general-purpose bells and whistles. ECOE 560, Spring 2006

Examples n n n n 4 Personal digital assistant (PDA). Printer. Cell phone. Automobile: engine, brakes, dash, etc. Television. Household appliances. PC keyboard (scans keys). ECOE 560, Spring 2006

Examples n n n n 4 Personal digital assistant (PDA). Printer. Cell phone. Automobile: engine, brakes, dash, etc. Television. Household appliances. PC keyboard (scans keys). ECOE 560, Spring 2006

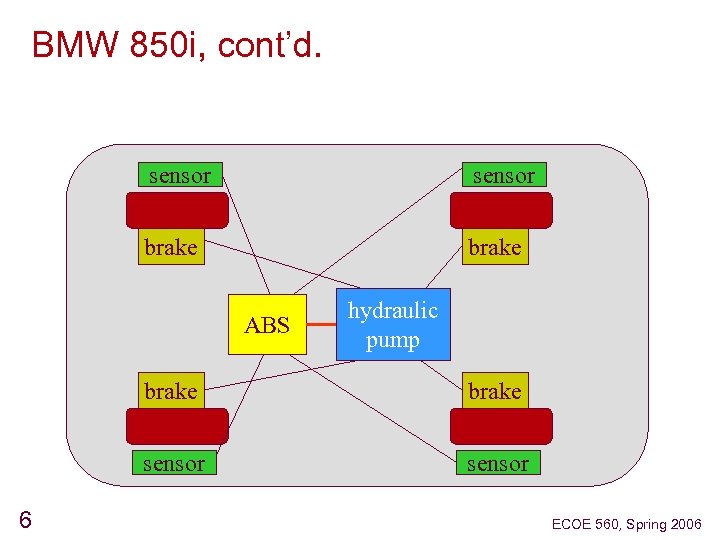

Example: BMW 850 i brake and stability control system n n n Anti-lock brake system (ABS): pumps brakes to reduce skidding. Automatic stability control (ASC+T): controls engine to improve stability. ABS and ASC+T communicate. n 5 ABS was introduced first---needed to interface to existing ABS module. ECOE 560, Spring 2006

Example: BMW 850 i brake and stability control system n n n Anti-lock brake system (ABS): pumps brakes to reduce skidding. Automatic stability control (ASC+T): controls engine to improve stability. ABS and ASC+T communicate. n 5 ABS was introduced first---needed to interface to existing ABS module. ECOE 560, Spring 2006

BMW 850 i, cont’d. sensor brake ABS hydraulic pump brake sensor 6 brake sensor ECOE 560, Spring 2006

BMW 850 i, cont’d. sensor brake ABS hydraulic pump brake sensor 6 brake sensor ECOE 560, Spring 2006

Characteristics of embedded systems n n n 7 Sophisticated functionality. Real-time operation. Low manufacturing cost. Low power. Designed to tight deadlines by small teams. ECOE 560, Spring 2006

Characteristics of embedded systems n n n 7 Sophisticated functionality. Real-time operation. Low manufacturing cost. Low power. Designed to tight deadlines by small teams. ECOE 560, Spring 2006

Functional complexity n Often have to run sophisticated algorithms or multiple algorithms. n n 8 Cell phone, laser printer. Often provide sophisticated user interfaces. ECOE 560, Spring 2006

Functional complexity n Often have to run sophisticated algorithms or multiple algorithms. n n 8 Cell phone, laser printer. Often provide sophisticated user interfaces. ECOE 560, Spring 2006

Real-time operation n Must finish operations by deadlines. n n n 9 Hard real time: missing deadline causes failure. Soft real time: missing deadline results in degraded performance. Many systems are multi-rate: must handle operations at widely varying rates. ECOE 560, Spring 2006

Real-time operation n Must finish operations by deadlines. n n n 9 Hard real time: missing deadline causes failure. Soft real time: missing deadline results in degraded performance. Many systems are multi-rate: must handle operations at widely varying rates. ECOE 560, Spring 2006

Non-functional requirements n Many embedded systems are mass-market items that must have low manufacturing costs. n n Power consumption is critical in battery-powered devices. n 10 Limited memory, microprocessor power, etc. Excessive power consumption increases system cost even in wall-powered devices. ECOE 560, Spring 2006

Non-functional requirements n Many embedded systems are mass-market items that must have low manufacturing costs. n n Power consumption is critical in battery-powered devices. n 10 Limited memory, microprocessor power, etc. Excessive power consumption increases system cost even in wall-powered devices. ECOE 560, Spring 2006

Design teams n n Often designed by a small team of designers. Often must meet tight deadlines. n n 11 6 month market window is common. Can’t miss back-to-school window for calculator. ECOE 560, Spring 2006

Design teams n n Often designed by a small team of designers. Often must meet tight deadlines. n n 11 6 month market window is common. Can’t miss back-to-school window for calculator. ECOE 560, Spring 2006

Example: HP Design. Jet drafting plotter n n Plots up to 36 inches wide at 300 DPI. Combines a variety of tasks: n n 12 host communication; graphics language interpretation; rasterization; device control. ECOE 560, Spring 2006

Example: HP Design. Jet drafting plotter n n Plots up to 36 inches wide at 300 DPI. Combines a variety of tasks: n n 12 host communication; graphics language interpretation; rasterization; device control. ECOE 560, Spring 2006

The plotting process HP-GL/2 Post. Script rasterizer raster memory plotter controller 13 ECOE 560, Spring 2006

The plotting process HP-GL/2 Post. Script rasterizer raster memory plotter controller 13 ECOE 560, Spring 2006

Design considerations n Memory utilization is important. n n 14 36 inches x large x 300 DPI x n bits/pixel is a lot of memory. Requires clever algorithms to minimize raster memory requirements. Requires real-time control. Requires concurrency: read new data, rasterize, control print head. ECOE 560, Spring 2006

Design considerations n Memory utilization is important. n n 14 36 inches x large x 300 DPI x n bits/pixel is a lot of memory. Requires clever algorithms to minimize raster memory requirements. Requires real-time control. Requires concurrency: read new data, rasterize, control print head. ECOE 560, Spring 2006

HP Design. Jet hardware architecture adrs latch bus if i 960 KA EEPROM swath RAM pen ctrl ASIC servo proc. (8052) front panel 15 stepper motor carriage PC board 1 MB ROM 2 MB DRAM proc. support ASIC DRAM ctrl || if RS 422 ECOE 560, Spring 2006

HP Design. Jet hardware architecture adrs latch bus if i 960 KA EEPROM swath RAM pen ctrl ASIC servo proc. (8052) front panel 15 stepper motor carriage PC board 1 MB ROM 2 MB DRAM proc. support ASIC DRAM ctrl || if RS 422 ECOE 560, Spring 2006

Early architectural decisions n Chose Intel 80960 KA as main processor. n n n 16 Handled parsing, rasterization control, print engine control. Multiplexed bus reduced pin count. Could be upgraded to floating-point if necessary. Used modular I/O to host system. Did not use disk for local storage. ECOE 560, Spring 2006

Early architectural decisions n Chose Intel 80960 KA as main processor. n n n 16 Handled parsing, rasterization control, print engine control. Multiplexed bus reduced pin count. Could be upgraded to floating-point if necessary. Used modular I/O to host system. Did not use disk for local storage. ECOE 560, Spring 2006

System components n n 2 MB RAM (SIMM sockets for more). Three ASICs: n n 17 pen interface; processor support; carriage. Servo processing performed by 8052 microcontroller. ECOE 560, Spring 2006

System components n n 2 MB RAM (SIMM sockets for more). Three ASICs: n n 17 pen interface; processor support; carriage. Servo processing performed by 8052 microcontroller. ECOE 560, Spring 2006

Rasterization n Plot is generated in swaths. n n 18 Separate swath memory. Pixels are generated in row order by main processor. Pixels are fed to pens in column order. Pen interface ASIC transforms row order to column order. ECOE 560, Spring 2006

Rasterization n Plot is generated in swaths. n n 18 Separate swath memory. Pixels are generated in row order by main processor. Pixels are fed to pens in column order. Pen interface ASIC transforms row order to column order. ECOE 560, Spring 2006

Data flows parsing and rasterization adrs latch bus if i 960 KA swath generation EEPROM servo proc. (8052) front panel 19 pen ctrl ASIC swath RAM drawing stepper motor carriage PC board 1 MB ROM 2 MB DRAM proc. support ASIC DRAM ctrl || if RS 422 ECOE 560, Spring 2006

Data flows parsing and rasterization adrs latch bus if i 960 KA swath generation EEPROM servo proc. (8052) front panel 19 pen ctrl ASIC swath RAM drawing stepper motor carriage PC board 1 MB ROM 2 MB DRAM proc. support ASIC DRAM ctrl || if RS 422 ECOE 560, Spring 2006

Operations n n 20 Servo processor controls stepper motor. Carriage processor must write, read pen alignment marks. Processor support ASIC provides multiple functions: interrupt and mailbox communication. Motion controller decodes position of print carriage and paper; watchdogs servo. ECOE 560, Spring 2006

Operations n n 20 Servo processor controls stepper motor. Carriage processor must write, read pen alignment marks. Processor support ASIC provides multiple functions: interrupt and mailbox communication. Motion controller decodes position of print carriage and paper; watchdogs servo. ECOE 560, Spring 2006

Pen interface ASIC n n n 21 Interfaces to i 960 bus, swath memory, carriage ASIC. Pen interface reads pixels from swath in predetermined pattern using pixel address generator. Must support bidirectional printing since head prints both ways. ECOE 560, Spring 2006

Pen interface ASIC n n n 21 Interfaces to i 960 bus, swath memory, carriage ASIC. Pen interface reads pixels from swath in predetermined pattern using pixel address generator. Must support bidirectional printing since head prints both ways. ECOE 560, Spring 2006

Carriage ASIC n n n 22 Interfaces to carriage processor bus, pen interface ASIC, servo controller. Reads timing control registers using the CPU bus. Delay registers add correction for pen alignment. ECOE 560, Spring 2006

Carriage ASIC n n n 22 Interfaces to carriage processor bus, pen interface ASIC, servo controller. Reads timing control registers using the CPU bus. Delay registers add correction for pen alignment. ECOE 560, Spring 2006

Development process n n 23 Pixel shuffling algorithm for pen interface/carriage ASICs was prototyped in C. Built emulators for ASICs to allow parallel development of i 960 software and hardware. ECOE 560, Spring 2006

Development process n n 23 Pixel shuffling algorithm for pen interface/carriage ASICs was prototyped in C. Built emulators for ASICs to allow parallel development of i 960 software and hardware. ECOE 560, Spring 2006

Software development environment n Plotter software could be run on Unix workstation or target platform. n n 24 Differed in I/O and print engine subsystems. Print engine was emulated on host with X window interface showing swath state. Used in-house RTOS. HP-GL/2 parser was legacy code. ECOE 560, Spring 2006

Software development environment n Plotter software could be run on Unix workstation or target platform. n n 24 Differed in I/O and print engine subsystems. Print engine was emulated on host with X window interface showing swath state. Used in-house RTOS. HP-GL/2 parser was legacy code. ECOE 560, Spring 2006

Software development environment, cont’d. n n 25 Rewrote vector/raster converter from assembly language to C to port to i 960. Used gdb 960 as monitor debugger on target system, communicating with host. Front panel developed on PC, tested by user interface designers, marketing. Paper loading designed by mechanical engineers. ECOE 560, Spring 2006

Software development environment, cont’d. n n 25 Rewrote vector/raster converter from assembly language to C to port to i 960. Used gdb 960 as monitor debugger on target system, communicating with host. Front panel developed on PC, tested by user interface designers, marketing. Paper loading designed by mechanical engineers. ECOE 560, Spring 2006

Outline of today’s lecture n n 26 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Outline of today’s lecture n n 26 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Course Outline n n System design flow Modeling, specifying, and representing systems: n n Description languages for design specifications and implementations Modeling formalisms: Models of computation and concurrency n Fundamentals: n Hardware implementation (component) technologies: n Software implementation (component) technologies: n Analysis, verification, testing: Functionality. n Analysis, verification, testing: Performance and timing. n Analysis, verification, testing: Power. n System partitioning, architecture exploration. Hardware synthesis. Software synthesis Interface design and synthesis n n 27 n Boolean algebras, functions, relations. Propositional logic, first-order logic. Temporal logics. CPUs, ASICs, FPGAs, DSPs, IP blocks, I/O components, networks, buses, on-chip communication networks, reconfigurable platforms. Operating systems, real-time operating systems, inter-process communication, scheduling. Design and implementation verification. Simulation, emulation, formal verification. Timing analysis and verification of hardware and software. Performance evaluation and estimation. Power analysis, optimization of hardware and software. Power minimization techniques. ECOE 560, Spring 2006

Course Outline n n System design flow Modeling, specifying, and representing systems: n n Description languages for design specifications and implementations Modeling formalisms: Models of computation and concurrency n Fundamentals: n Hardware implementation (component) technologies: n Software implementation (component) technologies: n Analysis, verification, testing: Functionality. n Analysis, verification, testing: Performance and timing. n Analysis, verification, testing: Power. n System partitioning, architecture exploration. Hardware synthesis. Software synthesis Interface design and synthesis n n 27 n Boolean algebras, functions, relations. Propositional logic, first-order logic. Temporal logics. CPUs, ASICs, FPGAs, DSPs, IP blocks, I/O components, networks, buses, on-chip communication networks, reconfigurable platforms. Operating systems, real-time operating systems, inter-process communication, scheduling. Design and implementation verification. Simulation, emulation, formal verification. Timing analysis and verification of hardware and software. Performance evaluation and estimation. Power analysis, optimization of hardware and software. Power minimization techniques. ECOE 560, Spring 2006

Outline of today’s lecture n n 28 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Outline of today’s lecture n n 28 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Design methodologies n n n A procedure for designing a system. Understanding your methodology helps you ensure you didn’t skip anything. Compilers, software engineering tools, computer-aided design (CAD) tools, etc. , can be used to: n n 29 help automate methodology steps; keep track of the methodology itself. ECOE 560, Spring 2006

Design methodologies n n n A procedure for designing a system. Understanding your methodology helps you ensure you didn’t skip anything. Compilers, software engineering tools, computer-aided design (CAD) tools, etc. , can be used to: n n 29 help automate methodology steps; keep track of the methodology itself. ECOE 560, Spring 2006

Design goals n Performance. n n n 30 Overall speed, deadlines. Functionality and user interface. Manufacturing cost. Power consumption. Other requirements (physical size, etc. ) ECOE 560, Spring 2006

Design goals n Performance. n n n 30 Overall speed, deadlines. Functionality and user interface. Manufacturing cost. Power consumption. Other requirements (physical size, etc. ) ECOE 560, Spring 2006

Complexity Design Challenges: Increasing Device and Context Complexity n Exponential increase in device complexity—increasing with Moore’s law (or faster)! n System context in which devices are deployed (e. g. cellular radio) are increasing in complexity as well exponential increases in design productivity We have exponentially more components! 31 ECOE 560, Spring 2006

Complexity Design Challenges: Increasing Device and Context Complexity n Exponential increase in device complexity—increasing with Moore’s law (or faster)! n System context in which devices are deployed (e. g. cellular radio) are increasing in complexity as well exponential increases in design productivity We have exponentially more components! 31 ECOE 560, Spring 2006

Design Challenges: Deep Submicron Effects n Smaller geometries are causing a wide variety of effects that we have largely ignored in the past: n n n DSM Effects n Cross-coupled capacitances Signal integrity Resistance Inductance Design of each transistor is getting more difficult! 32 ECOE 560, Spring 2006

Design Challenges: Deep Submicron Effects n Smaller geometries are causing a wide variety of effects that we have largely ignored in the past: n n n DSM Effects n Cross-coupled capacitances Signal integrity Resistance Inductance Design of each transistor is getting more difficult! 32 ECOE 560, Spring 2006

Design Challenges: Heterogeneous Components Heterogeneity n Greater diversity of on-chip elements n n Processors Software Memory Analog More components doing different things! 33 ECOE 560, Spring 2006

Design Challenges: Heterogeneous Components Heterogeneity n Greater diversity of on-chip elements n n Processors Software Memory Analog More components doing different things! 33 ECOE 560, Spring 2006

Design Challenges: Stronger Market Pressures Time-to-Money n n Decreasing design window Less tolerance for design revisions Exponentially more complex, greater design risk, greater variety, and a smaller design window ! 34 ECOE 560, Spring 2006

Design Challenges: Stronger Market Pressures Time-to-Money n n Decreasing design window Less tolerance for design revisions Exponentially more complex, greater design risk, greater variety, and a smaller design window ! 34 ECOE 560, Spring 2006

Complexity A Quadruple-Whammy Time-to-Money Heterogeneity DSM Effects 35 ECOE 560, Spring 2006

Complexity A Quadruple-Whammy Time-to-Money Heterogeneity DSM Effects 35 ECOE 560, Spring 2006

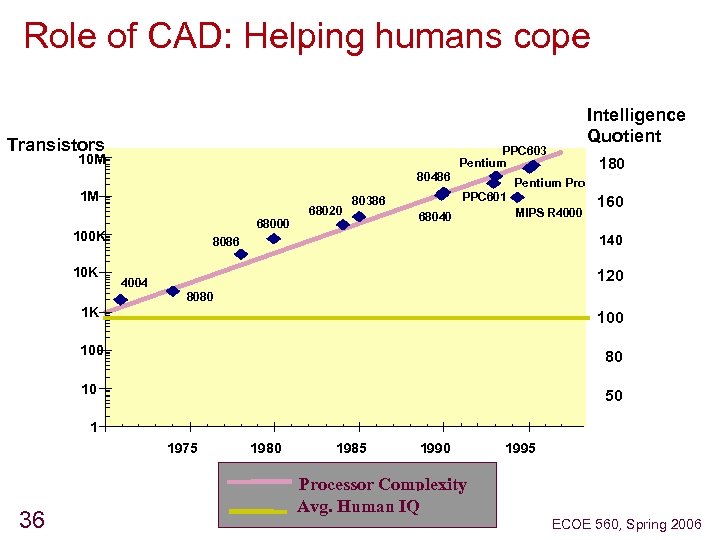

Role of CAD: Helping humans cope Transistors PPC 603 Pentium 10 M 80486 1 M 68000 100 K 10 K Intelligence Quotient 68020 Pentium Pro PPC 601 80386 68040 MIPS R 4000 160 140 8086 4004 180 120 8080 1 K 100 80 10 50 1 1975 36 1980 1985 1990 1995 Processor Complexity Avg. Human IQ ECOE 560, Spring 2006

Role of CAD: Helping humans cope Transistors PPC 603 Pentium 10 M 80486 1 M 68000 100 K 10 K Intelligence Quotient 68020 Pentium Pro PPC 601 80386 68040 MIPS R 4000 160 140 8086 4004 180 120 8080 1 K 100 80 10 50 1 1975 36 1980 1985 1990 1995 Processor Complexity Avg. Human IQ ECOE 560, Spring 2006

Outline of today’s lecture n n 37 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

Outline of today’s lecture n n 37 What is a software/hardware (embedded) system? Course outline Design automation methodologies and tools Levels of abstraction in design descriptions ECOE 560, Spring 2006

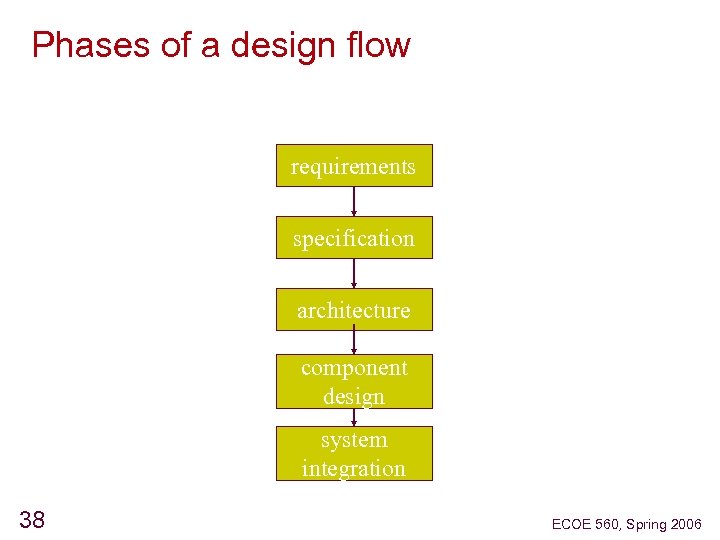

Phases of a design flow requirements specification architecture component design system integration 38 ECOE 560, Spring 2006

Phases of a design flow requirements specification architecture component design system integration 38 ECOE 560, Spring 2006

Top-down vs. bottom-up n Top-down design: n n n Bottom-up design: n n 39 start from most abstract description; work to most detailed. work from small components to big system. Real design uses both techniques. ECOE 560, Spring 2006

Top-down vs. bottom-up n Top-down design: n n n Bottom-up design: n n 39 start from most abstract description; work to most detailed. work from small components to big system. Real design uses both techniques. ECOE 560, Spring 2006

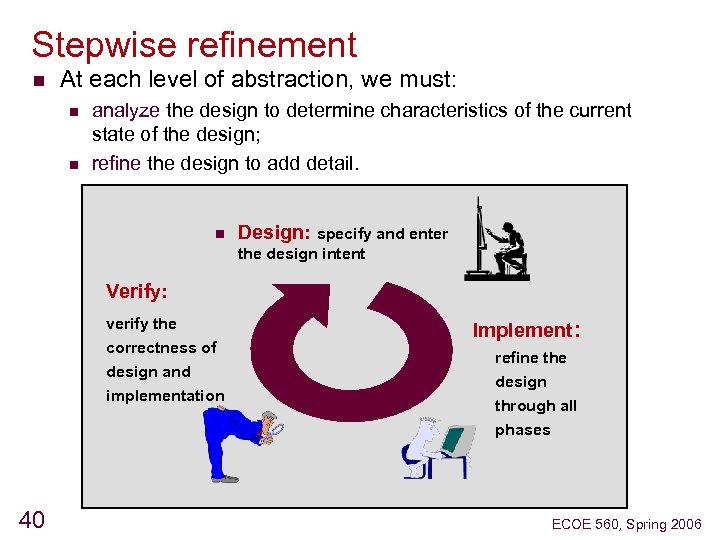

Stepwise refinement n At each level of abstraction, we must: n n analyze the design to determine characteristics of the current state of the design; refine the design to add detail. n Design: specify and enter the design intent Verify: verify the correctness of design and implementation 40 Implement: refine the design through all phases ECOE 560, Spring 2006

Stepwise refinement n At each level of abstraction, we must: n n analyze the design to determine characteristics of the current state of the design; refine the design to add detail. n Design: specify and enter the design intent Verify: verify the correctness of design and implementation 40 Implement: refine the design through all phases ECOE 560, Spring 2006