611791c44a2e11dd50d3172764d8b244.ppt

- Количество слайдов: 13

ECE 3430 – Introduction to Microcomputer Systems University of Colorado at Colorado Springs Lecture #4 Agenda Today 1. More on the LOAD Instructions 2. Big Endian vs. Little Endian 3. HC 11 Addressing Modes Announcements 1. Homework #1 due today. Hand it to me before you leave. 2. Homework #2 available on the web page. Due in one week. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 1

ECE 3430 – Introduction to Microcomputer Systems University of Colorado at Colorado Springs Lecture #4 Agenda Today 1. More on the LOAD Instructions 2. Big Endian vs. Little Endian 3. HC 11 Addressing Modes Announcements 1. Homework #1 due today. Hand it to me before you leave. 2. Homework #2 available on the web page. Due in one week. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 1

The LOAD Instruction LOAD An HC 11 instruction that moves information into the internal registers of the CPU (A, B, D, X, Y, SP). Where the “information” comes from depends on the addressing mode. The addressing mode is encoded in the instruction opcode. Recall operands provide additional information needed by an instruction. The HC 11 has 6 addressing modes. We will use the LOAD instruction to illustrate the first four: 1) 2) 3) 4) Immediate (operand provides the data) Direct (operand provides memory location of data) Extended (operand provides memory location of data) Indexed (operand provides offset to memory location relative to value stored in the X or Y index register) 5) Inherent (no operands used) 6) Relative (operand provides address relative to current value stored in PC register) Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 2

The LOAD Instruction LOAD An HC 11 instruction that moves information into the internal registers of the CPU (A, B, D, X, Y, SP). Where the “information” comes from depends on the addressing mode. The addressing mode is encoded in the instruction opcode. Recall operands provide additional information needed by an instruction. The HC 11 has 6 addressing modes. We will use the LOAD instruction to illustrate the first four: 1) 2) 3) 4) Immediate (operand provides the data) Direct (operand provides memory location of data) Extended (operand provides memory location of data) Indexed (operand provides offset to memory location relative to value stored in the X or Y index register) 5) Inherent (no operands used) 6) Relative (operand provides address relative to current value stored in PC register) Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 2

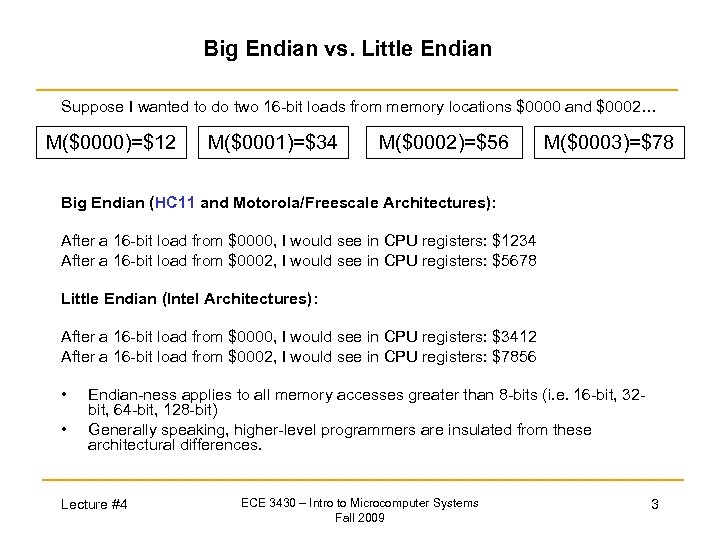

Big Endian vs. Little Endian Suppose I wanted to do two 16 -bit loads from memory locations $0000 and $0002… M($0000)=$12 M($0001)=$34 M($0002)=$56 M($0003)=$78 Big Endian (HC 11 and Motorola/Freescale Architectures): After a 16 -bit load from $0000, I would see in CPU registers: $1234 After a 16 -bit load from $0002, I would see in CPU registers: $5678 Little Endian (Intel Architectures): After a 16 -bit load from $0000, I would see in CPU registers: $3412 After a 16 -bit load from $0002, I would see in CPU registers: $7856 • • Endian-ness applies to all memory accesses greater than 8 -bits (i. e. 16 -bit, 32 bit, 64 -bit, 128 -bit) Generally speaking, higher-level programmers are insulated from these architectural differences. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 3

Big Endian vs. Little Endian Suppose I wanted to do two 16 -bit loads from memory locations $0000 and $0002… M($0000)=$12 M($0001)=$34 M($0002)=$56 M($0003)=$78 Big Endian (HC 11 and Motorola/Freescale Architectures): After a 16 -bit load from $0000, I would see in CPU registers: $1234 After a 16 -bit load from $0002, I would see in CPU registers: $5678 Little Endian (Intel Architectures): After a 16 -bit load from $0000, I would see in CPU registers: $3412 After a 16 -bit load from $0002, I would see in CPU registers: $7856 • • Endian-ness applies to all memory accesses greater than 8 -bits (i. e. 16 -bit, 32 bit, 64 -bit, 128 -bit) Generally speaking, higher-level programmers are insulated from these architectural differences. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 3

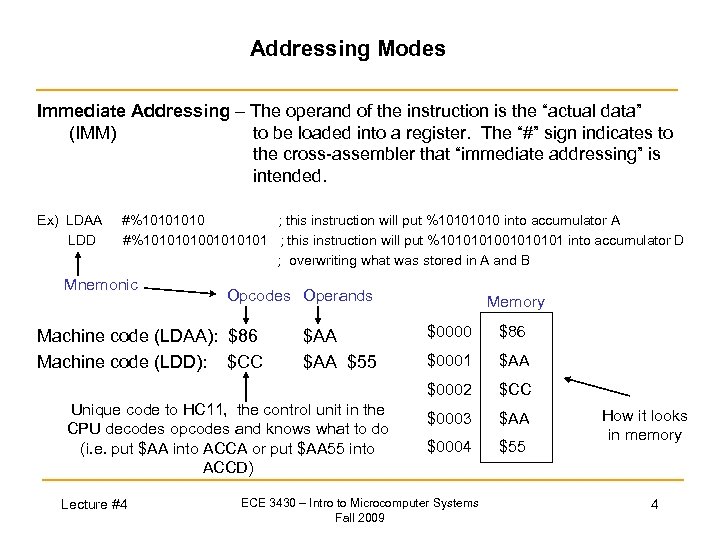

Addressing Modes Immediate Addressing – The operand of the instruction is the “actual data” (IMM) to be loaded into a register. The “#” sign indicates to the cross-assembler that “immediate addressing” is intended. Ex) LDAA LDD #%1010 ; this instruction will put %1010 into accumulator A #%10100101 ; this instruction will put %10100101 into accumulator D ; overwriting what was stored in A and B Mnemonic Opcodes Operands Memory $AA $55 Unique code to HC 11, the control unit in the CPU decodes opcodes and knows what to do (i. e. put $AA into ACCA or put $AA 55 into ACCD) Lecture #4 $0000 $86 $0001 $AA $0002 Machine code (LDAA): $86 Machine code (LDD): $CC $0003 $AA $0004 $55 ECE 3430 – Intro to Microcomputer Systems Fall 2009 How it looks in memory 4

Addressing Modes Immediate Addressing – The operand of the instruction is the “actual data” (IMM) to be loaded into a register. The “#” sign indicates to the cross-assembler that “immediate addressing” is intended. Ex) LDAA LDD #%1010 ; this instruction will put %1010 into accumulator A #%10100101 ; this instruction will put %10100101 into accumulator D ; overwriting what was stored in A and B Mnemonic Opcodes Operands Memory $AA $55 Unique code to HC 11, the control unit in the CPU decodes opcodes and knows what to do (i. e. put $AA into ACCA or put $AA 55 into ACCD) Lecture #4 $0000 $86 $0001 $AA $0002 Machine code (LDAA): $86 Machine code (LDD): $CC $0003 $AA $0004 $55 ECE 3430 – Intro to Microcomputer Systems Fall 2009 How it looks in memory 4

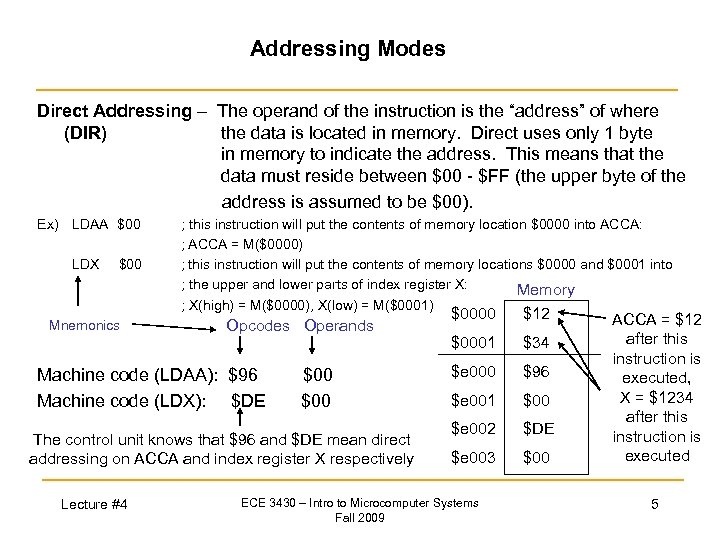

Addressing Modes Direct Addressing – The operand of the instruction is the “address” of where (DIR) the data is located in memory. Direct uses only 1 byte in memory to indicate the address. This means that the data must reside between $00 - $FF (the upper byte of the address is assumed to be $00). Ex) LDAA $00 LDX $00 Mnemonics ; this instruction will put the contents of memory location $0000 into ACCA: ; ACCA = M($0000) ; this instruction will put the contents of memory locations $0000 and $0001 into ; the upper and lower parts of index register X: Memory ; X(high) = M($0000), X(low) = M($0001) Opcodes Operands Machine code (LDAA): $96 Machine code (LDX): $DE $00 The control unit knows that $96 and $DE mean direct addressing on ACCA and index register X respectively Lecture #4 $0000 $12 $0001 $34 $e 000 $96 $e 001 $00 $e 002 $DE $e 003 $00 ECE 3430 – Intro to Microcomputer Systems Fall 2009 ACCA = $12 after this instruction is executed, X = $1234 after this instruction is executed 5

Addressing Modes Direct Addressing – The operand of the instruction is the “address” of where (DIR) the data is located in memory. Direct uses only 1 byte in memory to indicate the address. This means that the data must reside between $00 - $FF (the upper byte of the address is assumed to be $00). Ex) LDAA $00 LDX $00 Mnemonics ; this instruction will put the contents of memory location $0000 into ACCA: ; ACCA = M($0000) ; this instruction will put the contents of memory locations $0000 and $0001 into ; the upper and lower parts of index register X: Memory ; X(high) = M($0000), X(low) = M($0001) Opcodes Operands Machine code (LDAA): $96 Machine code (LDX): $DE $00 The control unit knows that $96 and $DE mean direct addressing on ACCA and index register X respectively Lecture #4 $0000 $12 $0001 $34 $e 000 $96 $e 001 $00 $e 002 $DE $e 003 $00 ECE 3430 – Intro to Microcomputer Systems Fall 2009 ACCA = $12 after this instruction is executed, X = $1234 after this instruction is executed 5

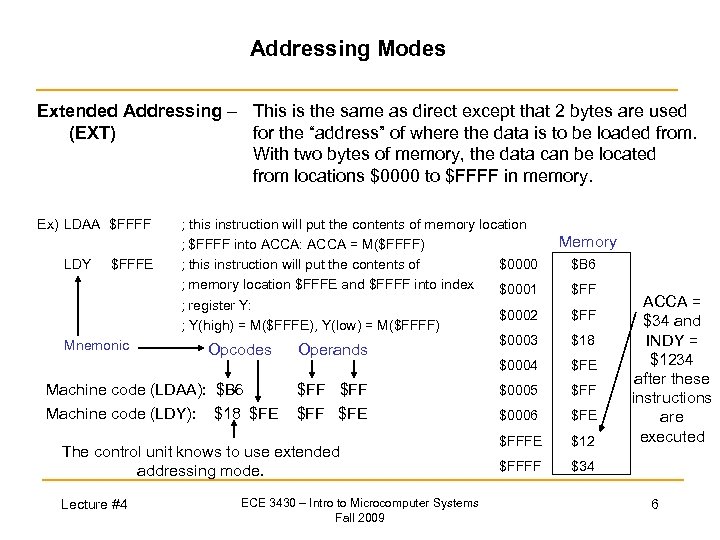

Addressing Modes Extended Addressing – This is the same as direct except that 2 bytes are used (EXT) for the “address” of where the data is to be loaded from. With two bytes of memory, the data can be located from locations $0000 to $FFFF in memory. Ex) LDAA $FFFF LDY $FFFE Mnemonic ; this instruction will put the contents of memory location ; $FFFF into ACCA: ACCA = M($FFFF) ; this instruction will put the contents of $0000 ; memory location $FFFE and $FFFF into index $0001 ; register Y: $0002 ; Y(high) = M($FFFE), Y(low) = M($FFFF) $0003 Opcodes Machine code (LDAA): $B 6 Machine code (LDY): $18 $FE Operands $FF $FF $FE The control unit knows to use extended addressing mode. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 Memory $B 6 $FF $18 $0004 $FE $0005 $FF $0006 $FE $FFFE $12 $FFFF ACCA = $34 and INDY = $1234 after these instructions are executed $34 6

Addressing Modes Extended Addressing – This is the same as direct except that 2 bytes are used (EXT) for the “address” of where the data is to be loaded from. With two bytes of memory, the data can be located from locations $0000 to $FFFF in memory. Ex) LDAA $FFFF LDY $FFFE Mnemonic ; this instruction will put the contents of memory location ; $FFFF into ACCA: ACCA = M($FFFF) ; this instruction will put the contents of $0000 ; memory location $FFFE and $FFFF into index $0001 ; register Y: $0002 ; Y(high) = M($FFFE), Y(low) = M($FFFF) $0003 Opcodes Machine code (LDAA): $B 6 Machine code (LDY): $18 $FE Operands $FF $FF $FE The control unit knows to use extended addressing mode. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 Memory $B 6 $FF $18 $0004 $FE $0005 $FF $0006 $FE $FFFE $12 $FFFF ACCA = $34 and INDY = $1234 after these instructions are executed $34 6

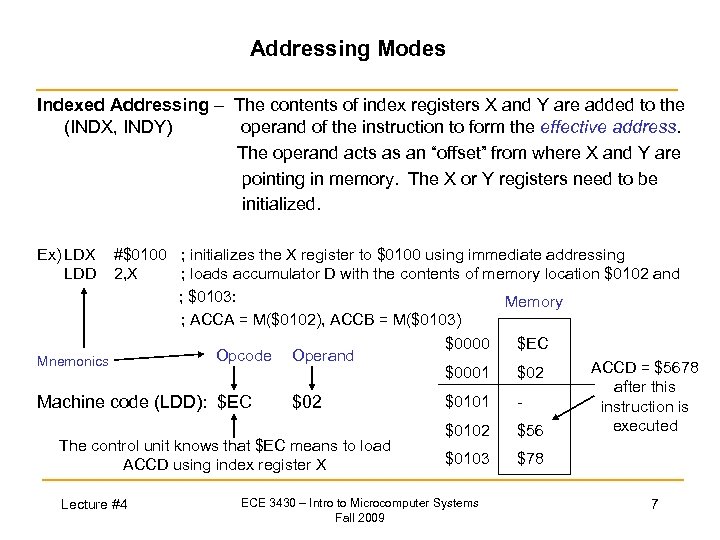

Addressing Modes Indexed Addressing – The contents of index registers X and Y are added to the (INDX, INDY) operand of the instruction to form the effective address. The operand acts as an “offset” from where X and Y are pointing in memory. The X or Y registers need to be initialized. Ex) LDX LDD #$0100 ; initializes the X register to $0100 using immediate addressing 2, X ; loads accumulator D with the contents of memory location $0102 and ; $0103: Memory ; ACCA = M($0102), ACCB = M($0103) $0000 $EC Opcode Operand Mnemonics ACCD = $5678 $0001 $02 after this $0101 Machine code (LDD): $EC $02 instruction is executed $0102 $56 The control unit knows that $EC means to load $0103 $78 ACCD using index register X Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 7

Addressing Modes Indexed Addressing – The contents of index registers X and Y are added to the (INDX, INDY) operand of the instruction to form the effective address. The operand acts as an “offset” from where X and Y are pointing in memory. The X or Y registers need to be initialized. Ex) LDX LDD #$0100 ; initializes the X register to $0100 using immediate addressing 2, X ; loads accumulator D with the contents of memory location $0102 and ; $0103: Memory ; ACCA = M($0102), ACCB = M($0103) $0000 $EC Opcode Operand Mnemonics ACCD = $5678 $0001 $02 after this $0101 Machine code (LDD): $EC $02 instruction is executed $0102 $56 The control unit knows that $EC means to load $0103 $78 ACCD using index register X Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 7

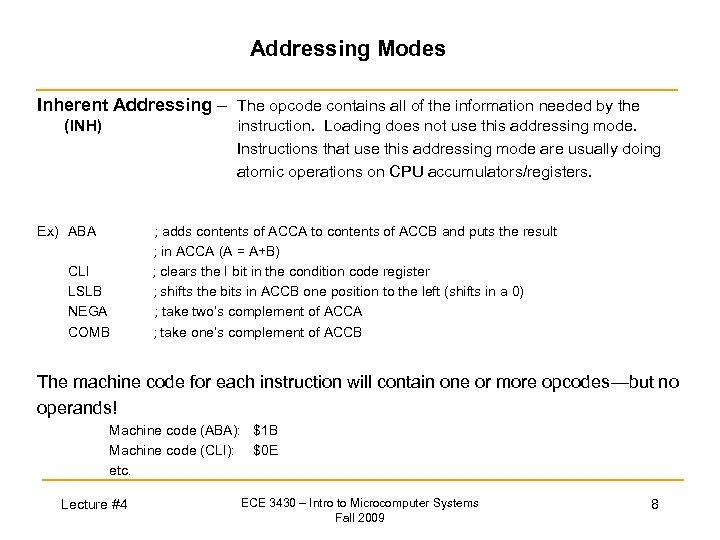

Addressing Modes Inherent Addressing – The opcode contains all of the information needed by the (INH) instruction. Loading does not use this addressing mode. Instructions that use this addressing mode are usually doing atomic operations on CPU accumulators/registers. Ex) ABA CLI LSLB NEGA COMB ; adds contents of ACCA to contents of ACCB and puts the result ; in ACCA (A = A+B) ; clears the I bit in the condition code register ; shifts the bits in ACCB one position to the left (shifts in a 0) ; take two’s complement of ACCA ; take one’s complement of ACCB The machine code for each instruction will contain one or more opcodes—but no operands! Machine code (ABA): $1 B Machine code (CLI): $0 E etc. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 8

Addressing Modes Inherent Addressing – The opcode contains all of the information needed by the (INH) instruction. Loading does not use this addressing mode. Instructions that use this addressing mode are usually doing atomic operations on CPU accumulators/registers. Ex) ABA CLI LSLB NEGA COMB ; adds contents of ACCA to contents of ACCB and puts the result ; in ACCA (A = A+B) ; clears the I bit in the condition code register ; shifts the bits in ACCB one position to the left (shifts in a 0) ; take two’s complement of ACCA ; take one’s complement of ACCB The machine code for each instruction will contain one or more opcodes—but no operands! Machine code (ABA): $1 B Machine code (CLI): $0 E etc. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 8

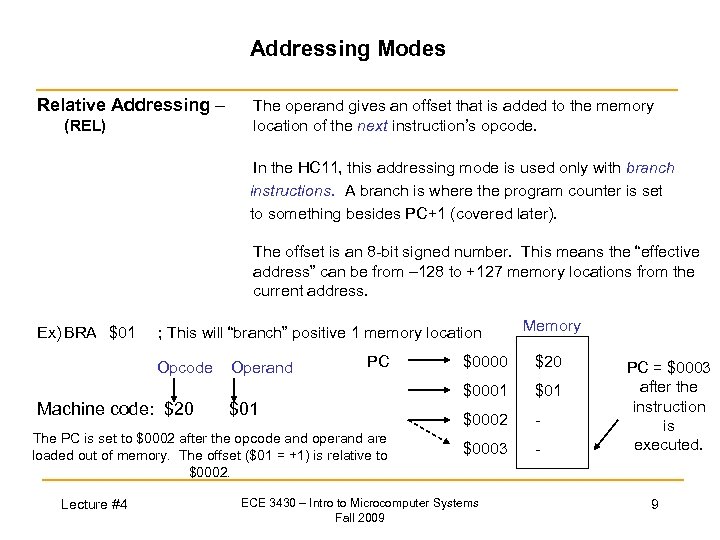

Addressing Modes Relative Addressing – (REL) The operand gives an offset that is added to the memory location of the next instruction’s opcode. In the HC 11, this addressing mode is used only with branch instructions. A branch is where the program counter is set to something besides PC+1 (covered later). The offset is an 8 -bit signed number. This means the “effective address” can be from – 128 to +127 memory locations from the current address. Ex) BRA $01 ; This will “branch” positive 1 memory location Opcode Machine code: $20 Operand PC $01 The PC is set to $0002 after the opcode and operand are loaded out of memory. The offset ($01 = +1) is relative to $0002. Lecture #4 Memory $0000 $20 $0001 $0002 - $0003 - ECE 3430 – Intro to Microcomputer Systems Fall 2009 PC = $0003 after the instruction is executed. 9

Addressing Modes Relative Addressing – (REL) The operand gives an offset that is added to the memory location of the next instruction’s opcode. In the HC 11, this addressing mode is used only with branch instructions. A branch is where the program counter is set to something besides PC+1 (covered later). The offset is an 8 -bit signed number. This means the “effective address” can be from – 128 to +127 memory locations from the current address. Ex) BRA $01 ; This will “branch” positive 1 memory location Opcode Machine code: $20 Operand PC $01 The PC is set to $0002 after the opcode and operand are loaded out of memory. The offset ($01 = +1) is relative to $0002. Lecture #4 Memory $0000 $20 $0001 $0002 - $0003 - ECE 3430 – Intro to Microcomputer Systems Fall 2009 PC = $0003 after the instruction is executed. 9

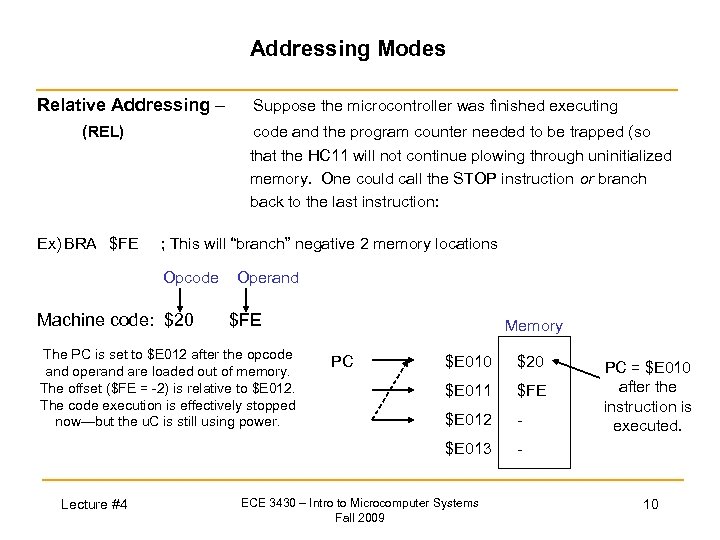

Addressing Modes Relative Addressing – (REL) Ex) BRA $FE Suppose the microcontroller was finished executing code and the program counter needed to be trapped (so that the HC 11 will not continue plowing through uninitialized memory. One could call the STOP instruction or branch back to the last instruction: ; This will “branch” negative 2 memory locations Opcode Machine code: $20 Operand $FE The PC is set to $E 012 after the opcode and operand are loaded out of memory. The offset ($FE = -2) is relative to $E 012. The code execution is effectively stopped now—but the u. C is still using power. Memory $E 010 $20 $E 011 $FE $E 012 - $E 013 Lecture #4 PC - ECE 3430 – Intro to Microcomputer Systems Fall 2009 PC = $E 010 after the instruction is executed. 10

Addressing Modes Relative Addressing – (REL) Ex) BRA $FE Suppose the microcontroller was finished executing code and the program counter needed to be trapped (so that the HC 11 will not continue plowing through uninitialized memory. One could call the STOP instruction or branch back to the last instruction: ; This will “branch” negative 2 memory locations Opcode Machine code: $20 Operand $FE The PC is set to $E 012 after the opcode and operand are loaded out of memory. The offset ($FE = -2) is relative to $E 012. The code execution is effectively stopped now—but the u. C is still using power. Memory $E 010 $20 $E 011 $FE $E 012 - $E 013 Lecture #4 PC - ECE 3430 – Intro to Microcomputer Systems Fall 2009 PC = $E 010 after the instruction is executed. 10

Addressing Modes Relative Addressing – (REL) Ex) DONE: These offsets are really confusing! Fortunately assemblers make use of labels and these labels allow the assembler to automatically calculate the correct offsets for you! This will be discussed later. BRA DONE is a label which labels the BRA instruction. The label can be called just about anything. The above is valid assembly syntax and will be converted the correct machine code by the assembler. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 11

Addressing Modes Relative Addressing – (REL) Ex) DONE: These offsets are really confusing! Fortunately assemblers make use of labels and these labels allow the assembler to automatically calculate the correct offsets for you! This will be discussed later. BRA DONE is a label which labels the BRA instruction. The label can be called just about anything. The above is valid assembly syntax and will be converted the correct machine code by the assembler. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 11

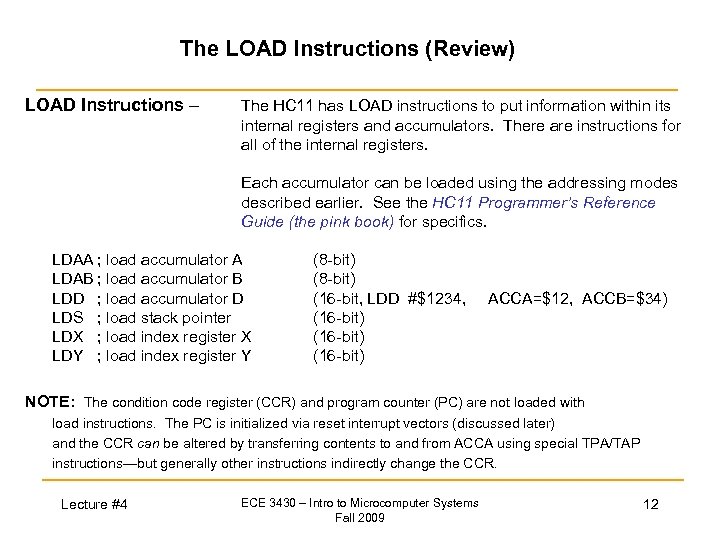

The LOAD Instructions (Review) LOAD Instructions – The HC 11 has LOAD instructions to put information within its internal registers and accumulators. There are instructions for all of the internal registers. Each accumulator can be loaded using the addressing modes described earlier. See the HC 11 Programmer’s Reference Guide (the pink book) for specifics. LDAA ; load accumulator A LDAB ; load accumulator B LDD ; load accumulator D LDS ; load stack pointer LDX ; load index register X LDY ; load index register Y (8 -bit) (16 -bit, LDD #$1234, (16 -bit) ACCA=$12, ACCB=$34) NOTE: The condition code register (CCR) and program counter (PC) are not loaded with load instructions. The PC is initialized via reset interrupt vectors (discussed later) and the CCR can be altered by transferring contents to and from ACCA using special TPA/TAP instructions—but generally other instructions indirectly change the CCR. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 12

The LOAD Instructions (Review) LOAD Instructions – The HC 11 has LOAD instructions to put information within its internal registers and accumulators. There are instructions for all of the internal registers. Each accumulator can be loaded using the addressing modes described earlier. See the HC 11 Programmer’s Reference Guide (the pink book) for specifics. LDAA ; load accumulator A LDAB ; load accumulator B LDD ; load accumulator D LDS ; load stack pointer LDX ; load index register X LDY ; load index register Y (8 -bit) (16 -bit, LDD #$1234, (16 -bit) ACCA=$12, ACCB=$34) NOTE: The condition code register (CCR) and program counter (PC) are not loaded with load instructions. The PC is initialized via reset interrupt vectors (discussed later) and the CCR can be altered by transferring contents to and from ACCA using special TPA/TAP instructions—but generally other instructions indirectly change the CCR. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 12

To Find Out More About HC 11 Instructions See the pink book. A large table runs length-wise and consumes many pages. Here you will find the entire HC 11 instruction set (alphabetized) along with the opcodes for each instruction (for all supported addressing modes). You will need to reference this when doing homework #2. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 13

To Find Out More About HC 11 Instructions See the pink book. A large table runs length-wise and consumes many pages. Here you will find the entire HC 11 instruction set (alphabetized) along with the opcodes for each instruction (for all supported addressing modes). You will need to reference this when doing homework #2. Lecture #4 ECE 3430 – Intro to Microcomputer Systems Fall 2009 13