38fbaff5864cd554e5a6ff7447d12ef6.ppt

- Количество слайдов: 52

Dynamic Traffic Control Group 2 Project Objective : Chun Han Chen Timothy Kwan Tom Bolds Shang Yi Lin Dynamic Control of Traffic Lights Manager Wed. Dec. 3 Randal Hong

Presentation Outline Marketing Project Description Design Process Floor Plan Evolution Layout Verification Issues Encountered Specifications

Marketing / Description Tom Bolds

Current System The current system has sensors that detects cars leaving their lanes Induction loops under the pavement Video cameras Depending on the time of day, the intersection lets each arm go for a set amount of time If no cars are present in one arm, the other arm is green It cannot learn or adapt Cost for entire system: $35, 000

A Better System This system detects cars entering and leaving each arm The time that an arm is green is determined in part, by past traffic Exceptional traffic flow will change the system immediately Cost for entire system: $24, 000

Market 4 Million traffic lights in the US A few user inputs lets the system be adjustable for different situations Roads of different sizes Different space constraints Price goes down and quality goes up

Goals When the government is involved, cost needs to be low Only 4 metal layers used Optimized for small size Could have gone the “all pseudo-nmos” route We don’t want to use megawatts on a traffic light Cmos logic to minimize size and power consumption

Goals Even if it causes just a few accidents nobody will buy it, and we get sued Design needs to be robust Handle power failures Return to a known state Predictable behavior People are used to driving a certain way No accidental switching Minimum time for lights to change

Installation The only change necessary would be the detectors for entering/leaving cars Current system has ground sensors or video camera to detect the first car at an intersection Could add another detector farther back, or use video/sound detection to determine where cars are

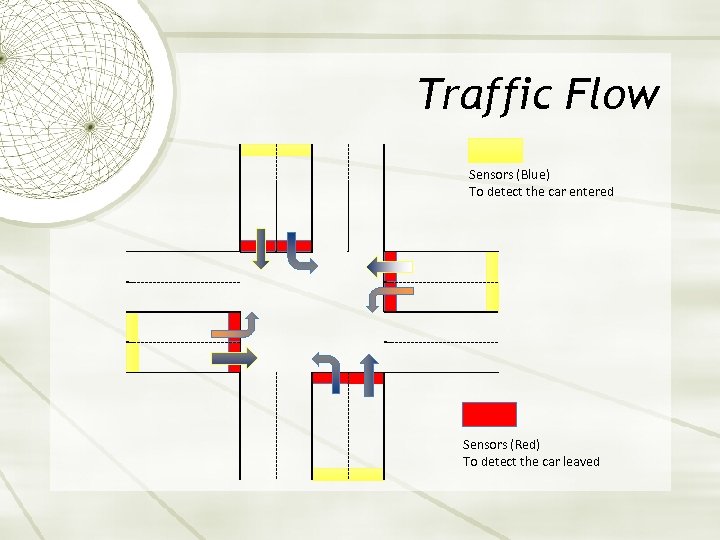

Traffic Flow Sensors (Blue) To detect the car entered Sensors (Red) To detect the car leaved

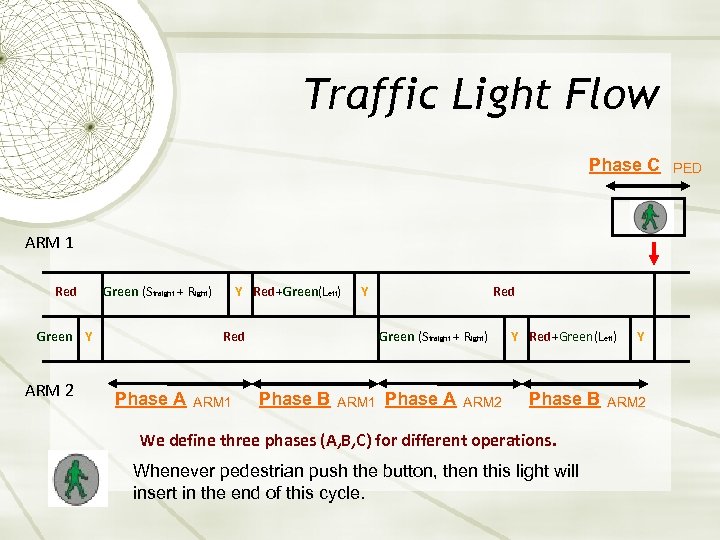

Traffic Light Flow Phase C ARM 1 Red Green (Straight + Right) Green Y ARM 2 Y Red+Green(Left) Y Red Phase A ARM 1 Red Green (Straight + Right) Phase B ARM 1 Phase A ARM 2 Y Red+Green(Left) Phase B We define three phases (A, B, C) for different operations. Whenever pedestrian push the button, then this light will insert in the end of this cycle. Y ARM 2 PED

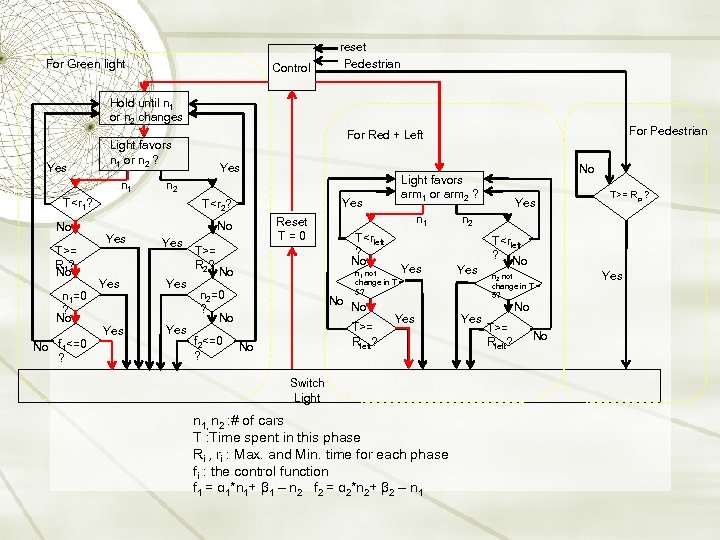

For Green light Control reset Pedestrian Hold until n 1 or n 2 changes Yes Light favors n 1 or n 2 ? n 1 No T>= R 1? No n 1=0 ? No No f 1<=0 ? Yes n 2 T<r 1? Yes T<r 2? Yes Yes Reset T=0 No Yes Yes For Pedestrian For Red + Left T>= R 2? n 2=0 ? No f 2<=0 ? n 1 T<rleft ? No Yes n 1 not change in T = 5? No No No T>= Rleft? No No Light favors arm 1 or arm 2 ? Yes Switch Light n 1, n 2 : # of cars T : Time spent in this phase Ri , ri : Max. and Min. time for each phase fi : the control function f 1 = α 1*n 1+ β 1 – n 2 f 2 = α 2*n 2+ β 2 – n 1 Yes T>= Rp ? n 2 Yes T<rleft ? No n 2 not change in T = 5? No T>= Rleft? No Yes

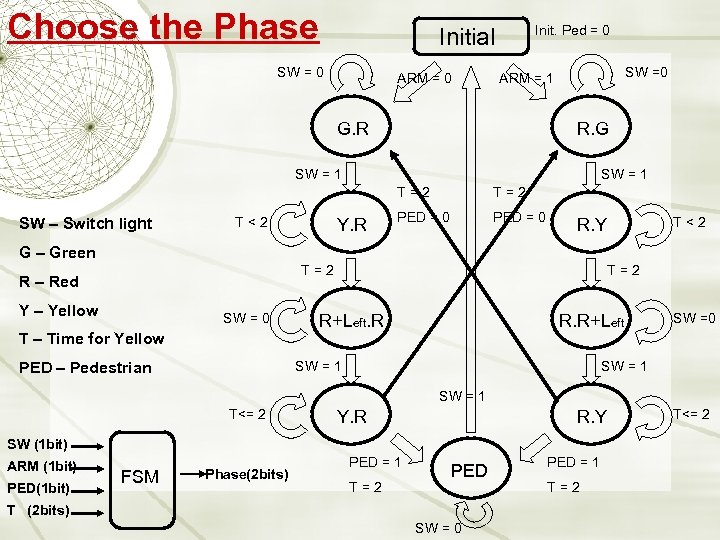

Choose the Phase Init. Ped = 0 Initial SW = 0 ARM = 0 SW =0 ARM = 1 G. R R. G SW = 1 T=2 SW – Switch light T<2 Y. R T=2 PED = 0 T<2 R. Y G – Green T=2 R – Red Y – Yellow SW = 0 T – Time for Yellow T=2 R+Left. R R. R+Left SW = 1 PED – Pedestrian SW =0 SW = 1 T<= 2 Y. R R. Y SW (1 bit) ARM (1 bit) PED(1 bit) FSM Phase(2 bits) PED = 1 T=2 PED T (2 bits) SW = 0 PED = 1 T=2 T<= 2

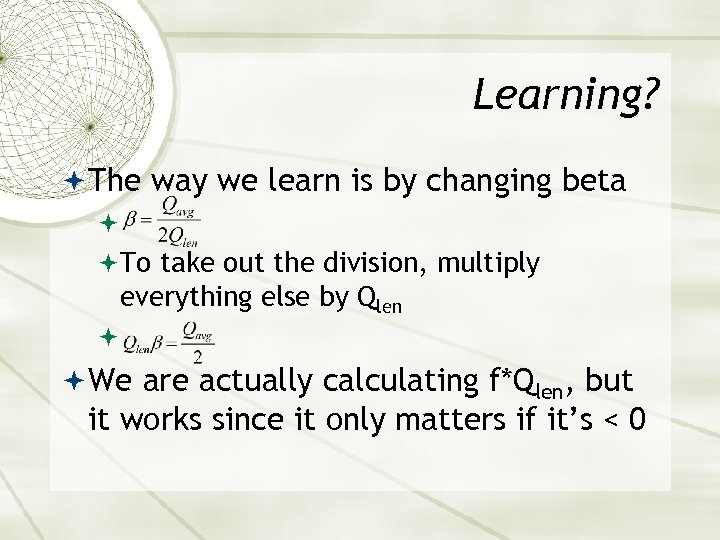

Learning? The way we learn is by changing beta To take out the division, multiply everything else by Qlen We are actually calculating f*Qlen, but it works since it only matters if it’s < 0

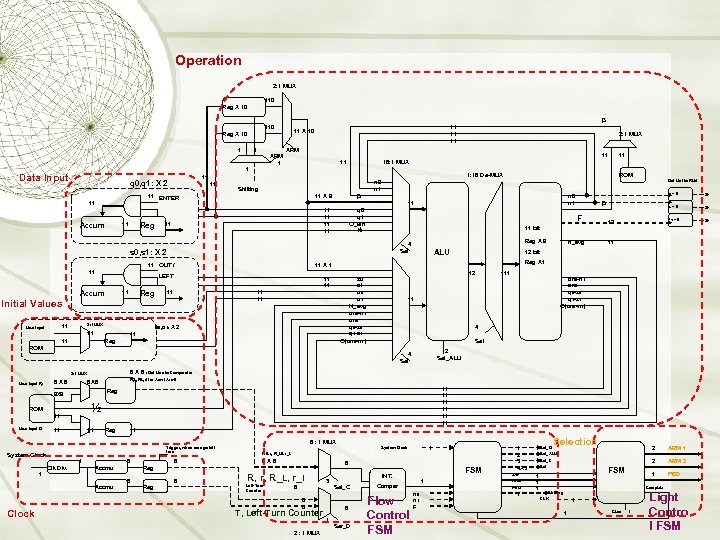

Operation 2: 1 MUX 110 Reg X 10 β 110 Reg X 10 1 1 ARM 1 1 Data Input 11 q 0, q 1: X 2 11 11 Accum Reg 11 11 1: 16 De-MUX 11 X 9 Dot Lint to FSM β 11 11 11 q 0 q 1 Q_len ½ 11 bit Reg 2: 1 MUX 11 User Input 11 11 Reg Sel ½ 11 11 Reg Clk Div. 1 Accmu Clock 11 8 : 1 MUX Trigger, when cars go left turn System Clock 1 11 11 11 Reg 8 X 8 User Input Q 2 Sel_ALU R, r, RL, rl for Arm 1 Arm 2 8 X 8 11 αn 0 -n 1 αn 0 q 0 -s 0 q 1 -s 1 Q(αn 0 -n 1) 8 X 8 : Dot Line to Comparator 2: 1 MUX ROM 11 4 4 Sel 8 X 8 111 11 ROM User Input R, r n_avg F <= 0 12 12 bit 12 s 0 s 1 α 0 α 1 N_avg αn 0 -n 1 αn 0 q 0 -s 0 q 1 -s 1 Q(αn 0 -n 1) α 0, α 1: X 2 11 Reg X 9 ALU n 1 = 0 Reg X 1 11 11 Initial Values β F 11 X 1 11 n 0 = 0 n 1 11 4 Sel LEFT Accum ROM n 0 n 1 Shifting 11 OUT / 11 11 16: 1 MUX s 0, s 1: X 2 11 2: 1 MUX ARM 11 ENTER 11 11 11 X 10 8 8 Reg System Clock 1 R & r, R_L& r_L 8 8 X 8 8 R, r, R_L, r_l 8 Left-Turn Counter T, T Left-Turn 8 3 8 8 Counter 2 : 1 MUX FSM INT. Sel_C 1 Compar n 0 1 8 1 Ser_D SW ARM PED n Flow F Control FSM Sel_D 1 2 3 4 X 3 1 Selection 2 Sel 1 1 1 FSM ARM 2 1 Sel_C ARM 1 2 Sel_ALU PED Complete Shifting CLK 1 1 Clear 1 Light Contro l FSM

Design Process Shang-Yi Lin

Design Process – Objective Goal - Compact Area - Low Power Trade-Off - Performance

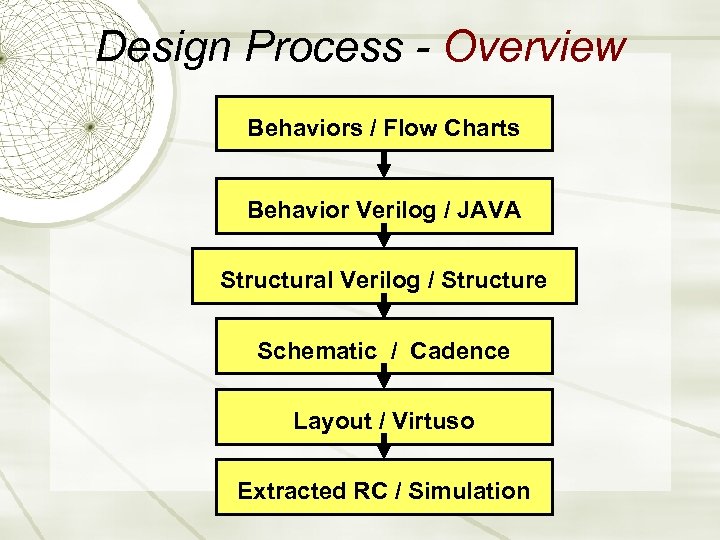

Design Process - Overview Behaviors / Flow Charts Behavior Verilog / JAVA Structural Verilog / Structure Schematic / Cadence Layout / Virtuso Extracted RC / Simulation

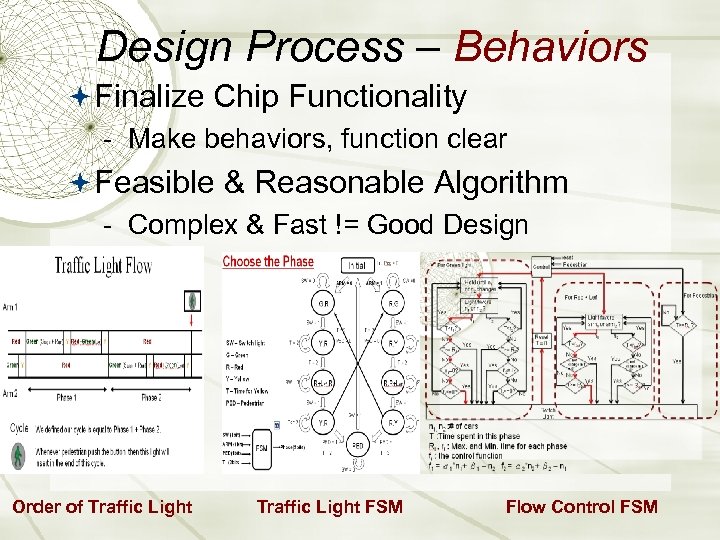

Design Process – Behaviors Finalize Chip Functionality - Make behaviors, function clear Feasible & Reasonable Algorithm - Complex & Fast != Good Design Order of Traffic Light FSM Flow Control FSM

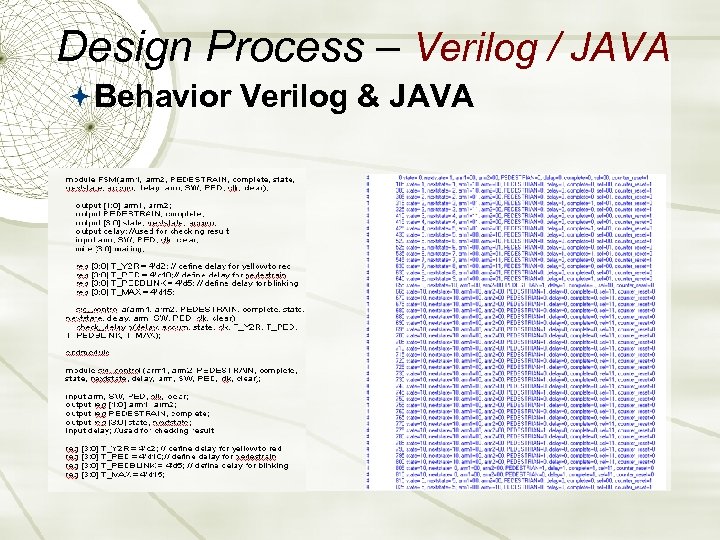

Design Process – Verilog / JAVA Behavior Verilog & JAVA

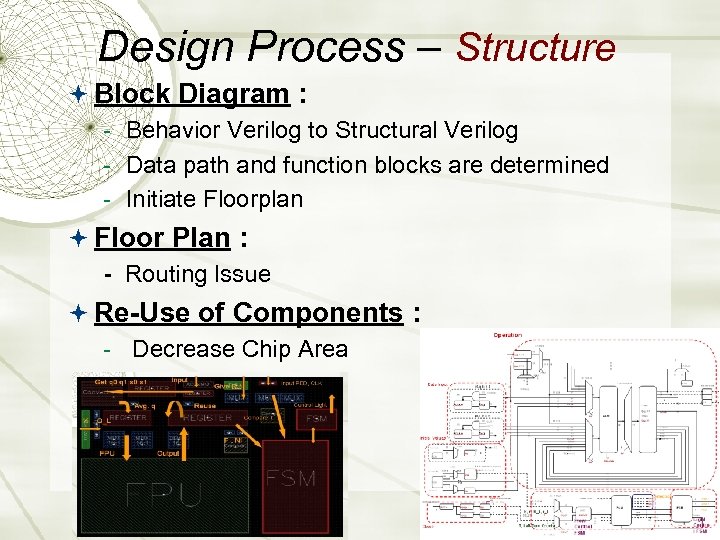

Design Process – Structure Block Diagram : - Behavior Verilog to Structural Verilog - Data path and function blocks are determined - Initiate Floorplan Floor Plan : - Routing Issue Re-Use of Components : - Decrease Chip Area

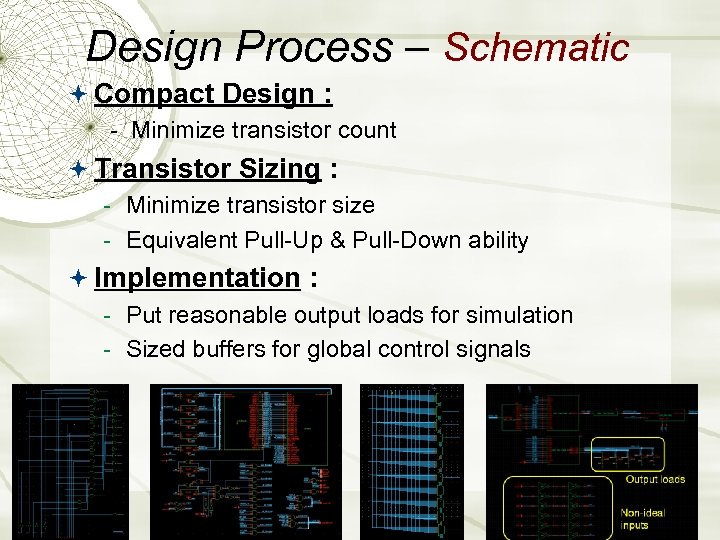

Design Process – Schematic Compact Design : - Minimize transistor count Transistor Sizing : - Minimize transistor size - Equivalent Pull-Up & Pull-Down ability Implementation : - Put reasonable output loads for simulation - Sized buffers for global control signals

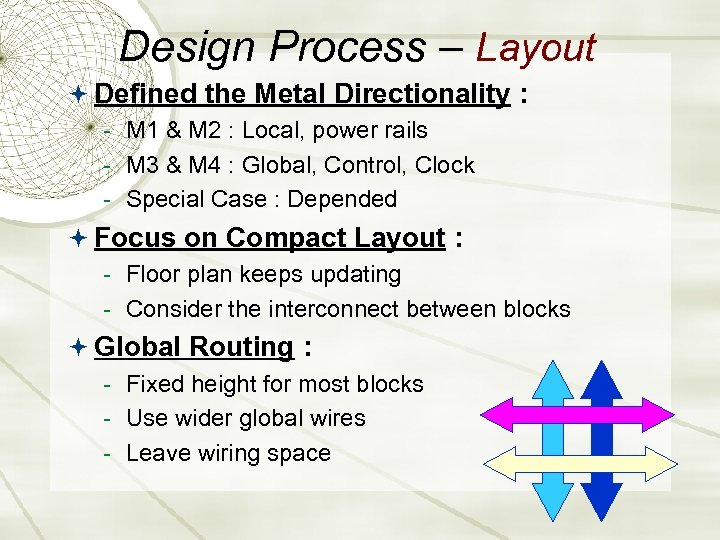

Design Process – Layout Defined the Metal Directionality : - M 1 & M 2 : Local, power rails - M 3 & M 4 : Global, Control, Clock - Special Case : Depended Focus on Compact Layout : - Floor plan keeps updating - Consider the interconnect between blocks Global Routing : - Fixed height for most blocks - Use wider global wires - Leave wiring space

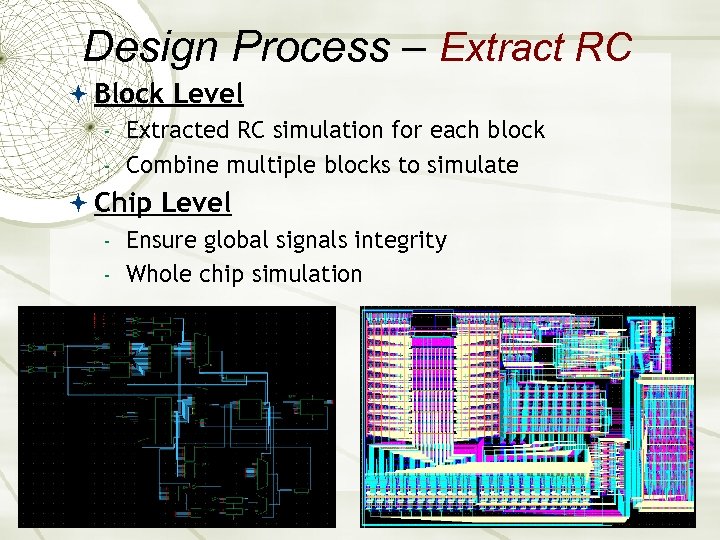

Design Process – Extract RC Block Level - Extracted RC simulation for each block - Combine multiple blocks to simulate Chip Level - Ensure global signals integrity - Whole chip simulation

Floorplan Evolution Shang-Yi Lin

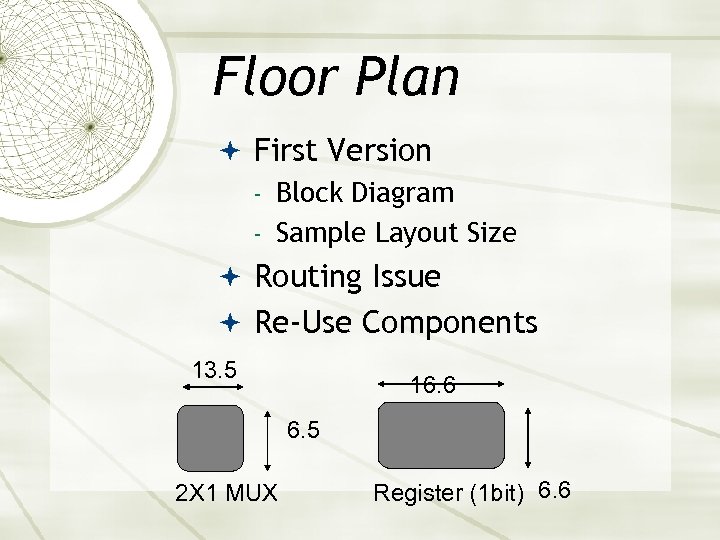

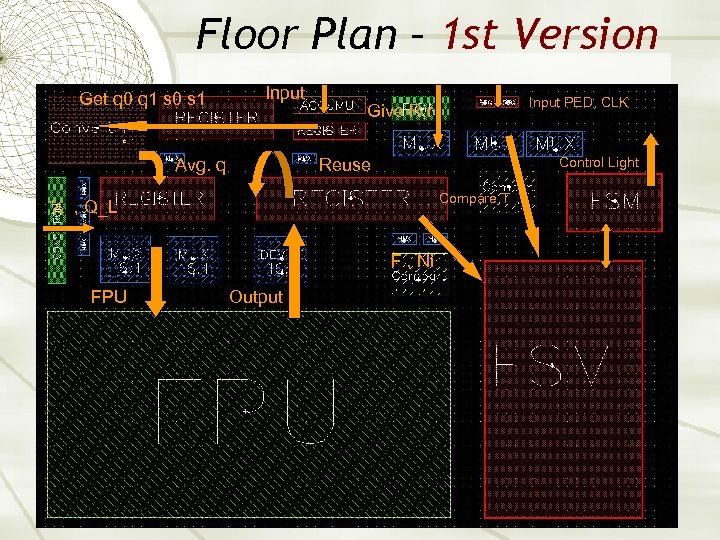

Floor Plan First Version - Block Diagram - Sample Layout Size Routing Issue Re-Use Components 13. 5 16. 6 6. 5 2 X 1 MUX Register (1 bit) 6. 6

Floor Plan – 1 st Version Get q 0 q 1 s 0 s 1 Input Avg. q Control Light Reuse Compare T ½ , Q_L F , Ni FPU Input PED, CLK Give R, r Output

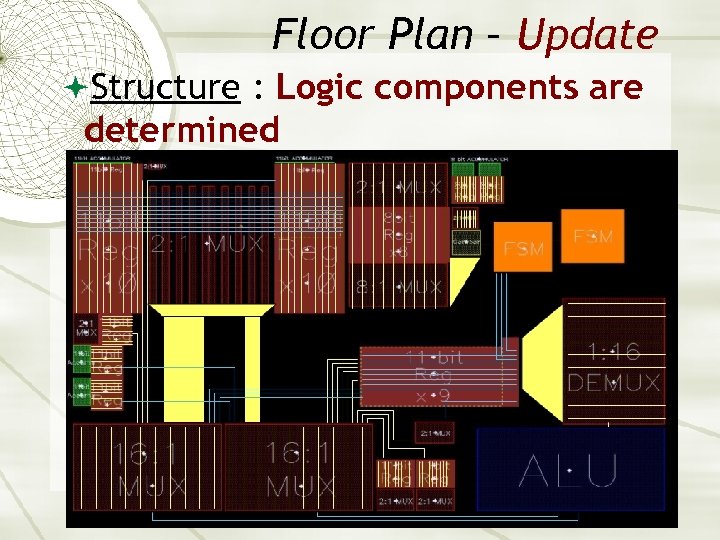

Floor Plan – Update Structure : Logic components are determined

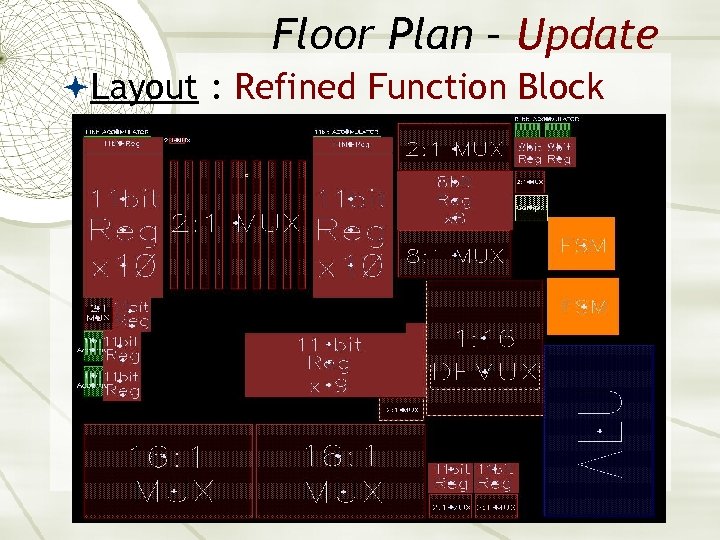

Floor Plan – Update Layout : Refined Function Block

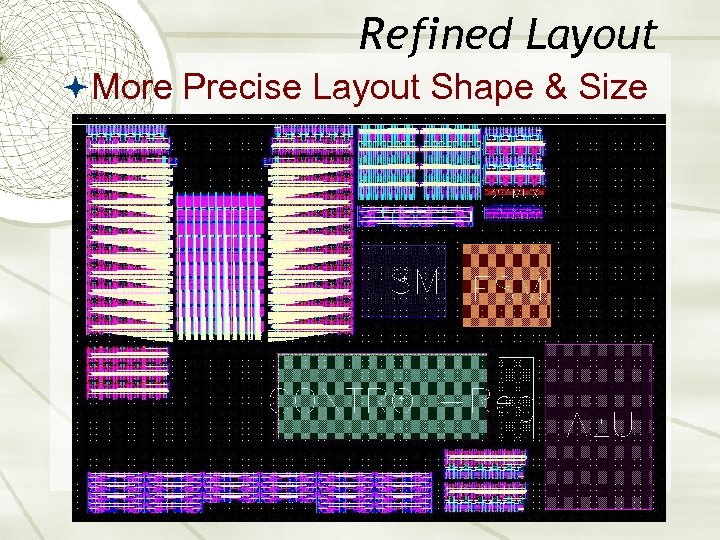

Refined Layout More Precise Layout Shape & Size

More and More

More and More…

Doing Global Routing

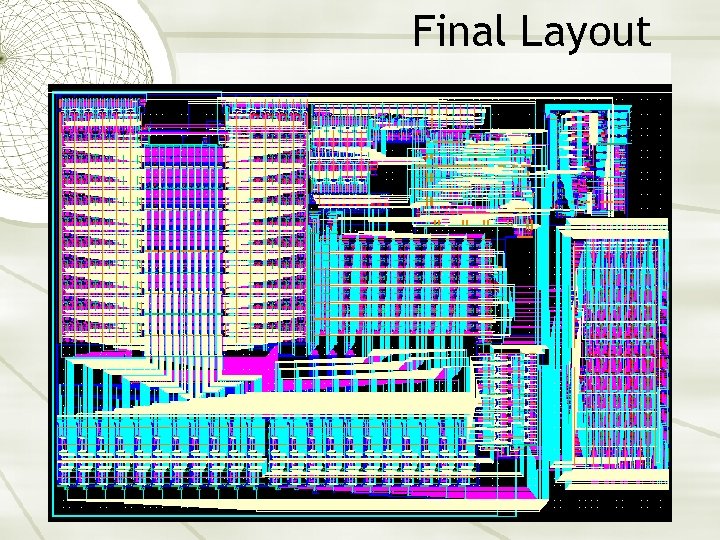

Final Layout

Layout / Verification Chun Han Chen

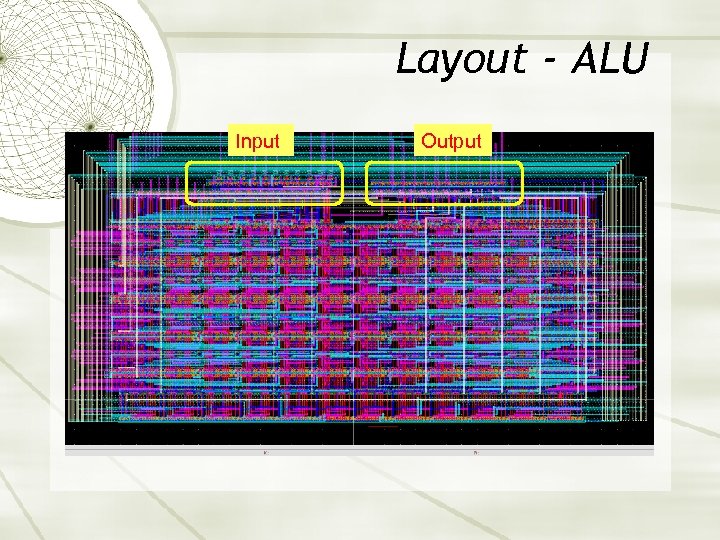

Layout - ALU Input Output

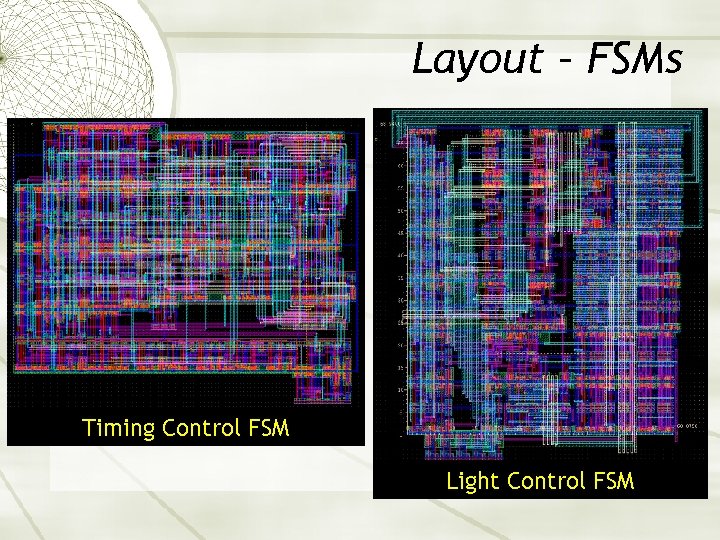

Layout – FSMs Timing Control FSM Light Control FSM

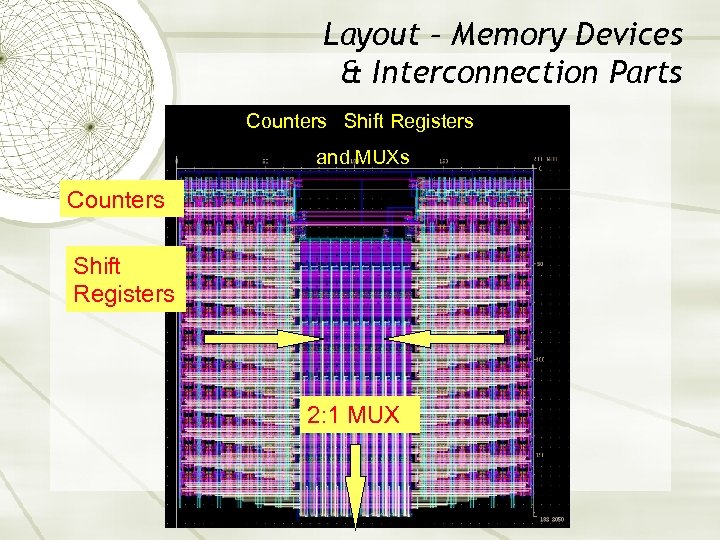

Layout – Memory Devices & Interconnection Parts Counters Shift Registers and MUXs Shift Registers Counters MUX Shift Registers 2: 1 MUX

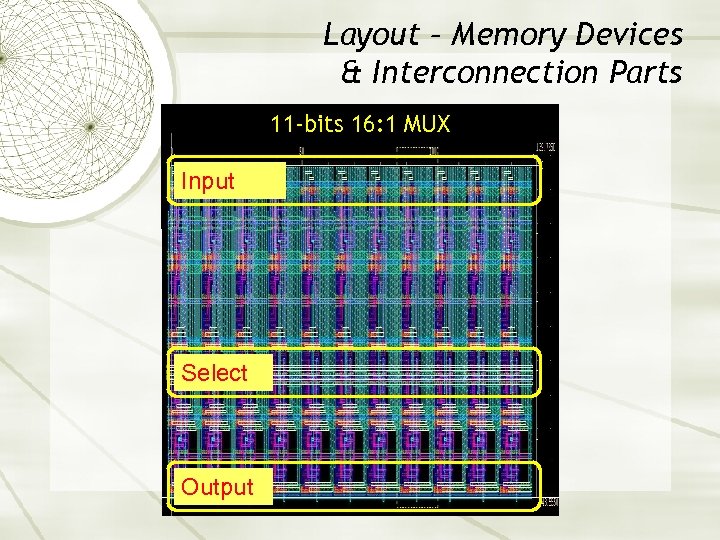

Layout – Memory Devices & Interconnection Parts 11 -bits 16: 1 MUX Input Select Output

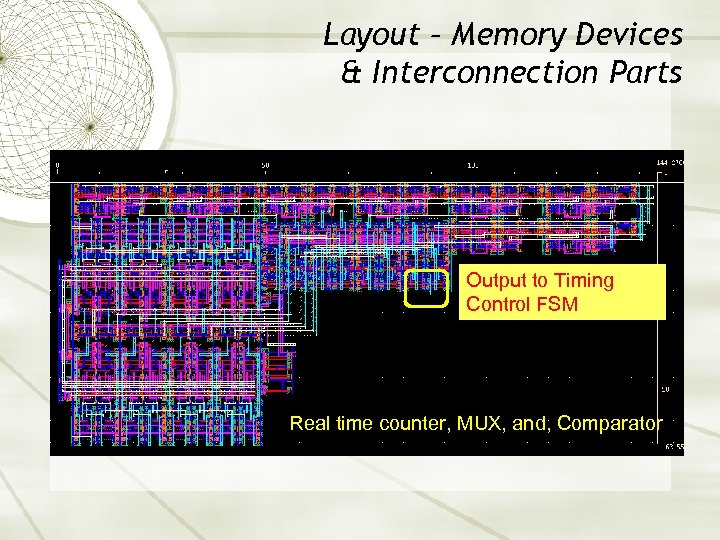

Layout – Memory Devices & Interconnection Parts Output to Timing Control FSM Real time counter, MUX, and, Comparator

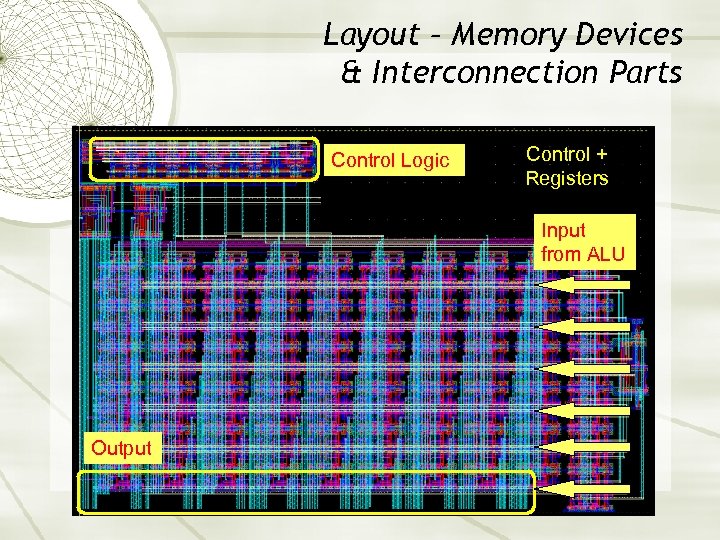

Layout – Memory Devices & Interconnection Parts Control Logic Control + Registers Input from ALU Output

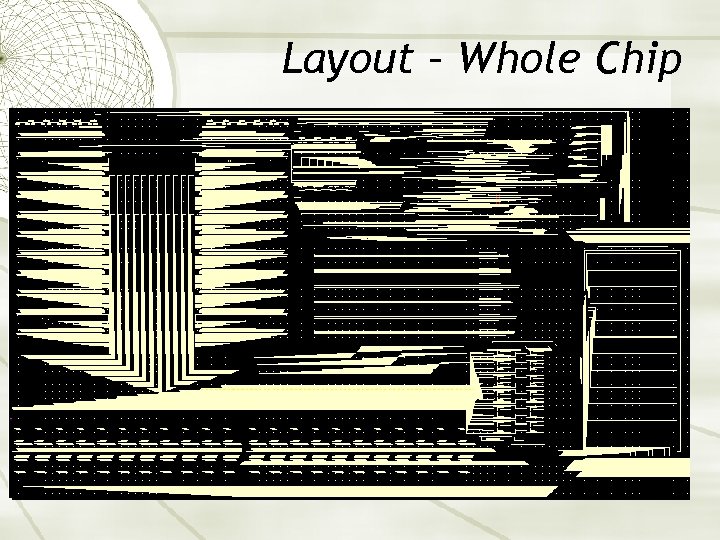

Layout – Whole Chip

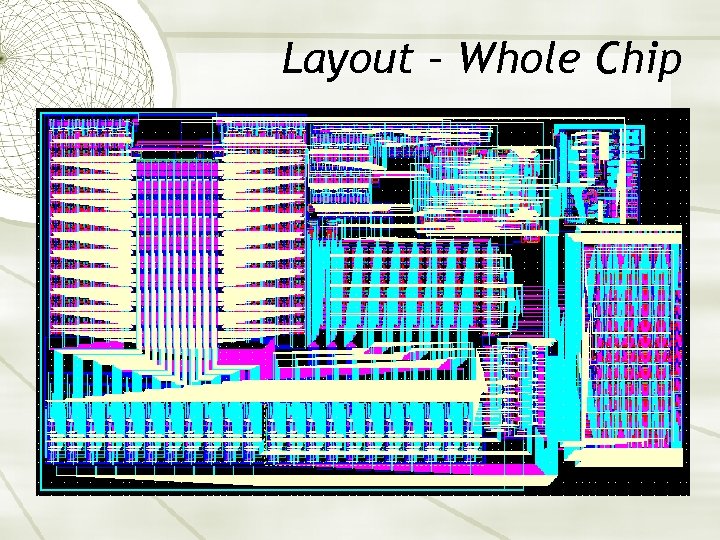

Layout – Whole Chip

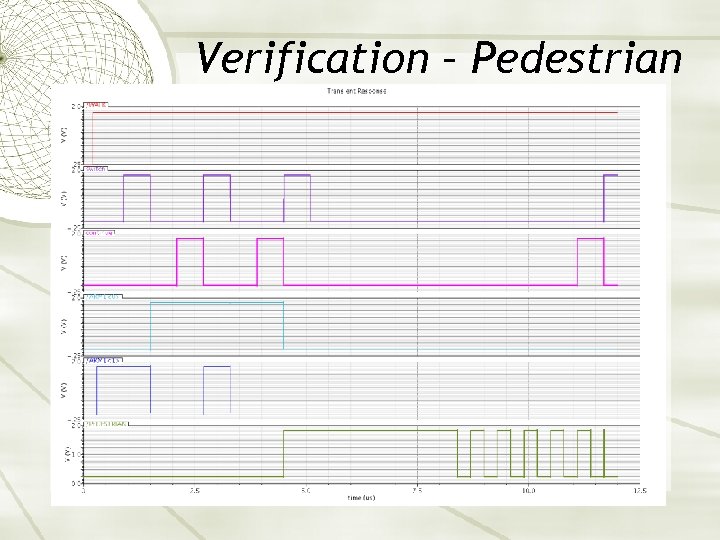

Verification – Methodology Functionality Validation -Java V. S. Behavioral Verilog -Behavioral Verilog V. S. Structural Verilog Schematic Checks -Structure Verilog V. S. Schematic Layout Verification 1. Whole chip extracted RC simulation by using Ultrasim 2. Comparing the results with schematic simulation 3. Separated simulations for pedestrian signal

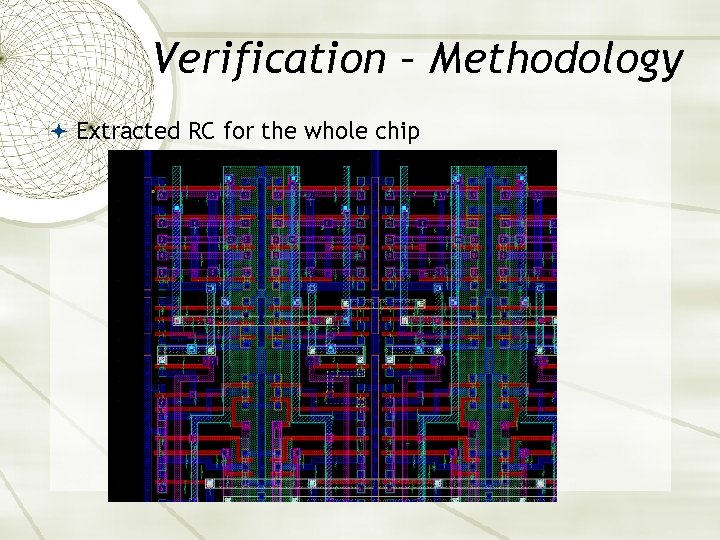

Verification – Methodology Extracted RC for the whole chip

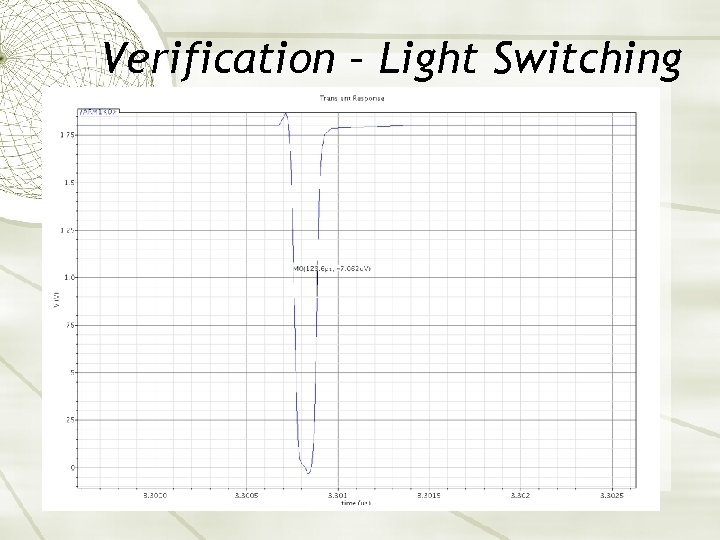

Verification – Light Switching Switch Continue

Verification – Pedestrian

Specification Issues Encountered Timothy Kwan

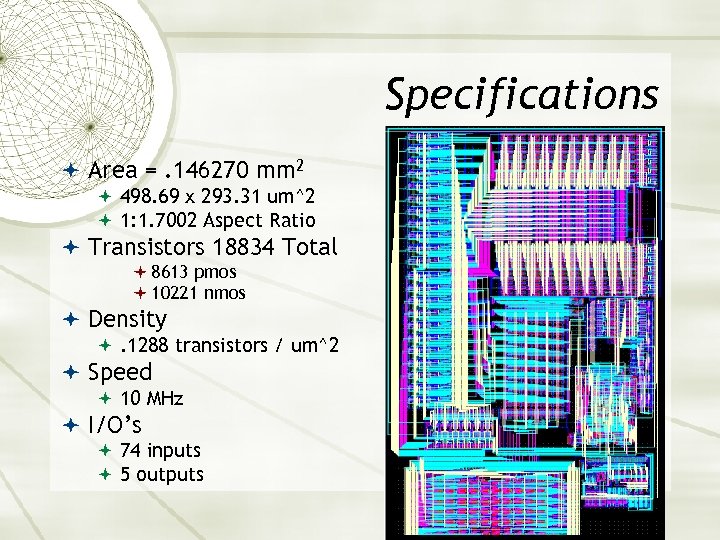

Specifications Area =. 146270 mm 2 498. 69 x 293. 31 um^2 1: 1. 7002 Aspect Ratio Transistors 18834 Total 8613 pmos 10221 nmos Density . 1288 transistors / um^2 Speed 10 MHz I/O’s 74 inputs 5 outputs

Issues Encountered Muxzilla Large consecutive pass transistor muxes Floor plan Increasing number of transistors led to larger blocks 12000 => 18834 Wire Routing Metal Directionality Large Number of Wires I/Os Complicated FSM Logic and glitches

Issues Encountered Large Fan Out in Some Blocks System Clock and Real Time Clock Timing Issues Arithmetic Unit or Floating Point Unit Simulation Issues New vs. Old Cadence Ultrasim vs. Spectre

?

38fbaff5864cd554e5a6ff7447d12ef6.ppt