9c231646b1aff12ec71527d4b6d6514b.ppt

- Количество слайдов: 40

DØSMT DØ Silicon Microstrip Tracker for run. IIa Design Production Assembly Readout Installation Commissioning Conclusions Eric Kajfasz (CPPM/FNAL) - Breese Quinn (FNAL) Como, October 15, 2001 presented by Alice Bean (Kansas/FNAL) Como 2001, 10/15/01 E. Kajfasz/B. Quinn

DØSMT DØ Silicon Microstrip Tracker for run. IIa Design Production Assembly Readout Installation Commissioning Conclusions Eric Kajfasz (CPPM/FNAL) - Breese Quinn (FNAL) Como, October 15, 2001 presented by Alice Bean (Kansas/FNAL) Como 2001, 10/15/01 E. Kajfasz/B. Quinn

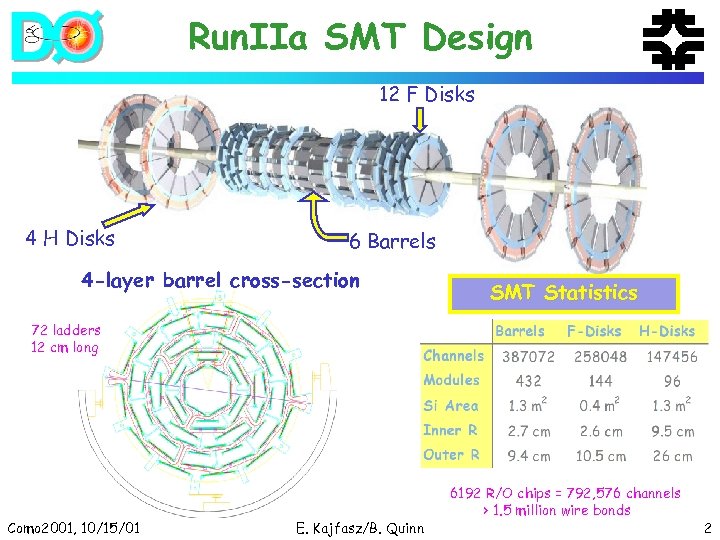

Run. IIa SMT Design 12 F Disks 4 H Disks 6 Barrels 4 -layer barrel cross-section SMT Statistics 72 ladders 12 cm long Como 2001, 10/15/01 E. Kajfasz/B. Quinn 6192 R/O chips = 792, 576 channels > 1. 5 million wire bonds 2

Run. IIa SMT Design 12 F Disks 4 H Disks 6 Barrels 4 -layer barrel cross-section SMT Statistics 72 ladders 12 cm long Como 2001, 10/15/01 E. Kajfasz/B. Quinn 6192 R/O chips = 792, 576 channels > 1. 5 million wire bonds 2

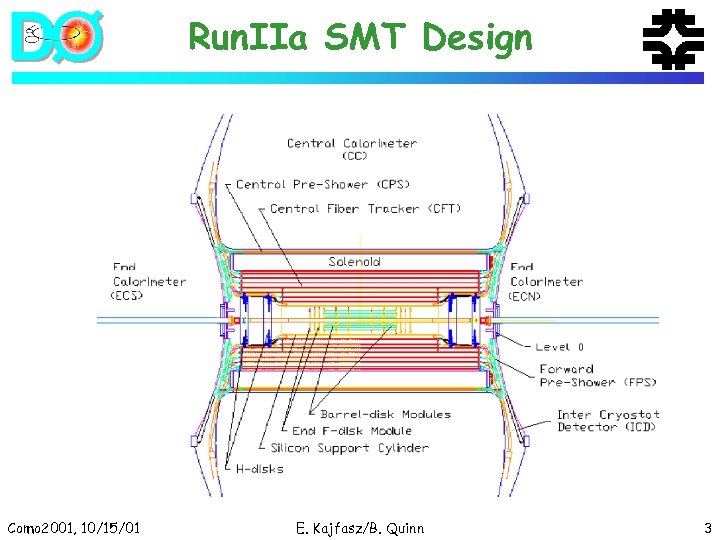

Run. IIa SMT Design Como 2001, 10/15/01 E. Kajfasz/B. Quinn 3

Run. IIa SMT Design Como 2001, 10/15/01 E. Kajfasz/B. Quinn 3

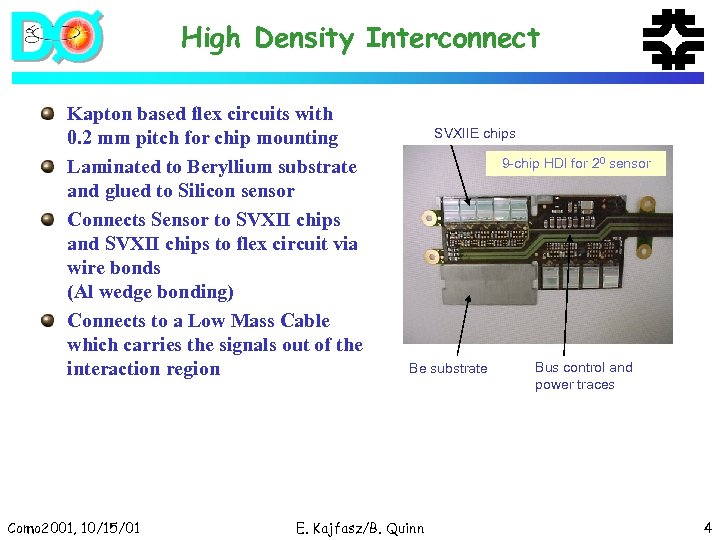

High Density Interconnect Kapton based flex circuits with 0. 2 mm pitch for chip mounting Laminated to Beryllium substrate and glued to Silicon sensor Connects Sensor to SVXII chips and SVXII chips to flex circuit via wire bonds (Al wedge bonding) Connects to a Low Mass Cable which carries the signals out of the interaction region Como 2001, 10/15/01 SVXIIE chips 9 -chip HDI for 20 sensor Be substrate E. Kajfasz/B. Quinn Bus control and power traces 4

High Density Interconnect Kapton based flex circuits with 0. 2 mm pitch for chip mounting Laminated to Beryllium substrate and glued to Silicon sensor Connects Sensor to SVXII chips and SVXII chips to flex circuit via wire bonds (Al wedge bonding) Connects to a Low Mass Cable which carries the signals out of the interaction region Como 2001, 10/15/01 SVXIIE chips 9 -chip HDI for 20 sensor Be substrate E. Kajfasz/B. Quinn Bus control and power traces 4

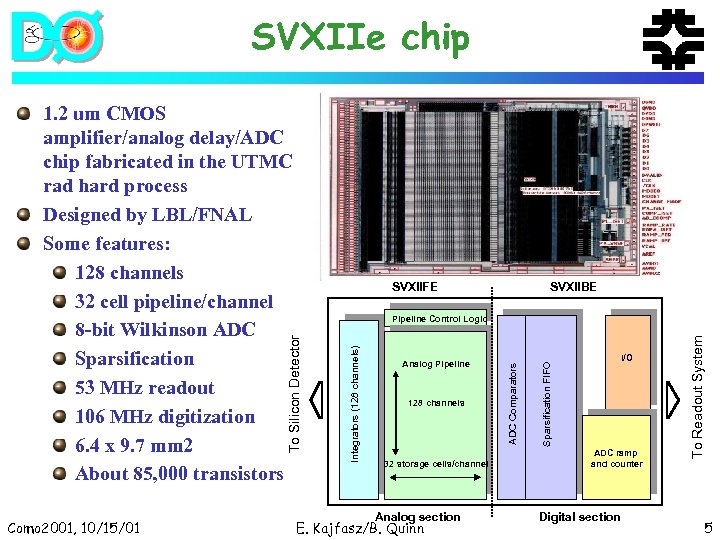

SVXIIe chip SVXIIFE Como 2001, 10/15/01 SVXIIBE 32 storage cells/channel Analog section E. Kajfasz/B. Quinn ADC ramp and counter Digital section To Readout System 128 channels I/O Sparsification FIFO Analog Pipeline ADC Comparators Integrators (128 channels) Pipeline Control Logic To Silicon Detector 1. 2 um CMOS amplifier/analog delay/ADC chip fabricated in the UTMC rad hard process Designed by LBL/FNAL Some features: 128 channels 32 cell pipeline/channel 8 -bit Wilkinson ADC Sparsification 53 MHz readout 106 MHz digitization 6. 4 x 9. 7 mm 2 About 85, 000 transistors 5

SVXIIe chip SVXIIFE Como 2001, 10/15/01 SVXIIBE 32 storage cells/channel Analog section E. Kajfasz/B. Quinn ADC ramp and counter Digital section To Readout System 128 channels I/O Sparsification FIFO Analog Pipeline ADC Comparators Integrators (128 channels) Pipeline Control Logic To Silicon Detector 1. 2 um CMOS amplifier/analog delay/ADC chip fabricated in the UTMC rad hard process Designed by LBL/FNAL Some features: 128 channels 32 cell pipeline/channel 8 -bit Wilkinson ADC Sparsification 53 MHz readout 106 MHz digitization 6. 4 x 9. 7 mm 2 About 85, 000 transistors 5

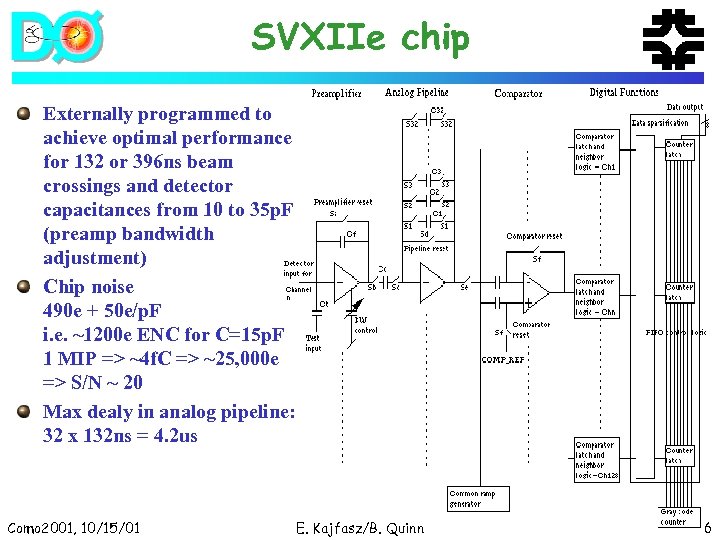

SVXIIe chip Externally programmed to achieve optimal performance for 132 or 396 ns beam crossings and detector capacitances from 10 to 35 p. F (preamp bandwidth adjustment) Chip noise 490 e + 50 e/p. F i. e. ~1200 e ENC for C=15 p. F 1 MIP => ~4 f. C => ~25, 000 e => S/N ~ 20 Max dealy in analog pipeline: 32 x 132 ns = 4. 2 us Como 2001, 10/15/01 E. Kajfasz/B. Quinn 6

SVXIIe chip Externally programmed to achieve optimal performance for 132 or 396 ns beam crossings and detector capacitances from 10 to 35 p. F (preamp bandwidth adjustment) Chip noise 490 e + 50 e/p. F i. e. ~1200 e ENC for C=15 p. F 1 MIP => ~4 f. C => ~25, 000 e => S/N ~ 20 Max dealy in analog pipeline: 32 x 132 ns = 4. 2 us Como 2001, 10/15/01 E. Kajfasz/B. Quinn 6

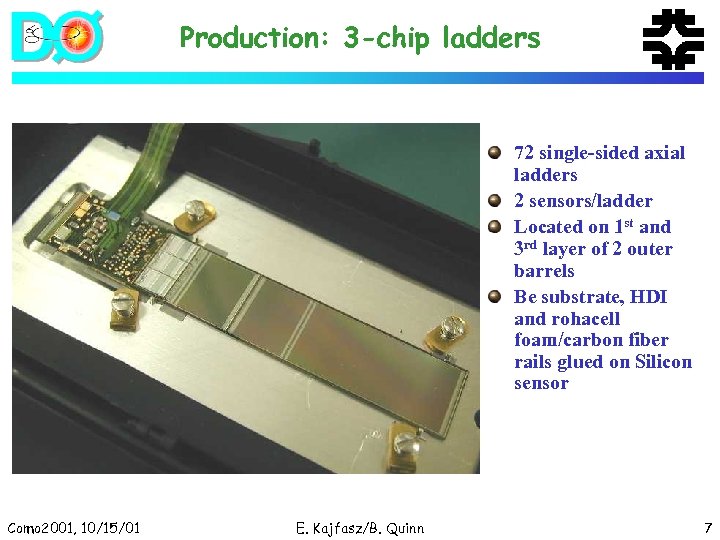

Production: 3 -chip ladders 72 single-sided axial ladders 2 sensors/ladder Located on 1 st and 3 rd layer of 2 outer barrels Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor Como 2001, 10/15/01 E. Kajfasz/B. Quinn 7

Production: 3 -chip ladders 72 single-sided axial ladders 2 sensors/ladder Located on 1 st and 3 rd layer of 2 outer barrels Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor Como 2001, 10/15/01 E. Kajfasz/B. Quinn 7

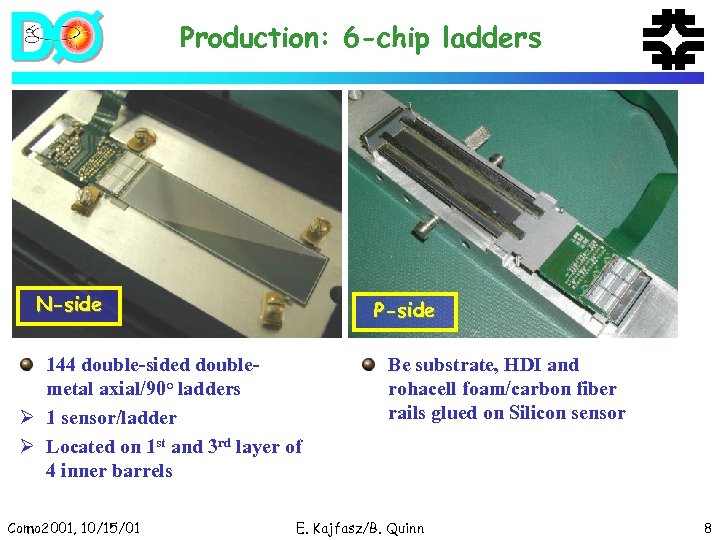

Production: 6 -chip ladders N-side P-side 144 double-sided doublemetal axial/90° ladders Ø 1 sensor/ladder Ø Located on 1 st and 3 rd layer of 4 inner barrels Como 2001, 10/15/01 Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor E. Kajfasz/B. Quinn 8

Production: 6 -chip ladders N-side P-side 144 double-sided doublemetal axial/90° ladders Ø 1 sensor/ladder Ø Located on 1 st and 3 rd layer of 4 inner barrels Como 2001, 10/15/01 Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor E. Kajfasz/B. Quinn 8

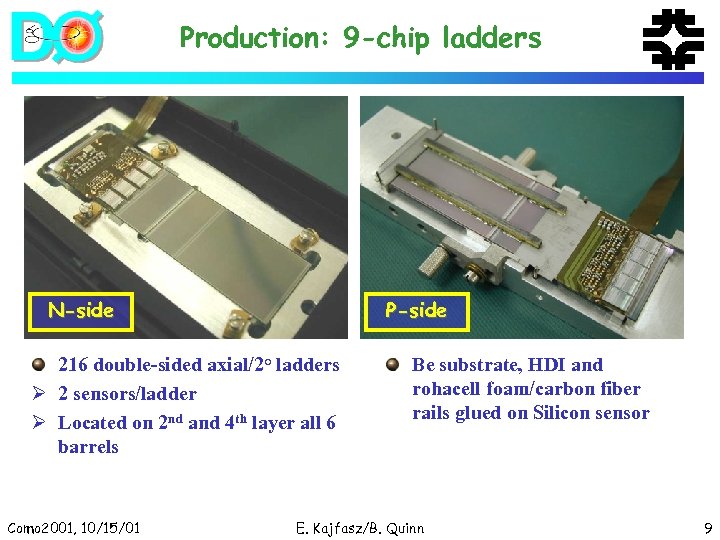

Production: 9 -chip ladders N-side P-side 216 double-sided axial/2° ladders Ø 2 sensors/ladder Ø Located on 2 nd and 4 th layer all 6 barrels Como 2001, 10/15/01 Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor E. Kajfasz/B. Quinn 9

Production: 9 -chip ladders N-side P-side 216 double-sided axial/2° ladders Ø 2 sensors/ladder Ø Located on 2 nd and 4 th layer all 6 barrels Como 2001, 10/15/01 Be substrate, HDI and rohacell foam/carbon fiber rails glued on Silicon sensor E. Kajfasz/B. Quinn 9

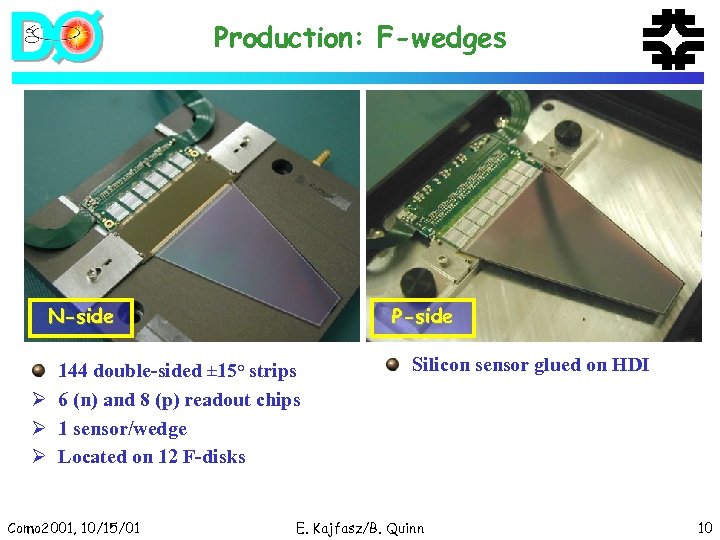

Production: F-wedges N-side P-side 144 double-sided ± 15° strips Ø 6 (n) and 8 (p) readout chips Ø 1 sensor/wedge Ø Located on 12 F-disks Como 2001, 10/15/01 Silicon sensor glued on HDI E. Kajfasz/B. Quinn 10

Production: F-wedges N-side P-side 144 double-sided ± 15° strips Ø 6 (n) and 8 (p) readout chips Ø 1 sensor/wedge Ø Located on 12 F-disks Como 2001, 10/15/01 Silicon sensor glued on HDI E. Kajfasz/B. Quinn 10

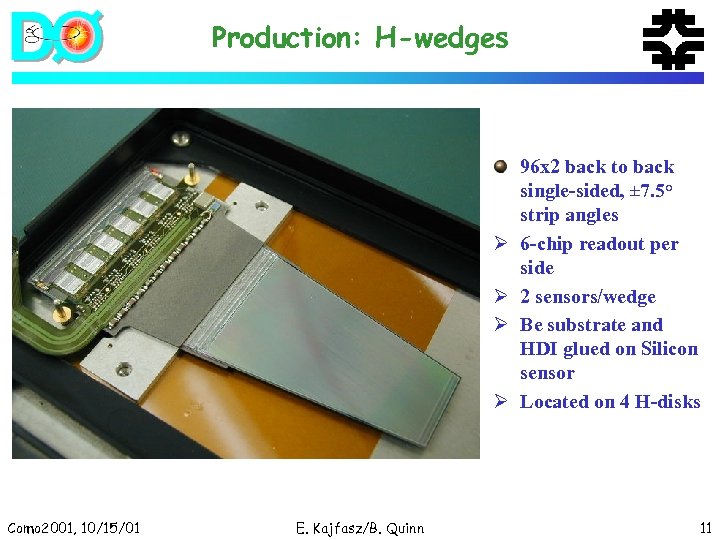

Production: H-wedges Ø Ø Como 2001, 10/15/01 E. Kajfasz/B. Quinn 96 x 2 back to back single-sided, ± 7. 5° strip angles 6 -chip readout per side 2 sensors/wedge Be substrate and HDI glued on Silicon sensor Located on 4 H-disks 11

Production: H-wedges Ø Ø Como 2001, 10/15/01 E. Kajfasz/B. Quinn 96 x 2 back to back single-sided, ± 7. 5° strip angles 6 -chip readout per side 2 sensors/wedge Be substrate and HDI glued on Silicon sensor Located on 4 H-disks 11

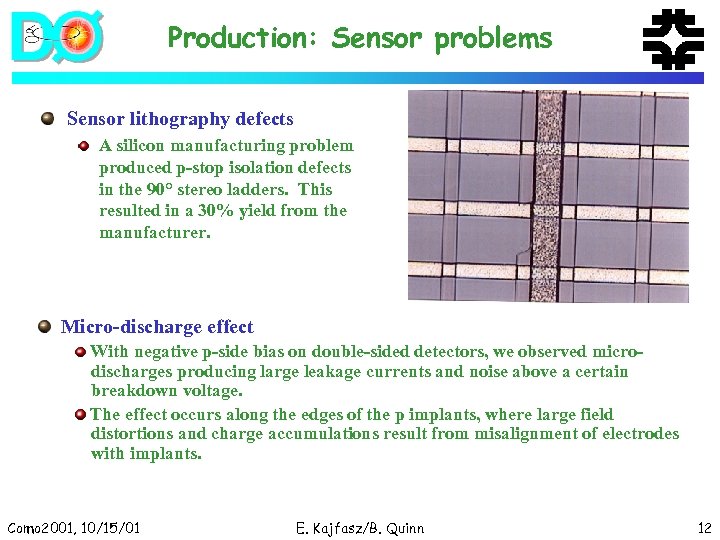

Production: Sensor problems Sensor lithography defects A silicon manufacturing problem produced p-stop isolation defects in the 90° stereo ladders. This resulted in a 30% yield from the manufacturer. Micro-discharge effect With negative p-side bias on double-sided detectors, we observed microdischarges producing large leakage currents and noise above a certain breakdown voltage. The effect occurs along the edges of the p implants, where large field distortions and charge accumulations result from misalignment of electrodes with implants. Como 2001, 10/15/01 E. Kajfasz/B. Quinn 12

Production: Sensor problems Sensor lithography defects A silicon manufacturing problem produced p-stop isolation defects in the 90° stereo ladders. This resulted in a 30% yield from the manufacturer. Micro-discharge effect With negative p-side bias on double-sided detectors, we observed microdischarges producing large leakage currents and noise above a certain breakdown voltage. The effect occurs along the edges of the p implants, where large field distortions and charge accumulations result from misalignment of electrodes with implants. Como 2001, 10/15/01 E. Kajfasz/B. Quinn 12

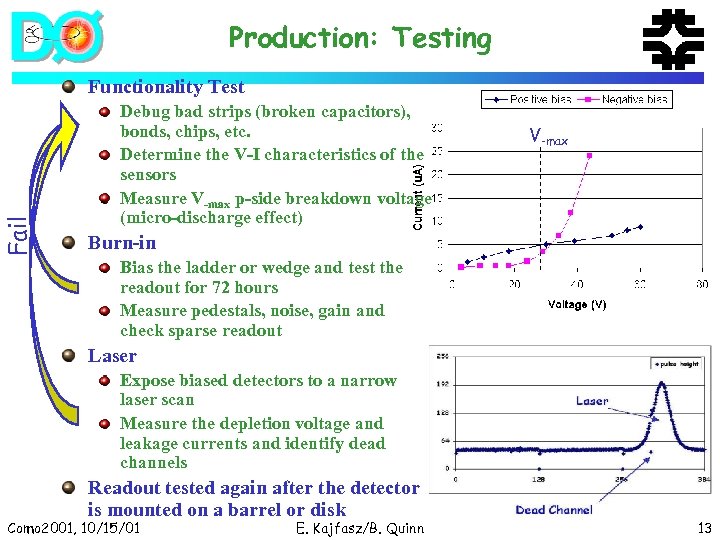

Production: Testing Fail Functionality Test Debug bad strips (broken capacitors), bonds, chips, etc. Determine the V-I characteristics of the sensors Measure V-max p-side breakdown voltage (micro-discharge effect) V-max Burn-in Bias the ladder or wedge and test the readout for 72 hours Measure pedestals, noise, gain and check sparse readout Laser Expose biased detectors to a narrow laser scan Measure the depletion voltage and leakage currents and identify dead channels Readout tested again after the detector is mounted on a barrel or disk Como 2001, 10/15/01 E. Kajfasz/B. Quinn 13

Production: Testing Fail Functionality Test Debug bad strips (broken capacitors), bonds, chips, etc. Determine the V-I characteristics of the sensors Measure V-max p-side breakdown voltage (micro-discharge effect) V-max Burn-in Bias the ladder or wedge and test the readout for 72 hours Measure pedestals, noise, gain and check sparse readout Laser Expose biased detectors to a narrow laser scan Measure the depletion voltage and leakage currents and identify dead channels Readout tested again after the detector is mounted on a barrel or disk Como 2001, 10/15/01 E. Kajfasz/B. Quinn 13

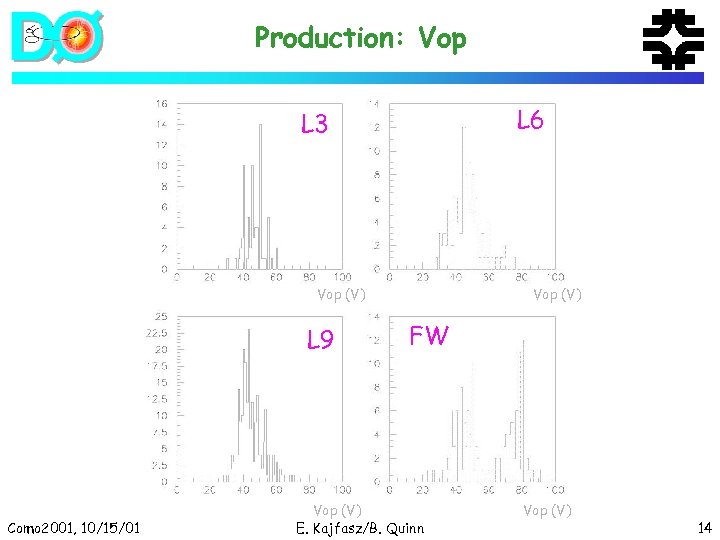

Production: Vop L 6 L 3 Vop (V) L 9 Como 2001, 10/15/01 Vop (V) FW Vop (V) E. Kajfasz/B. Quinn Vop (V) 14

Production: Vop L 6 L 3 Vop (V) L 9 Como 2001, 10/15/01 Vop (V) FW Vop (V) E. Kajfasz/B. Quinn Vop (V) 14

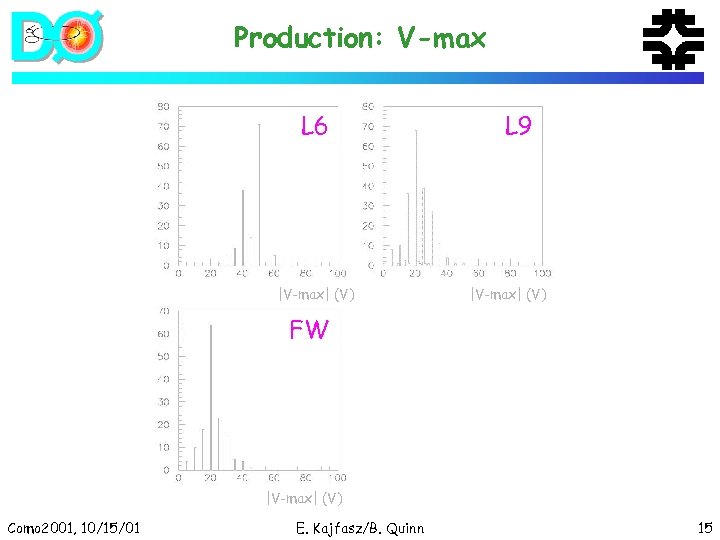

Production: V-max L 6 |V-max| (V) L 9 |V-max| (V) FW |V-max| (V) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 15

Production: V-max L 6 |V-max| (V) L 9 |V-max| (V) FW |V-max| (V) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 15

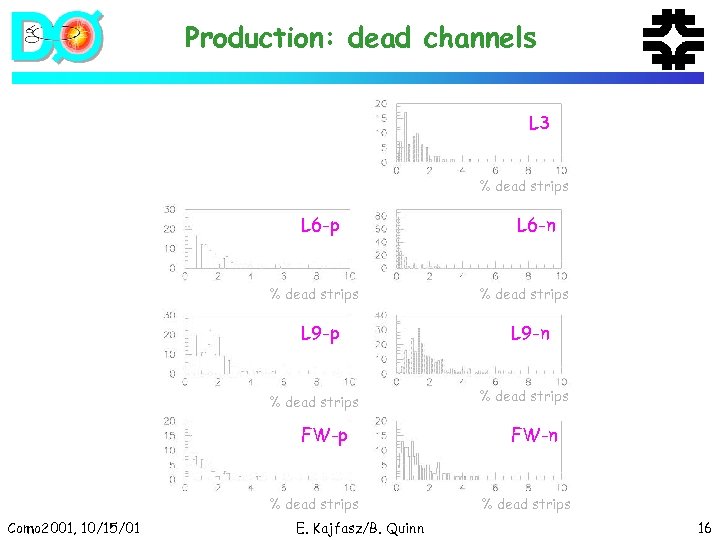

Production: dead channels L 3 % dead strips L 6 -p % dead strips L 9 -p % dead strips FW-p % dead strips Como 2001, 10/15/01 E. Kajfasz/B. Quinn L 6 -n % dead strips L 9 -n % dead strips FW-n % dead strips 16

Production: dead channels L 3 % dead strips L 6 -p % dead strips L 9 -p % dead strips FW-p % dead strips Como 2001, 10/15/01 E. Kajfasz/B. Quinn L 6 -n % dead strips L 9 -n % dead strips FW-n % dead strips 16

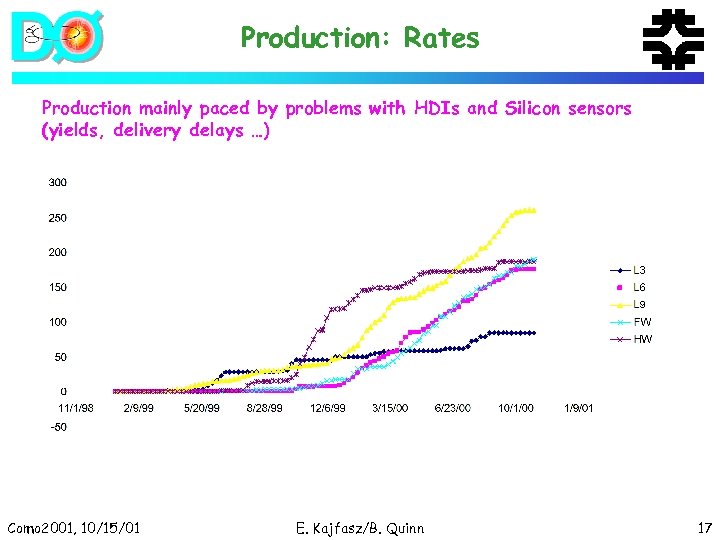

Production: Rates Production mainly paced by problems with HDIs and Silicon sensors (yields, delivery delays …) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 17

Production: Rates Production mainly paced by problems with HDIs and Silicon sensors (yields, delivery delays …) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 17

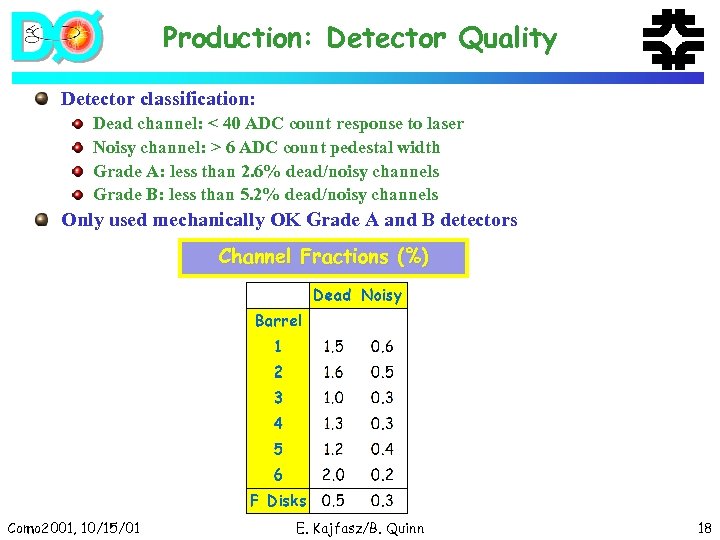

Production: Detector Quality Detector classification: Dead channel: < 40 ADC count response to laser Noisy channel: > 6 ADC count pedestal width Grade A: less than 2. 6% dead/noisy channels Grade B: less than 5. 2% dead/noisy channels Only used mechanically OK Grade A and B detectors Channel Fractions (%) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 18

Production: Detector Quality Detector classification: Dead channel: < 40 ADC count response to laser Noisy channel: > 6 ADC count pedestal width Grade A: less than 2. 6% dead/noisy channels Grade B: less than 5. 2% dead/noisy channels Only used mechanically OK Grade A and B detectors Channel Fractions (%) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 18

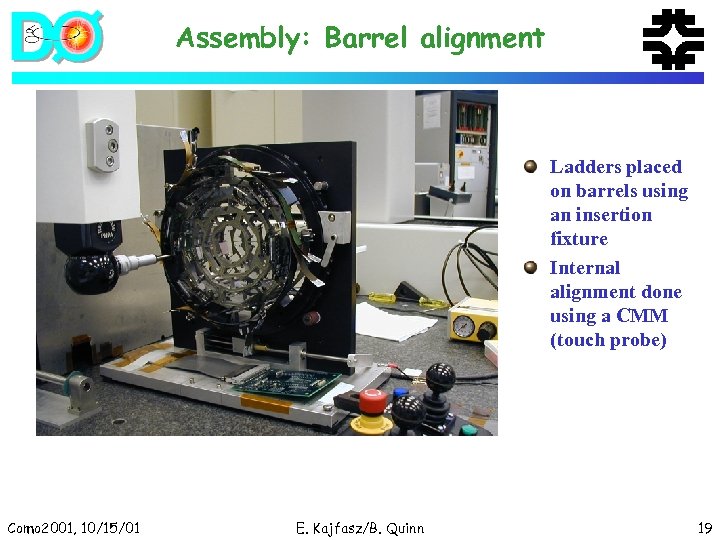

Assembly: Barrel alignment Ladders placed on barrels using an insertion fixture Internal alignment done using a CMM (touch probe) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 19

Assembly: Barrel alignment Ladders placed on barrels using an insertion fixture Internal alignment done using a CMM (touch probe) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 19

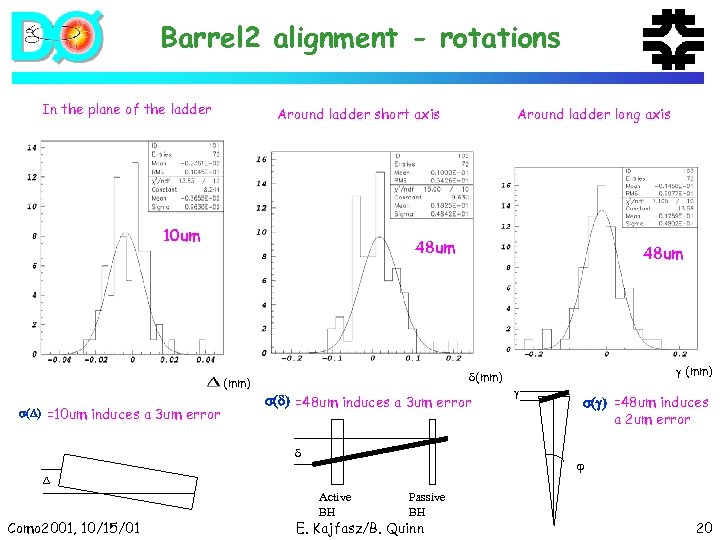

Barrel 2 alignment - rotations In the plane of the ladder Around ladder short axis 10 um 48 um s(d) =48 um induces a 3 um error (mm) s(g) =48 um induces a 2 um error Como 2001, 10/15/01 48 um (mm) s( ) =10 um induces a 3 um error Around ladder long axis Active BH Passive BH E. Kajfasz/B. Quinn 20

Barrel 2 alignment - rotations In the plane of the ladder Around ladder short axis 10 um 48 um s(d) =48 um induces a 3 um error (mm) s(g) =48 um induces a 2 um error Como 2001, 10/15/01 48 um (mm) s( ) =10 um induces a 3 um error Around ladder long axis Active BH Passive BH E. Kajfasz/B. Quinn 20

Assembly: Barrel-Fdisk mating Como 2001, 10/15/01 E. Kajfasz/B. Quinn 21

Assembly: Barrel-Fdisk mating Como 2001, 10/15/01 E. Kajfasz/B. Quinn 21

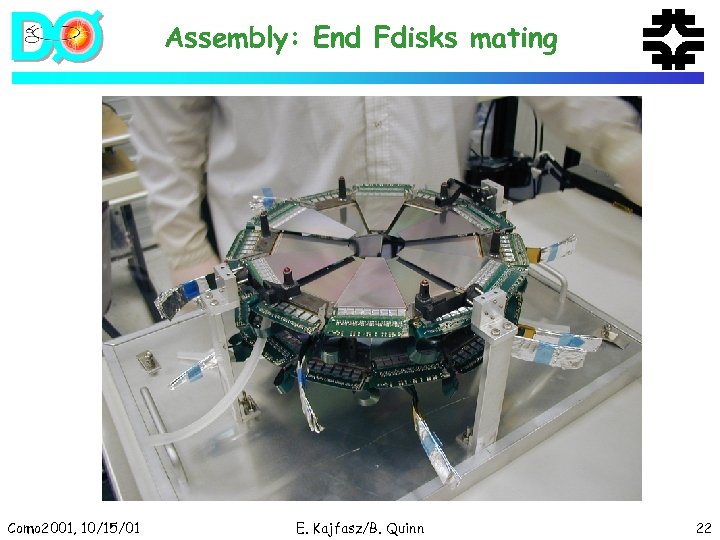

Assembly: End Fdisks mating Como 2001, 10/15/01 E. Kajfasz/B. Quinn 22

Assembly: End Fdisks mating Como 2001, 10/15/01 E. Kajfasz/B. Quinn 22

Assembly: Hdisk Como 2001, 10/15/01 E. Kajfasz/B. Quinn 23

Assembly: Hdisk Como 2001, 10/15/01 E. Kajfasz/B. Quinn 23

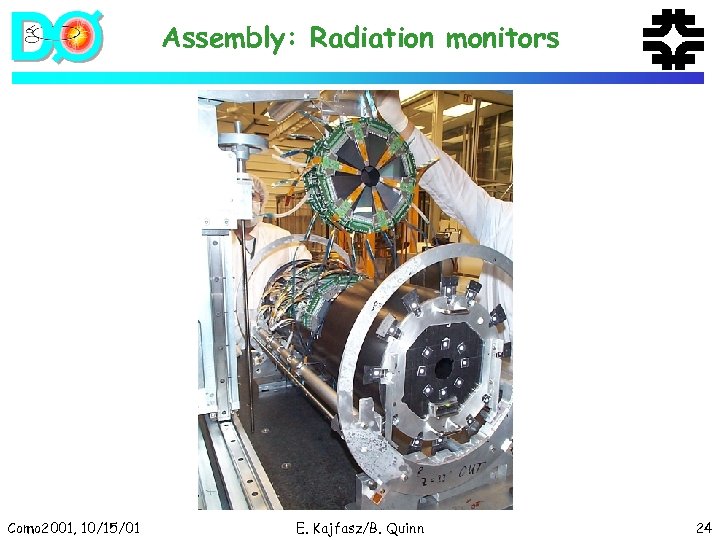

Assembly: Radiation monitors Como 2001, 10/15/01 E. Kajfasz/B. Quinn 24

Assembly: Radiation monitors Como 2001, 10/15/01 E. Kajfasz/B. Quinn 24

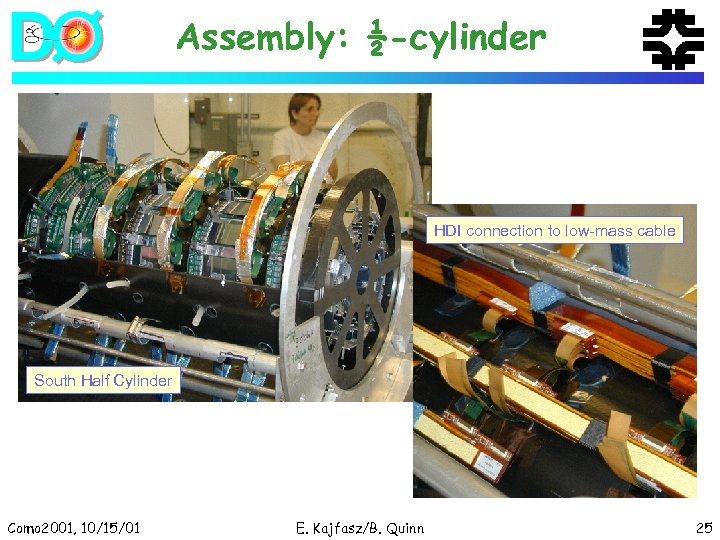

Assembly: ½-cylinder HDI connection to low-mass cable South Half Cylinder Como 2001, 10/15/01 E. Kajfasz/B. Quinn 25

Assembly: ½-cylinder HDI connection to low-mass cable South Half Cylinder Como 2001, 10/15/01 E. Kajfasz/B. Quinn 25

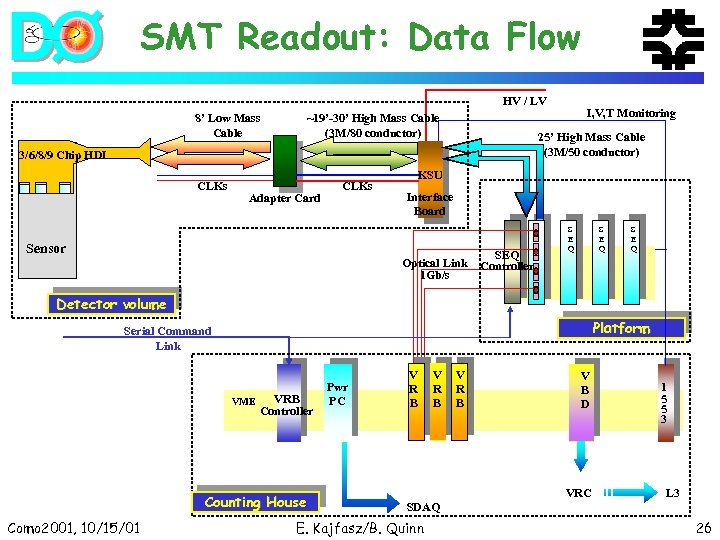

SMT Readout: Data Flow HV / LV 8’ Low Mass Cable ~19’-30’ High Mass Cable (3 M/80 conductor) 25’ High Mass Cable (3 M/50 conductor) 3/6/8/9 Chip HDI CLKs Adapter Card CLKs I, V, T Monitoring KSU Interface Board Sensor Optical Link 1 Gb/s SEQ Controller S E Q Detector volume Platform Serial Command Link VRB VME Controller Counting House Como 2001, 10/15/01 Pwr PC V R B SDAQ E. Kajfasz/B. Quinn V R B V B D VRC 1 5 5 3 L 3 26

SMT Readout: Data Flow HV / LV 8’ Low Mass Cable ~19’-30’ High Mass Cable (3 M/80 conductor) 25’ High Mass Cable (3 M/50 conductor) 3/6/8/9 Chip HDI CLKs Adapter Card CLKs I, V, T Monitoring KSU Interface Board Sensor Optical Link 1 Gb/s SEQ Controller S E Q Detector volume Platform Serial Command Link VRB VME Controller Counting House Como 2001, 10/15/01 Pwr PC V R B SDAQ E. Kajfasz/B. Quinn V R B V B D VRC 1 5 5 3 L 3 26

SMT Readout: Electronics Interface Boards 8 crates (144 boards) located inside the detector volume Regenerates signals SVX monitoring and power management Bias voltage distribution Como 2001, 10/15/01 SEQuencers 6 crates (120 boards) located on the detector platform Use SVX control lines to actuate acquisition, digitization and readout Convert SVX data to optical signals E. Kajfasz/B. Quinn VRBs (VME Readout Buffers) 12 crates (120 boards) located in counting house Data buffer pending L 2 trigger decision Input @ 5 -10 k. Hz L 1 accept rate ~ 50 Mb/s/channel Output @ 1 k. Hz L 2 accept rate ~ 50 Mb/s 27

SMT Readout: Electronics Interface Boards 8 crates (144 boards) located inside the detector volume Regenerates signals SVX monitoring and power management Bias voltage distribution Como 2001, 10/15/01 SEQuencers 6 crates (120 boards) located on the detector platform Use SVX control lines to actuate acquisition, digitization and readout Convert SVX data to optical signals E. Kajfasz/B. Quinn VRBs (VME Readout Buffers) 12 crates (120 boards) located in counting house Data buffer pending L 2 trigger decision Input @ 5 -10 k. Hz L 1 accept rate ~ 50 Mb/s/channel Output @ 1 k. Hz L 2 accept rate ~ 50 Mb/s 27

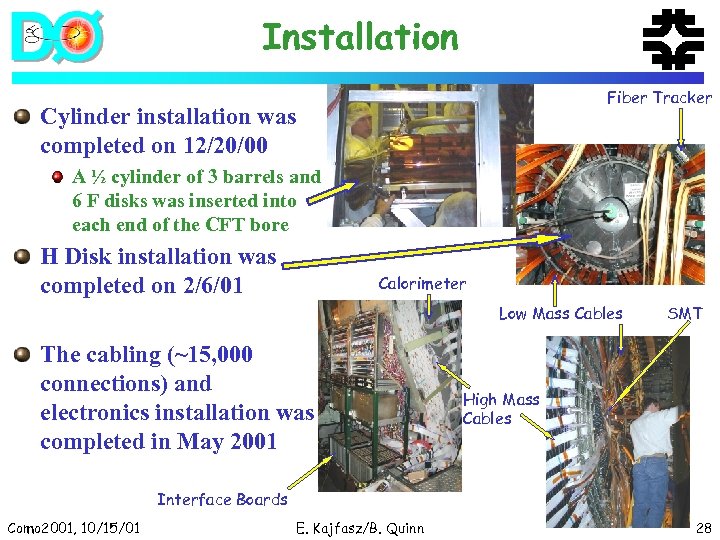

Installation Fiber Tracker Cylinder installation was completed on 12/20/00 A ½ cylinder of 3 barrels and 6 F disks was inserted into each end of the CFT bore H Disk installation was completed on 2/6/01 Calorimeter Low Mass Cables The cabling (~15, 000 connections) and electronics installation was completed in May 2001 SMT High Mass Cables Interface Boards Como 2001, 10/15/01 E. Kajfasz/B. Quinn 28

Installation Fiber Tracker Cylinder installation was completed on 12/20/00 A ½ cylinder of 3 barrels and 6 F disks was inserted into each end of the CFT bore H Disk installation was completed on 2/6/01 Calorimeter Low Mass Cables The cabling (~15, 000 connections) and electronics installation was completed in May 2001 SMT High Mass Cables Interface Boards Como 2001, 10/15/01 E. Kajfasz/B. Quinn 28

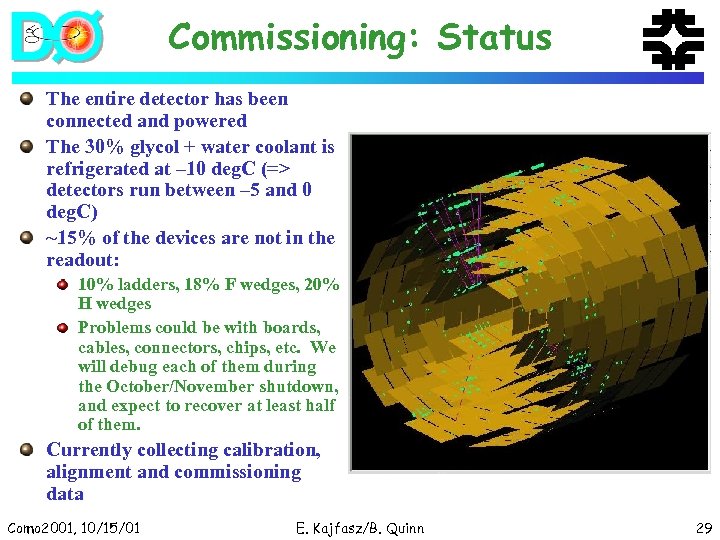

Commissioning: Status The entire detector has been connected and powered The 30% glycol + water coolant is refrigerated at – 10 deg. C (=> detectors run between – 5 and 0 deg. C) ~15% of the devices are not in the readout: 10% ladders, 18% F wedges, 20% H wedges Problems could be with boards, cables, connectors, chips, etc. We will debug each of them during the October/November shutdown, and expect to recover at least half of them. Currently collecting calibration, alignment and commissioning data Como 2001, 10/15/01 E. Kajfasz/B. Quinn 29

Commissioning: Status The entire detector has been connected and powered The 30% glycol + water coolant is refrigerated at – 10 deg. C (=> detectors run between – 5 and 0 deg. C) ~15% of the devices are not in the readout: 10% ladders, 18% F wedges, 20% H wedges Problems could be with boards, cables, connectors, chips, etc. We will debug each of them during the October/November shutdown, and expect to recover at least half of them. Currently collecting calibration, alignment and commissioning data Como 2001, 10/15/01 E. Kajfasz/B. Quinn 29

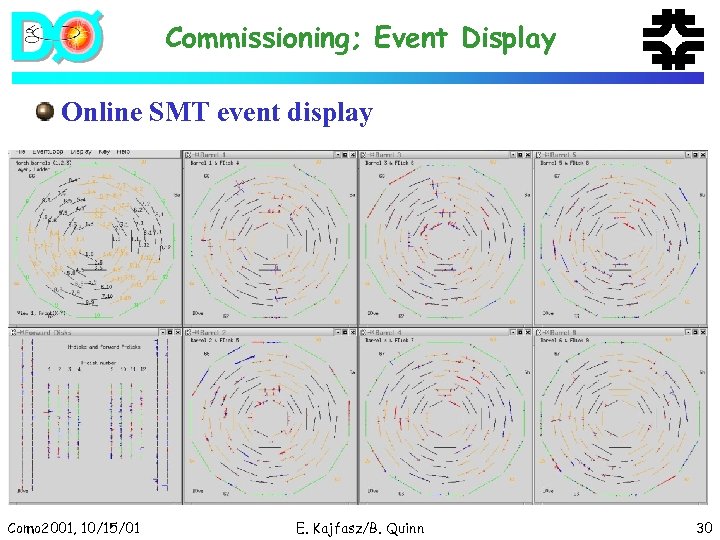

Commissioning; Event Display Online SMT event display Como 2001, 10/15/01 E. Kajfasz/B. Quinn 30

Commissioning; Event Display Online SMT event display Como 2001, 10/15/01 E. Kajfasz/B. Quinn 30

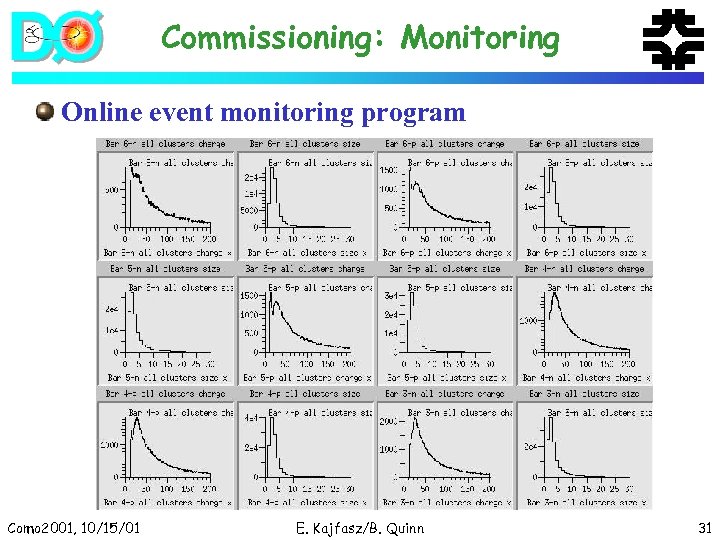

Commissioning: Monitoring Online event monitoring program Como 2001, 10/15/01 E. Kajfasz/B. Quinn 31

Commissioning: Monitoring Online event monitoring program Como 2001, 10/15/01 E. Kajfasz/B. Quinn 31

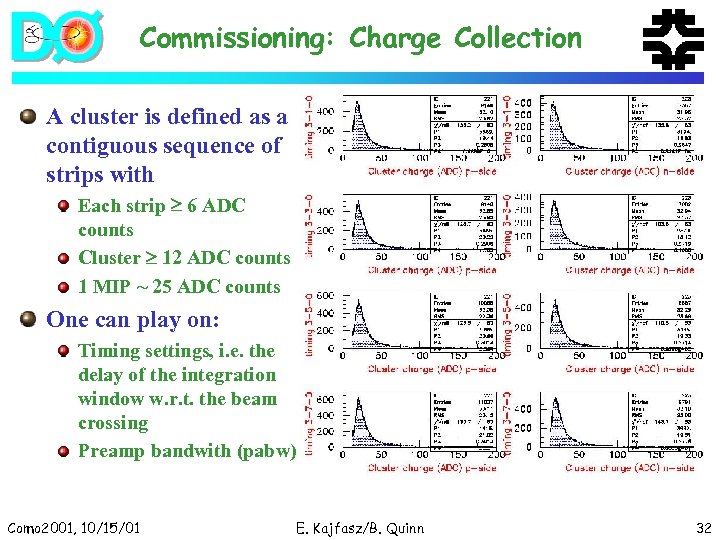

Commissioning: Charge Collection A cluster is defined as a contiguous sequence of strips with Each strip 6 ADC counts Cluster 12 ADC counts 1 MIP ~ 25 ADC counts One can play on: Timing settings, i. e. the delay of the integration window w. r. t. the beam crossing Preamp bandwith (pabw) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 32

Commissioning: Charge Collection A cluster is defined as a contiguous sequence of strips with Each strip 6 ADC counts Cluster 12 ADC counts 1 MIP ~ 25 ADC counts One can play on: Timing settings, i. e. the delay of the integration window w. r. t. the beam crossing Preamp bandwith (pabw) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 32

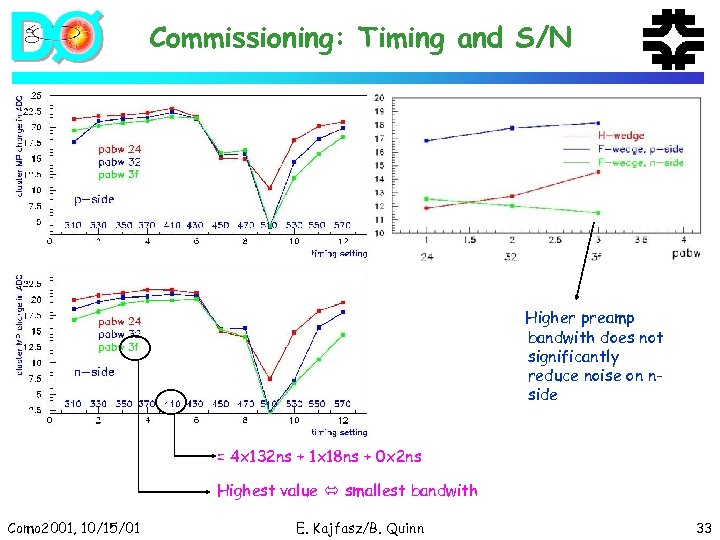

Commissioning: Timing and S/N Higher preamp bandwith does not significantly reduce noise on nside = 4 x 132 ns + 1 x 18 ns + 0 x 2 ns Highest value smallest bandwith Como 2001, 10/15/01 E. Kajfasz/B. Quinn 33

Commissioning: Timing and S/N Higher preamp bandwith does not significantly reduce noise on nside = 4 x 132 ns + 1 x 18 ns + 0 x 2 ns Highest value smallest bandwith Como 2001, 10/15/01 E. Kajfasz/B. Quinn 33

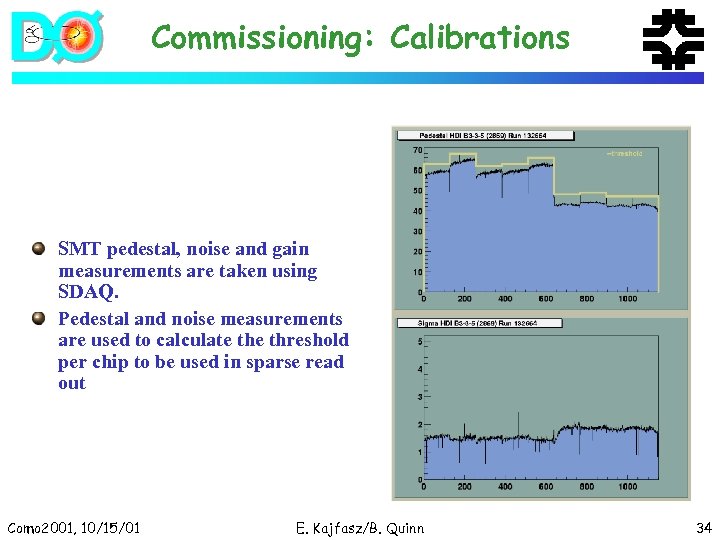

Commissioning: Calibrations SMT pedestal, noise and gain measurements are taken using SDAQ. Pedestal and noise measurements are used to calculate threshold per chip to be used in sparse read out Como 2001, 10/15/01 E. Kajfasz/B. Quinn 34

Commissioning: Calibrations SMT pedestal, noise and gain measurements are taken using SDAQ. Pedestal and noise measurements are used to calculate threshold per chip to be used in sparse read out Como 2001, 10/15/01 E. Kajfasz/B. Quinn 34

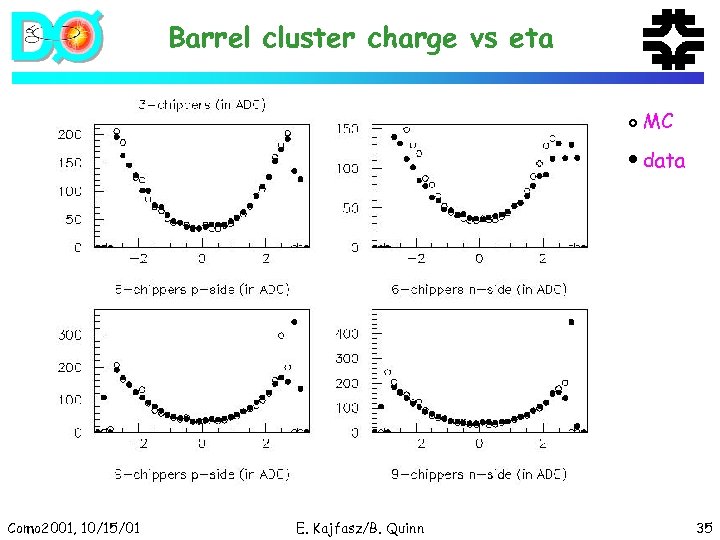

Barrel cluster charge vs eta MC data Como 2001, 10/15/01 E. Kajfasz/B. Quinn 35

Barrel cluster charge vs eta MC data Como 2001, 10/15/01 E. Kajfasz/B. Quinn 35

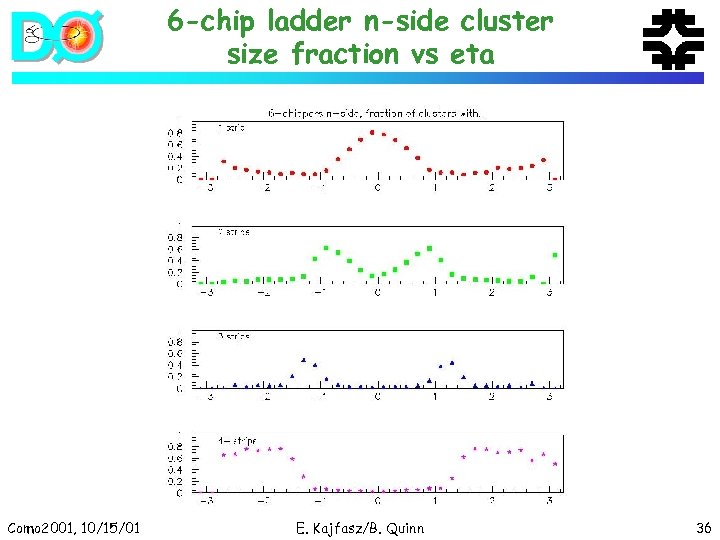

6 -chip ladder n-side cluster size fraction vs eta Como 2001, 10/15/01 E. Kajfasz/B. Quinn 36

6 -chip ladder n-side cluster size fraction vs eta Como 2001, 10/15/01 E. Kajfasz/B. Quinn 36

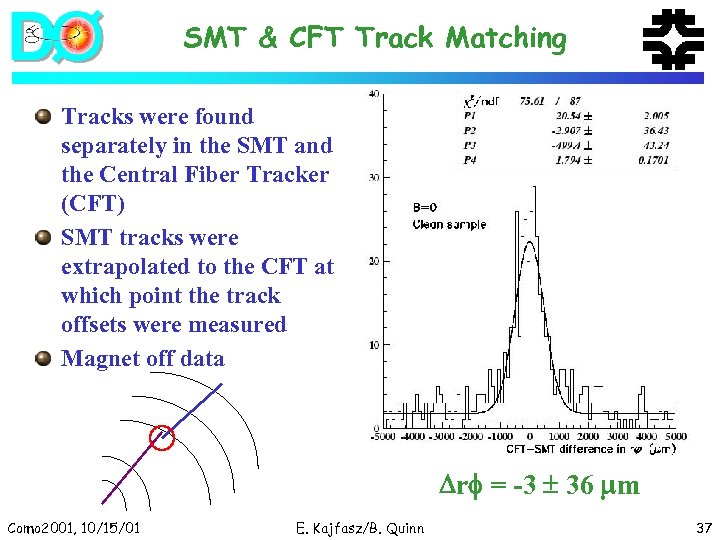

SMT & CFT Track Matching Tracks were found separately in the SMT and the Central Fiber Tracker (CFT) SMT tracks were extrapolated to the CFT at which point the track offsets were measured Magnet off data r = -3 36 m Como 2001, 10/15/01 E. Kajfasz/B. Quinn 37

SMT & CFT Track Matching Tracks were found separately in the SMT and the Central Fiber Tracker (CFT) SMT tracks were extrapolated to the CFT at which point the track offsets were measured Magnet off data r = -3 36 m Como 2001, 10/15/01 E. Kajfasz/B. Quinn 37

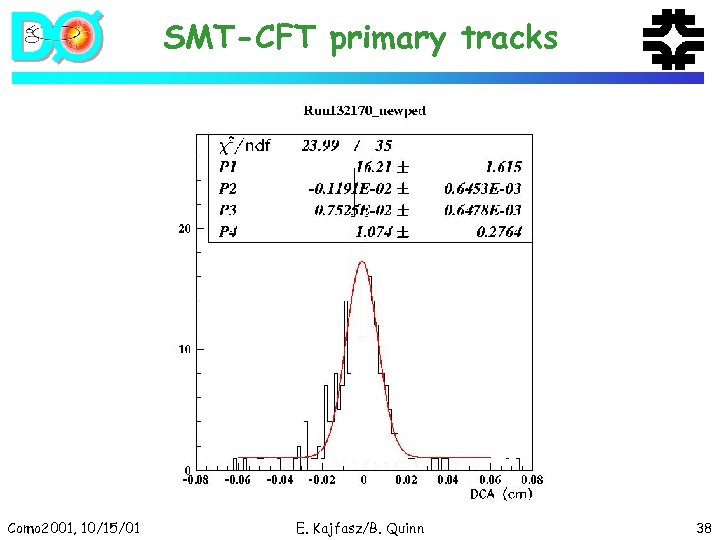

SMT-CFT primary tracks Como 2001, 10/15/01 E. Kajfasz/B. Quinn 38

SMT-CFT primary tracks Como 2001, 10/15/01 E. Kajfasz/B. Quinn 38

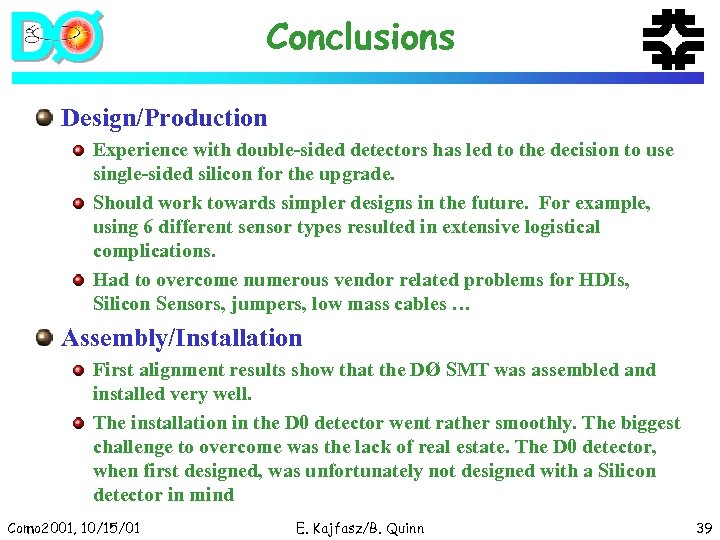

Conclusions Design/Production Experience with double-sided detectors has led to the decision to use single-sided silicon for the upgrade. Should work towards simpler designs in the future. For example, using 6 different sensor types resulted in extensive logistical complications. Had to overcome numerous vendor related problems for HDIs, Silicon Sensors, jumpers, low mass cables … Assembly/Installation First alignment results show that the DØ SMT was assembled and installed very well. The installation in the D 0 detector went rather smoothly. The biggest challenge to overcome was the lack of real estate. The D 0 detector, when first designed, was unfortunately not designed with a Silicon detector in mind Como 2001, 10/15/01 E. Kajfasz/B. Quinn 39

Conclusions Design/Production Experience with double-sided detectors has led to the decision to use single-sided silicon for the upgrade. Should work towards simpler designs in the future. For example, using 6 different sensor types resulted in extensive logistical complications. Had to overcome numerous vendor related problems for HDIs, Silicon Sensors, jumpers, low mass cables … Assembly/Installation First alignment results show that the DØ SMT was assembled and installed very well. The installation in the D 0 detector went rather smoothly. The biggest challenge to overcome was the lack of real estate. The D 0 detector, when first designed, was unfortunately not designed with a Silicon detector in mind Como 2001, 10/15/01 E. Kajfasz/B. Quinn 39

Conclusions Commissioning The SMT was the first major DØ Upgrade detector system fully operational for Run 2 a. More than 85% of the channels were available for readout on startup, and most of the remaining channels will be debugged and recovered by November. Calibrations and first look at physics show that we understand our detector. The offline software is debugged at the same time as the hardware. Now that they are both reasonably stable, we can start systematic studies. The detector should be commissioned by the end of the year. We are eager to start doing good physics with it. General Construction and commissioning of the SMT has been an adventure full of challenges. But thanks to the relentless efforts of many physicists, engineers and technicians, D 0 has now a vertex detector to play with. We had so much fun building this detector for run 2 a that we are already planning to build a completely new Silicon Microstrip detector for run 2 b (see Alice’s talk) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 40

Conclusions Commissioning The SMT was the first major DØ Upgrade detector system fully operational for Run 2 a. More than 85% of the channels were available for readout on startup, and most of the remaining channels will be debugged and recovered by November. Calibrations and first look at physics show that we understand our detector. The offline software is debugged at the same time as the hardware. Now that they are both reasonably stable, we can start systematic studies. The detector should be commissioned by the end of the year. We are eager to start doing good physics with it. General Construction and commissioning of the SMT has been an adventure full of challenges. But thanks to the relentless efforts of many physicists, engineers and technicians, D 0 has now a vertex detector to play with. We had so much fun building this detector for run 2 a that we are already planning to build a completely new Silicon Microstrip detector for run 2 b (see Alice’s talk) Como 2001, 10/15/01 E. Kajfasz/B. Quinn 40