14e7d9a0dae84e07a5ade65c9d60a8f0.ppt

- Количество слайдов: 43

DØ Run. IIb Trigger Upgrade Paul Padley for the DØ Trigger Upgrade Group 1

This talk · Will briefly review this (previously approved) upgrade · Will give the current status of the major components of this upgrade · Darien Wood will discuss future plans through commissioning. 2 Director’s Review, July 04

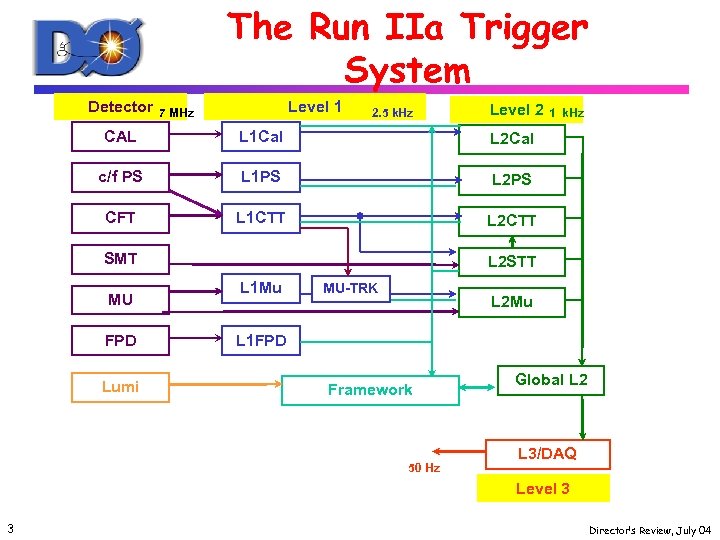

The Run IIa Trigger System Detector Level 1 7 MHz 2. 5 k. Hz Level 2 CAL L 1 Cal L 2 Cal c/f PS L 1 PS L 2 PS CFT L 1 CTT 1 k. Hz L 2 CTT SMT MU FPD Lumi L 2 STT L 1 Mu MU-TRK L 2 Mu L 1 FPD Framework 50 Hz Global L 2 L 3/DAQ Level 3 3 Director’s Review, July 04

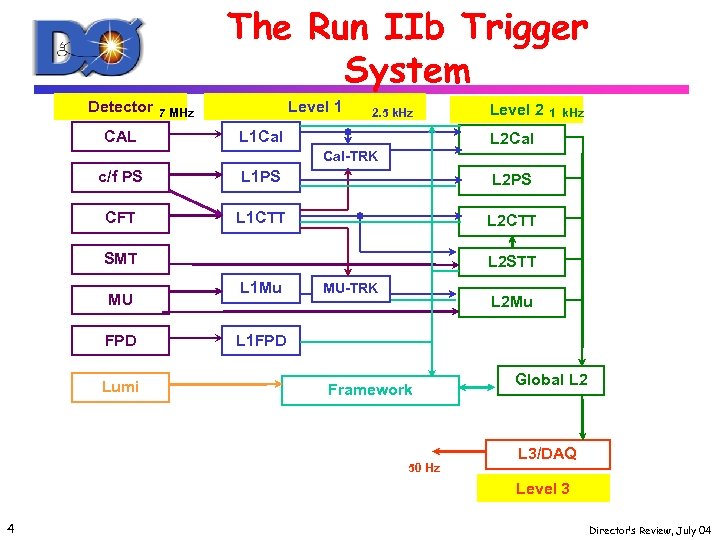

The Run IIb Trigger System Detector CAL Level 1 7 MHz 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT MU FPD Lumi L 2 STT L 1 Mu MU-TRK L 2 Mu L 1 FPD Framework 50 Hz Global L 2 L 3/DAQ Level 3 4 Director’s Review, July 04

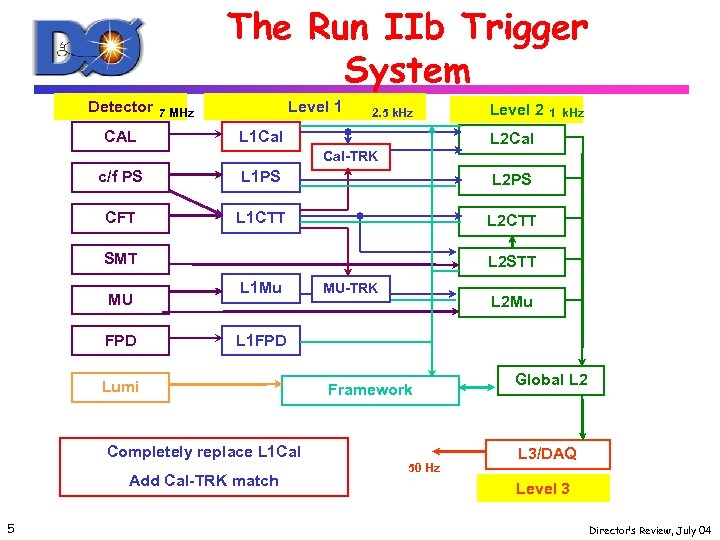

The Run IIb Trigger System Detector CAL Level 1 7 MHz 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT MU FPD L 2 STT L 1 Mu MU-TRK L 2 Mu L 1 FPD Lumi Framework Completely replace L 1 Cal Add Cal-TRK match 5 50 Hz Global L 2 L 3/DAQ Level 3 Director’s Review, July 04

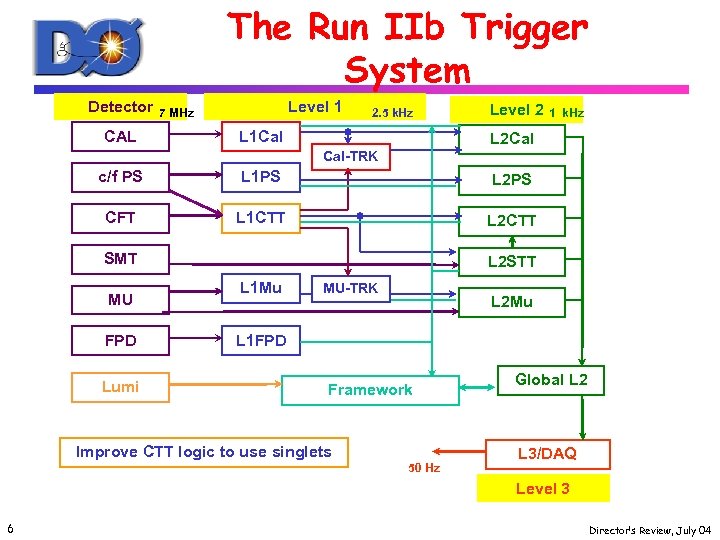

The Run IIb Trigger System Detector CAL Level 1 7 MHz 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT MU FPD Lumi L 2 STT L 1 Mu MU-TRK L 2 Mu L 1 FPD Framework Improve CTT logic to use singlets 50 Hz Global L 2 L 3/DAQ Level 3 6 Director’s Review, July 04

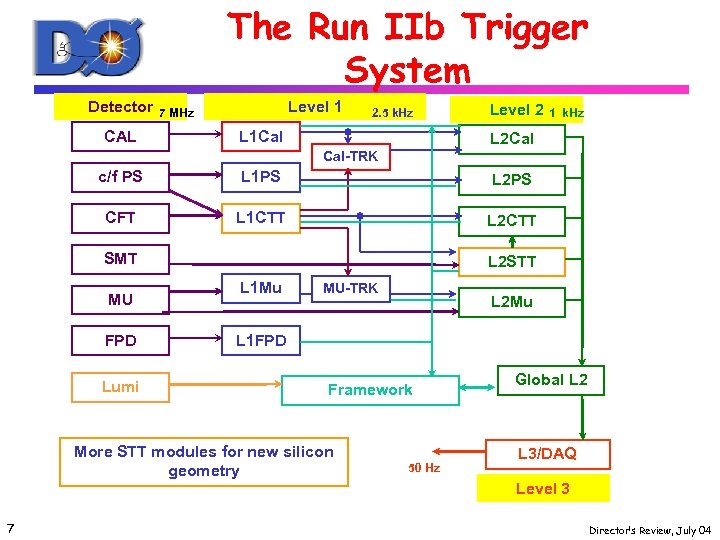

The Run IIb Trigger System Detector CAL Level 1 7 MHz 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT MU FPD Lumi L 2 STT L 1 Mu MU-TRK L 1 FPD Framework More STT modules for new silicon geometry 7 L 2 Mu 50 Hz Global L 2 L 3/DAQ Level 3 Director’s Review, July 04

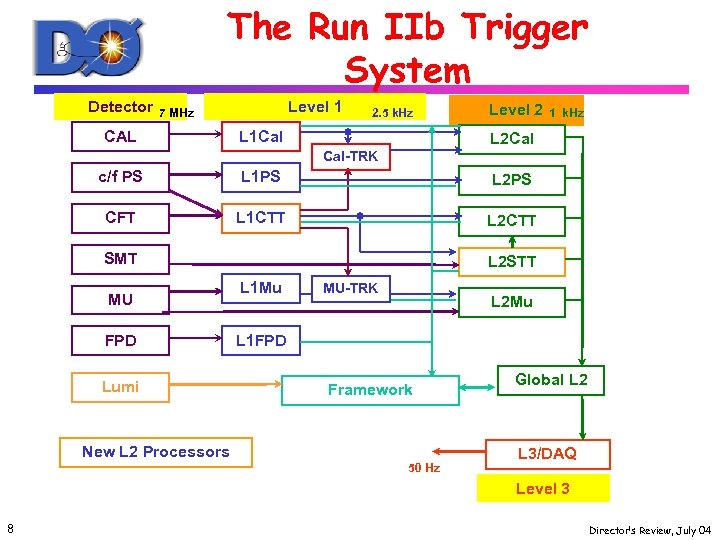

The Run IIb Trigger System Detector Level 1 7 MHz CAL 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT MU FPD Lumi L 2 STT L 1 Mu MU-TRK L 2 Mu L 1 FPD Framework New L 2 Processors 50 Hz Global L 2 L 3/DAQ Level 3 8 Director’s Review, July 04

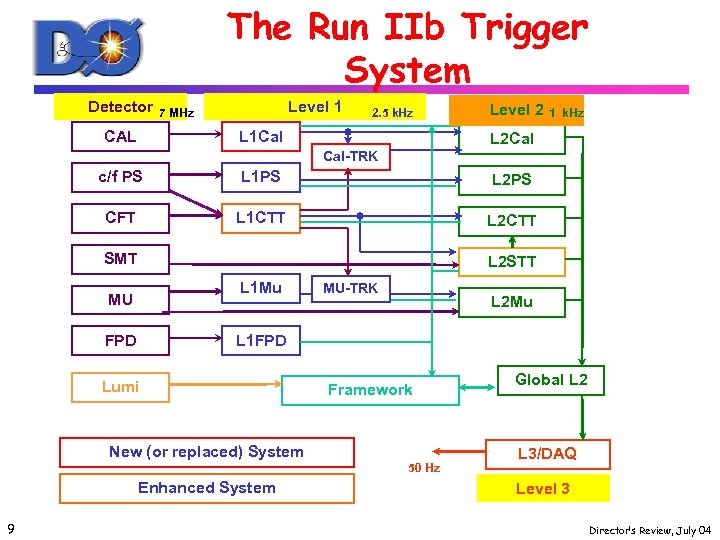

The Run IIb Trigger System Detector CAL Level 1 7 MHz 2. 5 k. Hz L 1 Cal Level 2 1 k. Hz L 2 Cal Cal-TRK c/f PS L 1 PS L 2 PS CFT L 1 CTT L 2 CTT SMT L 2 STT L 1 Mu MU FPD MU-TRK L 2 Mu L 1 FPD Lumi Framework New (or replaced) System 50 Hz Enhanced System 9 Global L 2 L 3/DAQ Level 3 Director’s Review, July 04

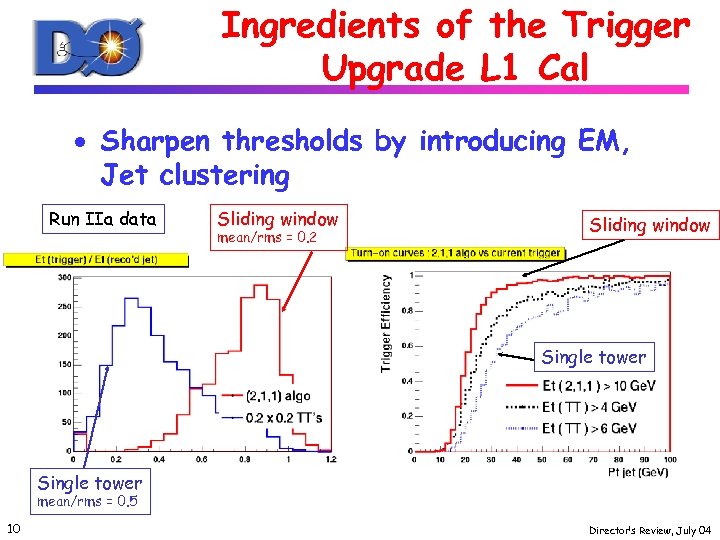

Ingredients of the Trigger Upgrade L 1 Cal · Sharpen thresholds by introducing EM, Jet clustering Run IIa data Sliding window mean/rms = 0. 2 Sliding window Single tower mean/rms = 0. 5 10 Director’s Review, July 04

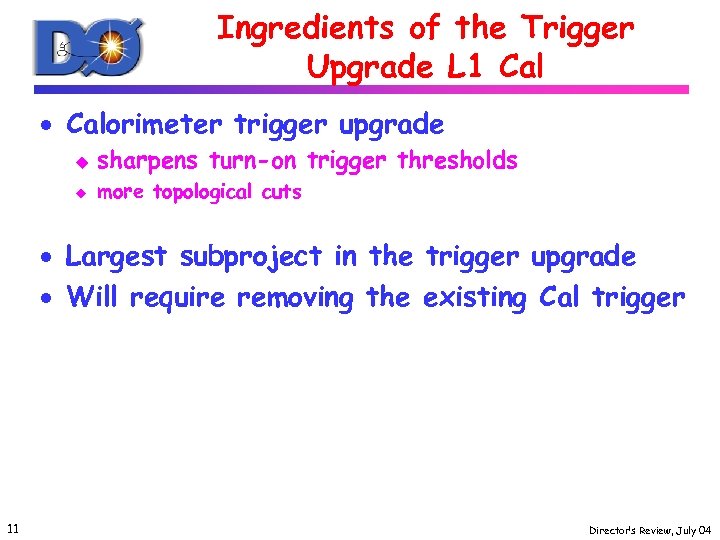

Ingredients of the Trigger Upgrade L 1 Cal · Calorimeter trigger upgrade u sharpens turn-on trigger thresholds u more topological cuts · Largest subproject in the trigger upgrade · Will require removing the existing Cal trigger 11 Director’s Review, July 04

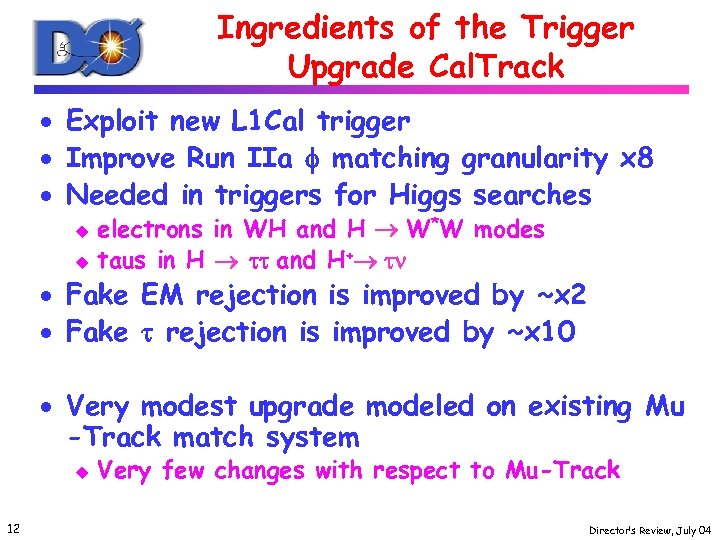

Ingredients of the Trigger Upgrade Cal. Track · Exploit new L 1 Cal trigger · Improve Run IIa f matching granularity x 8 · Needed in triggers for Higgs searches u u electrons in WH and H W*W modes taus in H tt and H+ t · Fake EM rejection is improved by ~x 2 · Fake t rejection is improved by ~x 10 · Very modest upgrade modeled on existing Mu -Track match system u 12 Very few changes with respect to Mu-Track Director’s Review, July 04

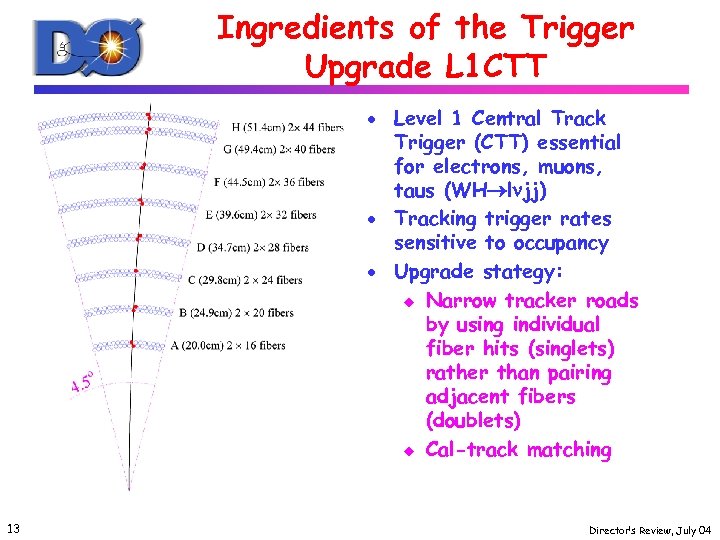

Ingredients of the Trigger Upgrade L 1 CTT · Level 1 Central Track Trigger (CTT) essential for electrons, muons, taus (WH l jj) · Tracking trigger rates sensitive to occupancy · Upgrade stategy: u Narrow tracker roads by using individual fiber hits (singlets) rather than pairing adjacent fibers (doublets) u Cal-track matching 13 Director’s Review, July 04

Ingredients of the Trigger Upgrade L 1 CTT · Original idea was to simply replace FPGAs to newer larger ones that allow more equations · Have recently upscoped the project to allow monitoring and debugging capability · The project now involves replacing two crates of electronics · All elements in this upgrade have been designed to minimize commissioning time and simplify debugging 14 Director’s Review, July 04

Ingredients of the Trigger Upgrade Level 2 · Level 2 STT – simply buy more boards to include the new layer 0 · Level 2 Processors. Just buy new faster processors to allow more functionality at this trigger level 15 Director’s Review, July 04

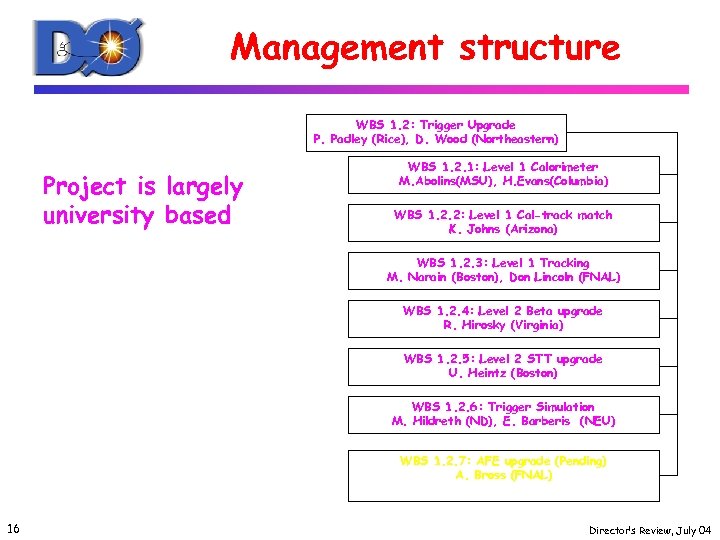

Management structure WBS 1. 2: Trigger Upgrade P. Padley (Rice), D. Wood (Northeastern) Project is largely university based WBS 1. 2. 1: Level 1 Calorimeter M. Abolins(MSU), H. Evans(Columbia) WBS 1. 2. 2: Level 1 Cal-track match K. Johns (Arizona) WBS 1. 2. 3: Level 1 Tracking M. Narain (Boston), Don Lincoln (FNAL) WBS 1. 2. 4: Level 2 Beta upgrade R. Hirosky (Virginia) WBS 1. 2. 5: Level 2 STT upgrade U. Heintz (Boston) WBS 1. 2. 6: Trigger Simulation M. Hildreth (ND), E. Barberis (NEU) WBS 1. 2. 7: AFE upgrade (Pending) A. Bross (FNAL) 16 Director’s Review, July 04

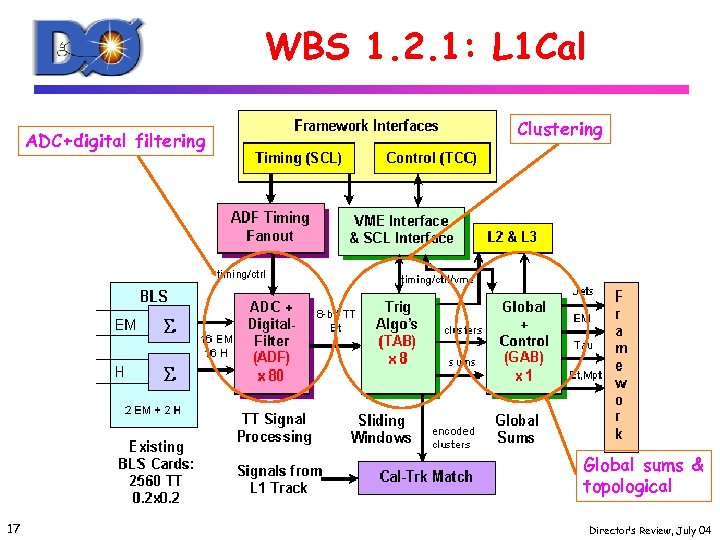

WBS 1. 2. 1: L 1 Cal ADC+digital filtering Clustering Global sums & topological 17 Director’s Review, July 04

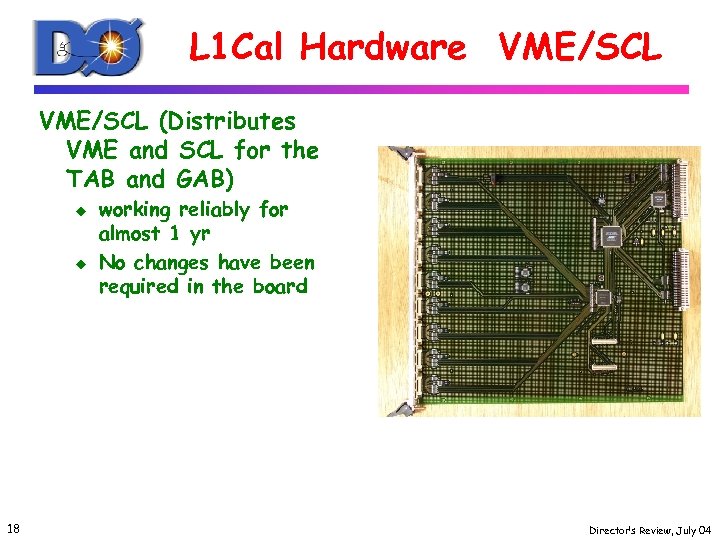

L 1 Cal Hardware VME/SCL (Distributes VME and SCL for the TAB and GAB) u u 18 working reliably for almost 1 yr No changes have been required in the board Director’s Review, July 04

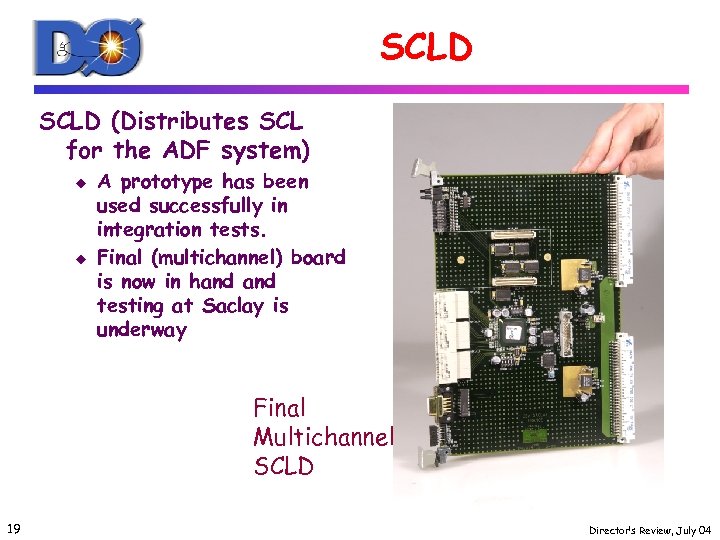

SCLD (Distributes SCL for the ADF system) u u A prototype has been used successfully in integration tests. Final (multichannel) board is now in hand testing at Saclay is underway Final Multichannel SCLD 19 Director’s Review, July 04

ADF Prototype V 1 ADF Prototype board Underwent integration tests at Fermilab, Oct 03 Was successfully operated with D 0 timing signals Sent data to TAB using D 0 timing signals 20 Director’s Review, July 04

ADF V 2 ADF Card (takes signals from BLS, digitizes them and applies digital filter) u u 21 Prototype has been in hand tested for some time MSU has taken responsibility for the second prototype and production MSU Engineers have been working with Saclay and Nevis engineering very thoroughly reviewing the design and implementing changes in the version 2 prototype design Design cycle has finished and layout step is well underway. Director’s Review, July 04

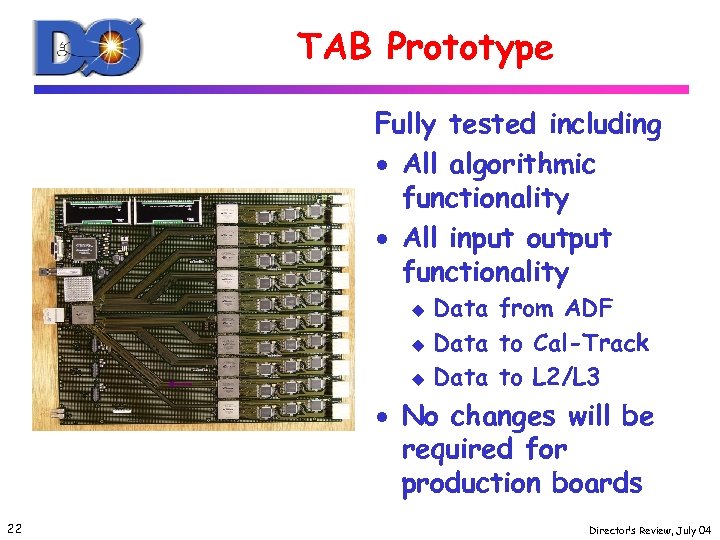

TAB Prototype Fully tested including · All algorithmic functionality · All input output functionality u u u Data from ADF Data to Cal-Track Data to L 2/L 3 · No changes will be required for production boards 22 Director’s Review, July 04

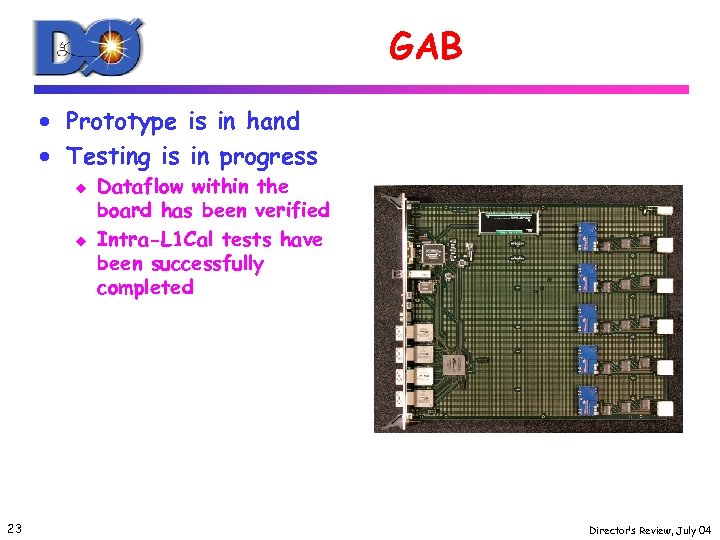

GAB · Prototype is in hand · Testing is in progress u u 23 Dataflow within the board has been verified Intra-L 1 Cal tests have been successfully completed Director’s Review, July 04

L 1 Cal Trigger Short Term Plans A number of tests are underway or about to be undertaken to completely test all inputs outputs and intrasystem communication paths TAB L 2/L 3 Write data to tape (test unpacking) ADF TAB Long Term Data Transfer Tests GAB Implement 1 st And/Or terms Test out to TFW SCLD Test Final Card BLS ADF Test Prototype of New Scheme in Test Area ADF v 2 Bench Test New Board Shutdown NO specific requirements Will make full use of access to detector/daq 24 Director’s Review, July 04

L 1 Cal Summary · · 25 All boards are in good shape Testing is well along Prototypes have worked well MSU has stepped up to the plate and picked up the ADF project. Director’s Review, July 04

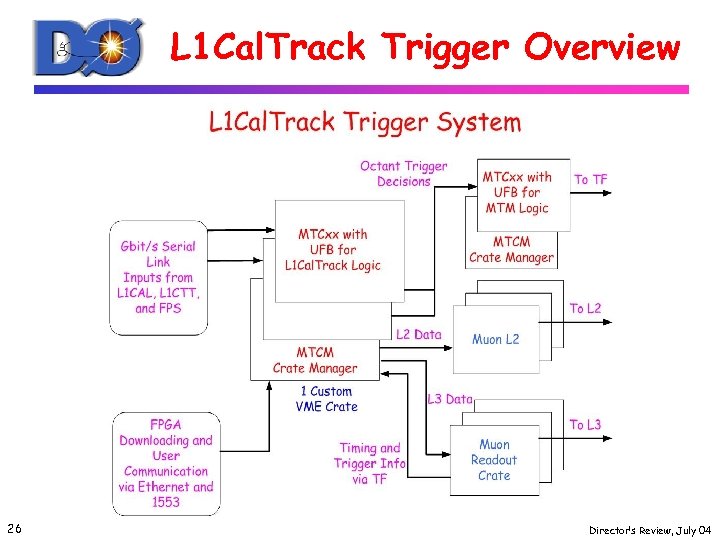

L 1 Cal. Track Trigger Overview 26 Director’s Review, July 04

Hardware Status · SLDB’s (Serial Link Daughter Boards) u Complete · MTCM (Crate Mananger) u Production fabrication complete and assembly in progress · MTCxx (Trigger Card) and UFB (Flavor Board) u u Preproduction testing well along Production version to be ordered early fall · Splitter Cards u Beginning parts order · Bottom line = Expect production hardware complete by early 2005 27 Director’s Review, July 04

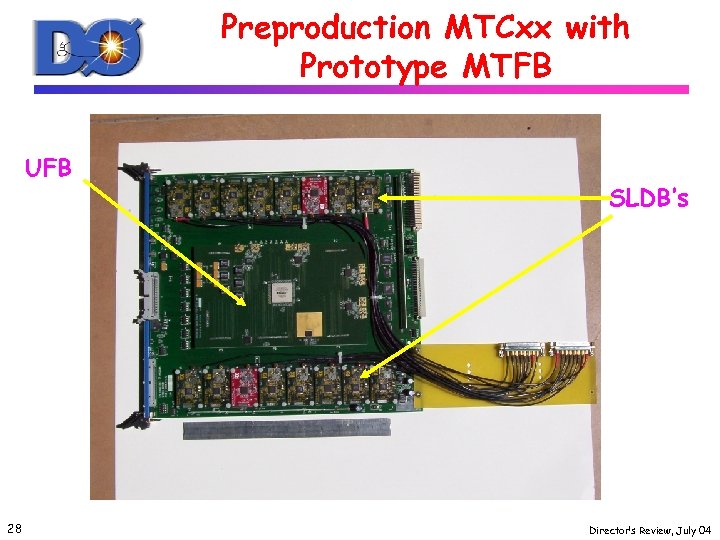

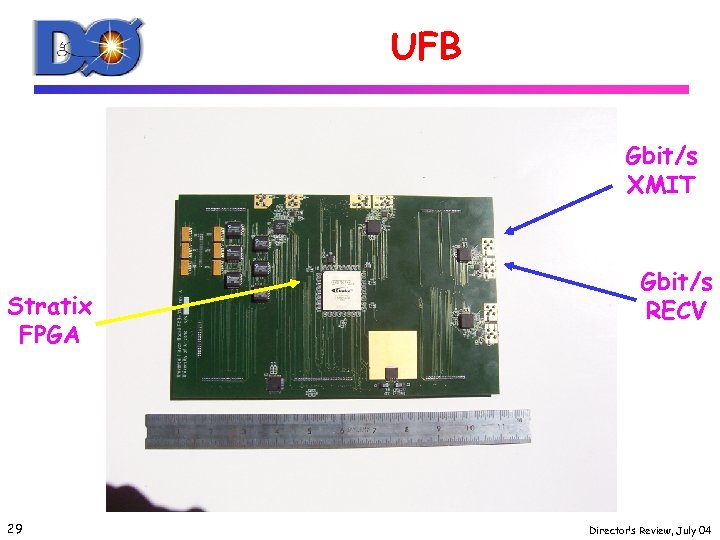

Preproduction MTCxx with Prototype MTFB UFB 28 SLDB’s Director’s Review, July 04

UFB Gbit/s XMIT Stratix FPGA 29 Gbit/s RECV Director’s Review, July 04

Software Status · Much of the software needed will result from modifying existing L 1 MU software including u u Control and FPGA downloading Online monitoring Trigger term downloading (COOR) Offline analysis s 30 Expect progress this summer on all Director’s Review, July 04

Infrastructure Status · L 1 Caltrack trigger and readout crates u Installed and populated (using spare L 1 MU cards) · Rack infrastructure (power, water, …) u Complete · VME crate power supply u u In hand, waiting for delivery of custom power leads Currently using spare L 1 MU supply · Cables u u 31 Collision hall to MCH 1 cables run but not terminated L 1 CTT transition cables not terminated MTCxx cable termination in progress (Fermilab) Cable termination inside collision hall planned for August 2004 shutdown Director’s Review, July 04

L 1 Cal. Track Summary · Most of the L 1 Cal. Track hardware will be completed in early 2005 · We hope to have L 1 Cal. Track crates integrated into the experiment (test triggers, readout) by the end of the August 2004 shutdown · Once this is complete, more emphasis will shift to simulation 32 Director’s Review, July 04

L 1 Central Track Trigger · Digital Front End Axial (DFEA) daughter cards redesigned with larger FPGA’s (Xilinx Virtex-II XC 2 V 6000) u Allows more complicated equations for using narrower roads · Implemented prototype firmware (Boston U) u u u Includes equation files from all 4 momentum bins DFEA logic is implemented in two FPGAs Prototype board functionality tested · Detailed system design changes to make the upgrade easier to commission 33 Director’s Review, July 04

DFEA Board · New DFEA card (combining the daughter card and motherboard functionality) has now been designed and laid out · Parts ordering has begun · Will send board out for manufacture once all parts have been ordered (just in case there is trouble obtaining a part) 34 Director’s Review, July 04

Standalone tester · In order to test the new DFEA boards an simple standalone tester board has be designed and laid out · This board has been sent for PCB manufacture (Should be back by the time this talk is given) 35 Director’s Review, July 04

Controller, Backplane and Splitters · New backplane – Layout is finished Part ordering has begun · Controller – the layout of this is now finished – work on the firmware continues u Work is also progressing on linux software to use this new controller · LVDS Splitters – Bare PC boards are now in hand 36 Director’s Review, July 04

CTT summary · Things are progressing well · We are in a period of very intense activity with the status of tasks changing weekly · On track to do tests during the shutdown 37 Director’s Review, July 04

STT upgrade · This upgrade is simply making more of the boards that are currently used to allow for the inclusion of layer 0 · Parts in danger of obsolescence have been procured · Gaining experience from Run IIa · Ready to go into a PRR to produce the boards 38 Director’s Review, July 04

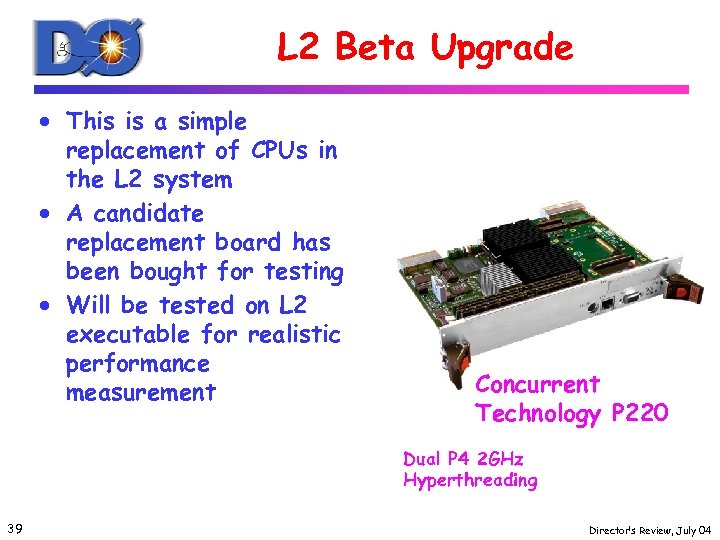

L 2 Beta Upgrade · This is a simple replacement of CPUs in the L 2 system · A candidate replacement board has been bought for testing · Will be tested on L 2 executable for realistic performance measurement Concurrent Technology P 220 Dual P 4 2 GHz Hyperthreading 39 Director’s Review, July 04

Simulation L 1 Cal - Completely new capabilities - new architecture trigsim & standalone code L 1 CTT - “Drop-in” replacement - same architecture trigsim & standalone code - in the works: updates for new VHDL eqns. L 1 Cal. Trk - completely new in the works: - trigsim code (long term) - macros (short term) on combined L 1 Cal and L 1 CTT standalone code 40 Director’s Review, July 04

Run IIb Trigger Simulation Plans · Simulations of the various trigger components have been in place for some time and were used to justify the upgrade in the first place · Now we are moving towards tools that are used to decide details of what will be implemented in the upgraded trigger and come up with an initial trigger list. · The ultimate goal is a well defined trigger list in place when the upgraded trigger is turned on. 41 Director’s Review, July 04

Recent changes to schedule · L 1 Cal changes for ADF in place and MOU with MSU signed. · Cal-track match (Apr 30 th update) u u Change control for schedule changes Minor cost changes ($12 k) · L 1 CTT (Apr 30 th update) u New tasks for s s u 42 DFEM DSAT Controller Backplane Major cost changes Director’s Review, July 04

Summary · L 1 cal ADF v. 2 design complete and layout is underway · L 1 cal TAB undergoing final tests before production review · L 1 cal-track: complete motherboard + daughterboard prototype set in hand undergoing tests · Simulation effort ramping up · L 1 CTT: upscope approved and underway 43 Director’s Review, July 04

14e7d9a0dae84e07a5ade65c9d60a8f0.ppt