12ed54c0b4b381724f14e513cd1cc179.ppt

- Количество слайдов: 29

Digital systems verification IAF 0620, 5. 0 AP, Exam http: //ati. ttu. ee/~jaan/verification Jaan Raik ICT-524, 620 2257, 55 13141 jaan@ati. ttu. ee 1

Digital systems verification IAF 0620, 5. 0 AP, Exam http: //ati. ttu. ee/~jaan/verification Jaan Raik ICT-524, 620 2257, 55 13141 jaan@ati. ttu. ee 1

Digital systems verification Course book: Hardware Design Verification: Simulation and Formal Method-Based Approaches William K. Lam, Sun Microsystems. . . Publisher: Prentice Hall PTR Pub Date: March 03, 2005 ISBN: 0 -13 -143347 -4 Pages: 624 Digital systems verification course 2

Digital systems verification Course book: Hardware Design Verification: Simulation and Formal Method-Based Approaches William K. Lam, Sun Microsystems. . . Publisher: Prentice Hall PTR Pub Date: March 03, 2005 ISBN: 0 -13 -143347 -4 Pages: 624 Digital systems verification course 2

Digital systems verification Course outline 1. Introduction, verification methods. (1. 1 -1. 5) 2. Decision diagrams and equivalence. (8. 1) 3. SAT solving (8. 4) Exercise 1 4. Simulation, symbolic simulation (8. 5) 5. Verification coverage (5. 5 -5. 6) 6. Assertions (5. 4) Exercise 2 7. Property checking (9) 8. Automated debug (bug localization + correction) 9. Verification and HDL (1. 6, 2 -4) 3

Digital systems verification Course outline 1. Introduction, verification methods. (1. 1 -1. 5) 2. Decision diagrams and equivalence. (8. 1) 3. SAT solving (8. 4) Exercise 1 4. Simulation, symbolic simulation (8. 5) 5. Verification coverage (5. 5 -5. 6) 6. Assertions (5. 4) Exercise 2 7. Property checking (9) 8. Automated debug (bug localization + correction) 9. Verification and HDL (1. 6, 2 -4) 3

Embedded Systems 4

Embedded Systems 4

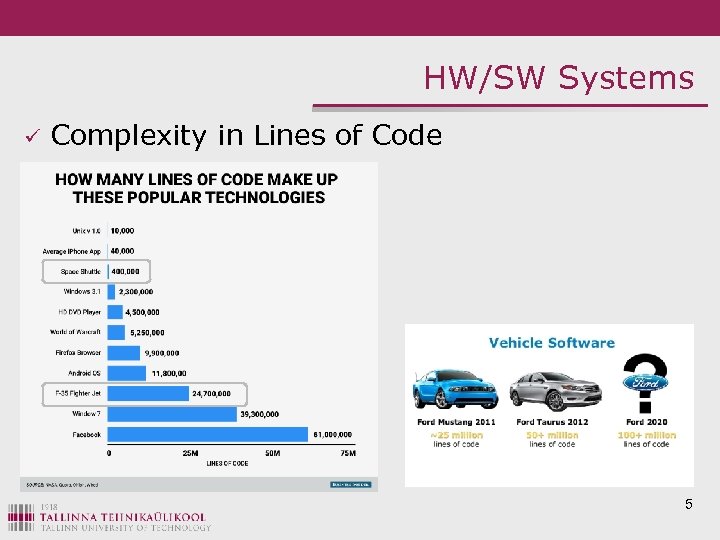

HW/SW Systems ü Complexity in Lines of Code 5

HW/SW Systems ü Complexity in Lines of Code 5

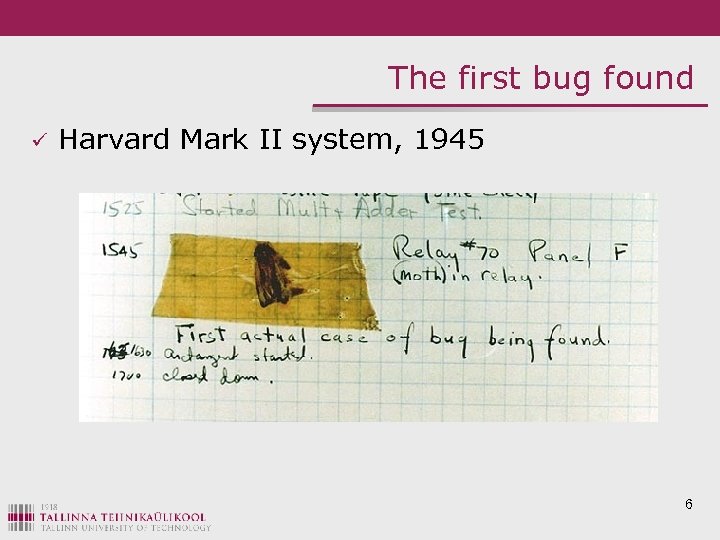

The first bug found ü Harvard Mark II system, 1945 6

The first bug found ü Harvard Mark II system, 1945 6

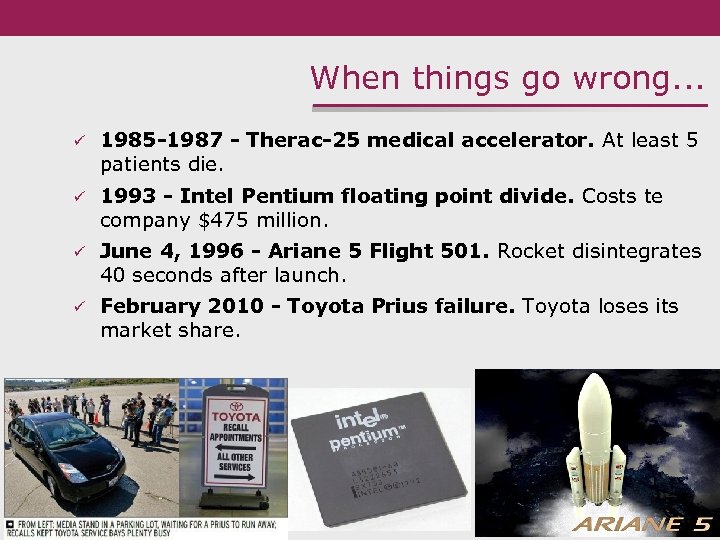

When things go wrong. . . ü 1985 -1987 - Therac-25 medical accelerator. At least 5 patients die. ü 1993 - Intel Pentium floating point divide. Costs te company $475 million. ü June 4, 1996 - Ariane 5 Flight 501. Rocket disintegrates 40 seconds after launch. ü February 2010 - Toyota Prius failure. Toyota loses its market share. 7

When things go wrong. . . ü 1985 -1987 - Therac-25 medical accelerator. At least 5 patients die. ü 1993 - Intel Pentium floating point divide. Costs te company $475 million. ü June 4, 1996 - Ariane 5 Flight 501. Rocket disintegrates 40 seconds after launch. ü February 2010 - Toyota Prius failure. Toyota loses its market share. 7

Digital systems verification course 8

Digital systems verification course 8

jne… ? ? ? 32. position ~ 4 billion grains 64. position ~1019 grains Digital systems verification course 9

jne… ? ? ? 32. position ~ 4 billion grains 64. position ~1019 grains Digital systems verification course 9

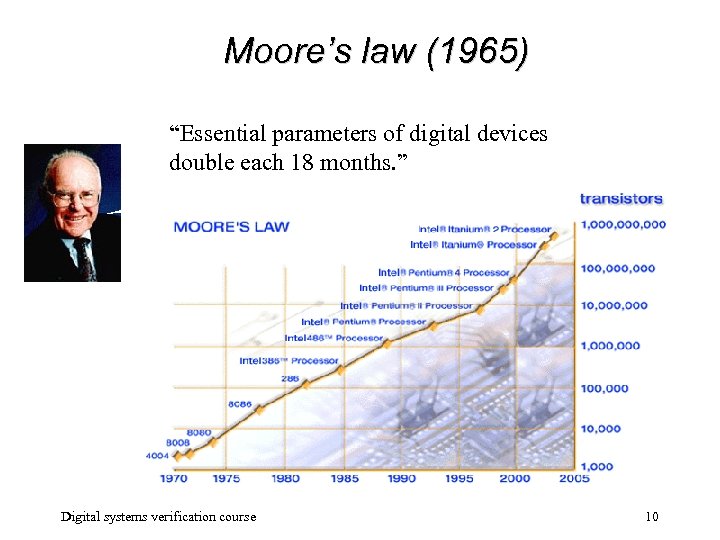

Moore’s law (1965) “Essential parameters of digital devices double each 18 months. ” Digital systems verification course 10

Moore’s law (1965) “Essential parameters of digital devices double each 18 months. ” Digital systems verification course 10

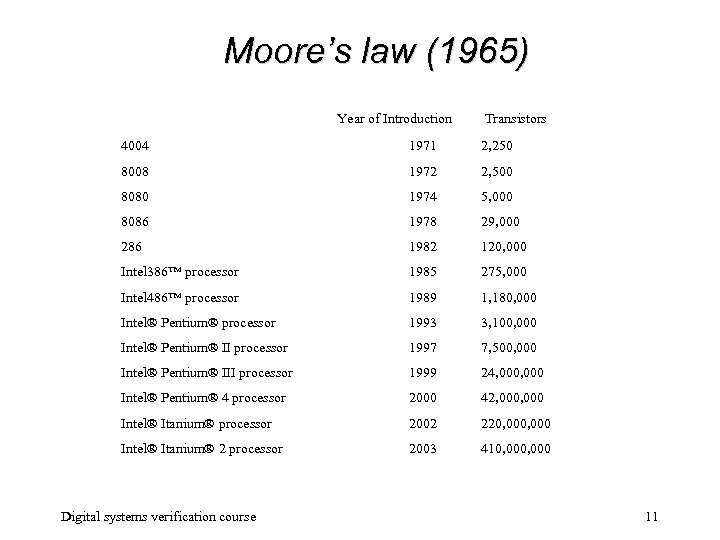

Moore’s law (1965) Year of Introduction Transistors 4004 1971 2, 250 8008 1972 2, 500 8080 1974 5, 000 8086 1978 29, 000 286 1982 120, 000 Intel 386™ processor 1985 275, 000 Intel 486™ processor 1989 1, 180, 000 Intel® Pentium® processor 1993 3, 100, 000 Intel® Pentium® II processor 1997 7, 500, 000 Intel® Pentium® III processor 1999 24, 000 Intel® Pentium® 4 processor 2000 42, 000 Intel® Itanium® processor 2002 220, 000 Intel® Itanium® 2 processor 2003 410, 000 Digital systems verification course 11

Moore’s law (1965) Year of Introduction Transistors 4004 1971 2, 250 8008 1972 2, 500 8080 1974 5, 000 8086 1978 29, 000 286 1982 120, 000 Intel 386™ processor 1985 275, 000 Intel 486™ processor 1989 1, 180, 000 Intel® Pentium® processor 1993 3, 100, 000 Intel® Pentium® II processor 1997 7, 500, 000 Intel® Pentium® III processor 1999 24, 000 Intel® Pentium® 4 processor 2000 42, 000 Intel® Itanium® processor 2002 220, 000 Intel® Itanium® 2 processor 2003 410, 000 Digital systems verification course 11

Rapid growth of digital technology J 25 -30 % annually decreasing cost per function J 15 percent annual growth of the market for integrated circuits • But … L The cost of developing a digital chip keeps on growing. • In 1981, development of a leading-edge CPU cost 1 M$ • …today it costs more than 300 M$ !!! • Why do costs increase ? ? ? Digital systems verification course 12

Rapid growth of digital technology J 25 -30 % annually decreasing cost per function J 15 percent annual growth of the market for integrated circuits • But … L The cost of developing a digital chip keeps on growing. • In 1981, development of a leading-edge CPU cost 1 M$ • …today it costs more than 300 M$ !!! • Why do costs increase ? ? ? Digital systems verification course 12

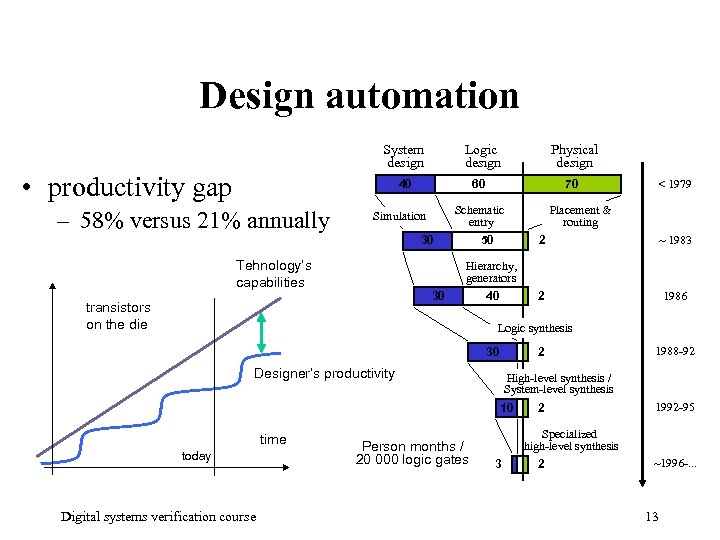

Design automation System design • productivity gap Logic design 40 – 58% versus 21% annually 70 60 Schematic entry Simulation 30 Tehnology’s capabilities Physical design 50 < 1979 Placement & routing 2 ~ 1983 2 1986 Hierarchy, generators 30 transistors on the die 40 Logic synthesis 30 2 Designer’s productivity High-level synthesis / System-level synthesis 10 time today Digital systems verification course Person months / 20 000 logic gates 1988 -92 2 1992 -95 Specialized high-level synthesis 3 2 ~1996 -. . . 13

Design automation System design • productivity gap Logic design 40 – 58% versus 21% annually 70 60 Schematic entry Simulation 30 Tehnology’s capabilities Physical design 50 < 1979 Placement & routing 2 ~ 1983 2 1986 Hierarchy, generators 30 transistors on the die 40 Logic synthesis 30 2 Designer’s productivity High-level synthesis / System-level synthesis 10 time today Digital systems verification course Person months / 20 000 logic gates 1988 -92 2 1992 -95 Specialized high-level synthesis 3 2 ~1996 -. . . 13

Verification versus test • The goal of verification is to check if a system is designed correctly. • Validation is similar to verification but we check on a prototype device, not a model. • By (manufacturing) Test we understand checking every instance of a produced chip against manufacruring defects. Digital systems verification course 14

Verification versus test • The goal of verification is to check if a system is designed correctly. • Validation is similar to verification but we check on a prototype device, not a model. • By (manufacturing) Test we understand checking every instance of a produced chip against manufacruring defects. Digital systems verification course 14

Types of verification • Mixed-signal, analog, RF, . . . • We consider only digital • Functional, timing, layout, electrical etc. verification • Here, we consider functional only Digital systems verification course 15

Types of verification • Mixed-signal, analog, RF, . . . • We consider only digital • Functional, timing, layout, electrical etc. verification • Here, we consider functional only Digital systems verification course 15

Why is verification important Some figures: • 2 -4 verification engineers per designer • Verification takes 70 -85 % of total cost of chip design • Why has verification become that important? Digital systems verification course 16

Why is verification important Some figures: • 2 -4 verification engineers per designer • Verification takes 70 -85 % of total cost of chip design • Why has verification become that important? Digital systems verification course 16

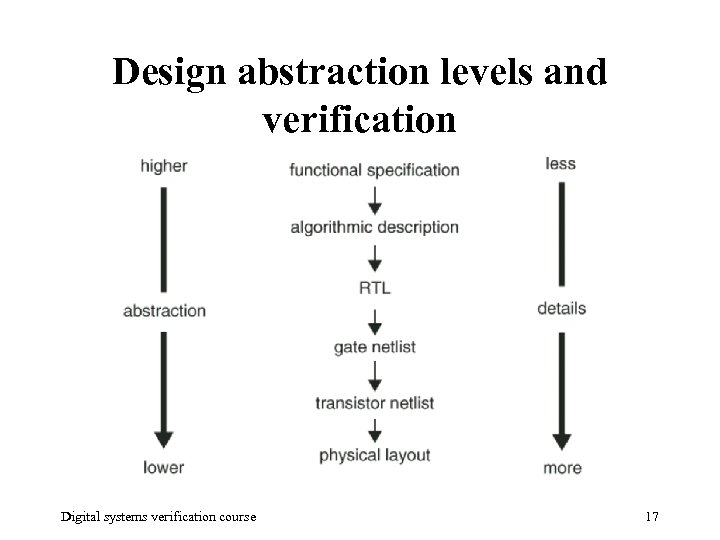

Design abstraction levels and verification Digital systems verification course 17

Design abstraction levels and verification Digital systems verification course 17

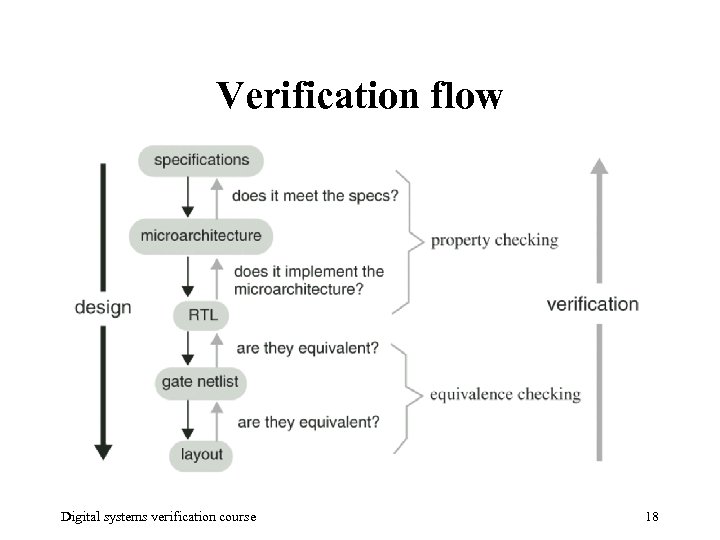

Verification flow Digital systems verification course 18

Verification flow Digital systems verification course 18

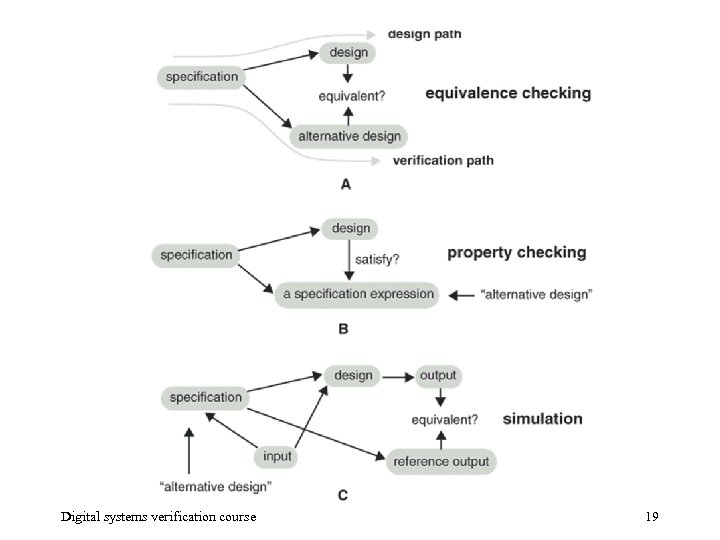

Digital systems verification course 19

Digital systems verification course 19

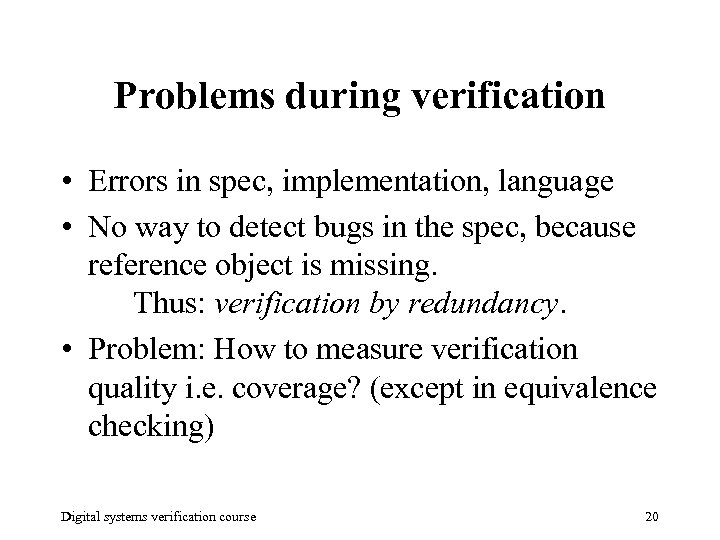

Problems during verification • Errors in spec, implementation, language • No way to detect bugs in the spec, because reference object is missing. Thus: verification by redundancy. • Problem: How to measure verification quality i. e. coverage? (except in equivalence checking) Digital systems verification course 20

Problems during verification • Errors in spec, implementation, language • No way to detect bugs in the spec, because reference object is missing. Thus: verification by redundancy. • Problem: How to measure verification quality i. e. coverage? (except in equivalence checking) Digital systems verification course 20

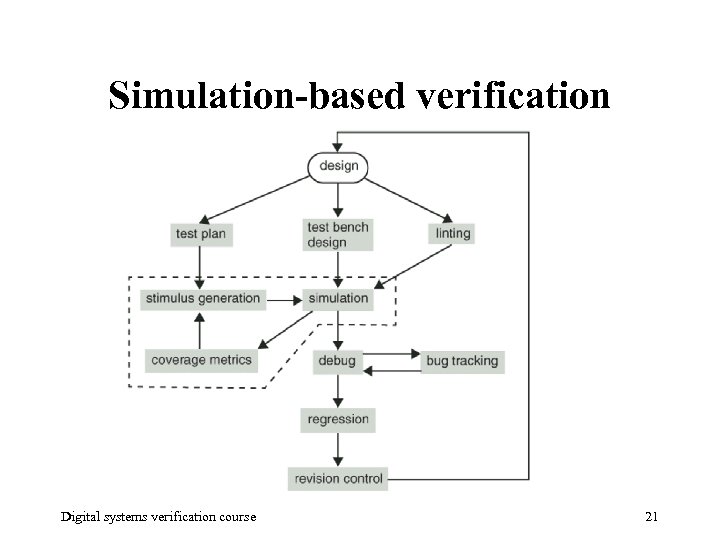

Simulation-based verification Digital systems verification course 21

Simulation-based verification Digital systems verification course 21

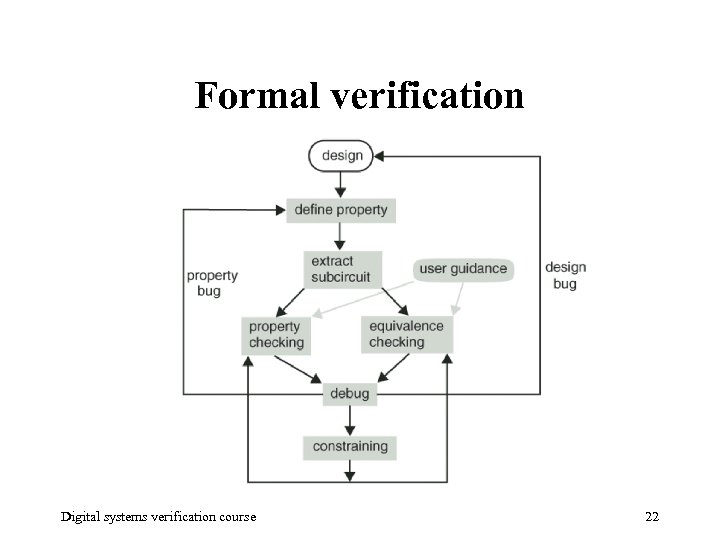

Formal verification Digital systems verification course 22

Formal verification Digital systems verification course 22

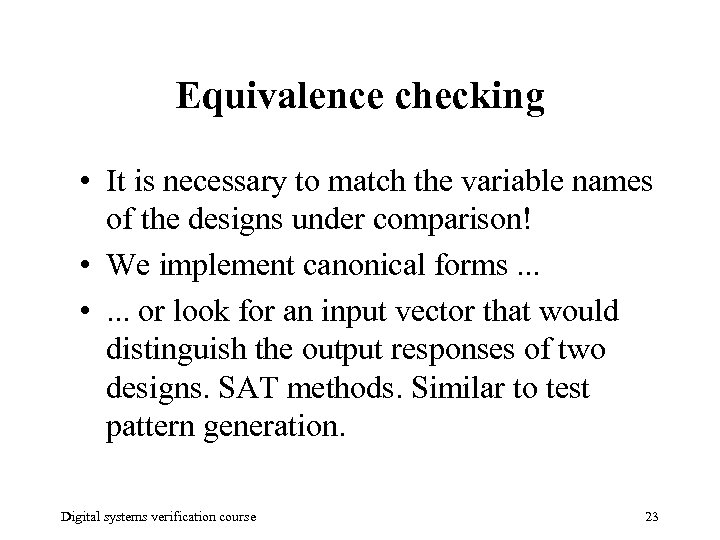

Equivalence checking • It is necessary to match the variable names of the designs under comparison! • We implement canonical forms. . . • . . . or look for an input vector that would distinguish the output responses of two designs. SAT methods. Similar to test pattern generation. Digital systems verification course 23

Equivalence checking • It is necessary to match the variable names of the designs under comparison! • We implement canonical forms. . . • . . . or look for an input vector that would distinguish the output responses of two designs. SAT methods. Similar to test pattern generation. Digital systems verification course 23

Equivalence checking • Comparison of pre- and post-scan schematics • Comparison of RTL versus transistor layout • Verification of minor changes in the design Digital systems verification course 24

Equivalence checking • Comparison of pre- and post-scan schematics • Comparison of RTL versus transistor layout • Verification of minor changes in the design Digital systems verification course 24

Model-checking • The goal is to find an input assignment violating the assumed property. • If such an assignment (counter-example!) exists then we can simulate it to obtain signal waveforms for debugging. • If there exists no counter-example then we have proven that the implementation matches the property. Digital systems verification course 25

Model-checking • The goal is to find an input assignment violating the assumed property. • If such an assignment (counter-example!) exists then we can simulate it to obtain signal waveforms for debugging. • If there exists no counter-example then we have proven that the implementation matches the property. Digital systems verification course 25

Model-checking Problems: • How to extract only this portion of the design that is related to the property to be checked. Currently done manually. . . • Selection of the properties to be checked is tricky. . . • Bugs may occur in the implementation, in properties or in configuration (i. e. environment). • Roughly 70 % of total effort for setting up the configuration. Digital systems verification course 26

Model-checking Problems: • How to extract only this portion of the design that is related to the property to be checked. Currently done manually. . . • Selection of the properties to be checked is tricky. . . • Bugs may occur in the implementation, in properties or in configuration (i. e. environment). • Roughly 70 % of total effort for setting up the configuration. Digital systems verification course 26

Model-checking Theorem provers • Not too much automated but. . . • . . . can handle larger designs, require less memory. • Use higher order logic. Thus, can check more complex properties. Digital systems verification course 27

Model-checking Theorem provers • Not too much automated but. . . • . . . can handle larger designs, require less memory. • Use higher order logic. Thus, can check more complex properties. Digital systems verification course 27

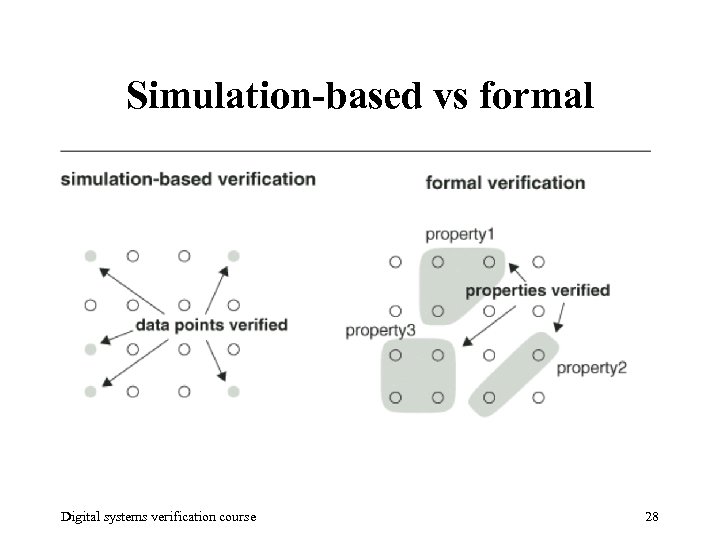

Simulation-based vs formal Digital systems verification course 28

Simulation-based vs formal Digital systems verification course 28

29

29