181e2911969b03fd257667e31812dace.ppt

- Количество слайдов: 22

Digital Pulse Processor DDC-8 (Universal Trigger Module) for PHOBOS. Wojtek Skulski University of Rochester W. Skulski Phobos Workshop April/2003

Digital Pulse Processor DDC-8 (Universal Trigger Module) for PHOBOS. Wojtek Skulski University of Rochester W. Skulski Phobos Workshop April/2003

Outline • Trigger application in PHOBOS. • Description of the Universal Trigger Module DDC-8. • Two configurations: 1. Standalone module without DAQ readout. 2. VME front-end with DAQ readout. • Response to scintillator pulses. • Programming tools: • FPGA programming tools. • Embedded microprocessor tools. • PC GUI programming environment. W. Skulski Phobos Workshop April/2003

Outline • Trigger application in PHOBOS. • Description of the Universal Trigger Module DDC-8. • Two configurations: 1. Standalone module without DAQ readout. 2. VME front-end with DAQ readout. • Response to scintillator pulses. • Programming tools: • FPGA programming tools. • Embedded microprocessor tools. • PC GUI programming environment. W. Skulski Phobos Workshop April/2003

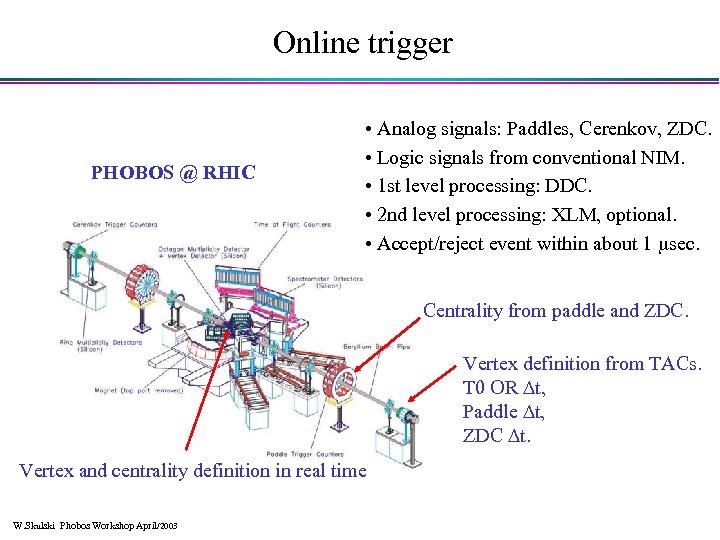

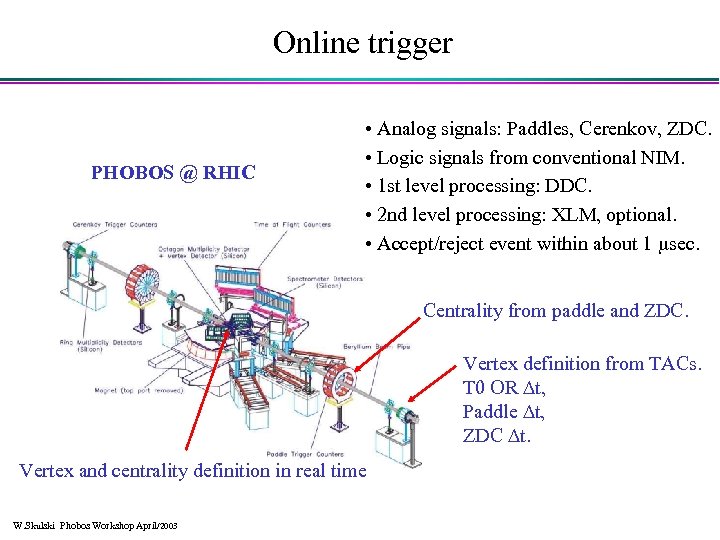

Online trigger PHOBOS @ RHIC • Analog signals: Paddles, Cerenkov, ZDC. • Logic signals from conventional NIM. • 1 st level processing: DDC. • 2 nd level processing: XLM, optional. • Accept/reject event within about 1 msec. Centrality from paddle and ZDC. Vertex definition from TACs. T 0 OR Dt, Paddle Dt, ZDC Dt. Vertex and centrality definition in real time W. Skulski Phobos Workshop April/2003

Online trigger PHOBOS @ RHIC • Analog signals: Paddles, Cerenkov, ZDC. • Logic signals from conventional NIM. • 1 st level processing: DDC. • 2 nd level processing: XLM, optional. • Accept/reject event within about 1 msec. Centrality from paddle and ZDC. Vertex definition from TACs. T 0 OR Dt, Paddle Dt, ZDC Dt. Vertex and centrality definition in real time W. Skulski Phobos Workshop April/2003

Possible configurations • Standalone Universal Trigger Module DDC-8. • 8 flash ADC channels + 41 logic I/O. • Standalone data acquisition and histogramming. • Counting House interfaces: USB and JTAG. • Tunnel interface: RS-232. • Real-time decision: fast. • DAQ readout: no. • The combo system UTM+XLM. • 8, 16, 24, or 32 flash ADC channels + many logic I/Os. • Real-time decision: slower due to “additional layer”. • DAQ readout: yes. • More complicated programming. W. Skulski Phobos Workshop April/2003

Possible configurations • Standalone Universal Trigger Module DDC-8. • 8 flash ADC channels + 41 logic I/O. • Standalone data acquisition and histogramming. • Counting House interfaces: USB and JTAG. • Tunnel interface: RS-232. • Real-time decision: fast. • DAQ readout: no. • The combo system UTM+XLM. • 8, 16, 24, or 32 flash ADC channels + many logic I/Os. • Real-time decision: slower due to “additional layer”. • DAQ readout: yes. • More complicated programming. W. Skulski Phobos Workshop April/2003

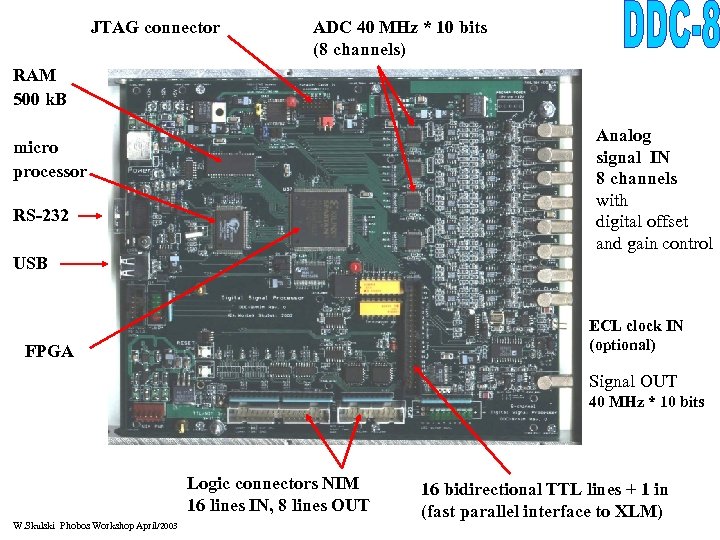

JTAG connector ADC 40 MHz * 10 bits (8 channels) RAM 500 k. B Analog signal IN 8 channels with digital offset and gain control micro processor RS-232 USB ECL clock IN (optional) FPGA Signal OUT 40 MHz * 10 bits Logic connectors NIM 16 lines IN, 8 lines OUT W. Skulski Phobos Workshop April/2003 16 bidirectional TTL lines + 1 in (fast parallel interface to XLM)

JTAG connector ADC 40 MHz * 10 bits (8 channels) RAM 500 k. B Analog signal IN 8 channels with digital offset and gain control micro processor RS-232 USB ECL clock IN (optional) FPGA Signal OUT 40 MHz * 10 bits Logic connectors NIM 16 lines IN, 8 lines OUT W. Skulski Phobos Workshop April/2003 16 bidirectional TTL lines + 1 in (fast parallel interface to XLM)

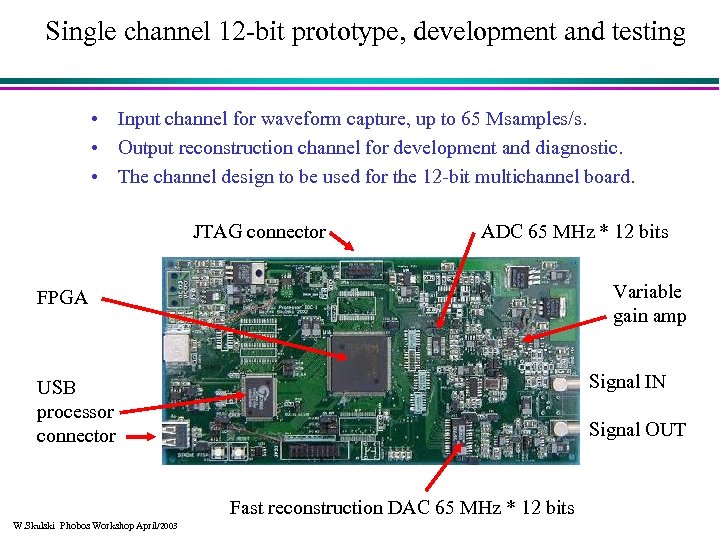

Single channel 12 -bit prototype, development and testing • Input channel for waveform capture, up to 65 Msamples/s. • Output reconstruction channel for development and diagnostic. • The channel design to be used for the 12 -bit multichannel board. JTAG connector ADC 65 MHz * 12 bits Variable gain amp FPGA Signal IN USB processor connector Signal OUT Fast reconstruction DAC 65 MHz * 12 bits W. Skulski Phobos Workshop April/2003

Single channel 12 -bit prototype, development and testing • Input channel for waveform capture, up to 65 Msamples/s. • Output reconstruction channel for development and diagnostic. • The channel design to be used for the 12 -bit multichannel board. JTAG connector ADC 65 MHz * 12 bits Variable gain amp FPGA Signal IN USB processor connector Signal OUT Fast reconstruction DAC 65 MHz * 12 bits W. Skulski Phobos Workshop April/2003

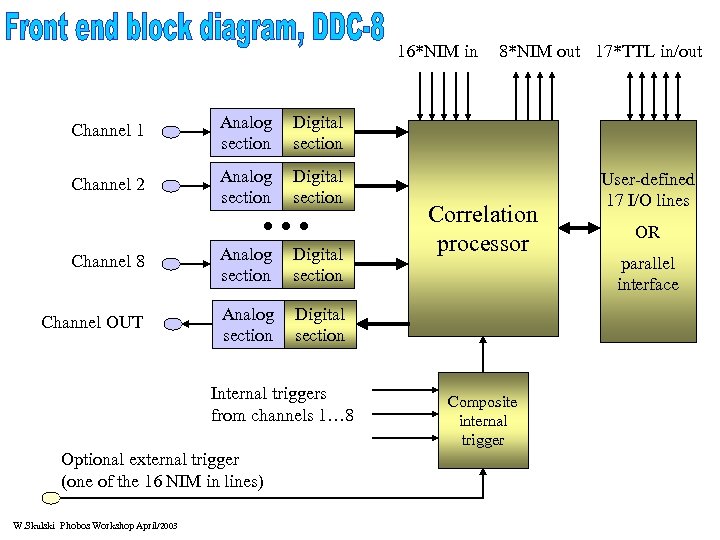

16*NIM in Channel 1 Analog section Channel 2 Analog section 8*NIM out 17*TTL in/out Digital section . . . Digital section Channel 8 Analog section Digital section Channel OUT Analog section Correlation processor Digital section Internal triggers from channels 1… 8 Optional external trigger (one of the 16 NIM in lines) W. Skulski Phobos Workshop April/2003 Composite internal trigger User-defined 17 I/O lines OR parallel interface

16*NIM in Channel 1 Analog section Channel 2 Analog section 8*NIM out 17*TTL in/out Digital section . . . Digital section Channel 8 Analog section Digital section Channel OUT Analog section Correlation processor Digital section Internal triggers from channels 1… 8 Optional external trigger (one of the 16 NIM in lines) W. Skulski Phobos Workshop April/2003 Composite internal trigger User-defined 17 I/O lines OR parallel interface

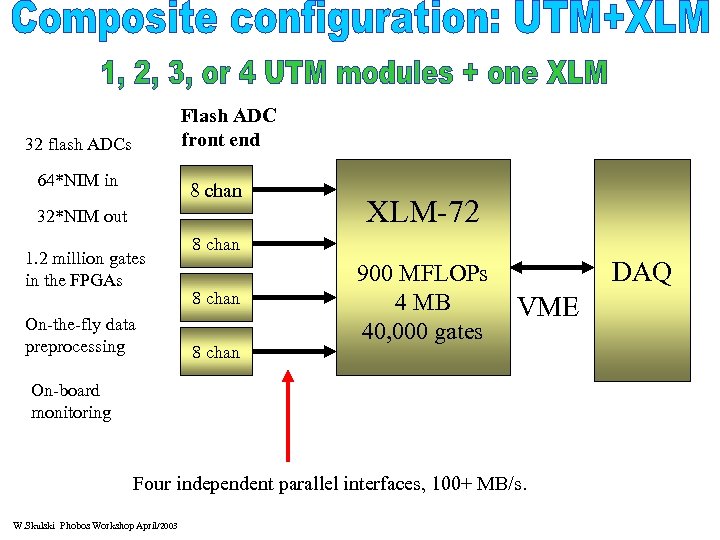

Flash ADC front end 32 flash ADCs 64*NIM in 8 chan 32*NIM out 1. 2 million gates in the FPGAs On-the-fly data preprocessing XLM-72 8 chan 900 MFLOPs 4 MB 40, 000 gates DAQ VME On-board monitoring Four independent parallel interfaces, 100+ MB/s. W. Skulski Phobos Workshop April/2003

Flash ADC front end 32 flash ADCs 64*NIM in 8 chan 32*NIM out 1. 2 million gates in the FPGAs On-the-fly data preprocessing XLM-72 8 chan 900 MFLOPs 4 MB 40, 000 gates DAQ VME On-board monitoring Four independent parallel interfaces, 100+ MB/s. W. Skulski Phobos Workshop April/2003

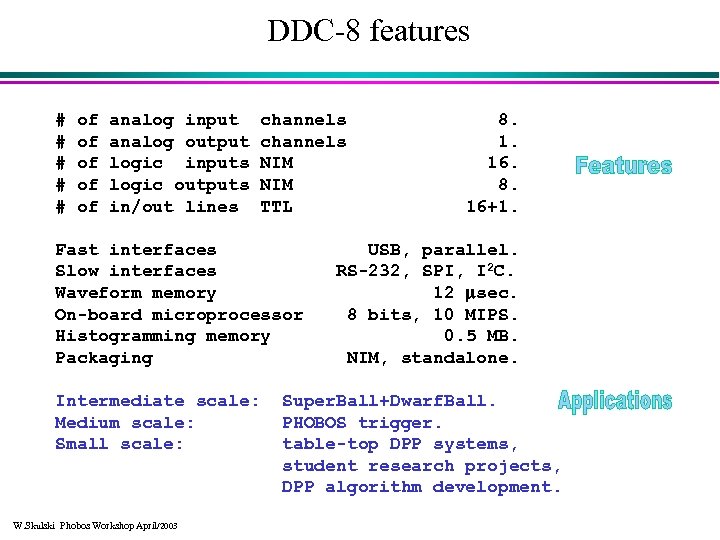

DDC-8 features # # # of of of analog input analog output logic inputs logic outputs in/out lines channels NIM TTL Fast interfaces Slow interfaces Waveform memory On-board microprocessor Histogramming memory Packaging Intermediate scale: Medium scale: Small scale: W. Skulski Phobos Workshop April/2003 8. 1. 16. 8. 16+1. USB, parallel. RS-232, SPI, I 2 C. 12 msec. 8 bits, 10 MIPS. 0. 5 MB. NIM, standalone. Super. Ball+Dwarf. Ball. PHOBOS trigger. table-top DPP systems, student research projects, DPP algorithm development.

DDC-8 features # # # of of of analog input analog output logic inputs logic outputs in/out lines channels NIM TTL Fast interfaces Slow interfaces Waveform memory On-board microprocessor Histogramming memory Packaging Intermediate scale: Medium scale: Small scale: W. Skulski Phobos Workshop April/2003 8. 1. 16. 8. 16+1. USB, parallel. RS-232, SPI, I 2 C. 12 msec. 8 bits, 10 MIPS. 0. 5 MB. NIM, standalone. Super. Ball+Dwarf. Ball. PHOBOS trigger. table-top DPP systems, student research projects, DPP algorithm development.

Response to scintillation pulses • DDC-8 firmware is under development. • Results obtained with DDC-1, 48 MHz @ 12 bits. • Very fast plastic BC-404: tpulse < tsampling. • Na. I(Tl): tpulse > tsampling. • Cs. I(Tl): particle identification. • Phoswich: two-component FAST-SLOW pulses. W. Skulski Phobos Workshop April/2003

Response to scintillation pulses • DDC-8 firmware is under development. • Results obtained with DDC-1, 48 MHz @ 12 bits. • Very fast plastic BC-404: tpulse < tsampling. • Na. I(Tl): tpulse > tsampling. • Cs. I(Tl): particle identification. • Phoswich: two-component FAST-SLOW pulses. W. Skulski Phobos Workshop April/2003

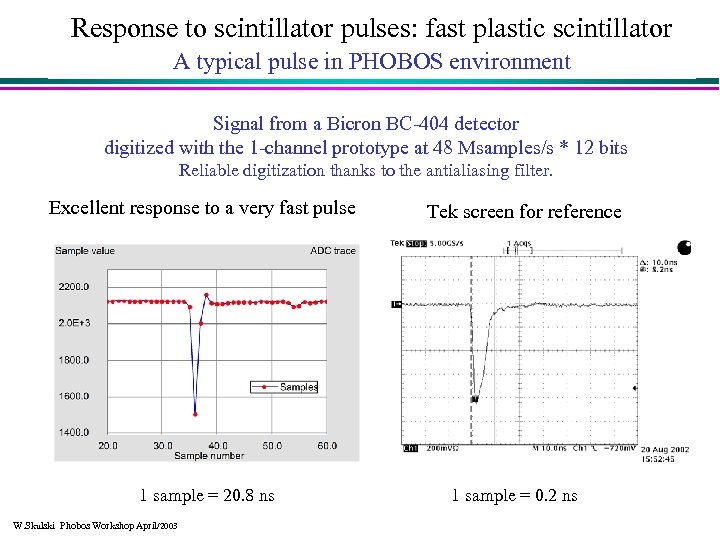

Response to scintillator pulses: fast plastic scintillator A typical pulse in PHOBOS environment Signal from a Bicron BC-404 detector digitized with the 1 -channel prototype at 48 Msamples/s * 12 bits Reliable digitization thanks to the antialiasing filter. Excellent response to a very fast pulse 1 sample = 20. 8 ns W. Skulski Phobos Workshop April/2003 Tek screen for reference 1 sample = 0. 2 ns

Response to scintillator pulses: fast plastic scintillator A typical pulse in PHOBOS environment Signal from a Bicron BC-404 detector digitized with the 1 -channel prototype at 48 Msamples/s * 12 bits Reliable digitization thanks to the antialiasing filter. Excellent response to a very fast pulse 1 sample = 20. 8 ns W. Skulski Phobos Workshop April/2003 Tek screen for reference 1 sample = 0. 2 ns

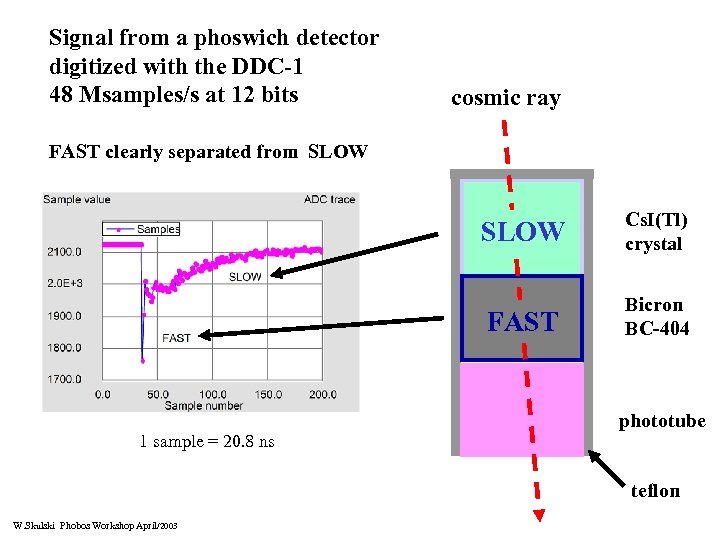

Signal from a phoswich detector digitized with the DDC-1 48 Msamples/s at 12 bits cosmic ray FAST clearly separated from SLOW FAST 1 sample = 20. 8 ns Cs. I(Tl) crystal Bicron BC-404 phototube teflon W. Skulski Phobos Workshop April/2003

Signal from a phoswich detector digitized with the DDC-1 48 Msamples/s at 12 bits cosmic ray FAST clearly separated from SLOW FAST 1 sample = 20. 8 ns Cs. I(Tl) crystal Bicron BC-404 phototube teflon W. Skulski Phobos Workshop April/2003

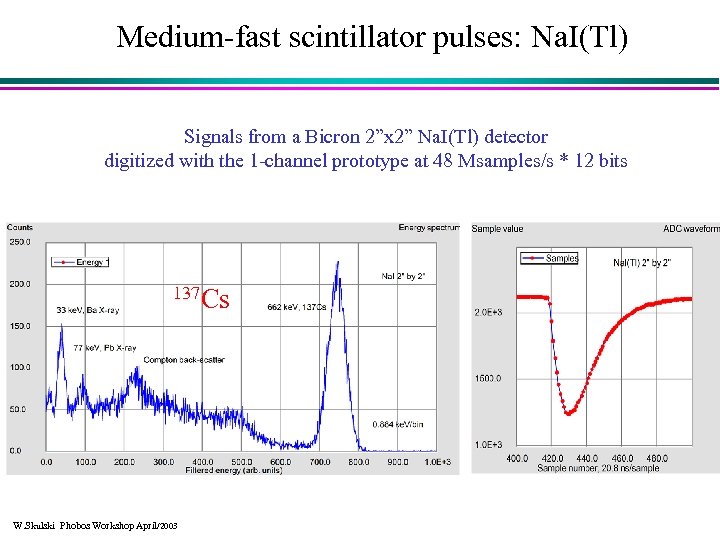

Medium-fast scintillator pulses: Na. I(Tl) Signals from a Bicron 2”x 2” Na. I(Tl) detector digitized with the 1 -channel prototype at 48 Msamples/s * 12 bits 137 Cs W. Skulski Phobos Workshop April/2003

Medium-fast scintillator pulses: Na. I(Tl) Signals from a Bicron 2”x 2” Na. I(Tl) detector digitized with the 1 -channel prototype at 48 Msamples/s * 12 bits 137 Cs W. Skulski Phobos Workshop April/2003

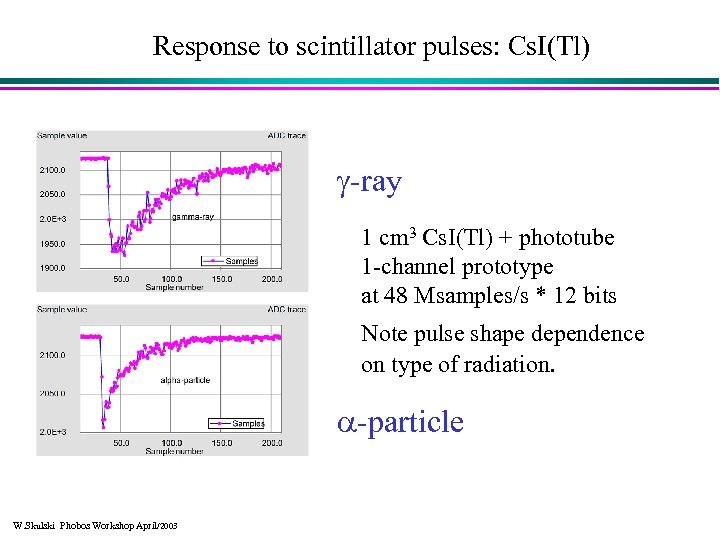

Response to scintillator pulses: Cs. I(Tl) g-ray 1 cm 3 Cs. I(Tl) + phototube 1 -channel prototype at 48 Msamples/s * 12 bits Note pulse shape dependence on type of radiation. a-particle W. Skulski Phobos Workshop April/2003

Response to scintillator pulses: Cs. I(Tl) g-ray 1 cm 3 Cs. I(Tl) + phototube 1 -channel prototype at 48 Msamples/s * 12 bits Note pulse shape dependence on type of radiation. a-particle W. Skulski Phobos Workshop April/2003

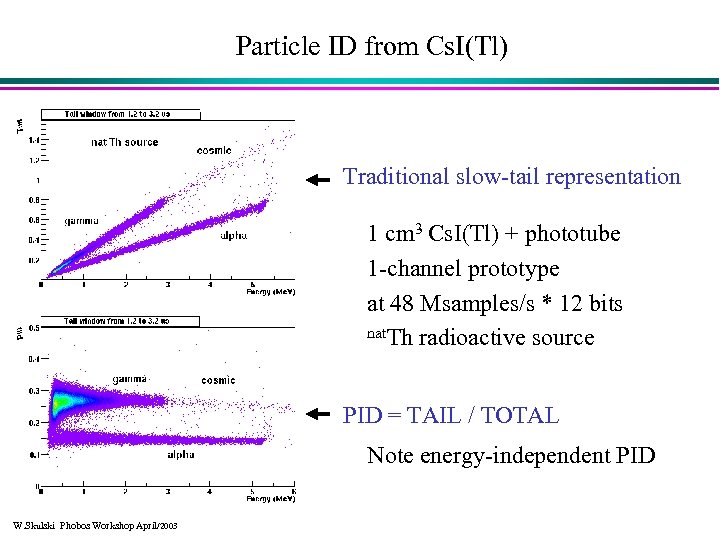

Particle ID from Cs. I(Tl) Traditional slow-tail representation 1 cm 3 Cs. I(Tl) + phototube 1 -channel prototype at 48 Msamples/s * 12 bits nat. Th radioactive source PID = TAIL / TOTAL Note energy-independent PID W. Skulski Phobos Workshop April/2003

Particle ID from Cs. I(Tl) Traditional slow-tail representation 1 cm 3 Cs. I(Tl) + phototube 1 -channel prototype at 48 Msamples/s * 12 bits nat. Th radioactive source PID = TAIL / TOTAL Note energy-independent PID W. Skulski Phobos Workshop April/2003

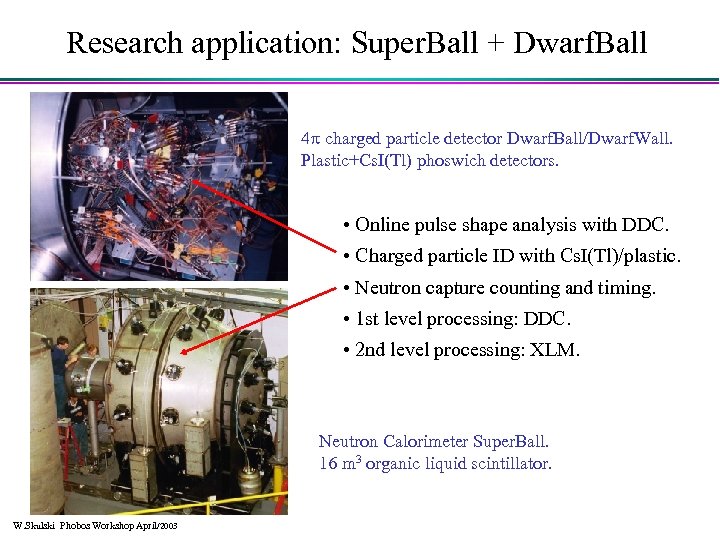

Research application: Super. Ball + Dwarf. Ball 4 p charged particle detector Dwarf. Ball/Dwarf. Wall. Plastic+Cs. I(Tl) phoswich detectors. • Online pulse shape analysis with DDC. • Charged particle ID with Cs. I(Tl)/plastic. • Neutron capture counting and timing. • 1 st level processing: DDC. • 2 nd level processing: XLM. Neutron Calorimeter Super. Ball. 16 m 3 organic liquid scintillator. W. Skulski Phobos Workshop April/2003

Research application: Super. Ball + Dwarf. Ball 4 p charged particle detector Dwarf. Ball/Dwarf. Wall. Plastic+Cs. I(Tl) phoswich detectors. • Online pulse shape analysis with DDC. • Charged particle ID with Cs. I(Tl)/plastic. • Neutron capture counting and timing. • 1 st level processing: DDC. • 2 nd level processing: XLM. Neutron Calorimeter Super. Ball. 16 m 3 organic liquid scintillator. W. Skulski Phobos Workshop April/2003

Online trigger PHOBOS @ RHIC • Analog signals: Paddles, Cerenkov, ZDC. • Logic signals from conventional NIM. • 1 st level processing: DDC. • 2 nd level processing: XLM, optional. • Accept/reject event within about 1 msec. Centrality from paddle and ZDC. Vertex definition from TACs. T 0 OR Dt, Paddle Dt, ZDC Dt. Vertex and centrality definition in real time W. Skulski Phobos Workshop April/2003

Online trigger PHOBOS @ RHIC • Analog signals: Paddles, Cerenkov, ZDC. • Logic signals from conventional NIM. • 1 st level processing: DDC. • 2 nd level processing: XLM, optional. • Accept/reject event within about 1 msec. Centrality from paddle and ZDC. Vertex definition from TACs. T 0 OR Dt, Paddle Dt, ZDC Dt. Vertex and centrality definition in real time W. Skulski Phobos Workshop April/2003

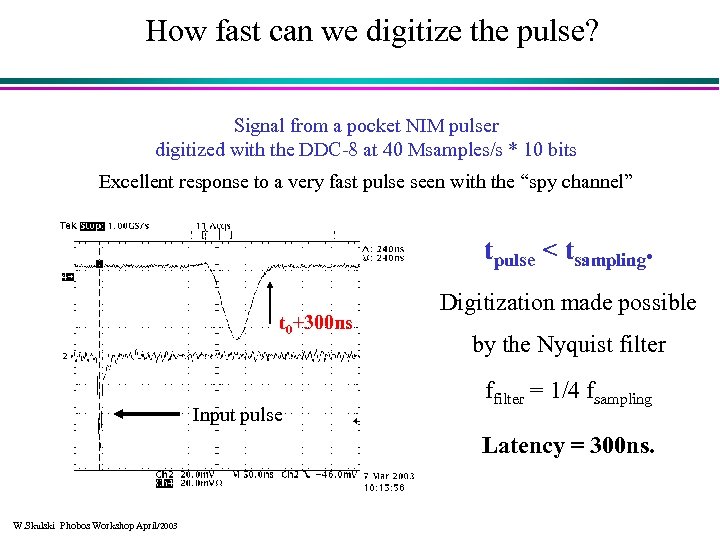

How fast can we digitize the pulse? Signal from a pocket NIM pulser digitized with the DDC-8 at 40 Msamples/s * 10 bits Excellent response to a very fast pulse seen with the “spy channel” tpulse < tsampling. t 0+300 ns Input pulse Digitization made possible by the Nyquist filter ffilter = 1/4 fsampling Latency = 300 ns. W. Skulski Phobos Workshop April/2003

How fast can we digitize the pulse? Signal from a pocket NIM pulser digitized with the DDC-8 at 40 Msamples/s * 10 bits Excellent response to a very fast pulse seen with the “spy channel” tpulse < tsampling. t 0+300 ns Input pulse Digitization made possible by the Nyquist filter ffilter = 1/4 fsampling Latency = 300 ns. W. Skulski Phobos Workshop April/2003

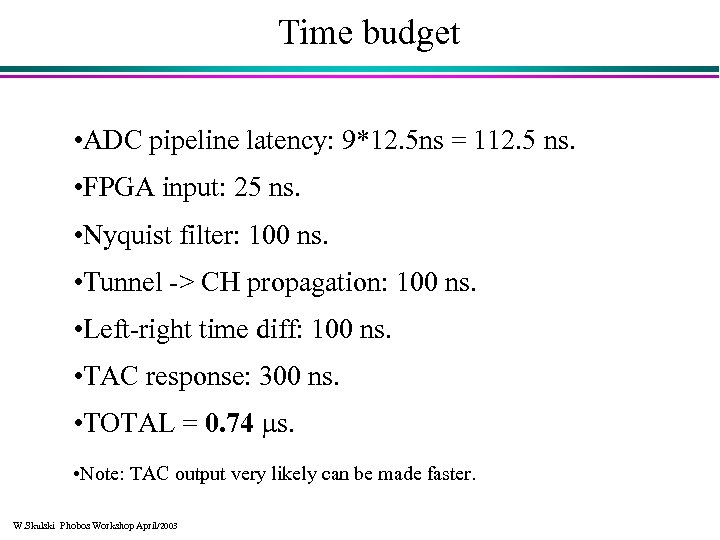

Time budget • ADC pipeline latency: 9*12. 5 ns = 112. 5 ns. • FPGA input: 25 ns. • Nyquist filter: 100 ns. • Tunnel -> CH propagation: 100 ns. • Left-right time diff: 100 ns. • TAC response: 300 ns. • TOTAL = 0. 74 ms. • Note: TAC output very likely can be made faster. W. Skulski Phobos Workshop April/2003

Time budget • ADC pipeline latency: 9*12. 5 ns = 112. 5 ns. • FPGA input: 25 ns. • Nyquist filter: 100 ns. • Tunnel -> CH propagation: 100 ns. • Left-right time diff: 100 ns. • TAC response: 300 ns. • TOTAL = 0. 74 ms. • Note: TAC output very likely can be made faster. W. Skulski Phobos Workshop April/2003

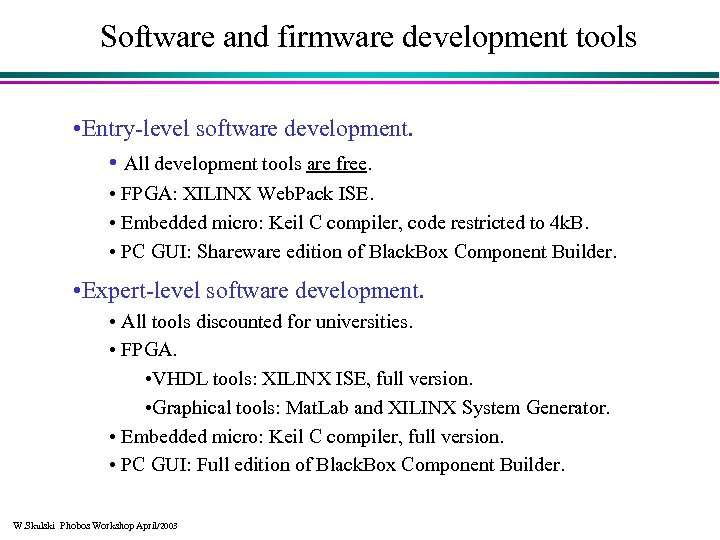

Software and firmware development tools • Entry-level software development. • All development tools are free. • FPGA: XILINX Web. Pack ISE. • Embedded micro: Keil C compiler, code restricted to 4 k. B. • PC GUI: Shareware edition of Black. Box Component Builder. • Expert-level software development. • All tools discounted for universities. • FPGA. • VHDL tools: XILINX ISE, full version. • Graphical tools: Mat. Lab and XILINX System Generator. • Embedded micro: Keil C compiler, full version. • PC GUI: Full edition of Black. Box Component Builder. W. Skulski Phobos Workshop April/2003

Software and firmware development tools • Entry-level software development. • All development tools are free. • FPGA: XILINX Web. Pack ISE. • Embedded micro: Keil C compiler, code restricted to 4 k. B. • PC GUI: Shareware edition of Black. Box Component Builder. • Expert-level software development. • All tools discounted for universities. • FPGA. • VHDL tools: XILINX ISE, full version. • Graphical tools: Mat. Lab and XILINX System Generator. • Embedded micro: Keil C compiler, full version. • PC GUI: Full edition of Black. Box Component Builder. W. Skulski Phobos Workshop April/2003

Obstacles and showstoppers • Obstacles. • Firmware & software development takes time. • Need an expert at the Phobos end. • Only one board exists, two more being assembled, all are already booked. • The 1 st board has not been fully tested yet. • Showstoppers? • Does Phobos need this tool? • Can Phobos designate an expert? • Recent deep cut in funding cannot be ignored. W. Skulski Phobos Workshop April/2003

Obstacles and showstoppers • Obstacles. • Firmware & software development takes time. • Need an expert at the Phobos end. • Only one board exists, two more being assembled, all are already booked. • The 1 st board has not been fully tested yet. • Showstoppers? • Does Phobos need this tool? • Can Phobos designate an expert? • Recent deep cut in funding cannot be ignored. W. Skulski Phobos Workshop April/2003

Summary • The technology is under control. • Glitches, if any, will be resolved. • One DDC-8 assembled, works OK, but not yet fully tested. • Two more boards being assembled. • Firmware & software development will take time. • A possible showstopper: recent cut in funding. • Does Phobos need this device? • My personal belief: if there is need, the expert will step forward. • The situation looks good, but not hopeless. W. Skulski Phobos Workshop April/2003

Summary • The technology is under control. • Glitches, if any, will be resolved. • One DDC-8 assembled, works OK, but not yet fully tested. • Two more boards being assembled. • Firmware & software development will take time. • A possible showstopper: recent cut in funding. • Does Phobos need this device? • My personal belief: if there is need, the expert will step forward. • The situation looks good, but not hopeless. W. Skulski Phobos Workshop April/2003