cfd61839a04e957b804b6ac6e426ff33.ppt

- Количество слайдов: 31

Development of a System-On-Chip Extensible Network Processor and debugging using Identify John W. Lockwood and Chris Zuver Applied Research Laboratory : Reconfigurable Network Group http: //www. arl. wustl. edu/projects/fpx/reconfig. htm lockwood@arl. wustl. edu cz 2@arl. wustl. edu Extensible Networking Platform 1 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 1

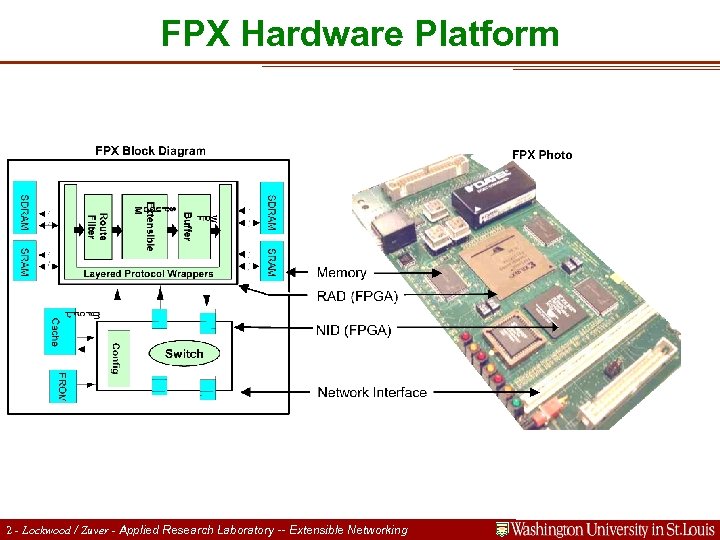

FPX Hardware Platform Extensible Networking Platform 2 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 2

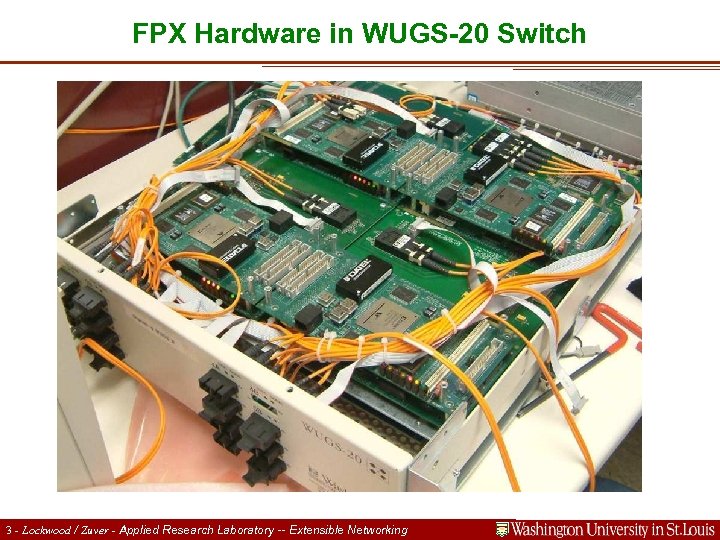

FPX Hardware in WUGS-20 Switch Extensible Networking Platform 3 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 3

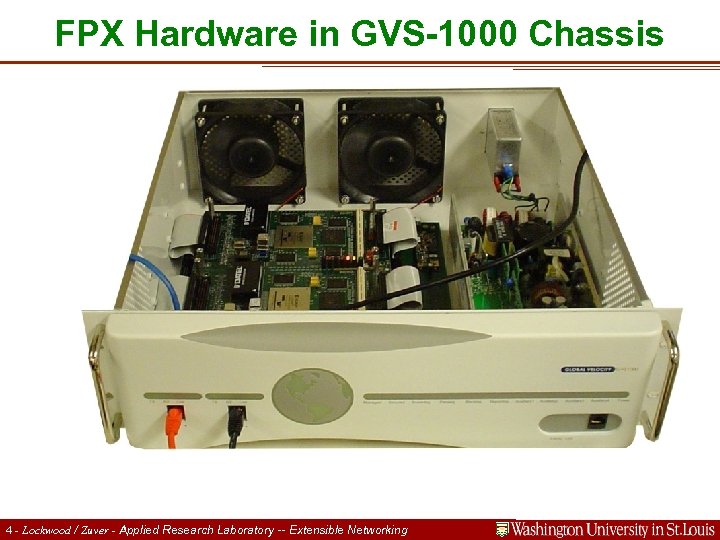

FPX Hardware in GVS-1000 Chassis Extensible Networking Platform 4 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 4

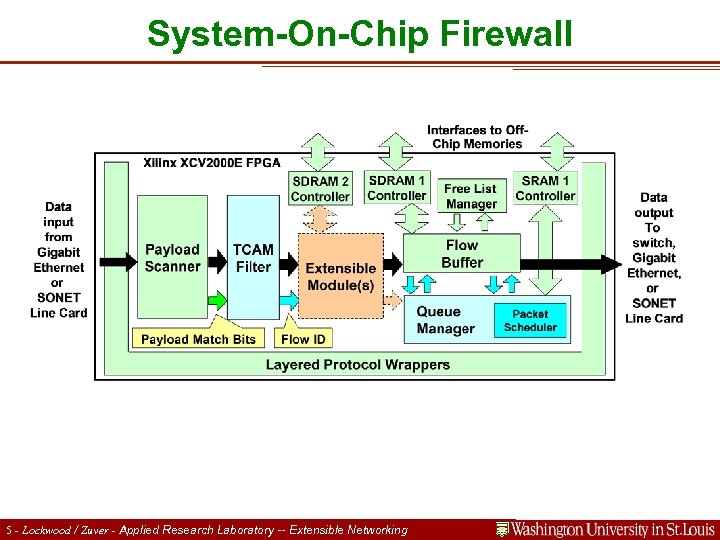

System-On-Chip Firewall Extensible Networking Platform 5 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 5

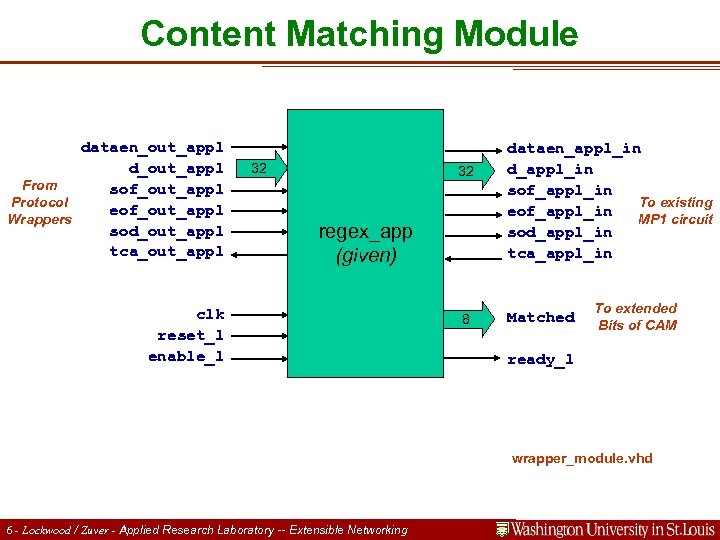

Content Matching Module dataen_out_appl d_out_appl From sof_out_appl Protocol eof_out_appl Wrappers sod_out_appl tca_out_appl 32 32 regex_app (given) clk reset_l enable_l 8 dataen_appl_in d_appl_in sof_appl_in To existing eof_appl_in MP 1 circuit sod_appl_in tca_appl_in Matched To extended Bits of CAM ready_l wrapper_module. vhd Extensible Networking Platform 6 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 6

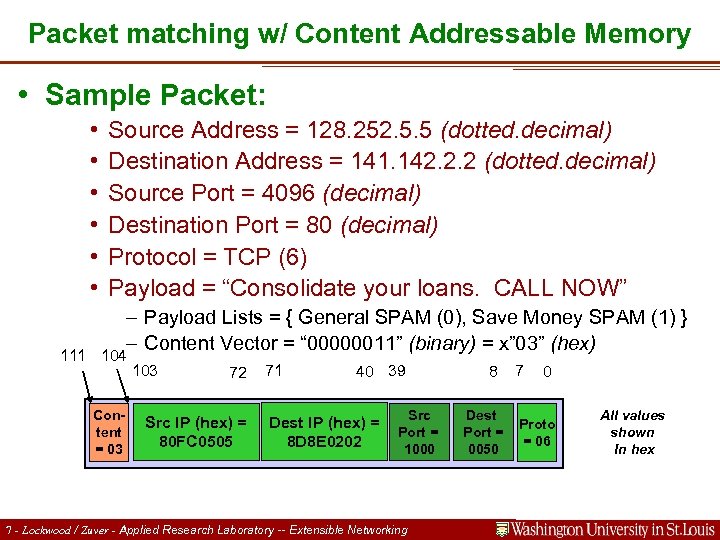

Packet matching w/ Content Addressable Memory • Sample Packet: • • • Source Address = 128. 252. 5. 5 (dotted. decimal) Destination Address = 141. 142. 2. 2 (dotted. decimal) Source Port = 4096 (decimal) Destination Port = 80 (decimal) Protocol = TCP (6) Payload = “Consolidate your loans. CALL NOW” – Payload Lists = { General SPAM (0), Save Money SPAM (1) } – Content Vector = “ 00000011” (binary) = x” 03” (hex) 111 104 Content = 03 103 72 Src IP (hex) = 80 FC 0505 71 40 39 Dest IP (hex) = 8 D 8 E 0202 Src Port = 1000 Extensible Networking Platform 7 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 8 Dest Port = 0050 7 0 Proto = 06 All values shown In hex 7

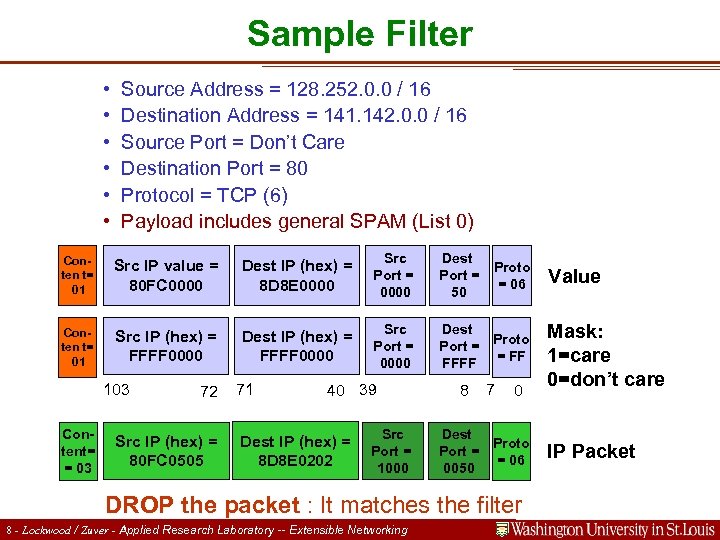

Sample Filter • • • Source Address = 128. 252. 0. 0 / 16 Destination Address = 141. 142. 0. 0 / 16 Source Port = Don’t Care Destination Port = 80 Protocol = TCP (6) Payload includes general SPAM (List 0) Conten t= 01 Src IP value = 80 FC 0000 Dest IP (hex) = 8 D 8 E 0000 Src Port = 0000 Dest Port = 50 Conten t= 01 Src IP (hex) = FFFF 0000 Dest IP (hex) = FFFF 0000 Src Port = 0000 Dest Proto Port = = FF FFFF 103 Content= = 03 72 Src IP (hex) = 80 FC 0505 71 40 39 Dest IP (hex) = 8 D 8 E 0202 Src Port = 1000 8 Dest Port = 0050 Proto = 06 7 0 Proto = 06 Value Mask: 1=care 0=don’t care IP Packet DROP the packet : It matches the filter Extensible Networking Platform 8 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking 8

![Packet Classifier with Flow. ID 16 bits 112 bits Flow ID [1] CAM MASK Packet Classifier with Flow. ID 16 bits 112 bits Flow ID [1] CAM MASK](https://present5.com/presentation/cfd61839a04e957b804b6ac6e426ff33/image-9.jpg)

Packet Classifier with Flow. ID 16 bits 112 bits Flow ID [1] CAM MASK [1] CAM VALUE [1] Flow ID [2] CAM MASK [2] CAM VALUE [2] 16 bits - - CAM Table - - Flow ID [3] CAM MASK [3] CAM VALUE [3] Resulting Flow Identifier . . . Flow ID [N] . . . CAM MASK [N] CAM VALUE [N] Bits in IP Header Flow List Priority Encoder Mask Matchers Payload Match Bits Value Comparators Extensible Networking Platform 9 - Lockwood / Zuver - Applied Research Laboratory -- Extensible Networking Source Address Source Port Destination Address Protocol Dest. Port 9

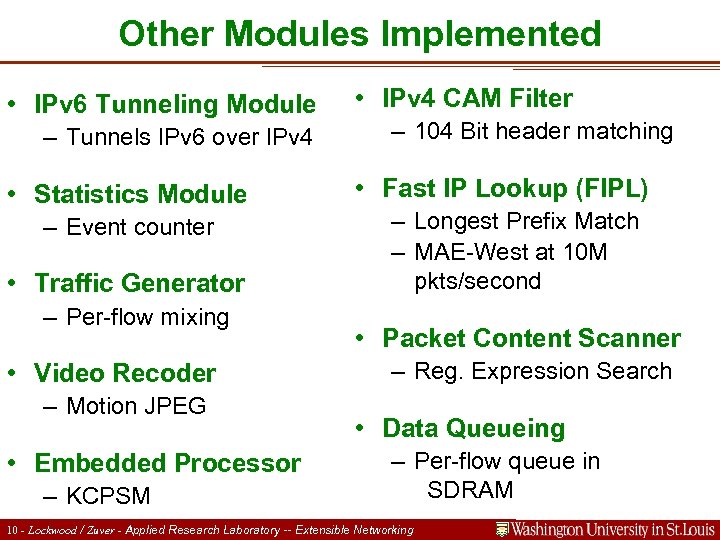

Other Modules Implemented • IPv 6 Tunneling Module – Tunnels IPv 6 over IPv 4 • Statistics Module – Event counter • Traffic Generator – Per-flow mixing • Video Recoder – Motion JPEG • Embedded Processor – KCPSM • IPv 4 CAM Filter – 104 Bit header matching • Fast IP Lookup (FIPL) – Longest Prefix Match – MAE-West at 10 M pkts/second • Packet Content Scanner – Reg. Expression Search • Data Queueing – Per-flow queue in SDRAM Extensible Zuver - Applied Platform 10 - Lockwood / Networking Research Laboratory -- Extensible Networking 10

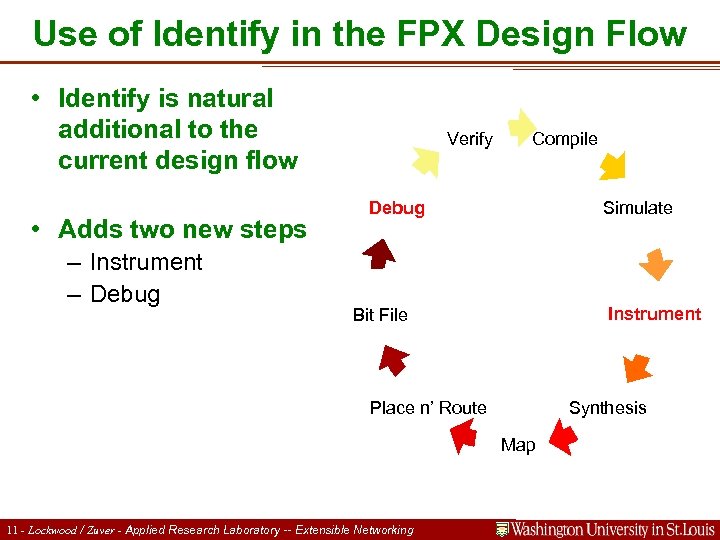

Use of Identify in the FPX Design Flow • Identify is natural additional to the current design flow • Adds two new steps – Instrument – Debug Verify Compile Simulate Debug Instrument Bit File Synthesis Place n’ Route Map Extensible Zuver - Applied Platform 11 - Lockwood / Networking Research Laboratory -- Extensible Networking 11

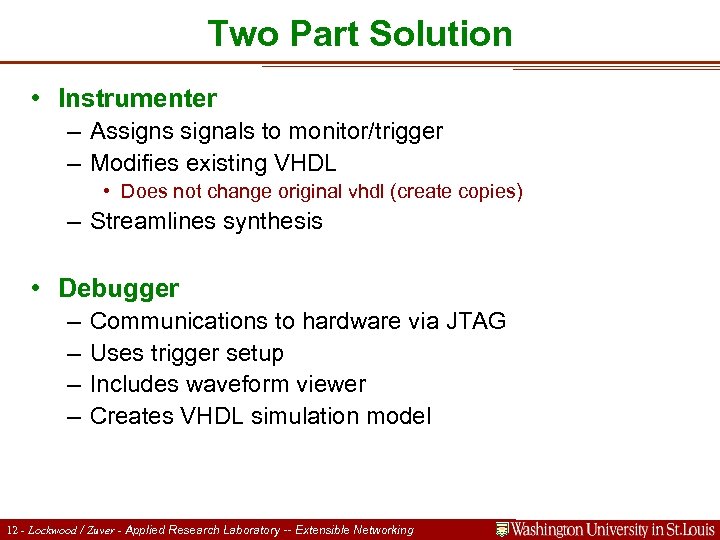

Two Part Solution • Instrumenter – Assigns signals to monitor/trigger – Modifies existing VHDL • Does not change original vhdl (create copies) – Streamlines synthesis • Debugger – – Communications to hardware via JTAG Uses trigger setup Includes waveform viewer Creates VHDL simulation model Extensible Zuver - Applied Platform 12 - Lockwood / Networking Research Laboratory -- Extensible Networking 12

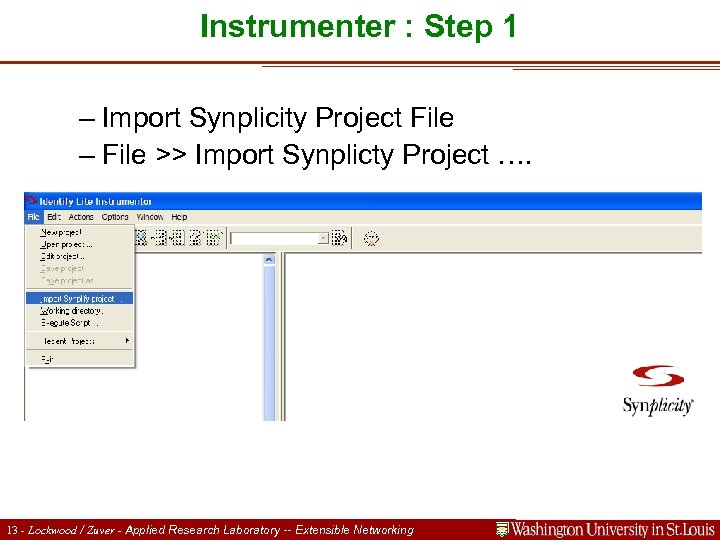

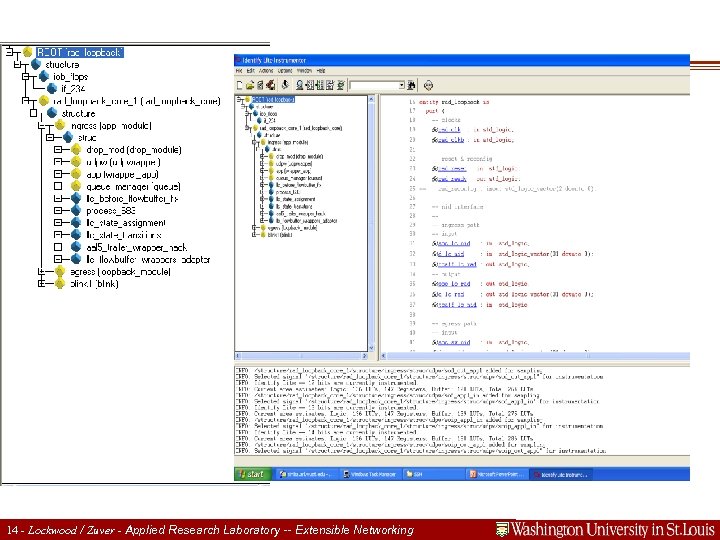

Instrumenter : Step 1 – Import Synplicity Project File – File >> Import Synplicty Project …. Extensible Zuver - Applied Platform 13 - Lockwood / Networking Research Laboratory -- Extensible Networking 13

Extensible Zuver - Applied Platform 14 - Lockwood / Networking Research Laboratory -- Extensible Networking 14

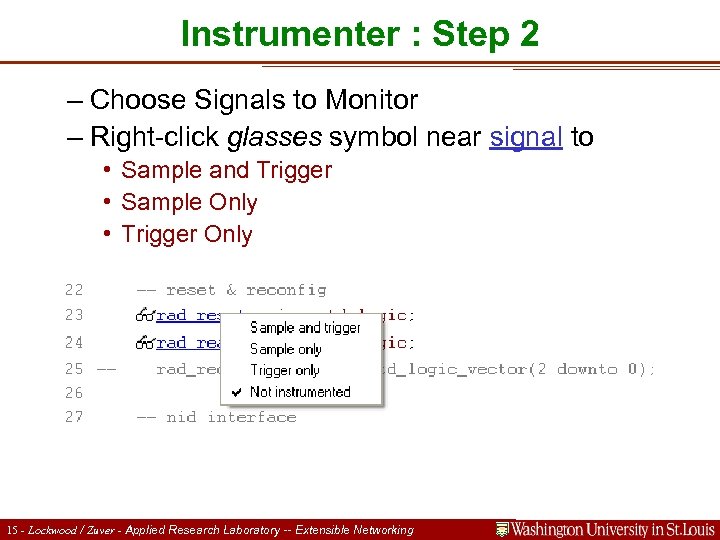

Instrumenter : Step 2 – Choose Signals to Monitor – Right-click glasses symbol near signal to • Sample and Trigger • Sample Only • Trigger Only Extensible Zuver - Applied Platform 15 - Lockwood / Networking Research Laboratory -- Extensible Networking 15

Instrumenter : Step 3 – Set Options – Click Edit IICE Options Extensible Zuver - Applied Platform 16 - Lockwood / Networking Research Laboratory -- Extensible Networking 16

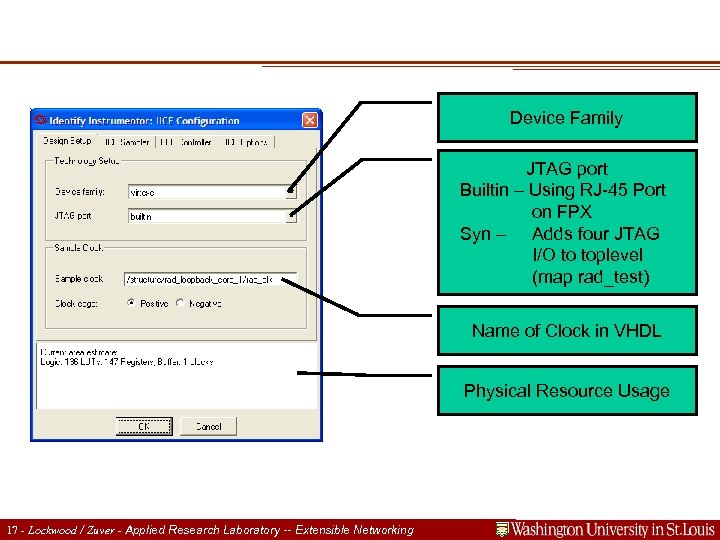

Device Family JTAG port Builtin – Using RJ-45 Port on FPX Syn – Adds four JTAG I/O to toplevel (map rad_test) Name of Clock in VHDL Physical Resource Usage Extensible Zuver - Applied Platform 17 - Lockwood / Networking Research Laboratory -- Extensible Networking 17

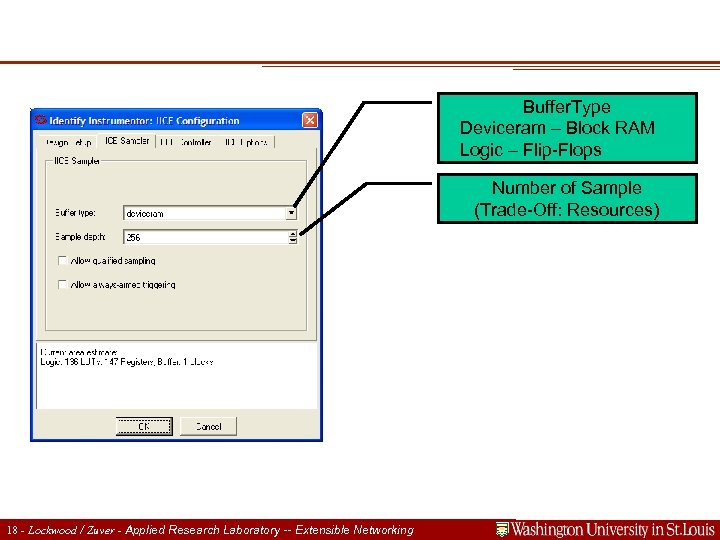

Buffer. Type Deviceram – Block RAM Logic – Flip-Flops Number of Sample (Trade-Off: Resources) Extensible Zuver - Applied Platform 18 - Lockwood / Networking Research Laboratory -- Extensible Networking 18

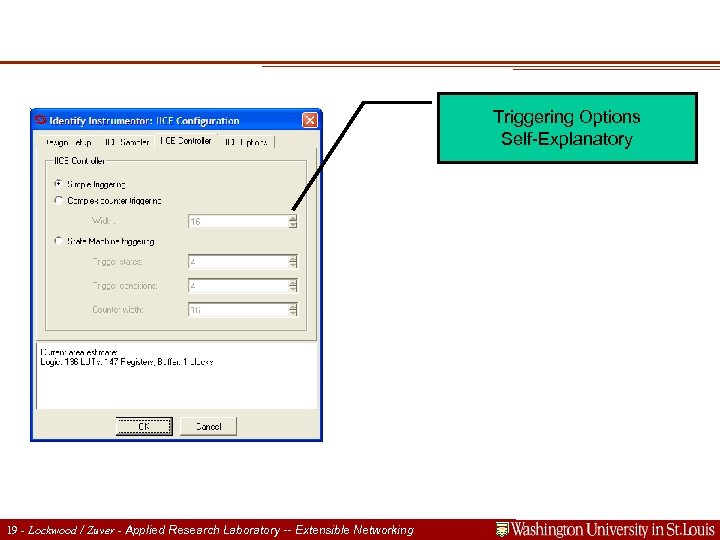

Triggering Options Self-Explanatory Extensible Zuver - Applied Platform 19 - Lockwood / Networking Research Laboratory -- Extensible Networking 19

Instrumenter : Step 4 – INSTRUMENT DESIGN – Click “Save and Instrument Current Project” Extensible Zuver - Applied Platform 20 - Lockwood / Networking Research Laboratory -- Extensible Networking 20

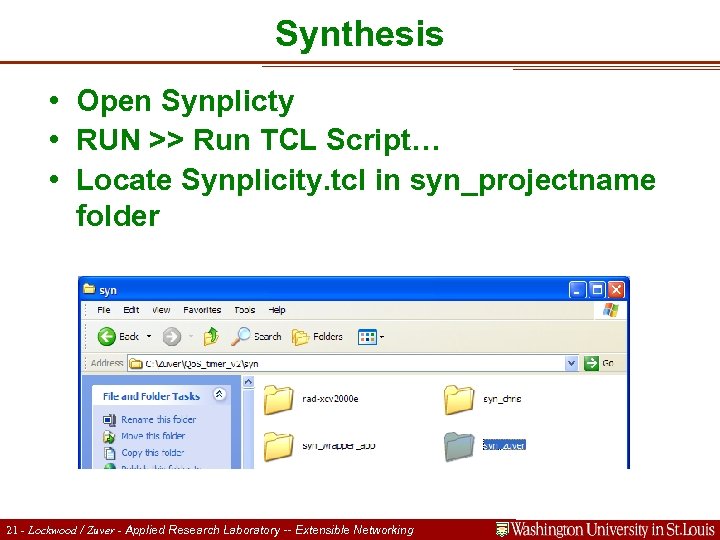

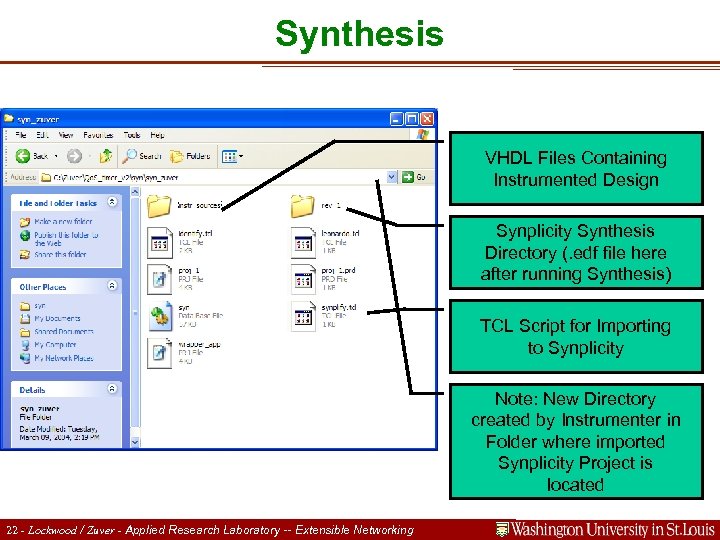

Synthesis • Open Synplicty • RUN >> Run TCL Script… • Locate Synplicity. tcl in syn_projectname folder Extensible Zuver - Applied Platform 21 - Lockwood / Networking Research Laboratory -- Extensible Networking 21

Synthesis VHDL Files Containing Instrumented Design Synplicity Synthesis Directory (. edf file here after running Synthesis) TCL Script for Importing to Synplicity Note: New Directory created by Instrumenter in Folder where imported Synplicity Project is located Extensible Zuver - Applied Platform 22 - Lockwood / Networking Research Laboratory -- Extensible Networking 22

Continue Design Flow • Add. edf file to build directory • Generate Bitfile like usual • Load Bitfile to FPX using NCHARGE – Make sure JTAG cable is unplugged • Connect JTAG Cable to FPX and PC running IDENTIFY (Parrallel JTAG) • Open IDENTIFY Debugger Extensible Zuver - Applied Platform 23 - Lockwood / Networking Research Laboratory -- Extensible Networking 23

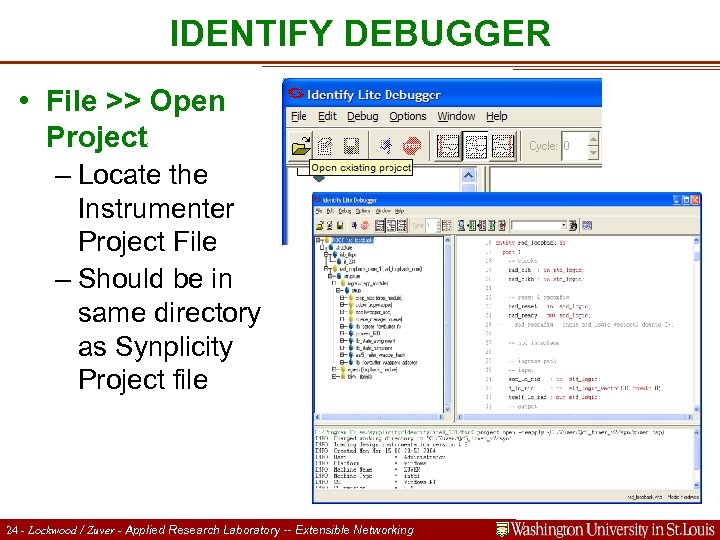

IDENTIFY DEBUGGER • File >> Open Project – Locate the Instrumenter Project File – Should be in same directory as Synplicity Project file Extensible Zuver - Applied Platform 24 - Lockwood / Networking Research Laboratory -- Extensible Networking 24

IDENTIFY DEBUGGER • Trigger – Locate and set Trigger Event – Right Click Signal Extensible Zuver - Applied Platform 25 - Lockwood / Networking Research Laboratory -- Extensible Networking 25

IDENTIFY DEBUGGER – Setup Project Options Extensible Zuver - Applied Platform 26 - Lockwood / Networking Research Laboratory -- Extensible Networking 26

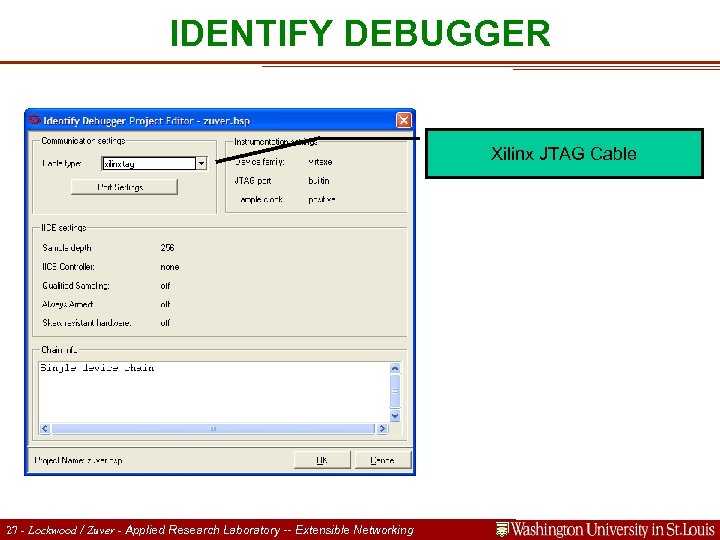

IDENTIFY DEBUGGER Xilinx JTAG Cable Extensible Zuver - Applied Platform 27 - Lockwood / Networking Research Laboratory -- Extensible Networking 27

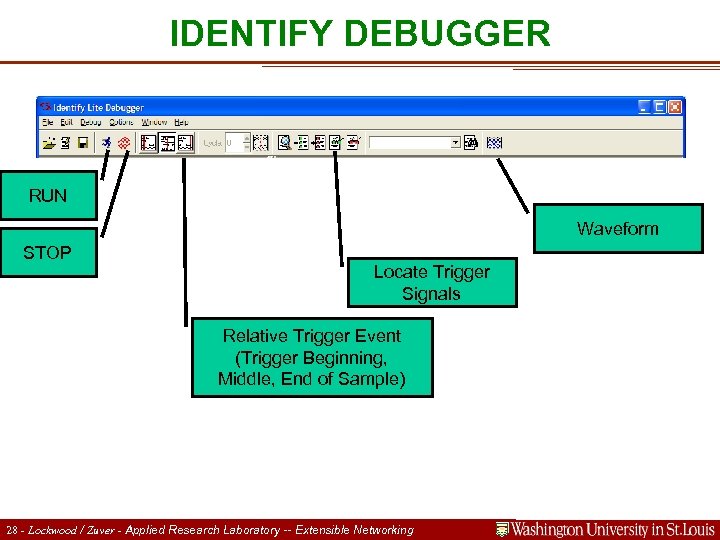

IDENTIFY DEBUGGER RUN Waveform STOP Locate Trigger Signals Relative Trigger Event (Trigger Beginning, Middle, End of Sample) Extensible Zuver - Applied Platform 28 - Lockwood / Networking Research Laboratory -- Extensible Networking 28

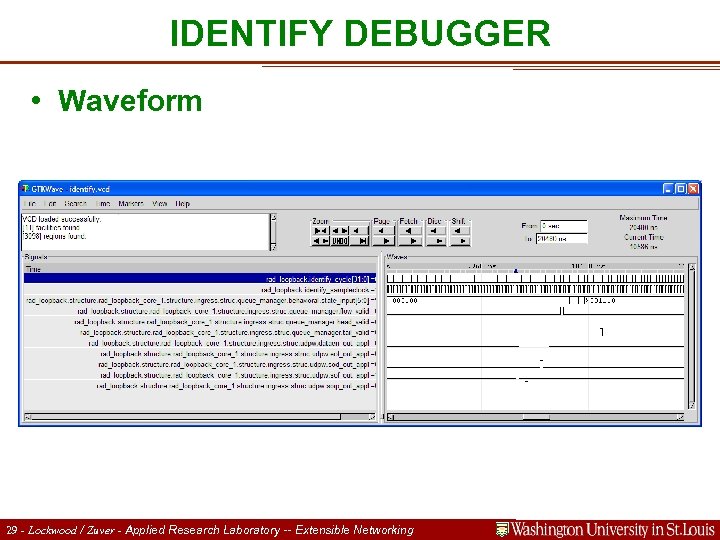

IDENTIFY DEBUGGER • Waveform Extensible Zuver - Applied Platform 29 - Lockwood / Networking Research Laboratory -- Extensible Networking 29

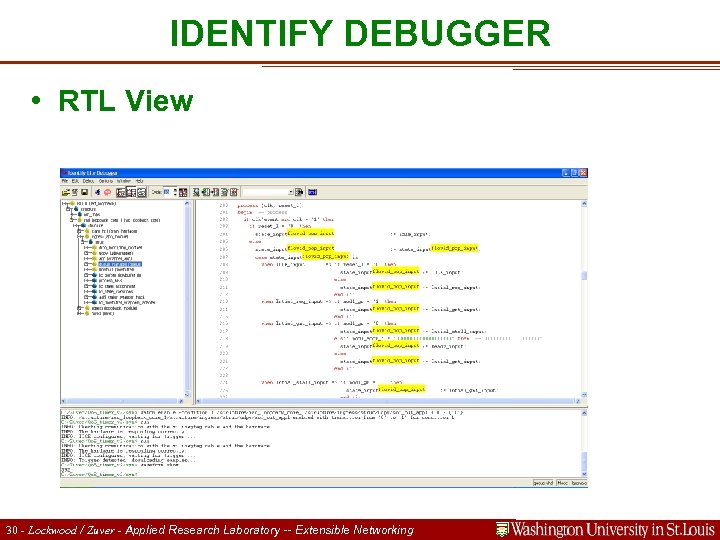

IDENTIFY DEBUGGER • RTL View Extensible Zuver - Applied Platform 30 - Lockwood / Networking Research Laboratory -- Extensible Networking 30

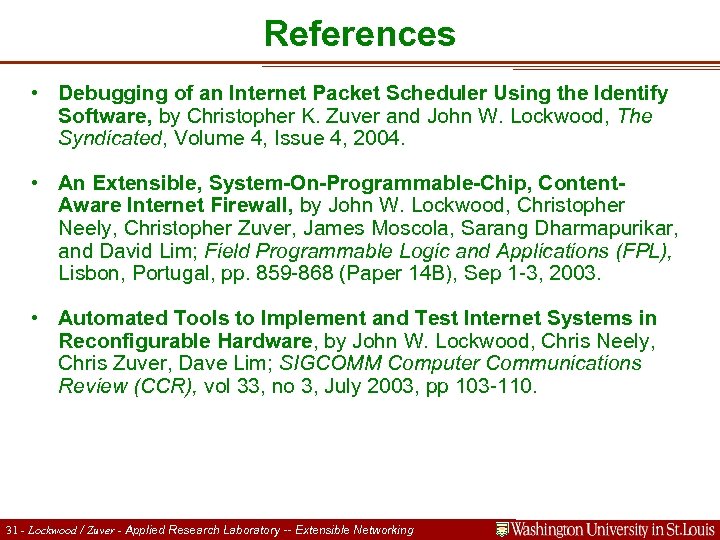

References • Debugging of an Internet Packet Scheduler Using the Identify Software, by Christopher K. Zuver and John W. Lockwood, The Syndicated, Volume 4, Issue 4, 2004. • An Extensible, System-On-Programmable-Chip, Content. Aware Internet Firewall, by John W. Lockwood, Christopher Neely, Christopher Zuver, James Moscola, Sarang Dharmapurikar, and David Lim; Field Programmable Logic and Applications (FPL), Lisbon, Portugal, pp. 859 -868 (Paper 14 B), Sep 1 -3, 2003. • Automated Tools to Implement and Test Internet Systems in Reconfigurable Hardware, by John W. Lockwood, Chris Neely, Chris Zuver, Dave Lim; SIGCOMM Computer Communications Review (CCR), vol 33, no 3, July 2003, pp 103 -110. Extensible Zuver - Applied Platform 31 - Lockwood / Networking Research Laboratory -- Extensible Networking 31

cfd61839a04e957b804b6ac6e426ff33.ppt