dffe3c1f5add2ea6da4110b546e4d619.ppt

- Количество слайдов: 36

Design Methodologies for System-on-A-Chip Allen C. -H. Wu Department of Computer Science Tsing Hua University Hsinchu, Taiwan 30043, ROC email: chunghaw@cs. nthu. edu. tw 1

Design Methodologies for System-on-A-Chip Allen C. -H. Wu Department of Computer Science Tsing Hua University Hsinchu, Taiwan 30043, ROC email: chunghaw@cs. nthu. edu. tw 1

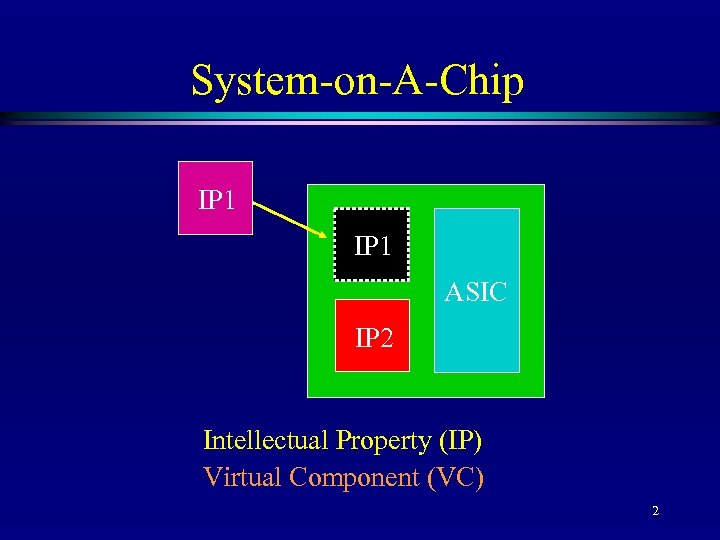

System-on-A-Chip IP 1 ASIC IP 2 Intellectual Property (IP) Virtual Component (VC) 2

System-on-A-Chip IP 1 ASIC IP 2 Intellectual Property (IP) Virtual Component (VC) 2

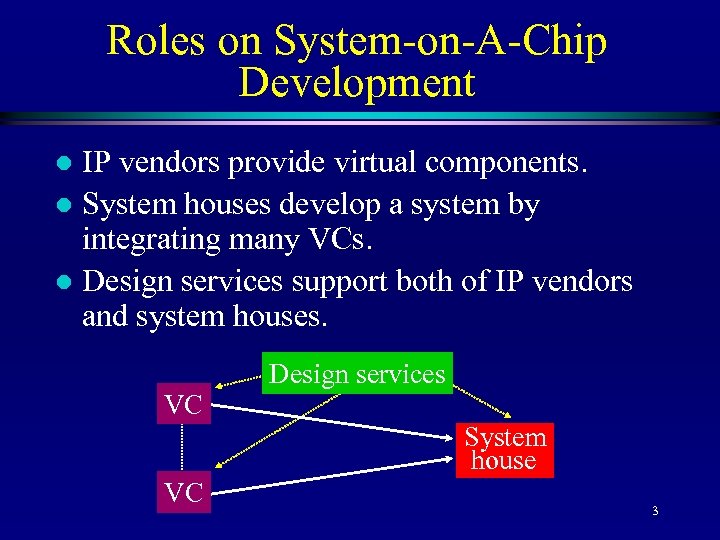

Roles on System-on-A-Chip Development IP vendors provide virtual components. l System houses develop a system by integrating many VCs. l Design services support both of IP vendors and system houses. l VC Design services System house VC 3

Roles on System-on-A-Chip Development IP vendors provide virtual components. l System houses develop a system by integrating many VCs. l Design services support both of IP vendors and system houses. l VC Design services System house VC 3

Design Methodologies IP vendors - design methodologies for application-specific virtual-component development. l System houses - design methodologies for system integration. l 4

Design Methodologies IP vendors - design methodologies for application-specific virtual-component development. l System houses - design methodologies for system integration. l 4

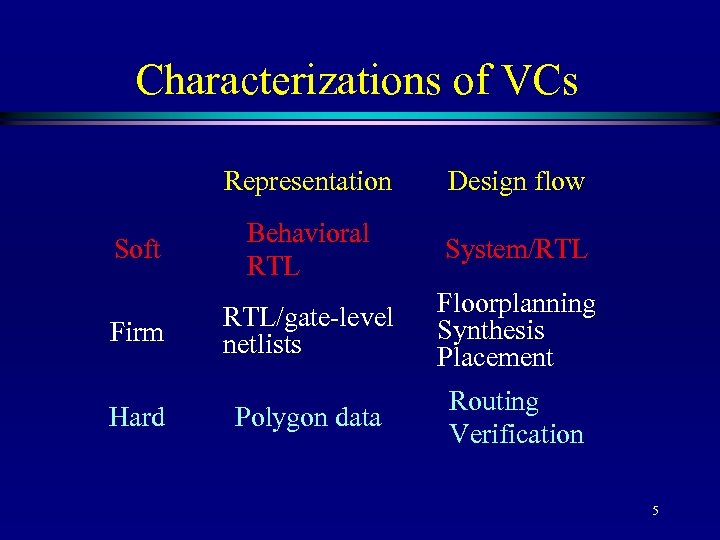

Characterizations of VCs Representation Design flow Soft Behavioral RTL System/RTL Firm RTL/gate-level netlists Floorplanning Synthesis Placement Polygon data Routing Verification Hard 5

Characterizations of VCs Representation Design flow Soft Behavioral RTL System/RTL Firm RTL/gate-level netlists Floorplanning Synthesis Placement Polygon data Routing Verification Hard 5

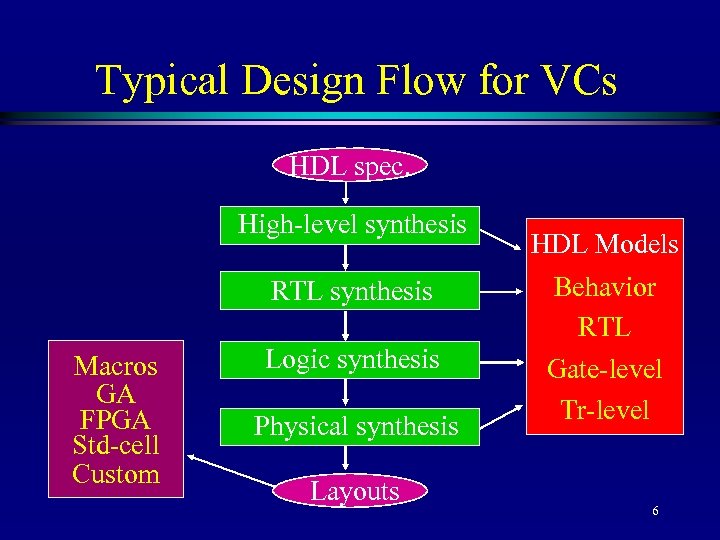

Typical Design Flow for VCs HDL spec. High-level synthesis RTL synthesis Macros GA FPGA Std-cell Custom Logic synthesis Physical synthesis Layouts HDL Models Behavior RTL Gate-level Tr-level 6

Typical Design Flow for VCs HDL spec. High-level synthesis RTL synthesis Macros GA FPGA Std-cell Custom Logic synthesis Physical synthesis Layouts HDL Models Behavior RTL Gate-level Tr-level 6

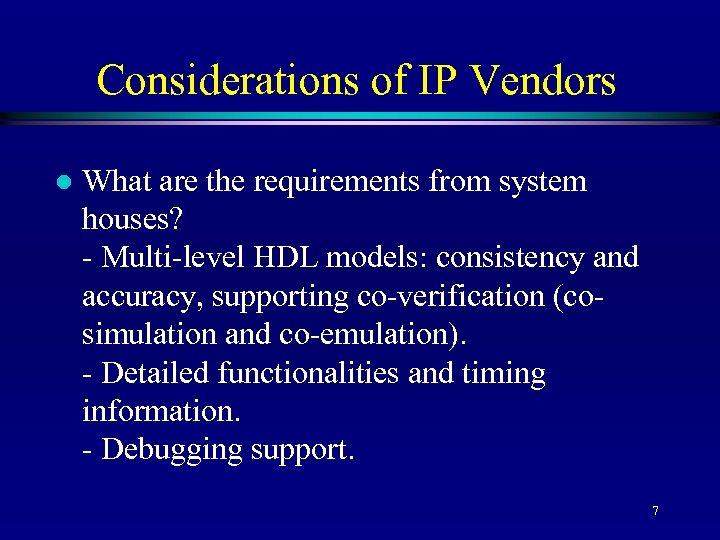

Considerations of IP Vendors l What are the requirements from system houses? - Multi-level HDL models: consistency and accuracy, supporting co-verification (cosimulation and co-emulation). - Detailed functionalities and timing information. - Debugging support. 7

Considerations of IP Vendors l What are the requirements from system houses? - Multi-level HDL models: consistency and accuracy, supporting co-verification (cosimulation and co-emulation). - Detailed functionalities and timing information. - Debugging support. 7

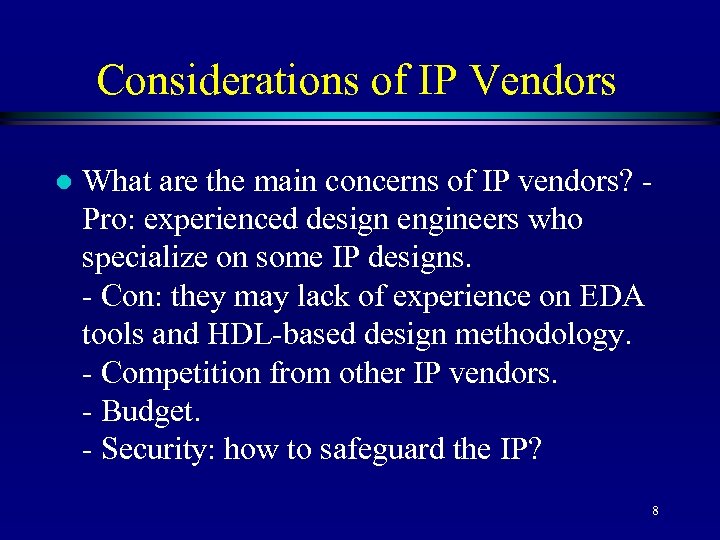

Considerations of IP Vendors l What are the main concerns of IP vendors? Pro: experienced design engineers who specialize on some IP designs. - Con: they may lack of experience on EDA tools and HDL-based design methodology. - Competition from other IP vendors. - Budget. - Security: how to safeguard the IP? 8

Considerations of IP Vendors l What are the main concerns of IP vendors? Pro: experienced design engineers who specialize on some IP designs. - Con: they may lack of experience on EDA tools and HDL-based design methodology. - Competition from other IP vendors. - Budget. - Security: how to safeguard the IP? 8

Design Methodologies for IP Vendors Application-specific in-house CAD. l Budget-driven design methodology. l Methods for developing higher level HDL models. l Tightly coupling to a multi-level verification methodology. l External design, verification, and layout supporting services. l 9

Design Methodologies for IP Vendors Application-specific in-house CAD. l Budget-driven design methodology. l Methods for developing higher level HDL models. l Tightly coupling to a multi-level verification methodology. l External design, verification, and layout supporting services. l 9

Security of IPs Safeguarding IPs - many ASIC suppliers have worked with EDA vendors for years on this issue. l Encryption schemes and protection processes for IPs. l How to safeguard the IP and providing all the necessary design information, e. g. , timing, to system houses? l 10

Security of IPs Safeguarding IPs - many ASIC suppliers have worked with EDA vendors for years on this issue. l Encryption schemes and protection processes for IPs. l How to safeguard the IP and providing all the necessary design information, e. g. , timing, to system houses? l 10

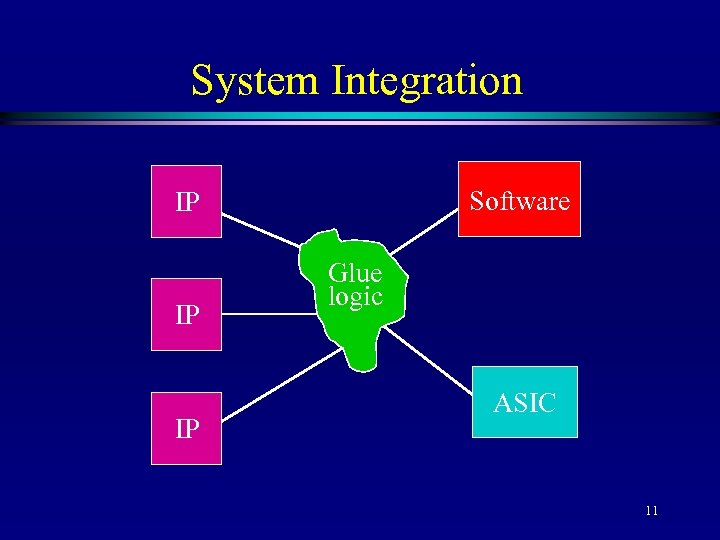

System Integration Software IP IP IP Glue logic ASIC 11

System Integration Software IP IP IP Glue logic ASIC 11

System Integration Issues Platform to evaluate various VC blocks to make their choices and to integrate the blocks for their design verification. l To verify the hardware design at system level, designers need to co-simulate or coemulate the design flow using different computational models. l Debugging and diagnosis environment to support system integration. l 12

System Integration Issues Platform to evaluate various VC blocks to make their choices and to integrate the blocks for their design verification. l To verify the hardware design at system level, designers need to co-simulate or coemulate the design flow using different computational models. l Debugging and diagnosis environment to support system integration. l 12

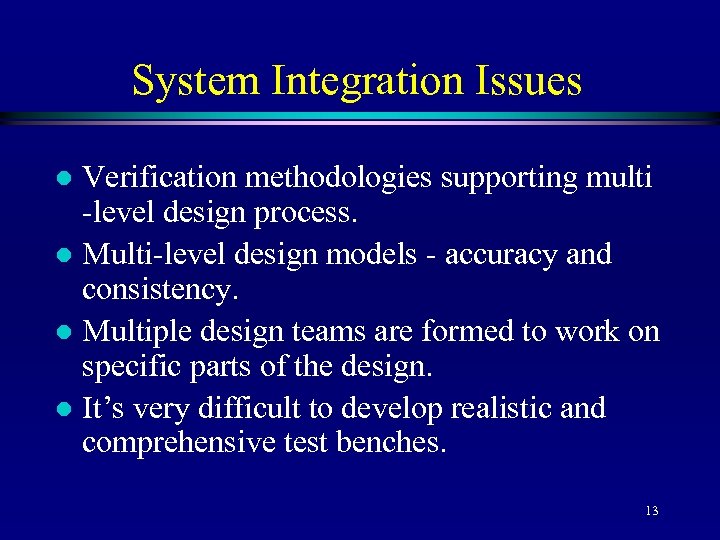

System Integration Issues Verification methodologies supporting multi -level design process. l Multi-level design models - accuracy and consistency. l Multiple design teams are formed to work on specific parts of the design. l It’s very difficult to develop realistic and comprehensive test benches. l 13

System Integration Issues Verification methodologies supporting multi -level design process. l Multi-level design models - accuracy and consistency. l Multiple design teams are formed to work on specific parts of the design. l It’s very difficult to develop realistic and comprehensive test benches. l 13

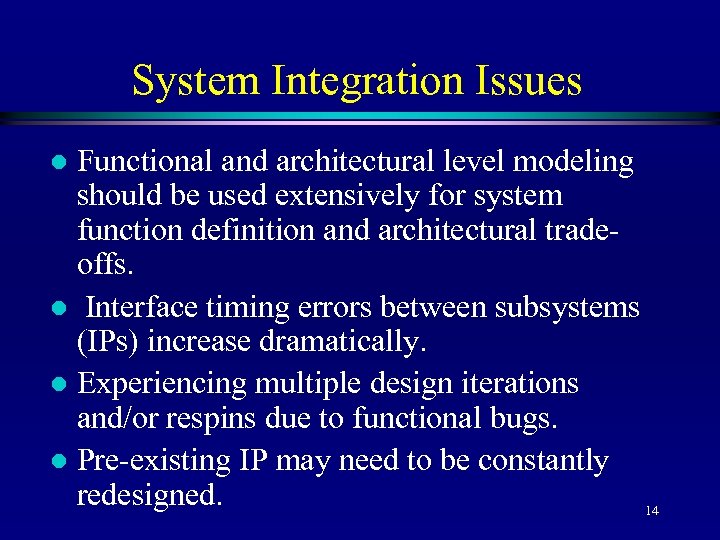

System Integration Issues Functional and architectural level modeling should be used extensively for system function definition and architectural tradeoffs. l Interface timing errors between subsystems (IPs) increase dramatically. l Experiencing multiple design iterations and/or respins due to functional bugs. l Pre-existing IP may need to be constantly redesigned. 14 l

System Integration Issues Functional and architectural level modeling should be used extensively for system function definition and architectural tradeoffs. l Interface timing errors between subsystems (IPs) increase dramatically. l Experiencing multiple design iterations and/or respins due to functional bugs. l Pre-existing IP may need to be constantly redesigned. 14 l

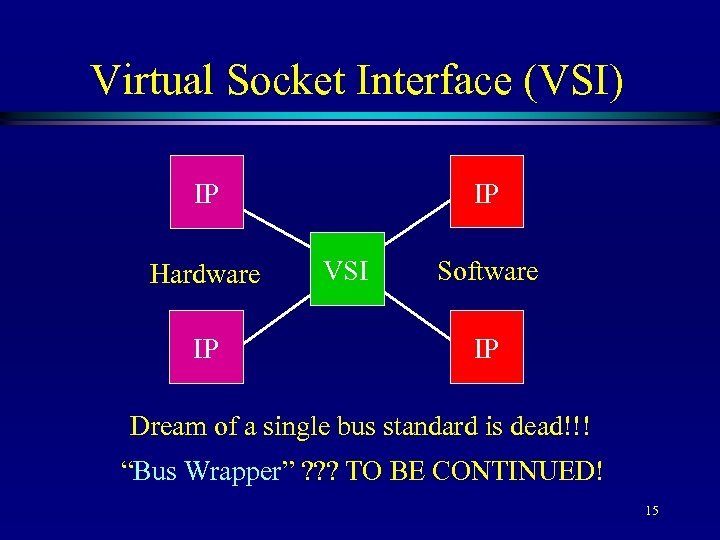

Virtual Socket Interface (VSI) IP IP Hardware IP VSI Software IP Dream of a single bus standard is dead!!! “Bus Wrapper” ? ? ? TO BE CONTINUED! 15

Virtual Socket Interface (VSI) IP IP Hardware IP VSI Software IP Dream of a single bus standard is dead!!! “Bus Wrapper” ? ? ? TO BE CONTINUED! 15

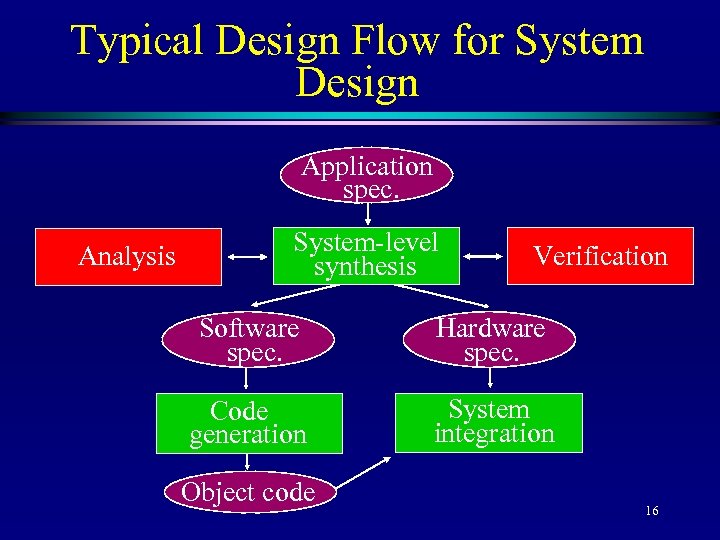

Typical Design Flow for System Design Application spec. Analysis System-level synthesis Verification Software spec. Hardware spec. Code generation System integration Object code 16

Typical Design Flow for System Design Application spec. Analysis System-level synthesis Verification Software spec. Hardware spec. Code generation System integration Object code 16

Design Tasks Definition of system-level design specification. l Design evaluation and exploration. l Hardware/software codesign. l Co-verification: co-simulation and coemulation. l Debugging and diagnosis. l Rapid prototyping. l 17

Design Tasks Definition of system-level design specification. l Design evaluation and exploration. l Hardware/software codesign. l Co-verification: co-simulation and coemulation. l Debugging and diagnosis. l Rapid prototyping. l 17

System Specification Language-based - C, C++, HDLs, or… l Graphical-based - control and data flow graph. l Formal hardware/software representation. l 18

System Specification Language-based - C, C++, HDLs, or… l Graphical-based - control and data flow graph. l Formal hardware/software representation. l 18

Design Evaluation and Exploration Determine which IP can be used for the system. If there is one and more than one, we have to determine which one should be used. l The required specification provided by IP vendors to support design evaluation and exploration. l Design evaluation and exploration environment and methodologies. l 19

Design Evaluation and Exploration Determine which IP can be used for the system. If there is one and more than one, we have to determine which one should be used. l The required specification provided by IP vendors to support design evaluation and exploration. l Design evaluation and exploration environment and methodologies. l 19

Hardware/Software Codesign IP selection. l Hardware/software partitioning. l Interface synthesis. l Software synthesis. l Estimation. l 20

Hardware/Software Codesign IP selection. l Hardware/software partitioning. l Interface synthesis. l Software synthesis. l Estimation. l 20

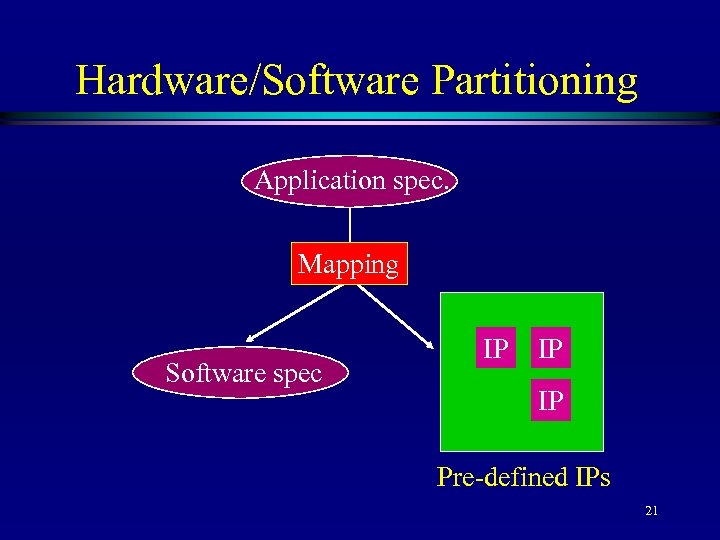

Hardware/Software Partitioning Application spec. Mapping Software spec IP IP IP Pre-defined IPs 21

Hardware/Software Partitioning Application spec. Mapping Software spec IP IP IP Pre-defined IPs 21

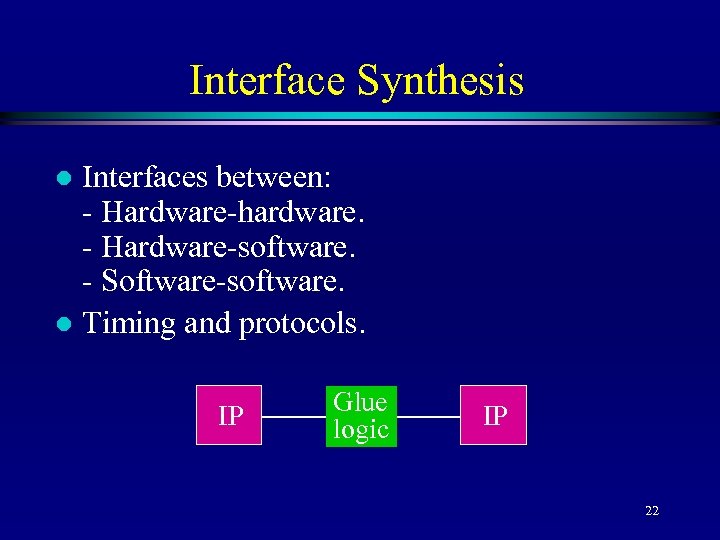

Interface Synthesis Interfaces between: - Hardware-hardware. - Hardware-software. - Software-software. l Timing and protocols. l IP Glue logic IP 22

Interface Synthesis Interfaces between: - Hardware-hardware. - Hardware-software. - Software-software. l Timing and protocols. l IP Glue logic IP 22

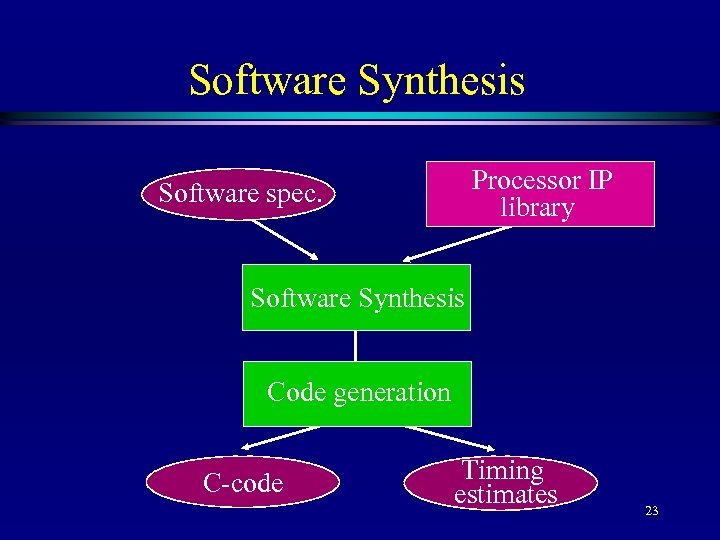

Software Synthesis Processor IP library Software spec. Software Synthesis Code generation C-code Timing estimates 23

Software Synthesis Processor IP library Software spec. Software Synthesis Code generation C-code Timing estimates 23

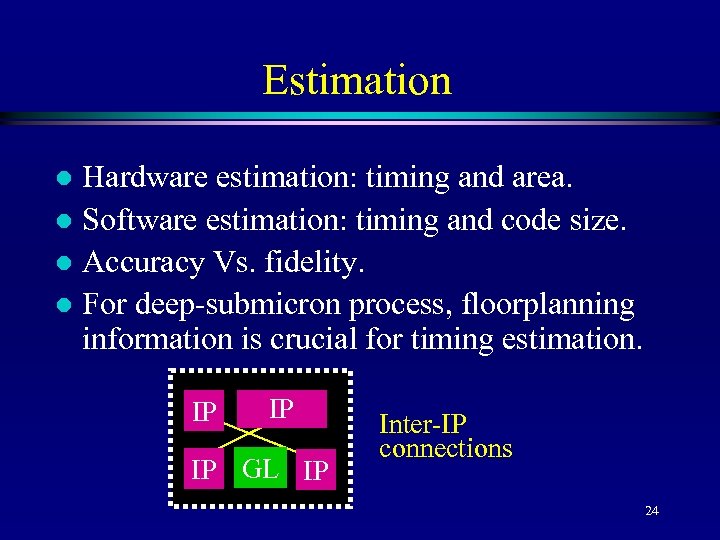

Estimation Hardware estimation: timing and area. l Software estimation: timing and code size. l Accuracy Vs. fidelity. l For deep-submicron process, floorplanning information is crucial for timing estimation. l IP IP IP GL IP Inter-IP connections 24

Estimation Hardware estimation: timing and area. l Software estimation: timing and code size. l Accuracy Vs. fidelity. l For deep-submicron process, floorplanning information is crucial for timing estimation. l IP IP IP GL IP Inter-IP connections 24

Co-Verification Key to co-design. l Plug-and-play system verification methods. l Interface-based verification flow - verifying the interfaces and pre-verified IP blocks. l Insufficient design information of IPs due to security reason. l Application-specific co-verification environment and methodologies. l Analog design verification? ? ? 25 l

Co-Verification Key to co-design. l Plug-and-play system verification methods. l Interface-based verification flow - verifying the interfaces and pre-verified IP blocks. l Insufficient design information of IPs due to security reason. l Application-specific co-verification environment and methodologies. l Analog design verification? ? ? 25 l

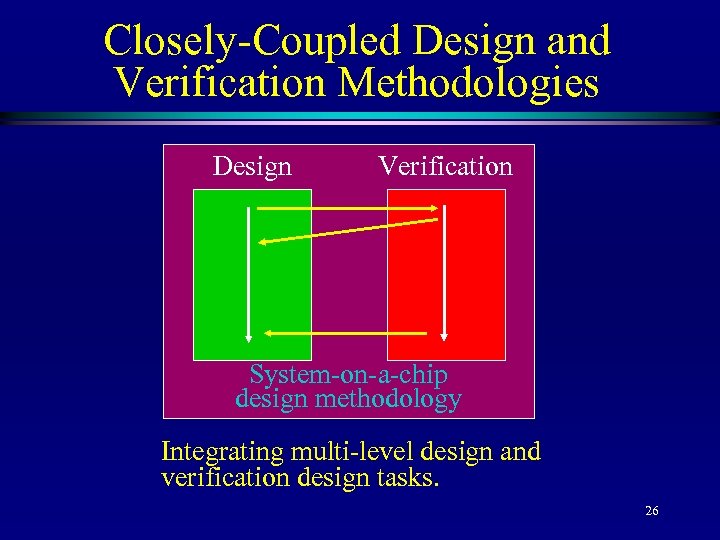

Closely-Coupled Design and Verification Methodologies Design Verification System-on-a-chip design methodology Integrating multi-level design and verification design tasks. 26

Closely-Coupled Design and Verification Methodologies Design Verification System-on-a-chip design methodology Integrating multi-level design and verification design tasks. 26

Co-Simulation Co-simulation - real-time connection of two or more simulators linked by a synchronization algorithm. Ex. mixed C, Verilog, and VHDL. l Working with multi-level models at different levels of abstraction. l Slow speed will be the problem. l 27

Co-Simulation Co-simulation - real-time connection of two or more simulators linked by a synchronization algorithm. Ex. mixed C, Verilog, and VHDL. l Working with multi-level models at different levels of abstraction. l Slow speed will be the problem. l 27

Co-Emulation Integrating simulation and emulation environments for co-verification. l Providing an in-circuit verification environment. l Providing a system-level testing environment. l Providing a system prototyping. l 28

Co-Emulation Integrating simulation and emulation environments for co-verification. l Providing an in-circuit verification environment. l Providing a system-level testing environment. l Providing a system prototyping. l 28

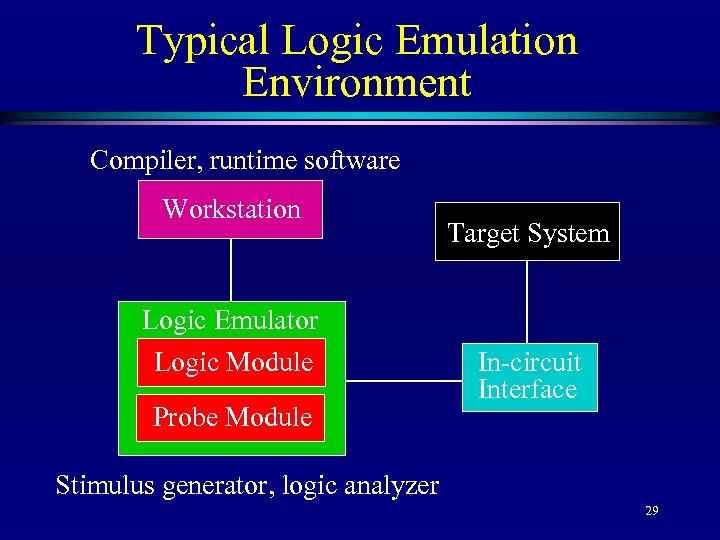

Typical Logic Emulation Environment Compiler, runtime software Workstation Logic Emulator Logic Module Probe Module Target System In-circuit Interface Stimulus generator, logic analyzer 29

Typical Logic Emulation Environment Compiler, runtime software Workstation Logic Emulator Logic Module Probe Module Target System In-circuit Interface Stimulus generator, logic analyzer 29

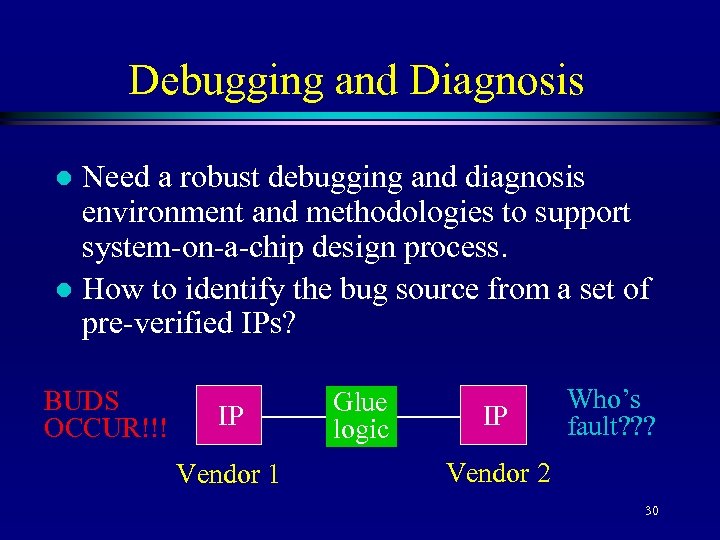

Debugging and Diagnosis Need a robust debugging and diagnosis environment and methodologies to support system-on-a-chip design process. l How to identify the bug source from a set of pre-verified IPs? l BUDS OCCUR!!! IP Vendor 1 Glue logic IP Who’s fault? ? ? Vendor 2 30

Debugging and Diagnosis Need a robust debugging and diagnosis environment and methodologies to support system-on-a-chip design process. l How to identify the bug source from a set of pre-verified IPs? l BUDS OCCUR!!! IP Vendor 1 Glue logic IP Who’s fault? ? ? Vendor 2 30

Rapid Prototyping Basic components: FPGAs and FPICs. l Hardware : boards, boxes, and cabinets. l Software: methodologies and CAD tools. l Time-to-market. l Design complexity. l 31

Rapid Prototyping Basic components: FPGAs and FPICs. l Hardware : boards, boxes, and cabinets. l Software: methodologies and CAD tools. l Time-to-market. l Design complexity. l 31

Rapid Prototyping Custom-designed prototyping board. l Logic-emulation systems. l Field-programmable printed-circuit-boards. l Application-specification in-house rapidprototyping methodologies for different VC vendors and system houses. l 32

Rapid Prototyping Custom-designed prototyping board. l Logic-emulation systems. l Field-programmable printed-circuit-boards. l Application-specification in-house rapidprototyping methodologies for different VC vendors and system houses. l 32

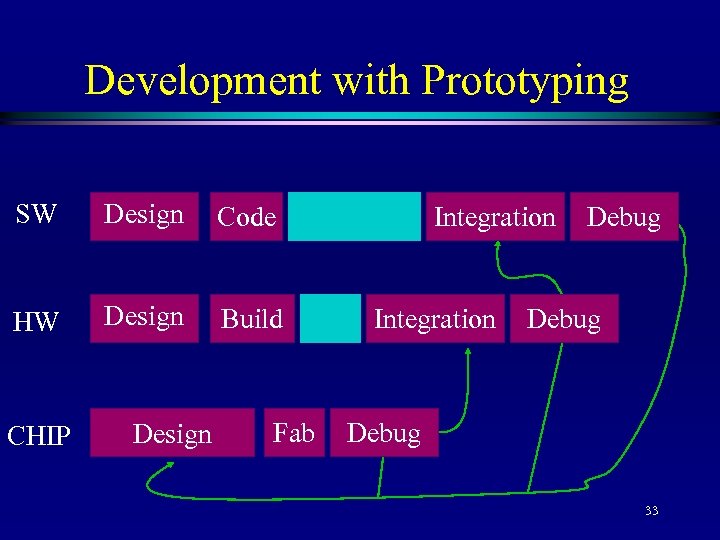

Development with Prototyping SW Design Code HW Design Build CHIP Design Fab Integration Debug 33

Development with Prototyping SW Design Code HW Design Build CHIP Design Fab Integration Debug 33

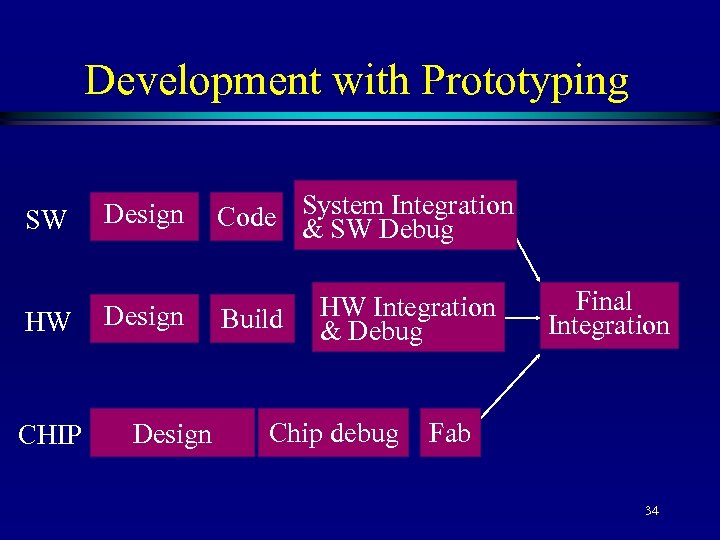

Development with Prototyping SW HW CHIP Design Integration Code System. Debug & SW Build HW Integration & Debug Chip debug Final Integration Fab 34

Development with Prototyping SW HW CHIP Design Integration Code System. Debug & SW Build HW Integration & Debug Chip debug Final Integration Fab 34

Conclusions Application-specific design methodologies for IP designs and system integration. l In a keynote speech at the IP forum 1997, LSI Logic Corp. chairman Wifred Corrigan pointed out “because of the high costs of the methodology, system-on-a-chip only makes sense when you have high volumes. ” => Easy to use and low cost methodology!!! l 35

Conclusions Application-specific design methodologies for IP designs and system integration. l In a keynote speech at the IP forum 1997, LSI Logic Corp. chairman Wifred Corrigan pointed out “because of the high costs of the methodology, system-on-a-chip only makes sense when you have high volumes. ” => Easy to use and low cost methodology!!! l 35

Conclusions A robust verification methodology is the key leading to successful system-on-a-chip designs. l Tightly coupling design and verification methodologies. l Joint effort by IP, system designers and EDA tool developers to develop robust system-ona-chip design methodologies. l 36

Conclusions A robust verification methodology is the key leading to successful system-on-a-chip designs. l Tightly coupling design and verification methodologies. l Joint effort by IP, system designers and EDA tool developers to develop robust system-ona-chip design methodologies. l 36