fcc484cd9967d60d5e81f7945145cefb.ppt

- Количество слайдов: 43

Design for Testability Virendra Singh Indian Institute of Science Bangalore virendra@ {computer, ieee}. org IEP on Digital System Synthesis at IIT Kanpur (Dec 11 -21, 2007) Dec 21, 2007 Df. T@IITK 1

Definition n Design for testability (DFT) refers to those design techniques that make test generation and test application cost-effective. DFT methods for digital circuits: § Ad-hoc methods § Structured methods: § Scan § Partial Scan § Built-in self-test (BIST) § Boundary scan DFT method for mixed-signal circuits: § Dec 21, 2007 Analog test bus Df. T@IITK 2

Ad-Hoc DFT Methods n Good design practices learnt through experience are used as guidelines: § § § n n Avoid asynchronous (unclocked) feedback. Make flip-flops initializable. Avoid redundant gates. Avoid large fanin gates. Provide test control for difficult-to-control signals. Avoid gated clocks. Consider ATE requirements (tristates, etc. ) Design reviews conducted by experts or design auditing tools. Disadvantages of ad-hoc DFT methods: § § § Dec 21, 2007 Experts and tools not always available. Test generation is often manual with no guarantee of high fault coverage. Design iterations may be necessary. Df. T@IITK 3

Scan Design § Circuit is designed using pre-specified design rules. § Test structure (hardware) is added to the verified design: § § § Add a test control (TC) primary input. Replace flip-flops by scan flip-flops (SFF) and connect to form one or more shift registers in the test mode. Make input/output of each scan shift register controllable/observable from PI/PO. § Use combinational ATPG to obtain tests for all testable faults in the combinational logic. § Add shift register tests and convert ATPG tests into scan sequences for use in manufacturing test. Dec 21, 2007 Df. T@IITK 4

Scan Design Rules n n Use only clocked D-type of flip-flops for all state variables. At least one PI pin must be available for test; more pins, if available, can be used. All clocks must be controlled from PIs. Clocks must not feed data inputs of flip-flops. Dec 21, 2007 Df. T@IITK 5

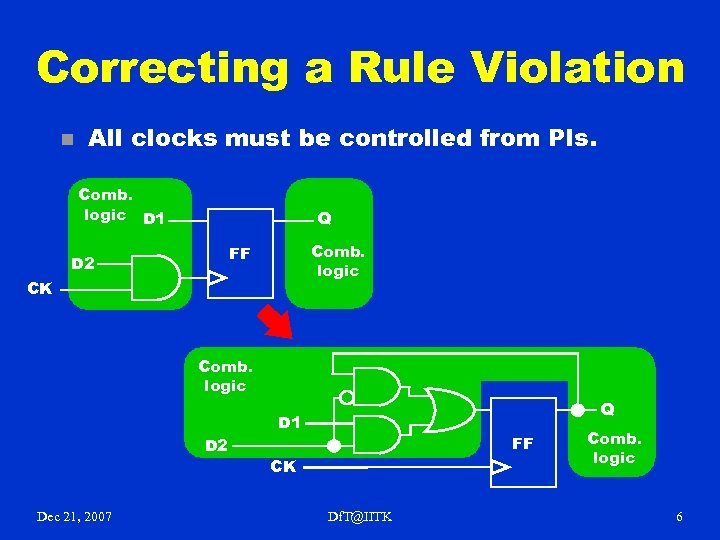

Correcting a Rule Violation n All clocks must be controlled from PIs. Comb. logic D 1 Q Comb. logic FF D 2 CK Comb. logic Q D 1 D 2 Dec 21, 2007 FF CK Df. T@IITK Comb. logic 6

Scan Flip-Flop (SFF) Master latch D Slave latch TC Q Logic overhead MUX SD Q CK D flip-flop CK TC Dec 21, 2007 Master open Slave open Normal mode, D selected Df. T@IITK t Scan mode, SD selected t 7

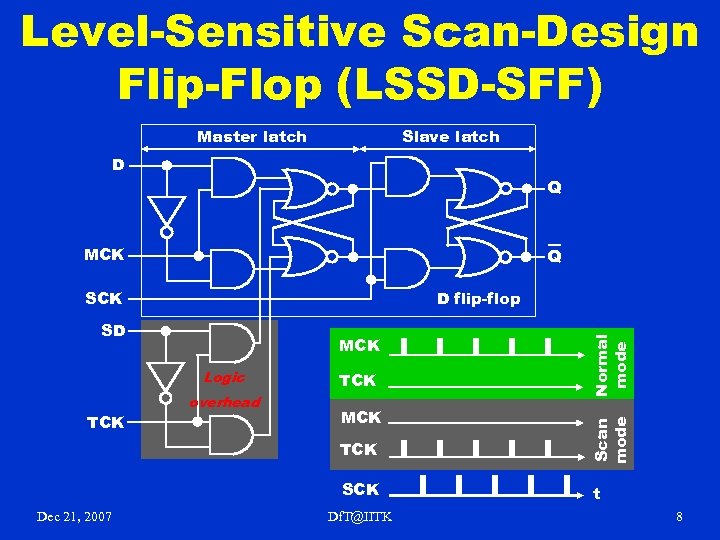

Level-Sensitive Scan-Design Flip-Flop (LSSD-SFF) Master latch Slave latch D Q MCK Q D flip-flop SD MCK TCK overhead TCK MCK TCK SCK Dec 21, 2007 Scan mode Logic Normal mode SCK t Df. T@IITK 8

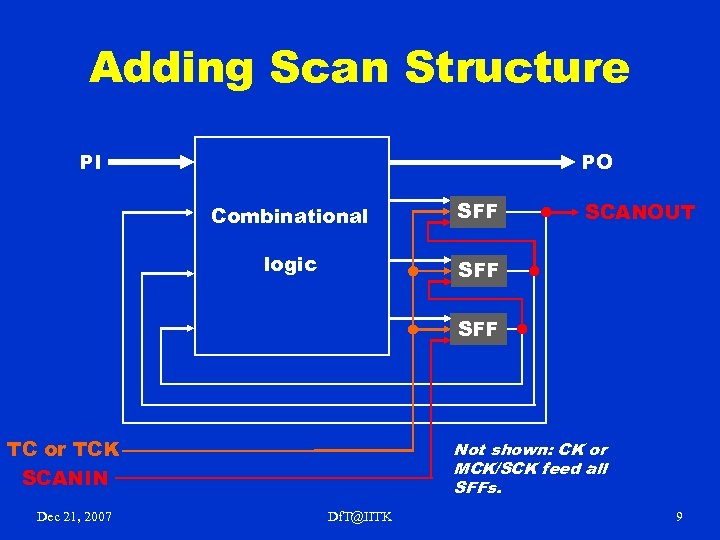

Adding Scan Structure PI PO Combinational SFF logic SFF SCANOUT SFF TC or TCK SCANIN Dec 21, 2007 Not shown: CK or MCK/SCK feed all SFFs. Df. T@IITK 9

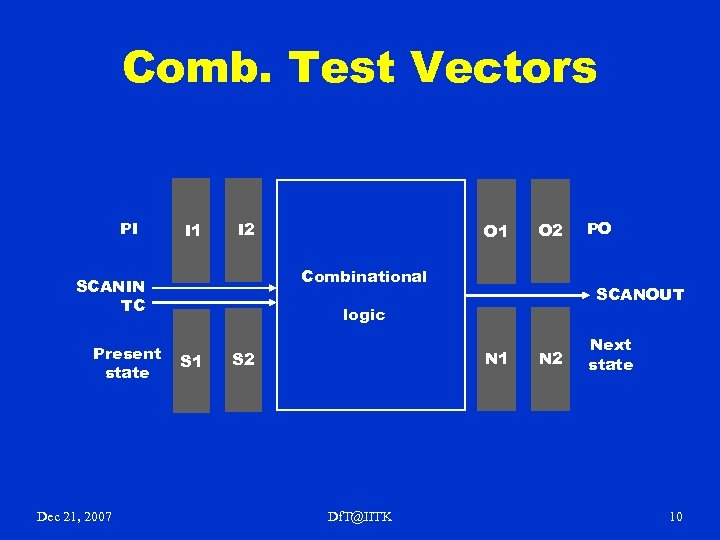

Comb. Test Vectors PI I 1 I 2 Dec 21, 2007 O 2 Combinational SCANIN TC Present state O 1 SCANOUT logic S 1 N 1 S 2 Df. T@IITK PO N 2 Next state 10

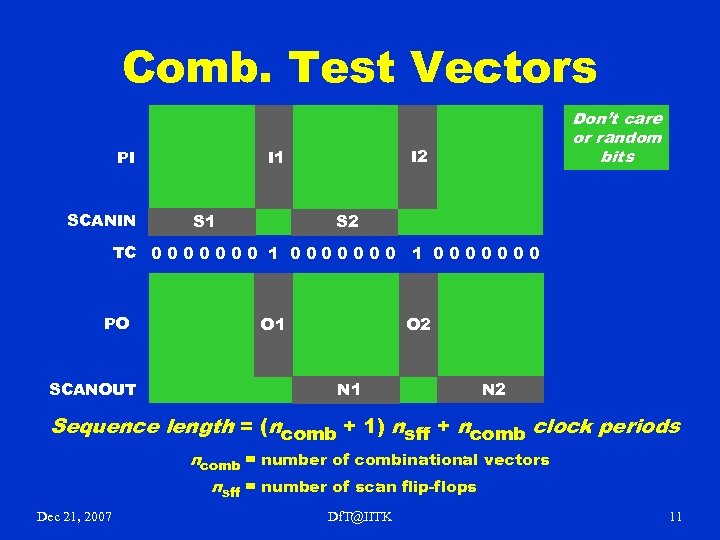

Comb. Test Vectors SCANIN I 2 I 1 PI S 1 Don’t care or random bits S 2 TC 0 0 0 0 1 0 0 0 0 PO SCANOUT O 2 O 1 N 2 Sequence length = (ncomb + 1) nsff + ncomb clock periods ncomb = number of combinational vectors nsff = number of scan flip-flops Dec 21, 2007 Df. T@IITK 11

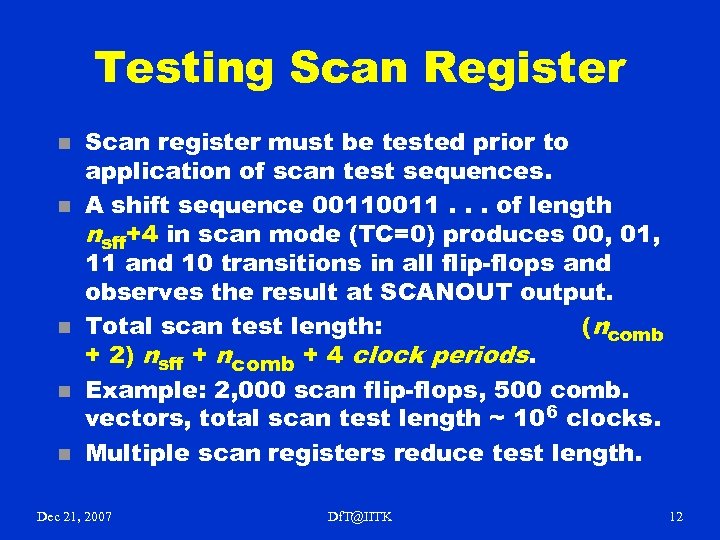

Testing Scan Register n n n Scan register must be tested prior to application of scan test sequences. A shift sequence 0011. . . of length nsff+4 in scan mode (TC=0) produces 00, 01, 11 and 10 transitions in all flip-flops and observes the result at SCANOUT output. Total scan test length: (ncomb + 2) nsff + ncomb + 4 clock periods. Example: 2, 000 scan flip-flops, 500 comb. vectors, total scan test length ~ 106 clocks. Multiple scan registers reduce test length. Dec 21, 2007 Df. T@IITK 12

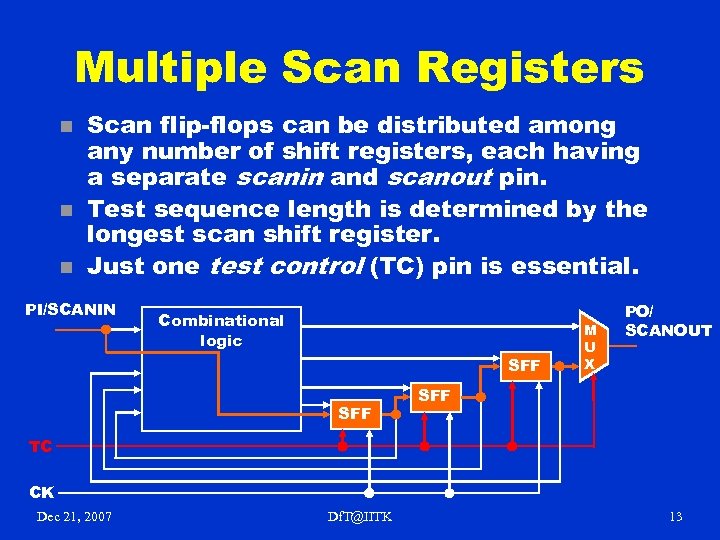

Multiple Scan Registers n n n Scan flip-flops can be distributed among any number of shift registers, each having a separate scanin and scanout pin. Test sequence length is determined by the longest scan shift register. Just one test control (TC) pin is essential. PI/SCANIN Combinational logic SFF M U X PO/ SCANOUT SFF TC CK Dec 21, 2007 Df. T@IITK 13

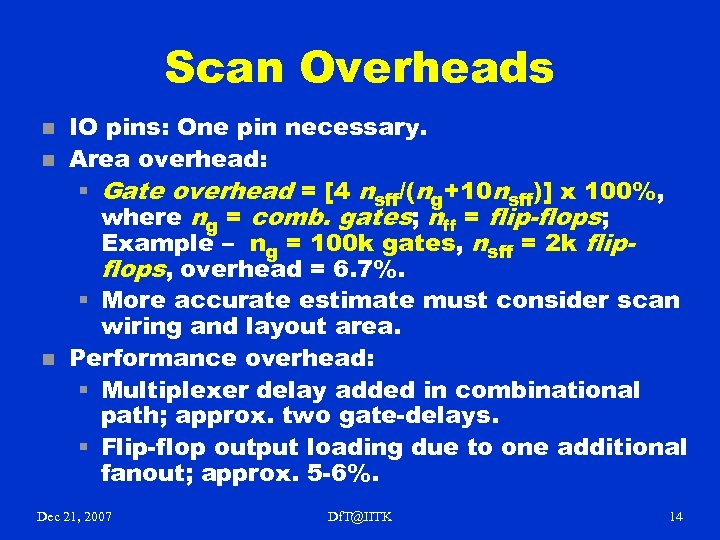

Scan Overheads n n n IO pins: One pin necessary. Area overhead: § Gate overhead = [4 nsff/(ng+10 nsff)] x 100%, where ng = comb. gates; nff = flip-flops; Example – ng = 100 k gates, nsff = 2 k flipflops, overhead = 6. 7%. § More accurate estimate must consider scan wiring and layout area. Performance overhead: § Multiplexer delay added in combinational path; approx. two gate-delays. § Flip-flop output loading due to one additional fanout; approx. 5 -6%. Dec 21, 2007 Df. T@IITK 14

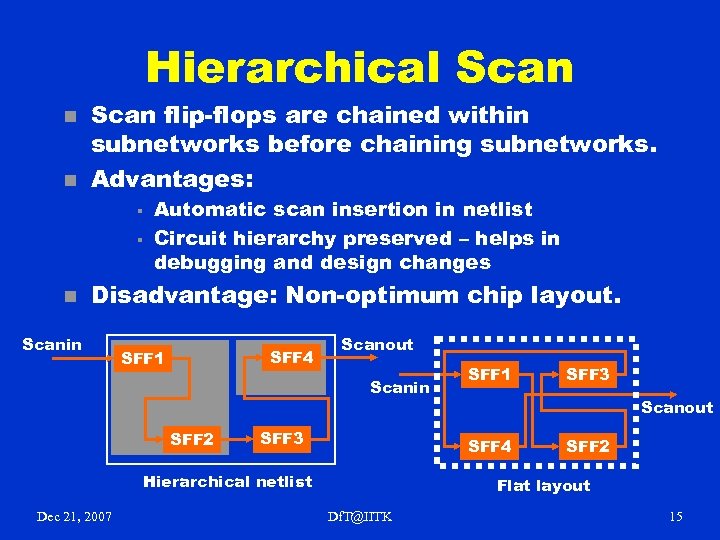

Hierarchical Scan n n Scan flip-flops are chained within subnetworks before chaining subnetworks. Advantages: § § n Automatic scan insertion in netlist Circuit hierarchy preserved – helps in debugging and design changes Disadvantage: Non-optimum chip layout. Scanin SFF 4 SFF 1 Scanout Scanin SFF 2 SFF 3 Scanout SFF 4 Hierarchical netlist Dec 21, 2007 SFF 1 SFF 2 Flat layout Df. T@IITK 15

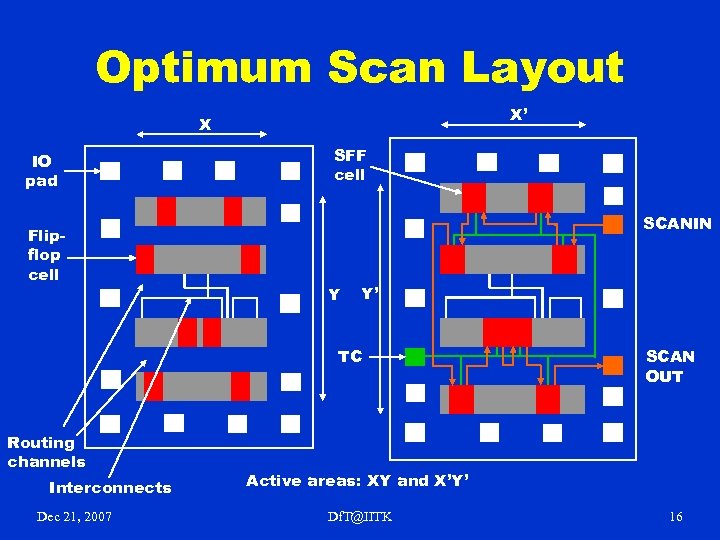

Optimum Scan Layout X’ X IO pad Flipflop cell SFF cell SCANIN Y Y’ TC Routing channels Interconnects Dec 21, 2007 SCAN OUT Active areas: XY and X’Y’ Df. T@IITK 16

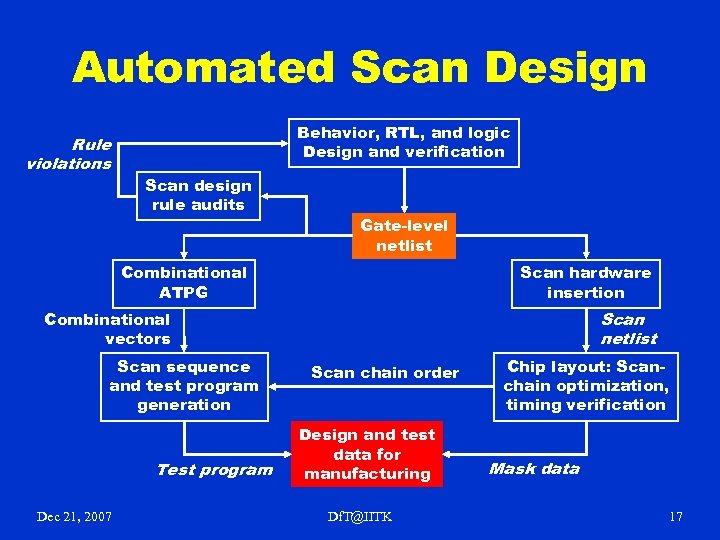

Automated Scan Design Rule violations Behavior, RTL, and logic Design and verification Scan design rule audits Gate-level netlist Combinational ATPG Scan hardware insertion Scan netlist Combinational vectors Scan sequence and test program generation Test program Dec 21, 2007 Scan chain order Design and test data for manufacturing Df. T@IITK Chip layout: Scanchain optimization, timing verification Mask data 17

Timing and Power n n Small delays in scan path and clock skew can cause race condition. Large delays in scan path require slower scan clock. Dynamic multiplexers: Skew between TC and TC signals can cause momentary shorting of D and SD inputs. Random signal activity in combinational circuit during scan cause excessive power dissipation. Dec 21, 2007 Df. T@IITK 18

Partial-Scan Definition n n A subset of flip-flops is scanned. Objectives: § Minimize area overhead and scan sequence length, yet achieve required fault coverage § Exclude selected flip-flops from scan: § § Improve performance Allow limited scan design rule violations § Allow automation: § § In scan flip-flop selection In test generation § Shorter scan sequences Dec 21, 2007 Df. T@IITK 19

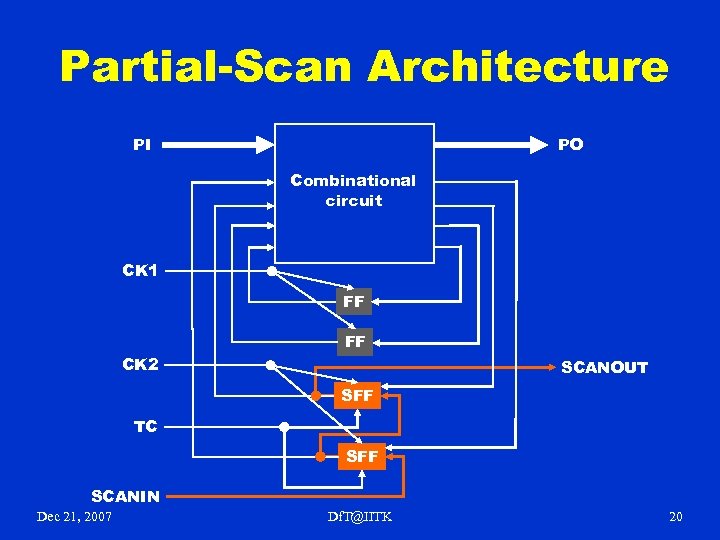

Partial-Scan Architecture PI PO Combinational circuit CK 1 FF CK 2 FF SCANOUT SFF TC SFF SCANIN Dec 21, 2007 Df. T@IITK 20

History of Partial-Scan n n Scan flip-flop selection from testability measures, Trischler et al. , ITC-80; not too successful. Use of combinational ATPG: § Agrawal et al. , D&T, Apr. 88 § § Functional vectors for initial fault coverage Scan flip-flops selected by ATPG § Gupta et al. , IEEETC, Apr. 90 § § n Balanced structure Sometimes requires high scan percentage Use of sequential ATPG: § Cheng and Agrawal, IEEETC, Apr. 90; Kunzmann and Wunderlich, JETTA, May 90 § Dec 21, 2007 Create cycle-free structure for efficient ATPG Df. T@IITK 21

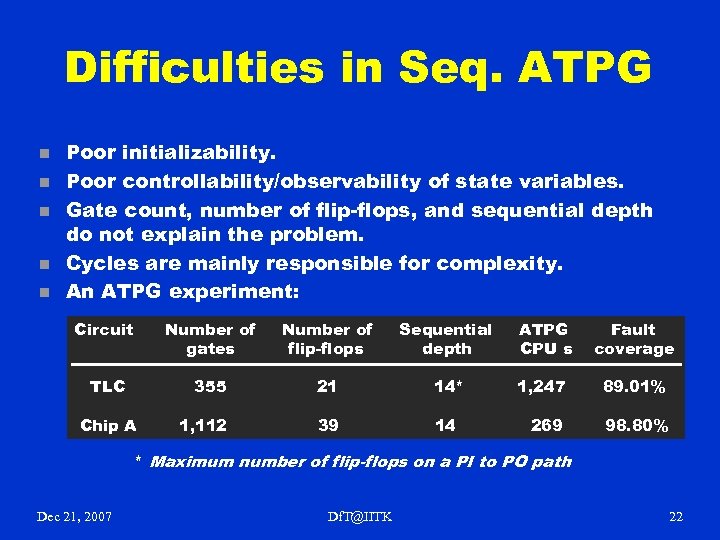

Difficulties in Seq. ATPG n n n Poor initializability. Poor controllability/observability of state variables. Gate count, number of flip-flops, and sequential depth do not explain the problem. Cycles are mainly responsible for complexity. An ATPG experiment: Circuit Number of gates Number of flip-flops Sequential depth ATPG CPU s Fault coverage TLC 355 21 14* 1, 247 89. 01% 1, 112 39 14 269 98. 80% Chip A * Maximum number of flip-flops on a PI to PO path Dec 21, 2007 Df. T@IITK 22

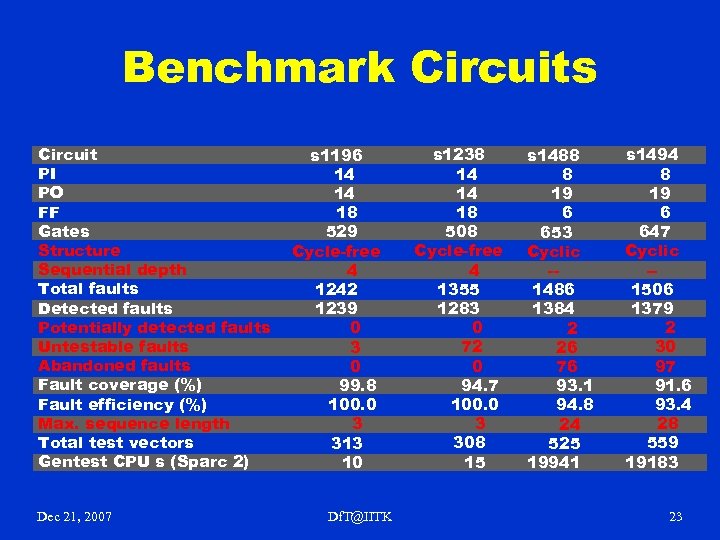

Benchmark Circuits Circuit PI PO FF Gates Structure Sequential depth Total faults Detected faults Potentially detected faults Untestable faults Abandoned faults Fault coverage (%) Fault efficiency (%) Max. sequence length Total test vectors Gentest CPU s (Sparc 2) Dec 21, 2007 s 1196 14 14 18 529 Cycle-free 4 1242 1239 0 3 0 99. 8 100. 0 3 313 10 Df. T@IITK s 1238 14 14 18 508 Cycle-free 4 1355 1283 0 72 0 94. 7 100. 0 3 308 15 s 1488 8 19 6 653 Cyclic -1486 1384 2 26 76 93. 1 94. 8 24 525 19941 s 1494 8 19 6 647 Cyclic -1506 1379 2 30 97 91. 6 93. 4 28 559 19183 23

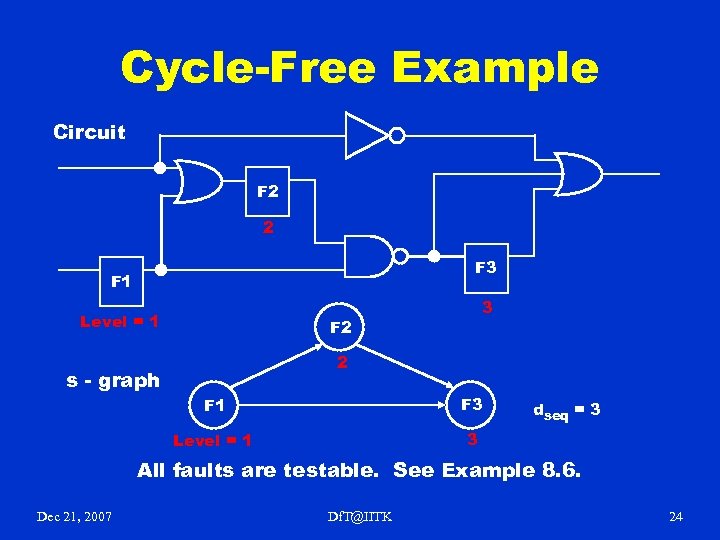

Cycle-Free Example Circuit F 2 2 F 3 F 1 Level = 1 3 F 2 2 s - graph F 1 F 3 Level = 1 3 dseq = 3 All faults are testable. See Example 8. 6. Dec 21, 2007 Df. T@IITK 24

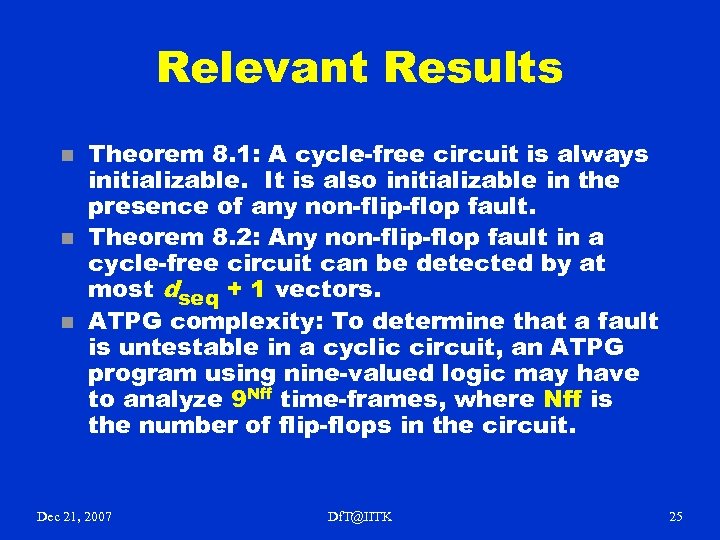

Relevant Results n n n Theorem 8. 1: A cycle-free circuit is always initializable. It is also initializable in the presence of any non-flip-flop fault. Theorem 8. 2: Any non-flip-flop fault in a cycle-free circuit can be detected by at most dseq + 1 vectors. ATPG complexity: To determine that a fault is untestable in a cyclic circuit, an ATPG program using nine-valued logic may have to analyze 9 Nff time-frames, where Nff is the number of flip-flops in the circuit. Dec 21, 2007 Df. T@IITK 25

A Partial-Scan Method n n n Select a minimal set of flip-flops for scan to eliminate all cycles. Alternatively, to keep the overhead low only long cycles may be eliminated. In some circuits with a large number of self -loops, all cycles other than self-loops may be eliminated. Dec 21, 2007 Df. T@IITK 26

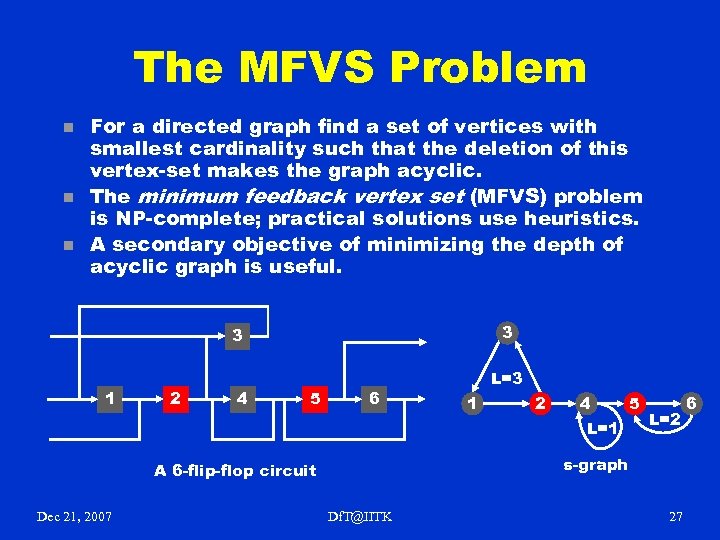

The MFVS Problem n n n For a directed graph find a set of vertices with smallest cardinality such that the deletion of this vertex-set makes the graph acyclic. The minimum feedback vertex set (MFVS) problem is NP-complete; practical solutions use heuristics. A secondary objective of minimizing the depth of acyclic graph is useful. 3 3 1 2 4 5 6 L=3 1 2 4 L=1 L=2 s-graph A 6 -flip-flop circuit Dec 21, 2007 5 Df. T@IITK 27 6

Test Generation n Scan and non-scan flip-flops are controlled from separate clock PIs: § § n Seq. ATPG model: § § § n Normal mode – Both clocks active Scan mode – Only scan clock active Scan flip-flops replaced by PI and PO Seq. ATPG program used for test generation Scan register test sequence, 001100…, of length nsff + 4 applied in the scan mode Each ATPG vector is preceded by a scan-in sequence to set scan flip-flop states A scan-out sequence is added at the end of each vector sequence Test length = (n. ATPG + 2) nsff + n. ATPG + 4 clocks Dec 21, 2007 Df. T@IITK 28

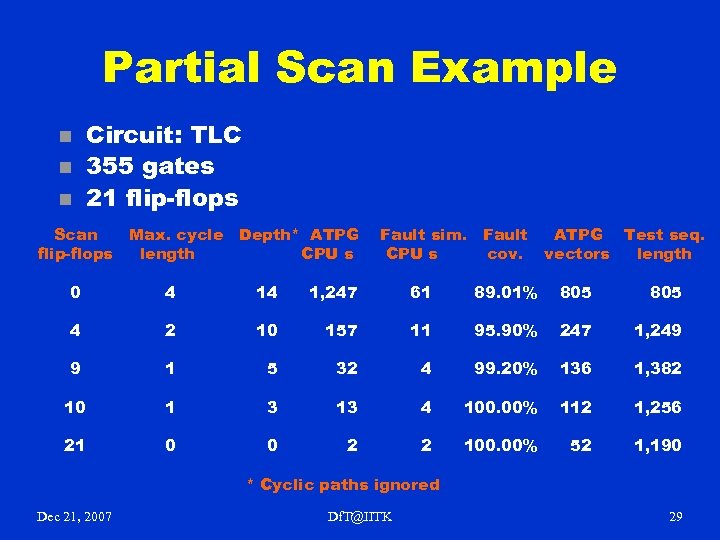

Partial Scan Example n n n Circuit: TLC 355 gates 21 flip-flops Scan flip-flops Max. cycle Depth* ATPG length CPU s Fault sim. Fault CPU s cov. ATPG Test seq. vectors length 0 4 14 1, 247 61 89. 01% 805 4 2 10 157 11 95. 90% 247 1, 249 9 1 5 32 4 99. 20% 136 1, 382 10 1 3 13 4 100. 00% 112 1, 256 21 0 0 2 2 100. 00% 52 1, 190 * Cyclic paths ignored Dec 21, 2007 Df. T@IITK 29

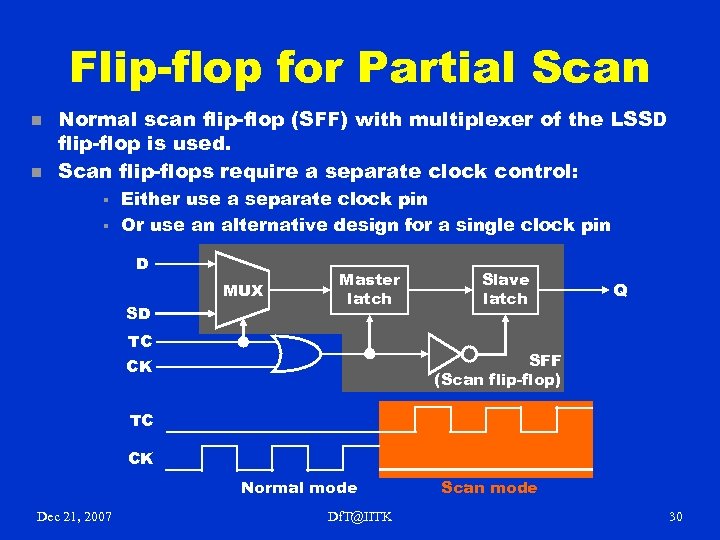

Flip-flop for Partial Scan n n Normal scan flip-flop (SFF) with multiplexer of the LSSD flip-flop is used. Scan flip-flops require a separate clock control: § § Either use a separate clock pin Or use an alternative design for a single clock pin D MUX SD Master latch TC Slave latch Q SFF (Scan flip-flop) CK TC CK Normal mode Dec 21, 2007 Df. T@IITK Scan mode 30

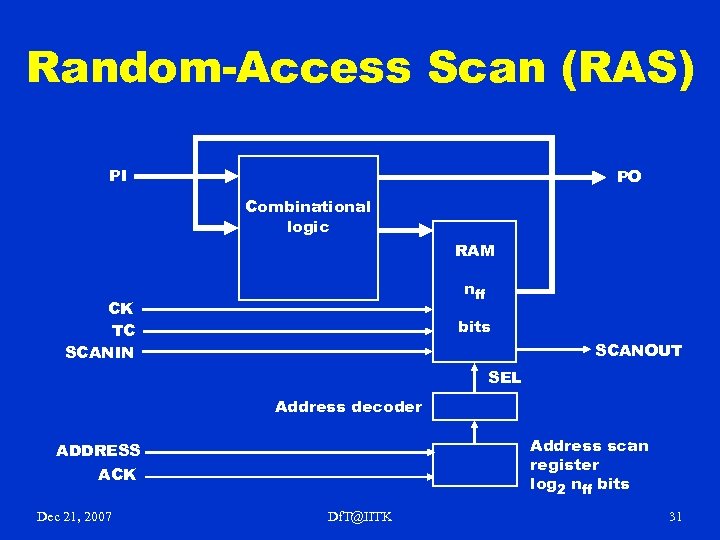

Random-Access Scan (RAS) PI PO Combinational logic RAM nff CK TC SCANIN bits SCANOUT SEL Address decoder Address scan register log 2 nff bits ADDRESS ACK Dec 21, 2007 Df. T@IITK 31

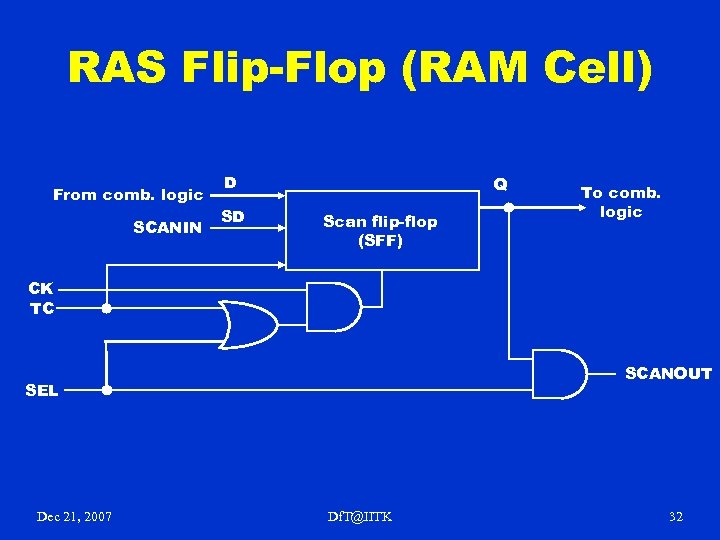

RAS Flip-Flop (RAM Cell) From comb. logic SCANIN D SD Q Scan flip-flop (SFF) To comb. logic CK TC SCANOUT SEL Dec 21, 2007 Df. T@IITK 32

RAS Applications n n Logic test: § Reduced test length § Reduced scan power Delay test: Easy to generate single-input-change (SIC) delay tests. Advantage: RAS may be suitable for certain architecture, e. g. , where memory is implemented as a RAM block. Disadvantages: § § Dec 21, 2007 Not suitable for random logic architecture High overhead – gates added to SFF, address decoder, address register, extra pins and routing Df. T@IITK 33

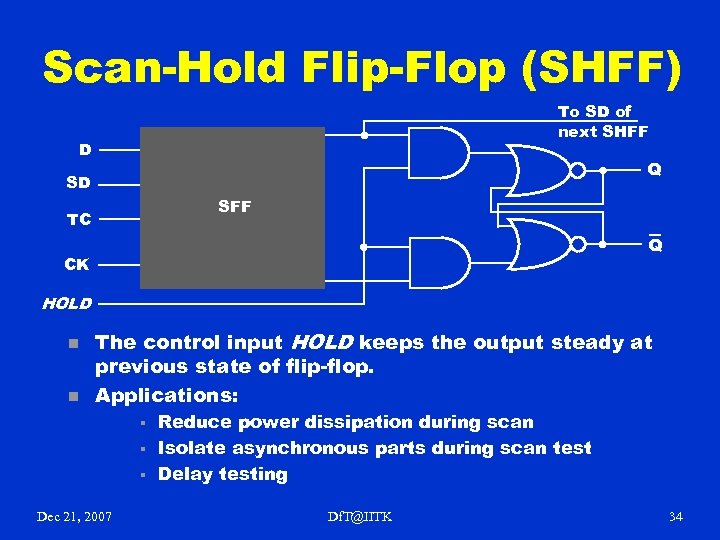

Scan-Hold Flip-Flop (SHFF) To SD of next SHFF D Q SD SFF TC Q CK HOLD n n The control input HOLD keeps the output steady at previous state of flip-flop. Applications: § § § Dec 21, 2007 Reduce power dissipation during scan Isolate asynchronous parts during scan test Delay testing Df. T@IITK 34

Delay Test Definition n A circuit that passes delay test must produce correct outputs when inputs are applied and outputs observed with specified timing. For a combinational or synchronous sequential circuit, delay test verifies the limits of delay in combinational logic. Delay test problem for asynchronous circuits is complex and not well understood. Dec 21, 2007 Df. T@IITK 35

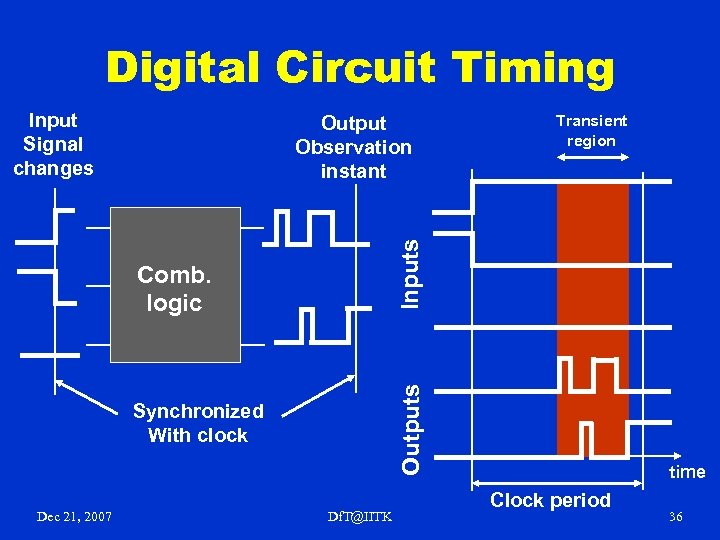

Digital Circuit Timing Input Signal changes Outputs Comb. logic Synchronized With clock Dec 21, 2007 Transient region Inputs Output Observation instant Df. T@IITK time Clock period 36

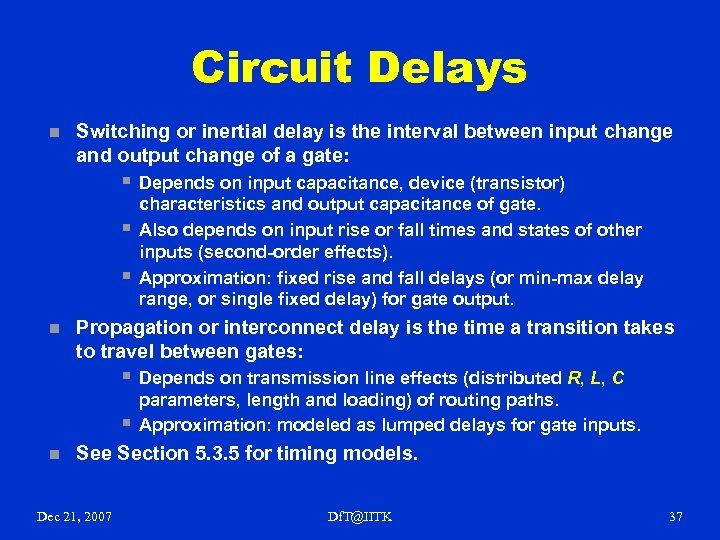

Circuit Delays n Switching or inertial delay is the interval between input change and output change of a gate: § § § n Propagation or interconnect delay is the time a transition takes to travel between gates: § § n Depends on input capacitance, device (transistor) characteristics and output capacitance of gate. Also depends on input rise or fall times and states of other inputs (second-order effects). Approximation: fixed rise and fall delays (or min-max delay range, or single fixed delay) for gate output. Depends on transmission line effects (distributed R, L, C parameters, length and loading) of routing paths. Approximation: modeled as lumped delays for gate inputs. See Section 5. 3. 5 for timing models. Dec 21, 2007 Df. T@IITK 37

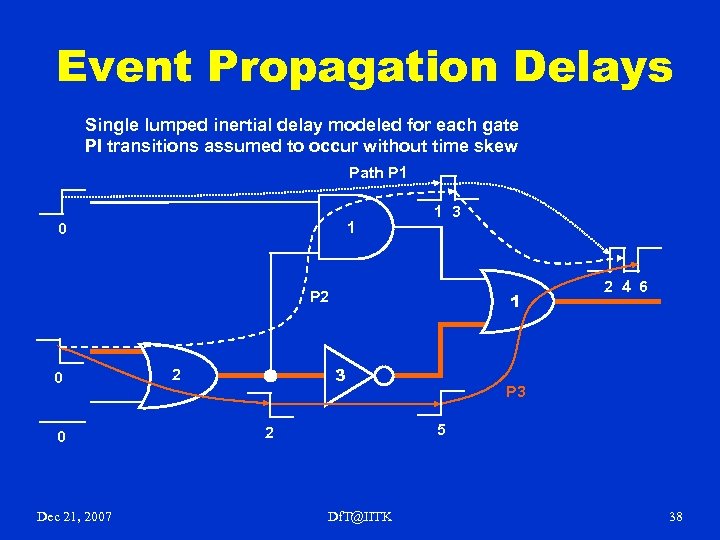

Event Propagation Delays Single lumped inertial delay modeled for each gate PI transitions assumed to occur without time skew Path P 1 1 0 1 3 P 2 0 0 Dec 21, 2007 1 3 2 2 4 6 P 3 5 2 Df. T@IITK 38

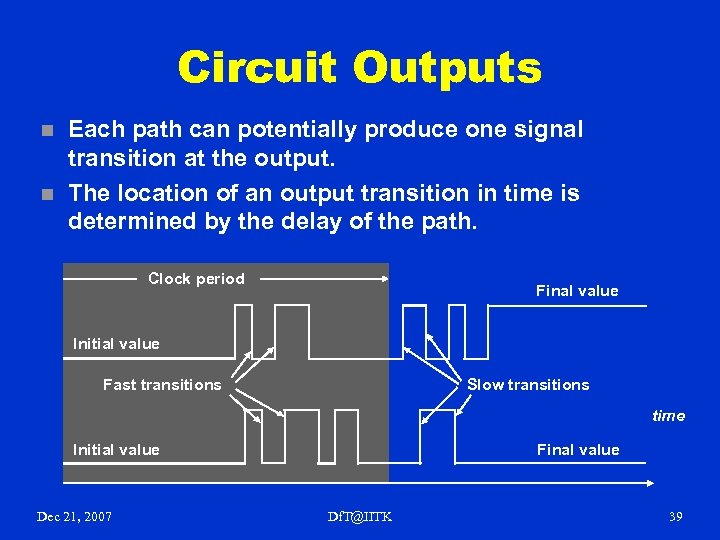

Circuit Outputs n n Each path can potentially produce one signal transition at the output. The location of an output transition in time is determined by the delay of the path. Clock period Final value Initial value Slow transitions Fast transitions time Initial value Dec 21, 2007 Final value Df. T@IITK 39

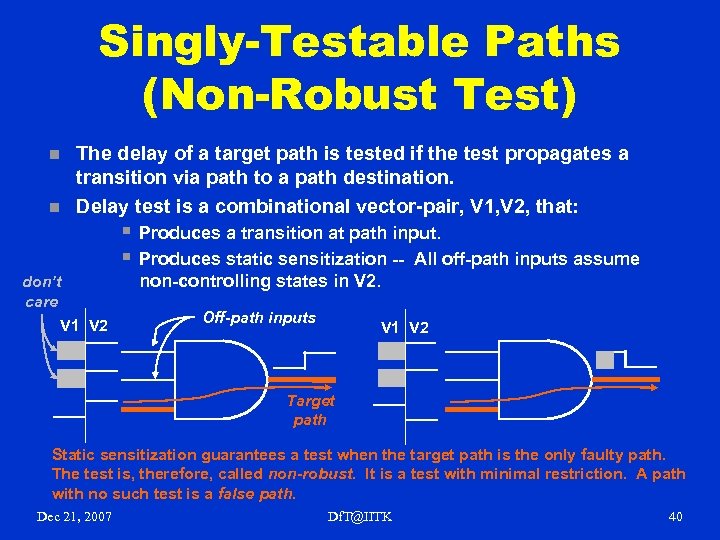

Singly-Testable Paths (Non-Robust Test) n n The delay of a target path is tested if the test propagates a transition via path to a path destination. Delay test is a combinational vector-pair, V 1, V 2, that: § § don’t care V 1 V 2 Produces a transition at path input. Produces static sensitization -- All off-path inputs assume non-controlling states in V 2. Off-path inputs V 1 V 2 Target path Static sensitization guarantees a test when the target path is the only faulty path. The test is, therefore, called non-robust. It is a test with minimal restriction. A path with no such test is a false path. Dec 21, 2007 Df. T@IITK 40

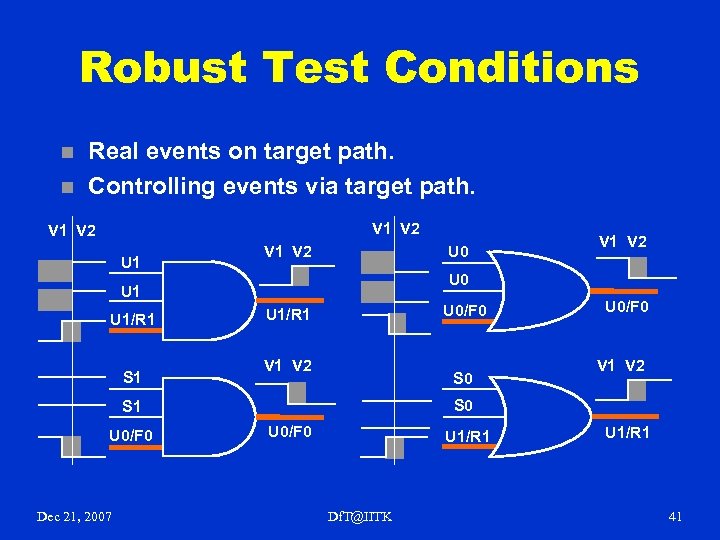

Robust Test Conditions n n Real events on target path. Controlling events via target path. V 1 V 2 U 1 U 0 V 1 V 2 U 0 U 1/R 1 S 1 U 0/F 0 U 1/R 1 V 2 S 0 Dec 21, 2007 U 0/F 0 V 1 V 2 S 0 S 1 U 0/F 0 V 1 V 2 U 0/F 0 U 1/R 1 Df. T@IITK U 1/R 1 41

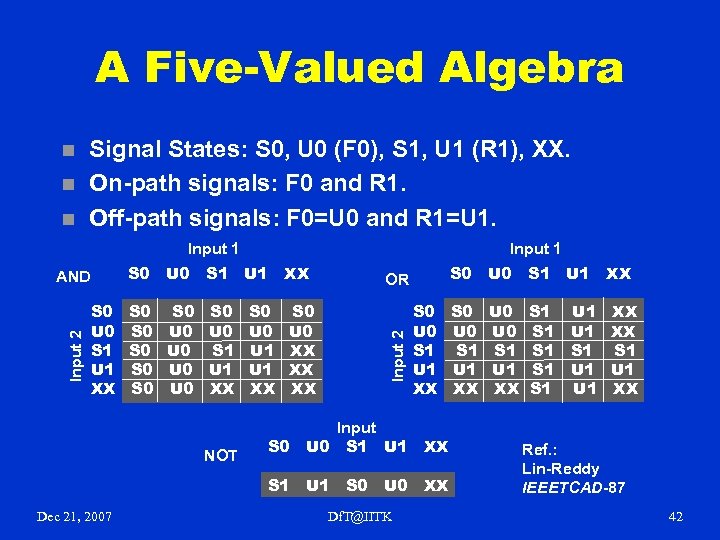

A Five-Valued Algebra n n n Signal States: S 0, U 0 (F 0), S 1, U 1 (R 1), XX. On-path signals: F 0 and R 1. Off-path signals: F 0=U 0 and R 1=U 1. Input 1 S 0 U 0 S 1 U 1 XX S 0 S 0 S 0 U 0 U 0 S 1 U 1 XX NOT S 0 U 1 U 1 XX S 0 U 0 XX XX XX S 0 U 0 S 1 U 1 XX OR Input 2 AND Input 1 S 0 U 0 S 1 U 1 XX Input S 0 U 0 S 1 U 1 XX S 1 U 1 S 0 U 0 XX Dec 21, 2007 Df. T@IITK S 0 U 0 S 1 U 1 XX S 1 U 1 XX S 1 S 1 U 1 XX Ref. : Lin-Reddy IEEETCAD-87 42

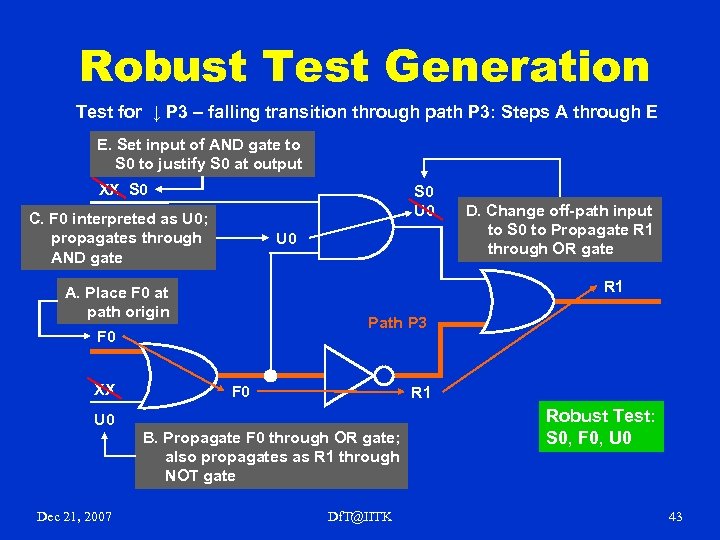

Robust Test Generation Test for ↓ P 3 – falling transition through path P 3: Steps A through E E. Set input of AND gate to S 0 to justify S 0 at output XX S 0 U 0 C. F 0 interpreted as U 0; propagates through AND gate U 0 R 1 A. Place F 0 at path origin Path P 3 F 0 XX U 0 Dec 21, 2007 D. Change off-path input to S 0 to Propagate R 1 through OR gate F 0 R 1 B. Propagate F 0 through OR gate; also propagates as R 1 through NOT gate Df. T@IITK Robust Test: S 0, F 0, U 0 43

fcc484cd9967d60d5e81f7945145cefb.ppt