04ea4dbc19e1b85f193f4f13fdc89aff.ppt

- Количество слайдов: 36

Department of computer Engineering ati. ttu. ee CEBE Seminar Digitaalsüsteemide diagnostika Jäneda mõis, Juuni 17, 2013 Raimund Ubar Tallinn University of Technology Department of Computer Engineering Estonia

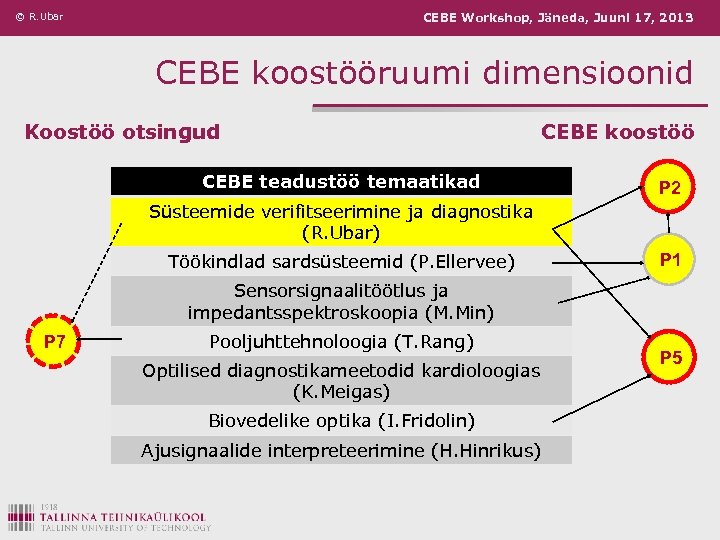

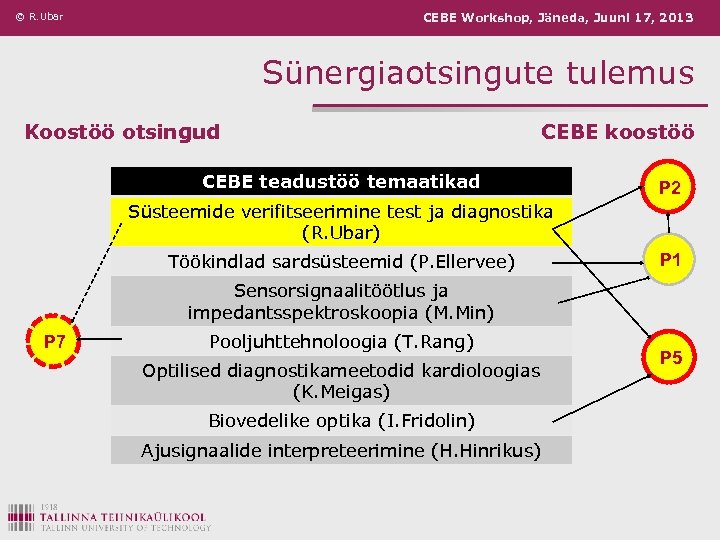

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 CEBE koostööruumi dimensioonid Koostöö otsingud CEBE teadustöö temaatikad CEBE koostöö P 2 Süsteemide verifitseerimine ja diagnostika (R. Ubar) Töökindlad sardsüsteemid (P. Ellervee) P 1 Sensorsignaalitöötlus ja impedantsspektroskoopia (M. Min) P 7 Pooljuhttehnoloogia (T. Rang) Optilised diagnostikameetodid kardioloogias (K. Meigas) Biovedelike optika (I. Fridolin) Ajusignaalide interpreteerimine (H. Hinrikus) P 5

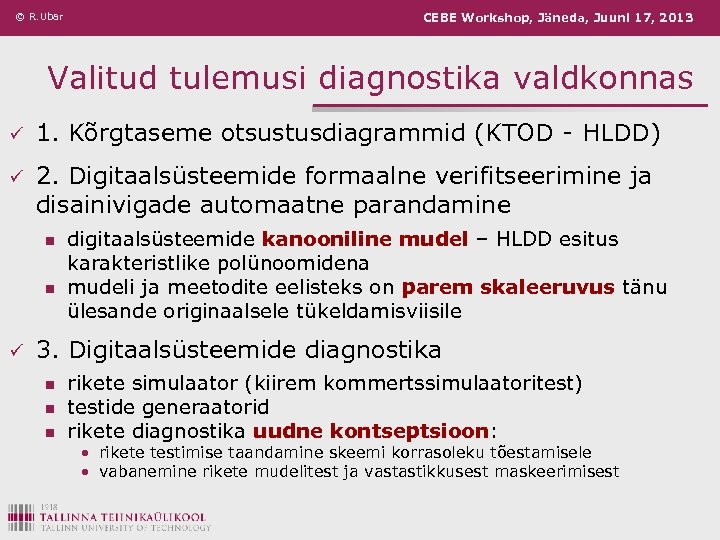

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Valitud tulemusi diagnostika valdkonnas ü 1. Kõrgtaseme otsustusdiagrammid (KTOD - HLDD) ü 2. Digitaalsüsteemide formaalne verifitseerimine ja disainivigade automaatne parandamine n n ü digitaalsüsteemide kanooniline mudel – HLDD esitus karakteristlike polünoomidena mudeli ja meetodite eelisteks on parem skaleeruvus tänu ülesande originaalsele tükeldamisviisile 3. Digitaalsüsteemide diagnostika n n n rikete simulaator (kiirem kommertssimulaatoritest) testide generaatorid rikete diagnostika uudne kontseptsioon: • rikete testimise taandamine skeemi korrasoleku tõestamisele • vabanemine rikete mudelitest ja vastastikkusest maskeerimisest

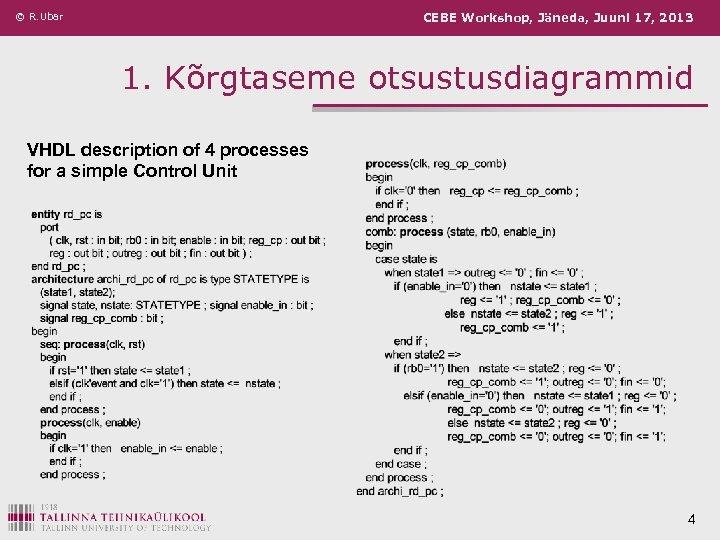

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 1. Kõrgtaseme otsustusdiagrammid VHDL description of 4 processes for a simple Control Unit 4

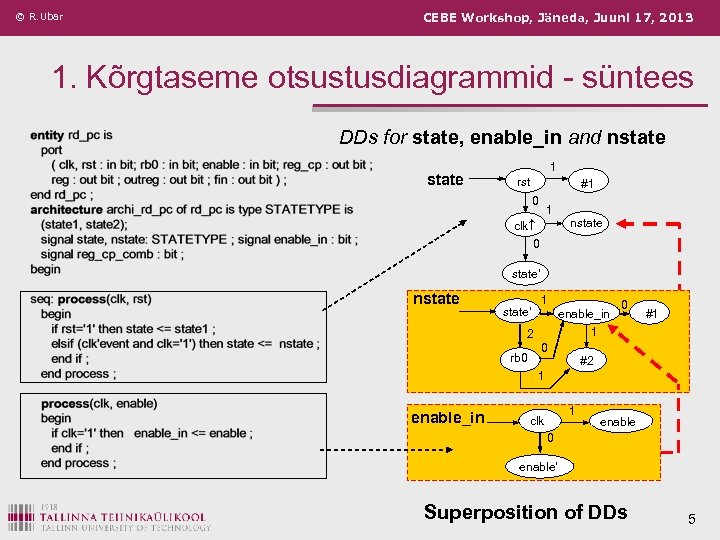

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 1. Kõrgtaseme otsustusdiagrammid - süntees DDs for state, enable_in and nstate 1 rst #1 0 1 nstate clk 0 state’ nstate’ 1 enable_in 1 2 rb 0 0 0 #1 #2 1 enable_in 1 clk enable 0 enable’ Superposition of DDs 5

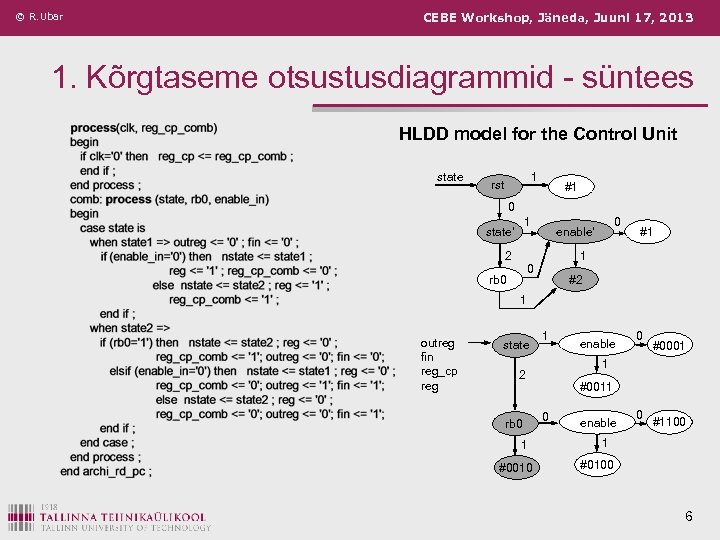

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 1. Kõrgtaseme otsustusdiagrammid - süntees HLDD model for the Control Unit state 1 rst #1 0 1 state’ 0 enable' 2 #1 1 0 rb 0 #2 1 outreg fin reg_cp reg state 1 1 #0010 0 #0001 1 2 rb 0 enable #0011 0 enable 0 #1100 1 #0100 6

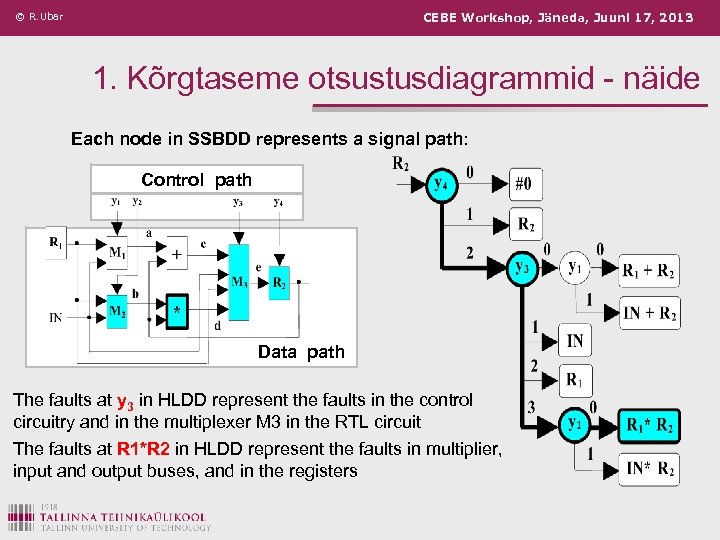

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 1. Kõrgtaseme otsustusdiagrammid - näide Each node in SSBDD represents a signal path: Control path Data path The faults at y 3 in HLDD represent the faults in the control circuitry and in the multiplexer M 3 in the RTL circuit The faults at R 1*R 2 in HLDD represent the faults in multiplier, input and output buses, and in the registers

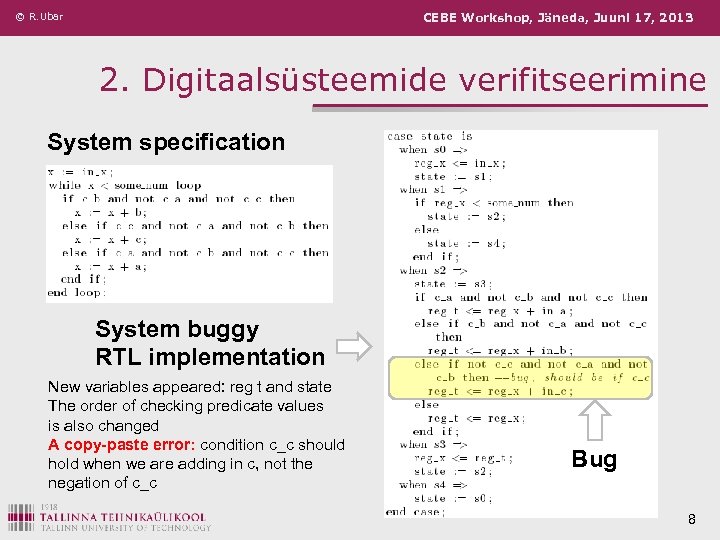

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 2. Digitaalsüsteemide verifitseerimine System specification System buggy RTL implementation New variables appeared: reg t and state The order of checking predicate values is also changed A copy-paste error: condition c_c should hold when we are adding in c, not the negation of c_c Bug 8

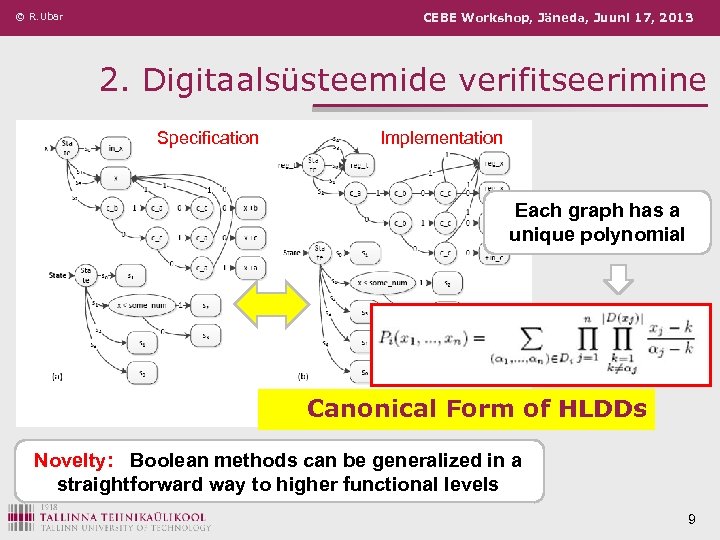

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 2. Digitaalsüsteemide verifitseerimine Specification Implementation Each graph has a unique polynomial Canonical Form of HLDDs Novelty: Boolean methods can be generalized in a straightforward way to higher functional levels 9

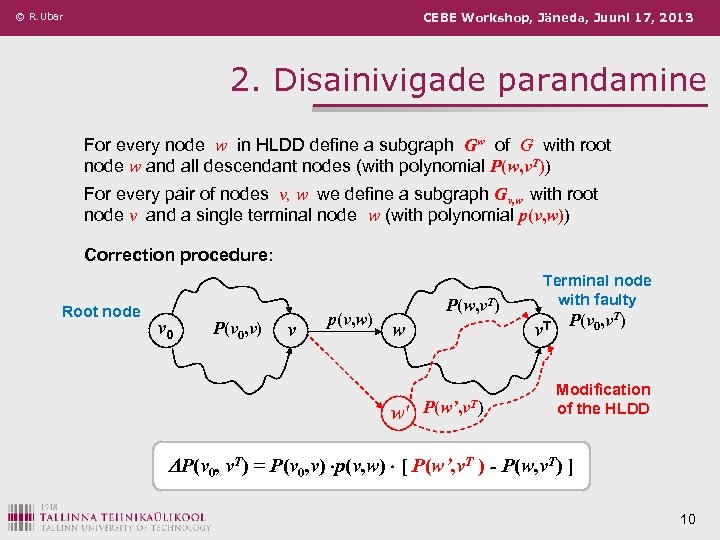

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 2. Disainivigade parandamine For every node w in HLDD define a subgraph Gw of G with root node w and all descendant nodes (with polynomial P(w, v. T)) For every pair of nodes v, w we define a subgraph Gv, w with root node v and a single terminal node w (with polynomial p(v, w)) Correction procedure: Root node v 0 P(v 0, v) v p(v, w) P(w, v. T) v. T w w' Terminal node with faulty P(w’, v. T) P(v 0, v. T) Modification of the HLDD P(v 0, v. T) = P(v 0, v) p(v, w) [ P(w’, v. T ) - P(w, v. T) ] 10

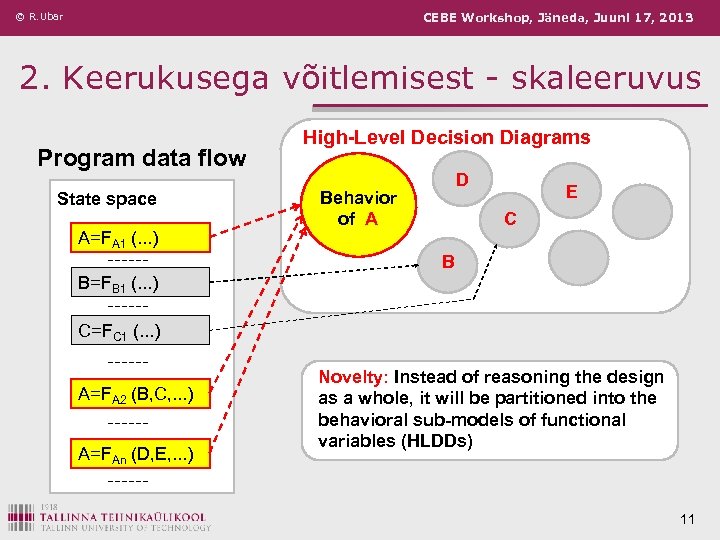

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 2. Keerukusega võitlemisest - skaleeruvus Program data flow State space A=FA 1 (. . . ) High-Level Decision Diagrams D Behavior of A E C B B=FB 1 (. . . ) C=FC 1 (. . . ) A=FA 2 (B, C, . . . ) A=FAn (D, E, . . . ) Novelty: Instead of reasoning the design as a whole, it will be partitioned into the behavioral sub-models of functional variables (HLDDs) 11

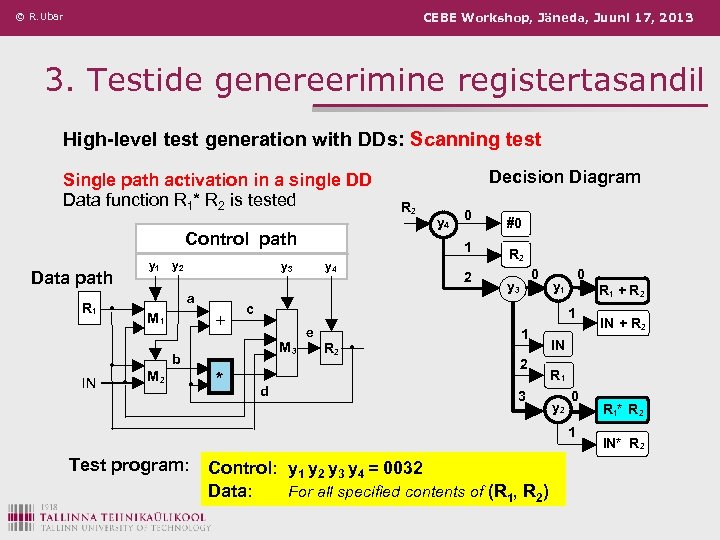

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Testide genereerimine registertasandil High-level test generation with DDs: Scanning test Single path activation in a single DD Data function R 1* R 2 is tested Control path y 1 Data path M 1 + · M 2 * 0 y 4 2 #0 R 2 0 y 3 0 y 1 R 1 + R 2 1 M 3 · y 4 c b · R 2 1 y 3 a R 1 · IN y 2 Decision Diagram e R 2 · 1 2 d 3 IN R 1 y 2 0 1 Test program: Control: y 1 y 2 y 3 y 4 = 0032 Data: For all specified contents of (R 1, R 2) IN + R 2 R 1* R 2 IN* R 2

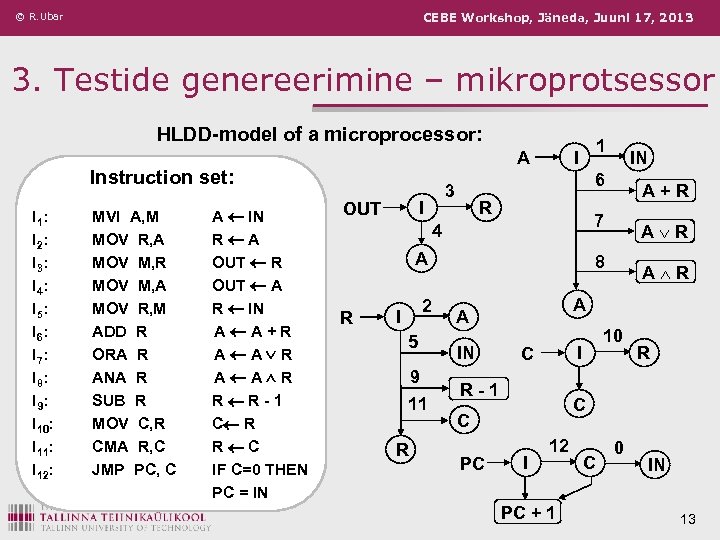

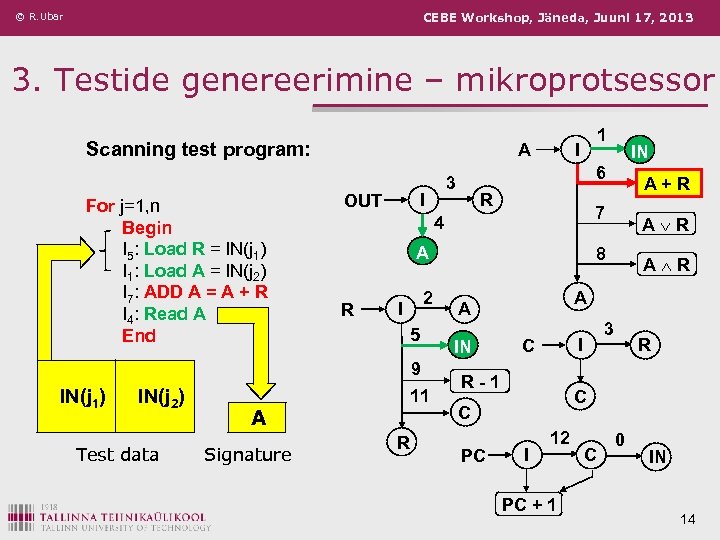

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Testide genereerimine – mikroprotsessor HLDD-model of a microprocessor: A Instruction set: I 1: I 2: I 3: I 4: I 5: I 6: I 7: I 8: I 9: I 10: I 11: I 12: MVI A, M MOV R, A MOV M, R MOV M, A MOV R, M ADD R ORA R ANA R SUB R MOV C, R CMA R, C JMP PC, C A IN R A OUT R OUT A R IN A A+R A A R R R-1 C R R C IF C=0 THEN PC = IN R A 2 I 5 9 11 R A+R 7 4 R IN 6 3 I OUT 1 I A R 8 A A IN 10 I C R-1 R C C PC A R I 12 PC + 1 C 0 IN 13

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Testide genereerimine – mikroprotsessor Scanning test program: For j=1, n Begin I 5: Load R = IN(j 1) I 1: Load A = IN(j 2) I 7: ADD A = A + R I 4: Read A End A IN(j 2) Test data A Signature R A R 2 I 5 11 R IN A+R 7 4 9 IN(j 1) I 6 3 I OUT 1 A R 8 A A IN 3 I C R-1 R C C PC A R I 12 PC + 1 C 0 IN 14

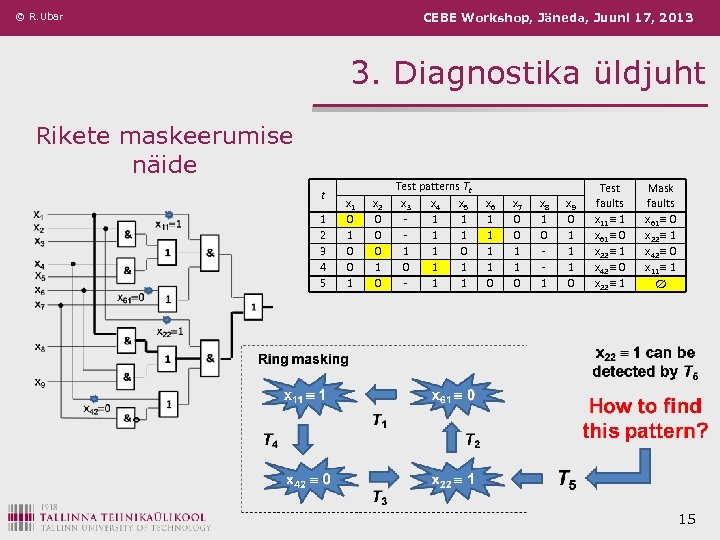

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Diagnostika üldjuht Rikete maskeerumise näide t 1 2 3 4 5 x 1 0 0 1 x 2 0 0 0 1 0 Test patterns Tt x 3 x 4 x 5 1 1 1 0 0 1 1 x 6 1 1 0 x 7 0 0 1 1 0 x 8 1 0 1 x 9 0 1 1 1 0 Test faults x 11 1 x 61 0 x 22 1 x 42 0 x 22 1 Mask faults x 61 0 x 22 1 x 42 0 x 11 1 15

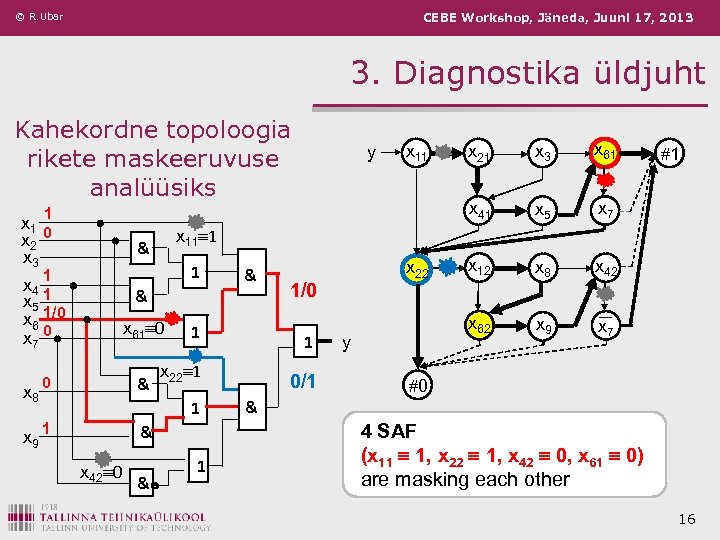

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Diagnostika üldjuht Kahekordne topoloogia rikete maskeeruvuse analüüsiks 1 x 0 1 1 x 4 x 5 1 x 6 1/0 0 x 61 0 0 & & x 7 x 8 x 9 & x 61 x 5 x 7 x 12 x 8 x 42 x 62 1 x 22 1/0 1 x 22 1 & x 42 0 & 1 1 1 x 3 x 9 x 7 1 x 11 1 & 2 x 3 x 11 x 21 x 41 y 0/1 y 0 & 4 SAF (x 11 1, x 22 1, x 42 0, x 61 0) are masking each other 16

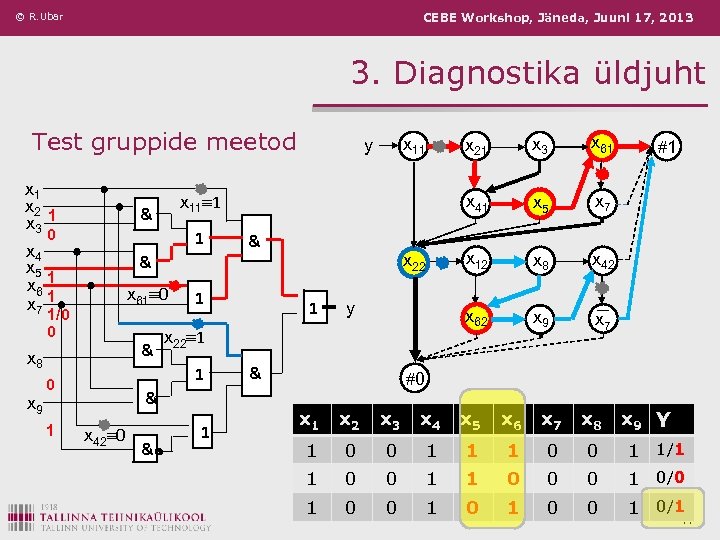

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 3. Diagnostika üldjuht Test gruppide meetod x 1 x 2 x 3 1 0 1 & x 61 0 1/0 0 & x 8 x 9 & x 42 0 & 1 y x 22 1 1 0 1 1 1 & x 5 x 7 x 12 x 22 x 61 x 8 x 42 x 62 & x 3 x 41 x 11 1 & x 4 x 5 x 6 1 x 7 1 x 21 x 11 y x 9 x 7 1 0 x 9 Y x 1 x 2 x 3 x 4 x 5 x 6 x 7 x 8 1 0 0 1 1/1 1 0 0 0 1 0/0 1 0/1 17

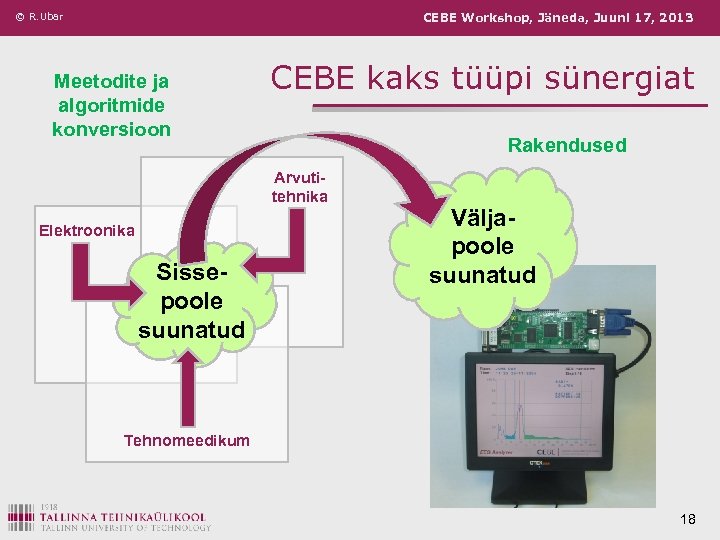

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Meetodite ja algoritmide konversioon CEBE kaks tüüpi sünergiat Rakendused Arvutitehnika Elektroonika Sissepoole suunatud Väljapoole suunatud Tehnomeedikum 18

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Sünergiaotsingute tulemus Koostöö otsingud CEBE koostöö CEBE teadustöö temaatikad P 2 Süsteemide verifitseerimine test ja diagnostika (R. Ubar) Töökindlad sardsüsteemid (P. Ellervee) P 1 Sensorsignaalitöötlus ja impedantsspektroskoopia (M. Min) P 7 Pooljuhttehnoloogia (T. Rang) Optilised diagnostikameetodid kardioloogias (K. Meigas) Biovedelike optika (I. Fridolin) Ajusignaalide interpreteerimine (H. Hinrikus) P 5

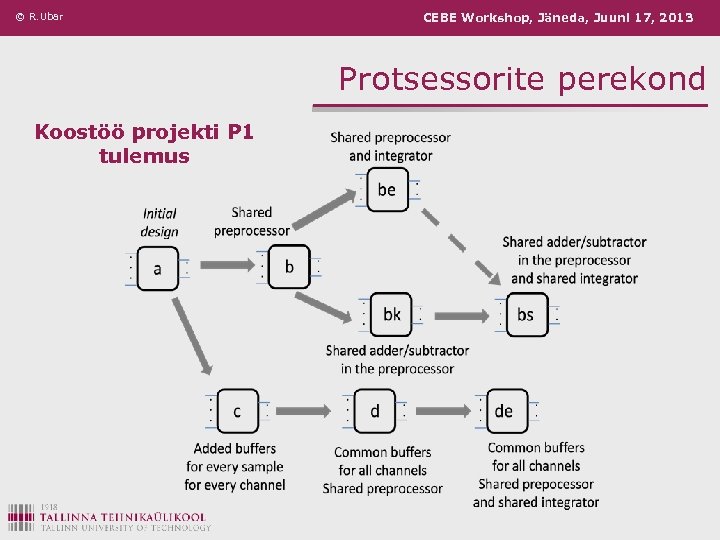

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Protsessorite perekond Koostöö projekti P 1 tulemus

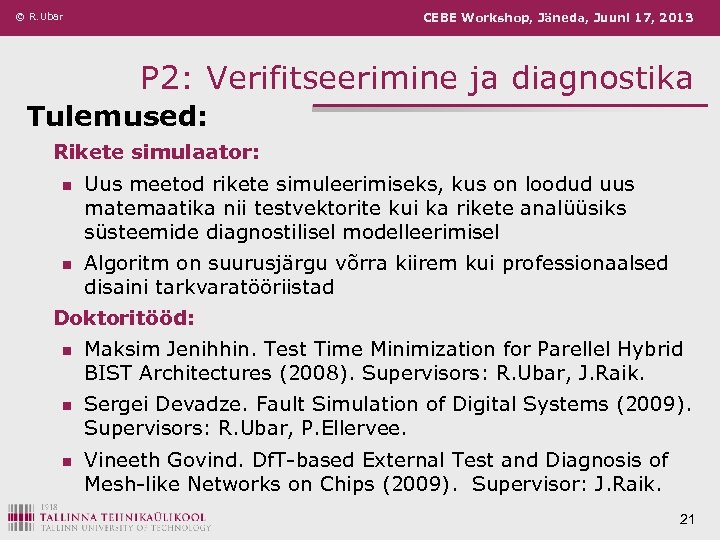

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 P 2: Verifitseerimine ja diagnostika Tulemused: Rikete simulaator: n Uus meetod rikete simuleerimiseks, kus on loodud uus matemaatika nii testvektorite kui ka rikete analüüsiks süsteemide diagnostilisel modelleerimisel n Algoritm on suurusjärgu võrra kiirem kui professionaalsed disaini tarkvaratööriistad Doktoritööd: n Maksim Jenihhin. Test Time Minimization for Parellel Hybrid BIST Architectures (2008). Supervisors: R. Ubar, J. Raik. n Sergei Devadze. Fault Simulation of Digital Systems (2009). Supervisors: R. Ubar, P. Ellervee. n Vineeth Govind. Df. T-based External Test and Diagnosis of Mesh-like Networks on Chips (2009). Supervisor: J. Raik. 21

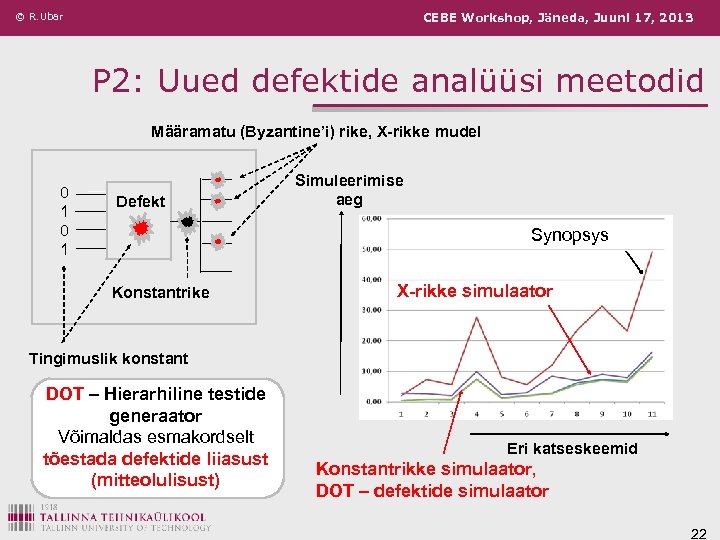

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 P 2: Uued defektide analüüsi meetodid Määramatu (Byzantine’i) rike, X-rikke mudel 0 1 Defekt Simuleerimise aeg Synopsys Konstantrike X-rikke simulaator Tingimuslik konstant DOT – Hierarhiline testide generaator Võimaldas esmakordselt tõestada defektide liiasust (mitteolulisust) Eri katseskeemid Konstantrikke simulaator, DOT – defektide simulaator 22

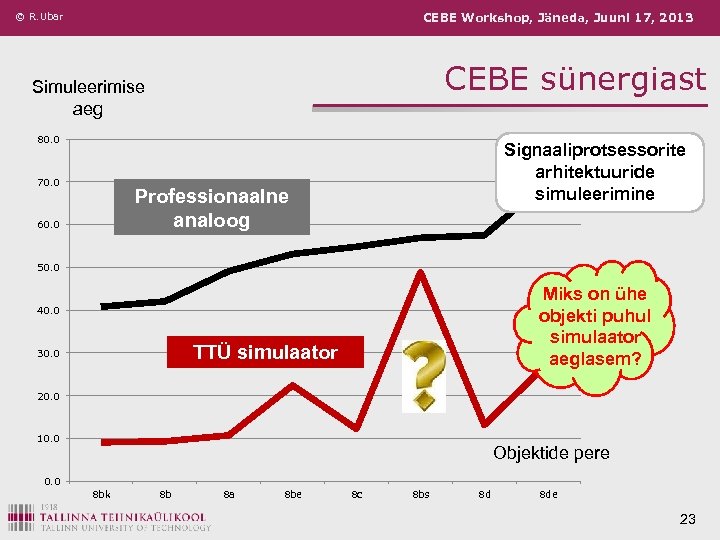

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 CEBE sünergiast Simuleerimise aeg 80. 0 70. 0 Signaaliprotsessorite arhitektuuride simuleerimine Professionaalne analoog 60. 0 50. 0 Miks on ühe Tetra. MAX objekti puhul Macro-2 simulaator aeglasem? 40. 0 TTÜ simulaator 30. 0 20. 0 10. 0 Objektide pere 0. 0 8 bk 8 b 8 a 8 be 8 c 8 bs 8 d 8 de 23

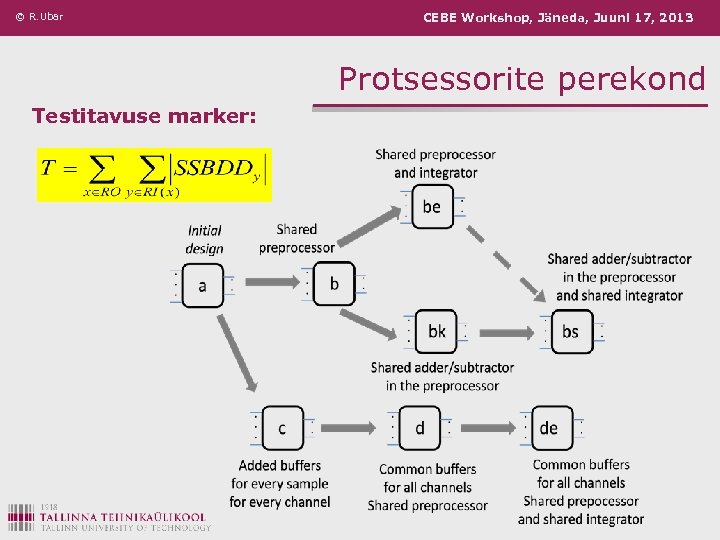

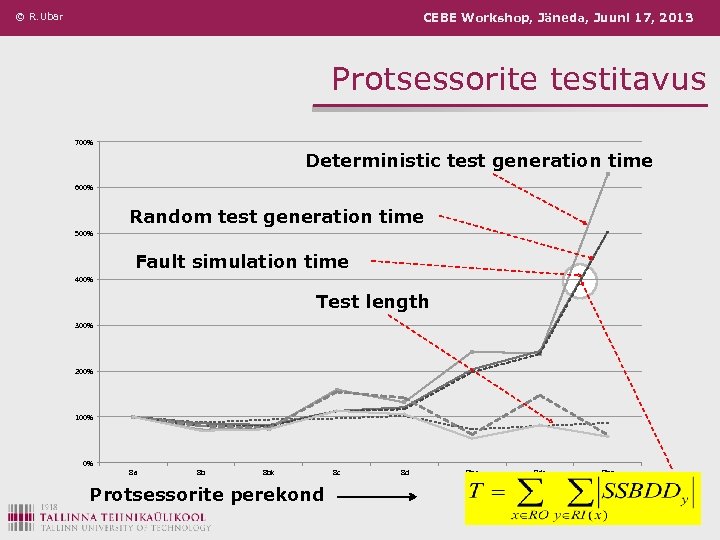

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Protsessorite perekond Testitavuse marker:

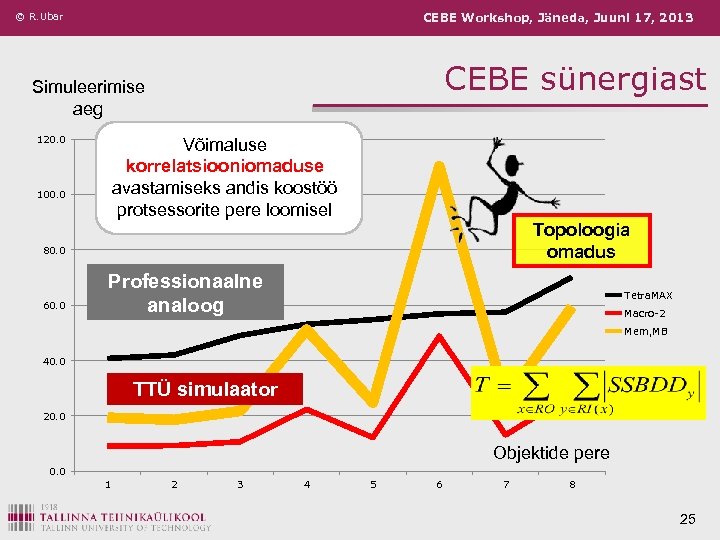

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 CEBE sünergiast Simuleerimise aeg 120. 0 Võimaluse korrelatsiooniomaduse avastamiseks andis koostöö protsessorite pere loomisel 100. 0 Topoloogia omadus 80. 0 60. 0 Professionaalne analoog Tetra. MAX Macro-2 Mem, MB 40. 0 TTÜ simulaator 20. 0 Objektide pere 0. 0 1 2 3 4 5 6 7 8 25

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Protsessorite testitavus 700% Deterministic test generation time 600% Random test generation time 500% Fault simulation time 400% Test length 300% 200% 100% 0% 8 a 8 b 8 bk Protsessorite perekond 8 c 8 d 8 be 8 de 8 bs

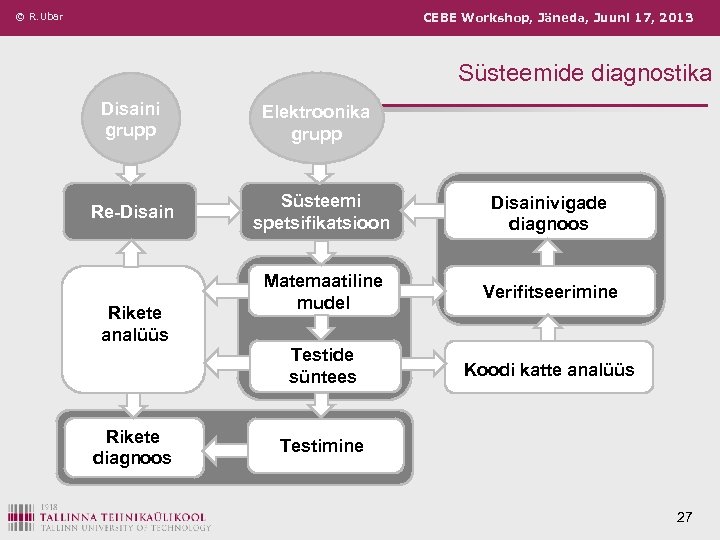

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Süsteemide diagnostika Disaini grupp Elektroonika grupp Re-Disain Süsteemi spetsifikatsioon Disainivigade diagnoos Matemaatiline mudel Verifitseerimine Testide süntees Koodi katte analüüs Rikete diagnoos Testimine 27

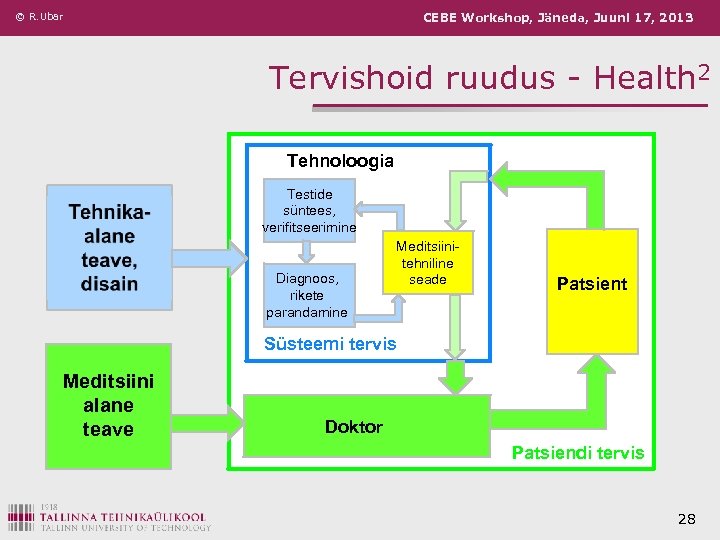

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Tervishoid ruudus - Health 2 Tehnoloogia Testide süntees, verifitseerimine Diagnoos, rikete parandamine Meditsiinitehniline seade Patsient Süsteemi tervis Meditsiini alane teave Doktor Patsiendi tervis 28

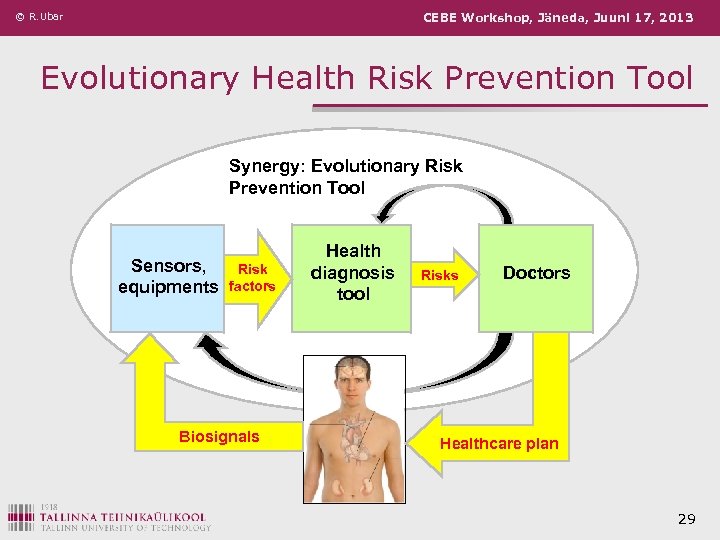

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Evolutionary Health Risk Prevention Tool Synergy: Evolutionary Risk Prevention Tool Sensors, equipments Risk factors Biosignals Health diagnosis tool Risks Doctors Healthcare plan 29

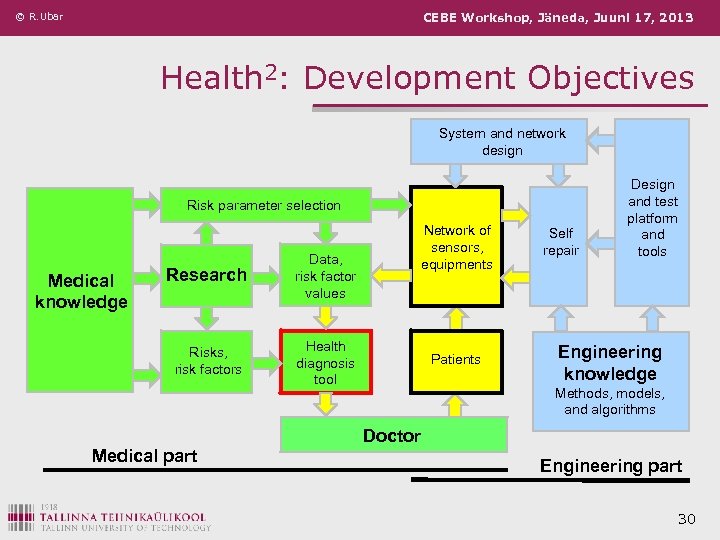

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Health 2: Development Objectives System and network design Risk parameter selection Research Data, risk factor values Risks, risk factors Medical knowledge Network of sensors, equipments Health diagnosis tool Medical part Patients Self repair Design and test platform and tools Engineering knowledge Methods, models, and algorithms Doctor Engineering part 30

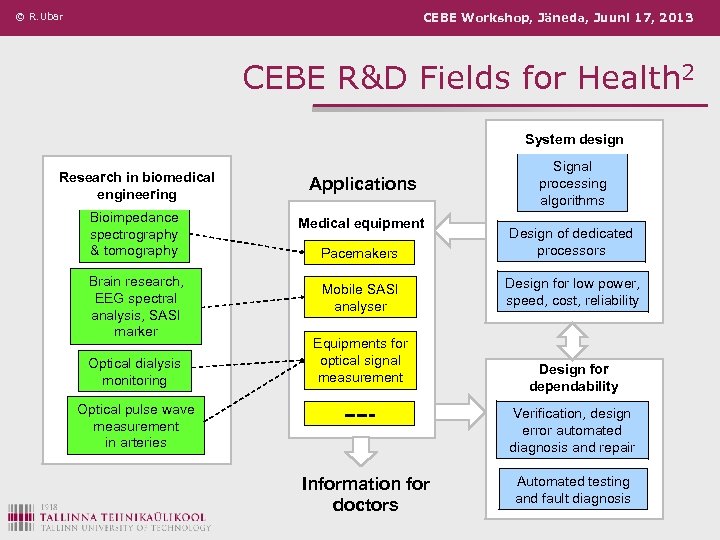

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 CEBE R&D Fields for Health 2 System design Research in biomedical engineering Applications Bioimpedance spectrography & tomography Medical equipment Brain research, EEG spectral analysis, SASI marker Optical dialysis monitoring Signal processing algorithms Pacemakers Design of dedicated processors Mobile SASI analyser Design for low power, speed, cost, reliability Equipments for optical signal measurement Optical pulse wave measurement in arteries Design for dependability Verification, design error automated diagnosis and repair Information for doctors Automated testing and fault diagnosis

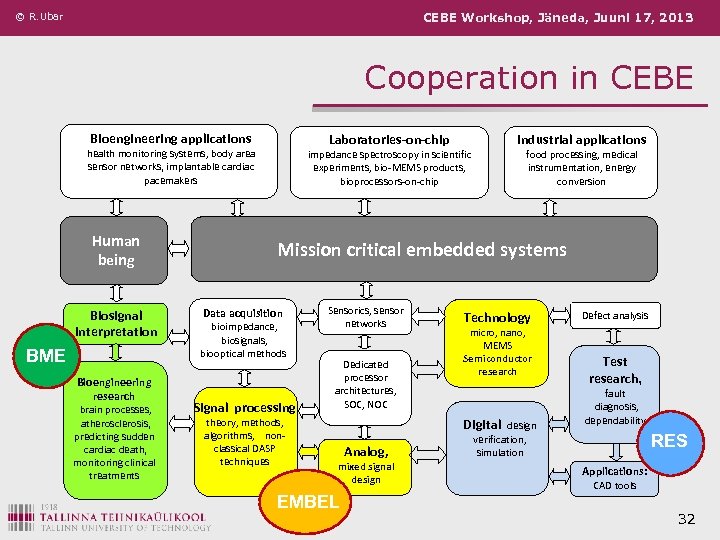

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Cooperation in CEBE Bioengineering applications Laboratories-on-chip health monitoring systems, body area sensor networks, implantable cardiac pacemakers Human being Biosignal interpretation BME Bioengineering research brain processes, atherosclerosis, predicting sudden cardiac death, monitoring clinical treatments Industrial applications impedance spectroscopy in scientific experiments, bio-MEMS products, bioprocessors-on-chip food processing, medical instrumentation, energy conversion Mission critical embedded systems Data acquisition bioimpedance, biosignals, biooptical methods Signal processing theory, methods, algorithms, nonclassical DASP techniques Sensorics, sensor networks Dedicated processor architectures, SOC, NOC Technology micro, nano, MEMS Semiconductor research Digital Analog, mixed signal design EMBEL design verification, simulation Defect analysis Test research, fault diagnosis, dependability RES Applications: CAD tools 32

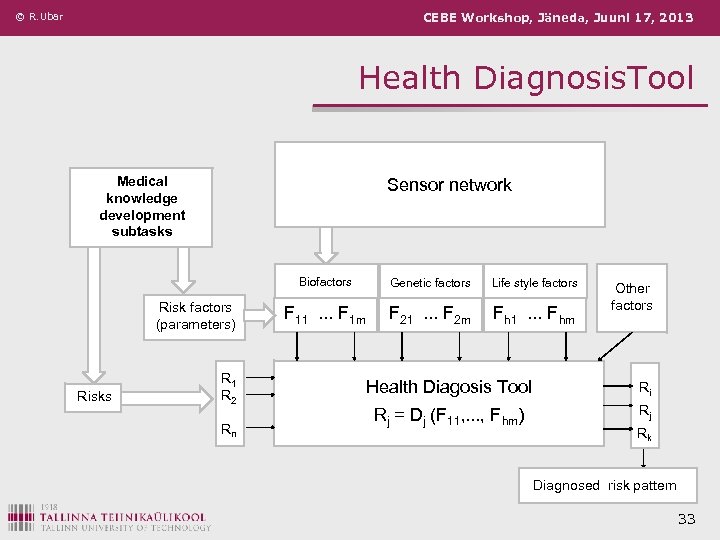

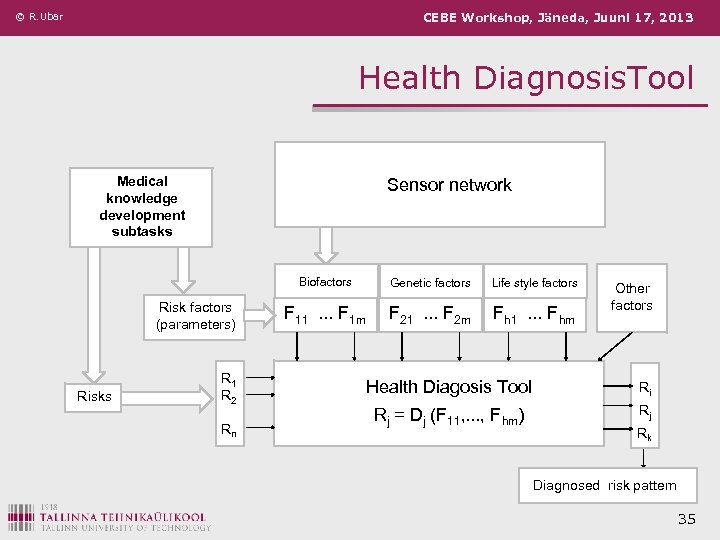

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Health Diagnosis. Tool Medical knowledge development subtasks Sensor network Biofactors Risk factors (parameters) Risks R 1 R 2 Rn Genetic factors Life style factors F 11. . . F 1 m F 21. . . F 2 m Fh 1. . . Fhm Other factors Health Diagosis Tool Ri Rj = Dj (F 11, . . . , Fhm) Rj Rk Diagnosed risk pattern 33

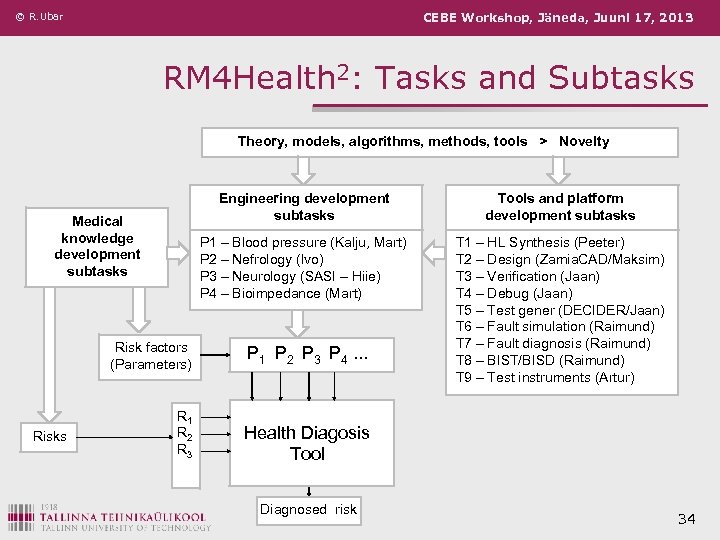

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 RM 4 Health 2: Tasks and Subtasks Theory, models, algorithms, methods, tools > Novelty Engineering development subtasks P 1 – Blood pressure (Kalju, Mart) P 2 – Nefrology (Ivo) P 3 – Neurology (SASI – Hiie) P 4 – Bioimpedance (Mart) Medical knowledge development subtasks Tools and platform development subtasks T 1 – HL Synthesis (Peeter) T 2 – Design (Zamia. CAD/Maksim) T 3 – Verification (Jaan) T 4 – Debug (Jaan) T 5 – Test gener (DECIDER/Jaan) T 6 – Fault simulation (Raimund) T 7 – Fault diagnosis (Raimund) T 8 – BIST/BISD (Raimund) T 9 – Test instruments (Artur) Risk factors (Parameters) Risks P 1 P 2 P 3 P 4. . . R 1 R 2 R 3 Health Diagosis Tool Diagnosed risk 34

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 Health Diagnosis. Tool Medical knowledge development subtasks Sensor network Biofactors Risk factors (parameters) Risks R 1 R 2 Rn Genetic factors Life style factors F 11. . . F 1 m F 21. . . F 2 m Fh 1. . . Fhm Other factors Health Diagosis Tool Ri Rj = Dj (F 11, . . . , Fhm) Rj Rk Diagnosed risk pattern 35

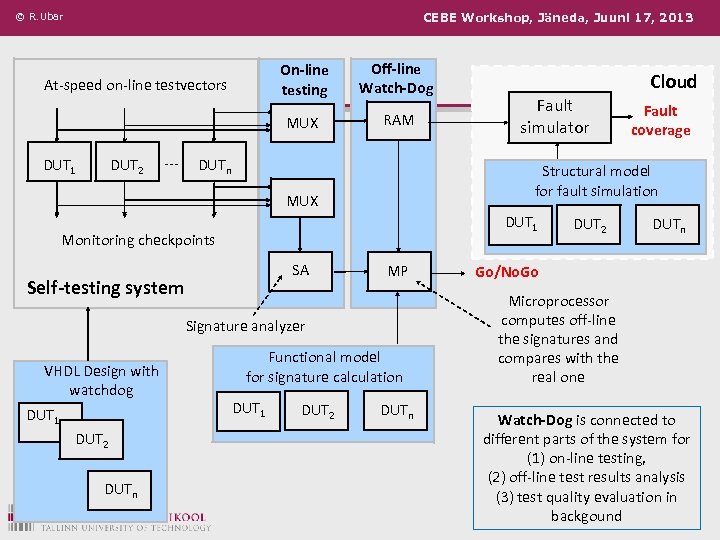

© R. Ubar CEBE Workshop, Jäneda, Juuni 17, 2013 On-line testing MUX At-speed on-line testvectors DUT 1 DUT 2 --- Off-line Watch-Dog RAM DUTn DUT 1 Monitoring checkpoints SA Self-testing system MP Signature analyzer DUT 1 DUT 2 DUTn Fault simulator Functional model for signature calculation DUT 1 DUT 2 Fault coverage Structural model for fault simulation MUX VHDL Design with watchdog Cloud DUTn DUT 2 DUTn Go/No. Go Microprocessor computes off-line the signatures and compares with the real one Watch-Dog is connected to different parts of the system for (1) on-line testing, (2) off-line test results analysis (3) test quality evaluation in backgound

04ea4dbc19e1b85f193f4f13fdc89aff.ppt