Департамент образования города Москвы

Департамент образования города Москвы Государственное автономное образовательное учреждение высшего образования города Москвы «Московский городской педагогический университет» Институт математики, информатики и естественных наук Учебная дисциплина «Информатика» Лекция 7 -8 Тема лекции: Логические элементы. Базис цифровой вычислительной техники и история развития средств ВТ. А. В. Полтавский

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ И СХЕМЫ ЭВМ Логика - наука, изучающая методы установления истинности или лож- ности одних высказываний на основе истинности или ложности других высказываний (утверждений). Логика составляет основу всякого управления, в том числе технологическими процессами и управления компьютером. Математическая логика - современная форма логики, опирающаяся на формальные математические методы. Основные объекты логики - высказывания, т. е. предложения, которые могут быть либо истинными ДА=1, либо ложными НЕТ=0.

Работа первых ЭВМ • Управляющий блок (УУ) координирует работу всей ЭВМ, последовательно получая из памяти по одной команде. • В начале вычислений программа и числовые данные ( информация ) считываются входным устройством и засылаются в ячейки памяти. Затем первая команда посылается в УУ. Если программа предусматривает выполнение арифметической операции, УУ посылает команду произвести операцию. Команда направляе- тся также и в блок памяти. Команда содержит номера ячеек, хранящих числа, необходимых для проведения операций ( сложение, вычитание. . . ). АУ выполняет требуемую операцию и снова отправляет результат в ячейки памяти. • Другая команда от УУ содержит номер ячейки, в которой следует «приказ» , что надо поместить этот «электронный» результат в этой ячейке.

Первые цифровые ЭВМ России

Основа (базис) процессора • Основной частью ЭВМ (для обработки данных ( информации ) является процессор, состоящий из электронных устройств - арифметическое устройство (АУ) и устройства управления (УУ). • В своей работе УУ руководствуется командами программы, читаемой из памяти запоминающего устройства (ЗУ).

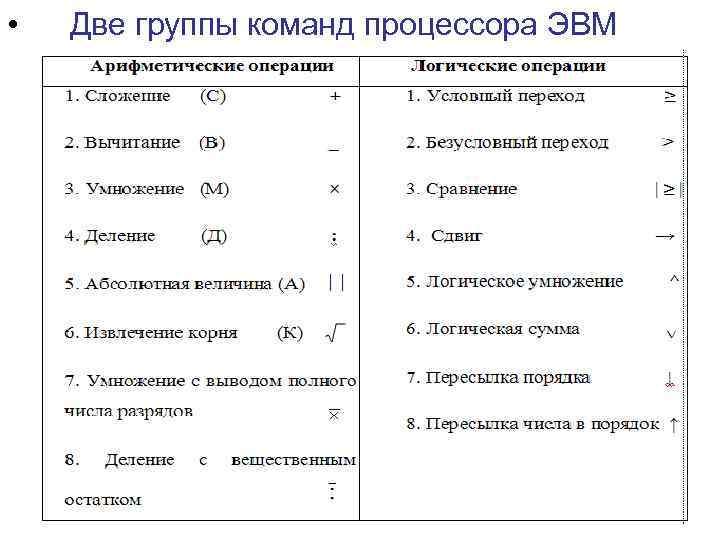

• Две группы команд процессора ЭВМ

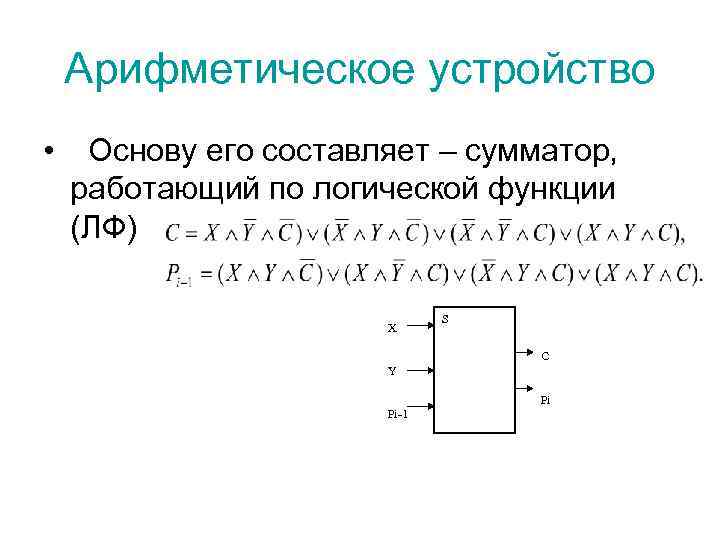

Арифметическое устройство • Основу его составляет – сумматор, работающий по логической функции (ЛФ) S X C Y Pi-1

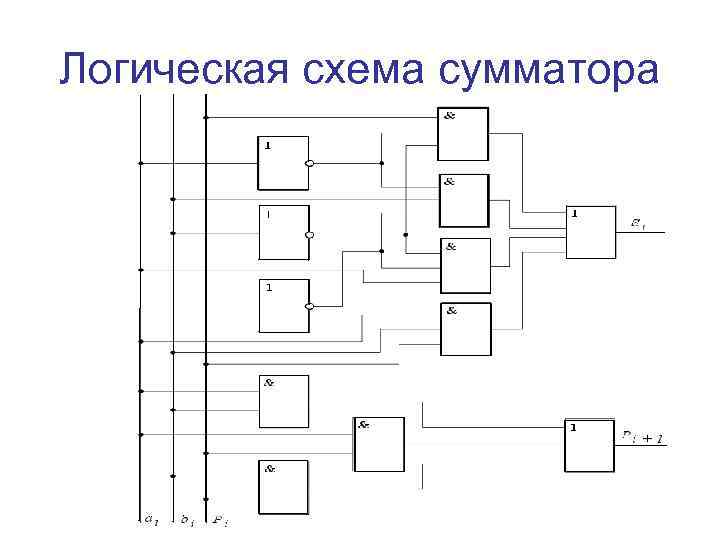

Логическая схема сумматора

Логический элемент НЕ - ИНВЕРТОР 1 А У= ┐А C F Б К Выход R 1 Rн D 1 Э НЕ Вход R 2 А 0 V -5 V -2 V +5 V

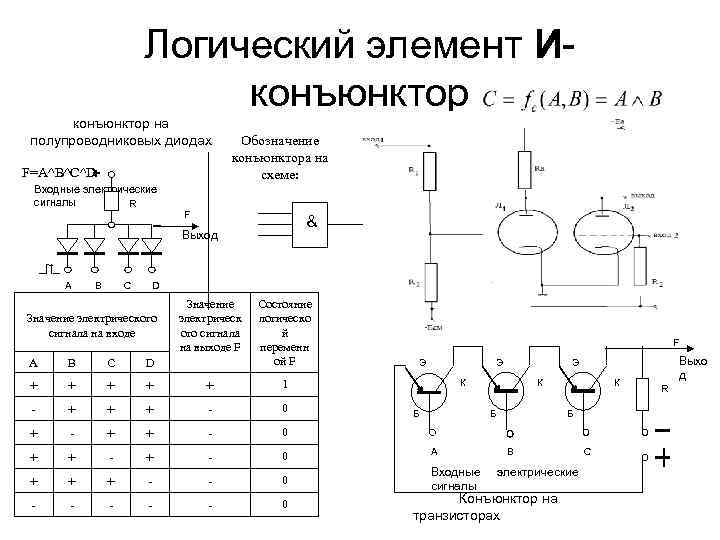

Логический элемент И- конъюнктор на полупроводниковых диодах Обозначение конъюнктора на F=A^B^C^D+ схеме: Входные электрические сигналы R F & Выход A B C D Значение Состояние Значение электрического электрическ логическо сигнала на входе ого сигнала й F на выходе F переменн A B C D ой F Э Э Выхо д + + + 1 К К R - + + + - 0 Б Б + - + + - 0 А В С + + - 0 Входные электрические + + + - - 0 сигналы - - - 0 Конъюнктор на транзисторах

Логический элемент ИЛИ- дизъюнктор F=Av. Bv. Cv. D Обозначение дизъюнктора на Входные электрические схеме: сигналы B A C D 1 F Выход R Дизъюнктор на полупроводниковых диодах F Значение Состояние Выхо Значение электрического электрическог логической Э Э д сигнала на входе о сигнала на переменной К R выходе F F A B C D Б Б + + + + 1 А В С - + + + 1 Входной + - + + 1 сигнал + + - + 1 + + + - + 1 Дизъюнктор на транзисторах - - - - - 0

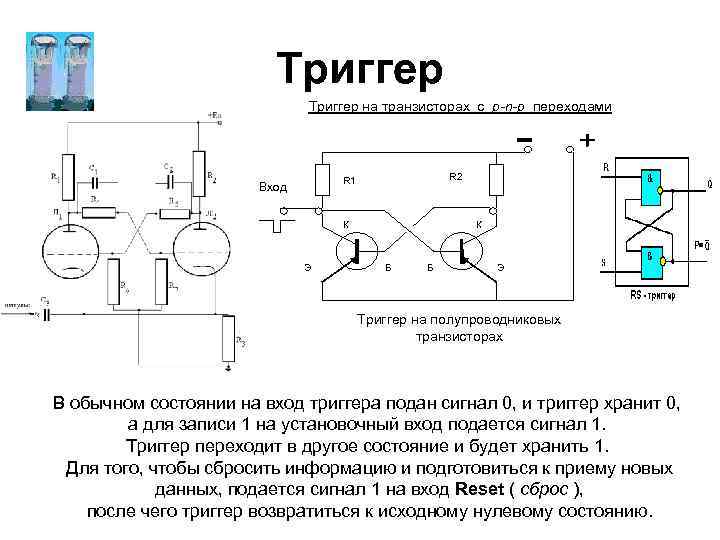

Триггер на транзисторах с p-n-p переходами R 1 R 2 Вход К Э Б Б Э Триггер на полупроводниковых транзисторах В обычном состоянии на вход триггера подан сигнал 0, и триггер хранит 0, а для записи 1 на установочный вход подается сигнал 1. Триггер переходит в другое состояние и будет хранить 1. Для того, чтобы сбросить информацию и подготовиться к приему новых данных, подается сигнал 1 на вход Reset ( сброс ), после чего триггер возвратиться к исходному нулевому состоянию.

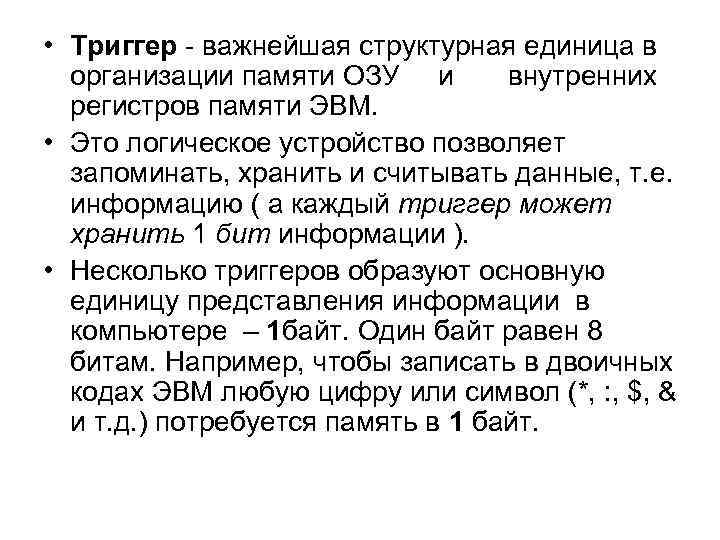

• Триггер - важнейшая структурная единица в организации памяти ОЗУ и внутренних регистров памяти ЭВМ. • Это логическое устройство позволяет запоминать, хранить и считывать данные, т. е. информацию ( а каждый триггер может хранить 1 бит информации ). • Несколько триггеров образуют основную единицу представления информации в компьютере – 1 байт. Один байт равен 8 битам. Например, чтобы записать в двоичных кодах ЭВМ любую цифру или символ (*, : , $, & и т. д. ) потребуется память в 1 байт.

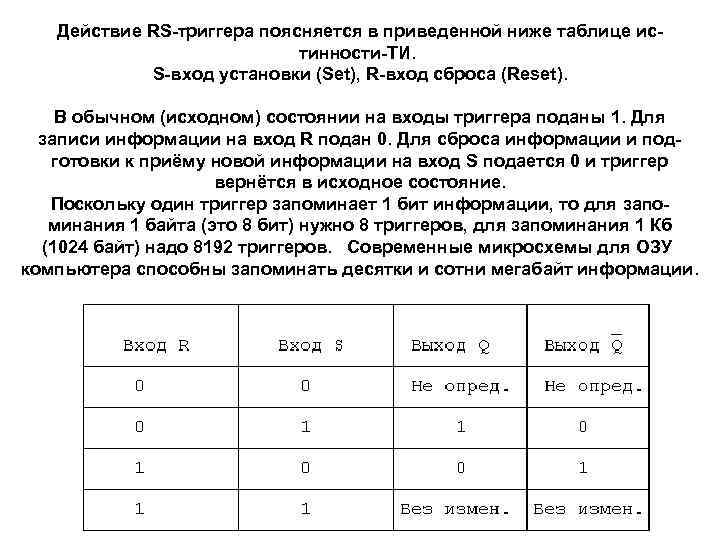

Действие RS-триггера поясняется в приведенной ниже таблице ис- тинности-ТИ. S-вход установки (Set), R-вход сброса (Reset). В обычном (исходном) состоянии на входы триггера поданы 1. Для записи информации на вход R подан 0. Для сброса информации и под- готовки к приёму новой информации на вход S подается 0 и триггер вернётся в исходное состояние. Поскольку один триггер запоминает 1 бит информации, то для запо- минания 1 байта (это 8 бит) нужно 8 триггеров, для запоминания 1 Кб (1024 байт) надо 8192 триггеров. Современные микросхемы для ОЗУ компьютера способны запоминать десятки и сотни мегабайт информации.

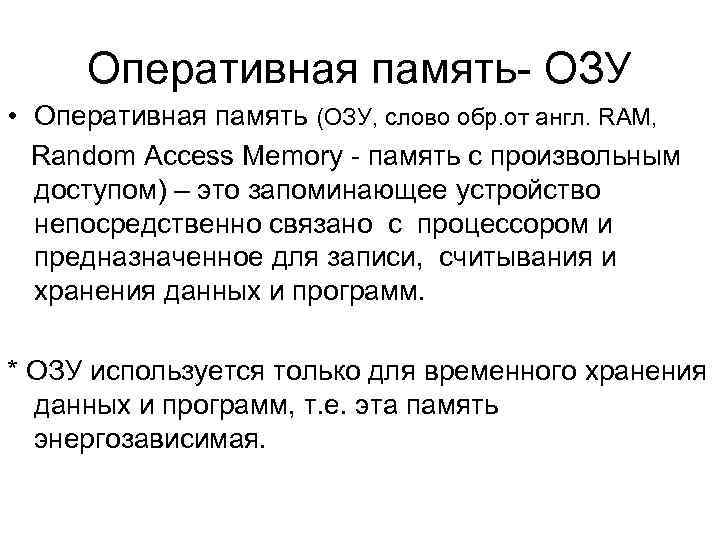

Оперативная память- ОЗУ • Оперативная память (ОЗУ, слово обр. от англ. RAM, Random Access Memory - память с произвольным доступом) – это запоминающее устройство непосредственно связано с процессором и предназначенное для записи, считывания и хранения данных и программ. * ОЗУ используется только для временного хранения данных и программ, т. е. эта память энергозависимая.

ШТРИХ ШЕФФЕРА И-НЕ Это электронный логический вентиль И-НЕ логическое устройство – штрих Шеффера*, Состоящее из конъюнктора и инвертора, соединенных последовательно, на выходе которого будет низкий логический уровень только в том случае, если на обоих входах – на входе А и на входе В – будет высокий уровень. Если уровни А и В – oбa высокие, то оба последовательно включенные n-канальные МОП – ключи T 1 и Т 2 – находятся в проводящем состоянии, фиксируя на выходе Потенциал земли; Входы А, В p-канальные ключи Т 3 и Т 4 будут разомкнуты, Схематизация КМОП – логические вентили И-НЕ ток через них не тече. Т. Схематизация европейского стандарта устройства И-НЕ * Штрих Ше ффера – бинарная логическая операция, т. е. булева функция над двумя переменными. Впервые эта ЛФ введена Генри Шеффером в 1913 г.

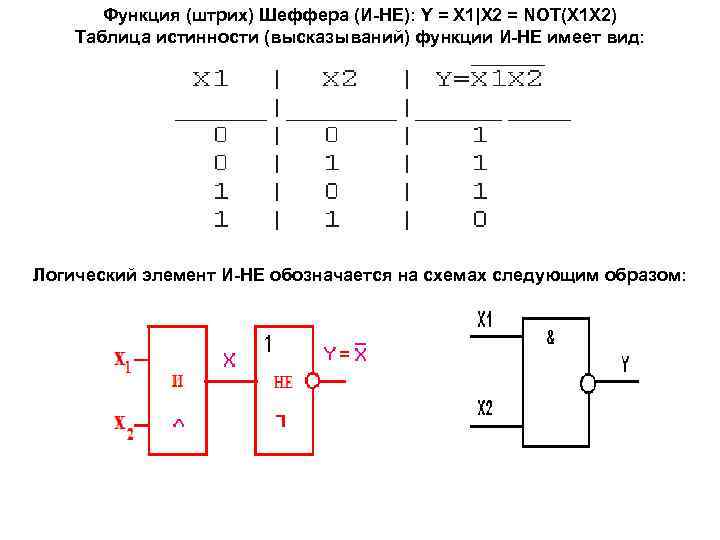

Функция (штрих) Шеффера (И-НЕ): Y = X 1|X 2 = NOT(X 1 X 2) Таблица истинности (высказываний) функции И-НЕ имеет вид: Логический элемент И-НЕ обозначается на схемах следующим образом:

СТРЕЛКА ПИРСА • СХЕМАТИЗАЦИЯ ЛЭ «ИЛИ–НЕ» • САМОСТОЯТЕЛЬНО (5 минут) • А) зарисовать логическую схему • Б) показать работу (высказывания) данного ЛЭ в таблице истинности -ТИ

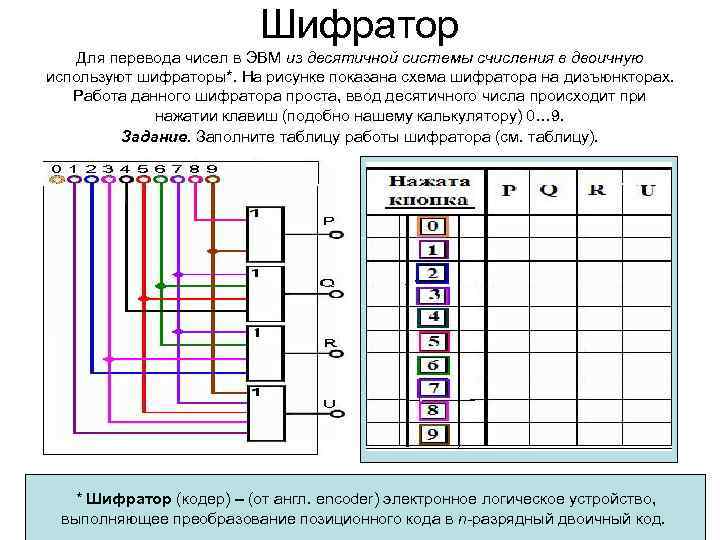

Шифратор Для перевода чисел в ЭВМ из десятичной системы счисления в двоичную используют шифраторы*. На рисунке показана схема шифратора на дизъюнкторах. Работа данного шифратора проста, ввод десятичного числа происходит при нажатии клавиш (подобно нашему калькулятору) 0… 9. Задание. Заполните таблицу работы шифратора (см. таблицу). * Шифратор (кодер) – (от англ. encoder) электронное логическое устройство, выполняющее преобразование позиционного кода в n-разрядный двоичный код.

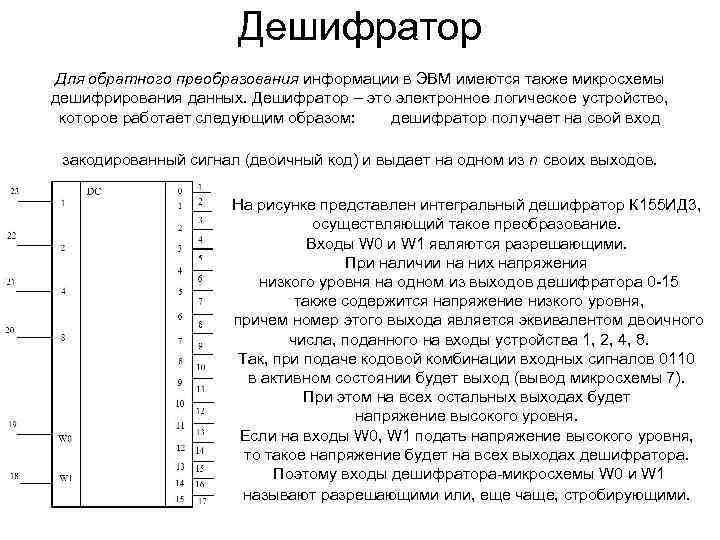

Дешифратор Для обратного преобразования информации в ЭВМ имеются также микросхемы дешифрирования данных. Дешифратор – это электронное логическое устройство, которое работает следующим образом: дешифратор получает на свой вход закодированный сигнал (двоичный код) и выдает на одном из n своих выходов. На рисунке представлен интегральный дешифратор К 155 ИД 3, осуществляющий такое преобразование. Входы W 0 и W 1 являются разрешающими. При наличии на них напряжения низкого уровня на одном из выходов дешифратора 0 -15 также содержится напряжение низкого уровня, причем номер этого выхода является эквивалентом двоичного числа, поданного на входы устройства 1, 2, 4, 8. Так, при подаче кодовой комбинации входных сигналов 0110 в активном состоянии будет выход (вывод микросхемы 7). При этом на всех остальных выходах будет напряжение высокого уровня. Если на входы W 0, W 1 подать напряжение высокого уровня, то такое напряжение будет на всех выходах дешифратора. Поэтому входы дешифратора-микросхемы W 0 и W 1 называют разрешающими или, еще чаще, стробирующими.

Алгебра Дж. Буля в ЛЭ ЭВМ

Мы представили основные логические элемента компьютера, а основу (базис) всех ЛЭ составляют элементы И, ИЛИ, НЕ. Система команд для любого процессора и большинства ВС включает операции над числами с плавающей запятой: • – сложение чисел (А + Х); • – вычитание чисел (А – Х); • – обратное вычитание чисел (Х – А); • – вычитание модулей чисел (А М Х); • – изменение знака числа (АV X); • – умножение чисел (А * Х); • – деление чисел (А/Х); • – сложение порядков чисел (Е + Х); • – вычитание порядков чисел (Е – Х); • – корректировка вычислений порядка сложением (Е + N); • – корректировка вычислений порядка вычитанием (Е – N).

ЛЭ И ЛФ – БАЗИС любой цифровой ВТ

Литература к изучению курса «Основы математической обработки информации» • Новиков А. М. , Новиков Д. А. Методология [сайт]. URL: http: // metodologya. • Бубнов В. А. , Скрыпник Н. Н. , Яковлева О. В. Информатика. Программа для студентов факультета технология и предпринимательства. – М. : МГПУ, 2003. – 120 с. • Информационные технологии в предметной области. Вып. I. Ноябрь 2002 / Отв. ред. проф. Бубнов В. А. – М. : МГПУ, 2002. – 192 с. (серия «Мастер-класс МГПУ» ). • Полтавский А. В. Программные средства вычислительных систем. Часть I. ЭВМ первых поколений. Учебное пособие. – М. : МГПУ, 2014 – 87 с. • Полтавский А. В. Программные средства вычислительных систем. Часть I I. ЭВМ третьего и четвертого поколений. Учебное пособие. – М. : МГПУ, 2014 – 96 с. • Бубнов В. А. , Яковлева О. В. Математика и информатика. Программа, методические указания и компьютерный практикум. – М. : МГПУ, 2007. • Гришин М. П. Математика и информатика. – М. : МГПУ, 2005. • Национальный открытый университет «ИНТУИТ» [электр. ресурс]. URL: www. intuit. ru / Курс «Введение в математику» . • К. Поляков «Преподавание, наука и жизнь» . Сайт. [электр. ресурс]. URL: Krolyakov. narod. ru / school / flash. html.

Л-7-8 Логические элементы и история ЭВМ.ppt

- Количество слайдов: 24