5ebb202104deb09890ae8f878b0a8f76.ppt

- Количество слайдов: 26

Deep UV-Blocking Particle Filter Using High Aspect Ratio Si Nanogratings with Smooth Sidewalls Pran Mukherjee, Thomas H. Zurbuchen, L. Jay Guo, and Fred A. Herrero Solid-State Electronics Lab University of Michigan

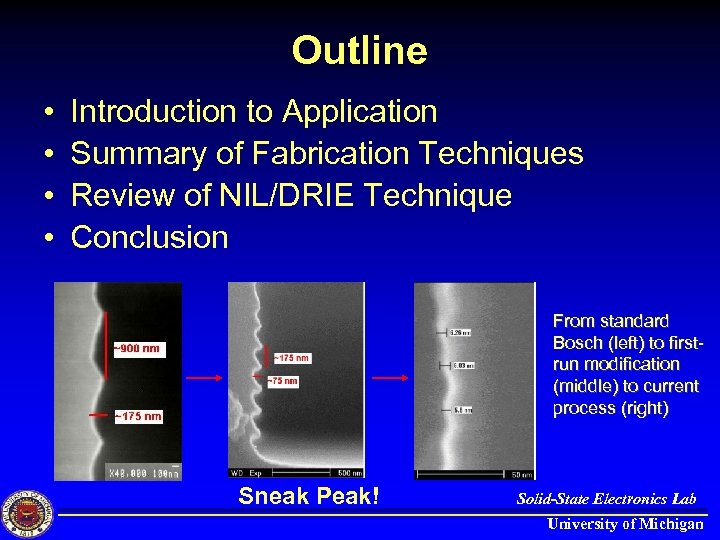

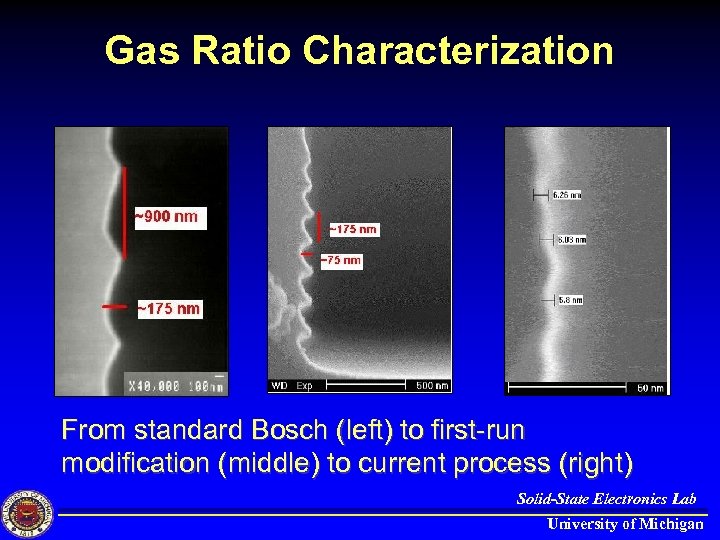

Outline • • Introduction to Application Summary of Fabrication Techniques Review of NIL/DRIE Technique Conclusion From standard Bosch (left) to firstrun modification (middle) to current process (right) Sneak Peak! Solid-State Electronics Lab University of Michigan

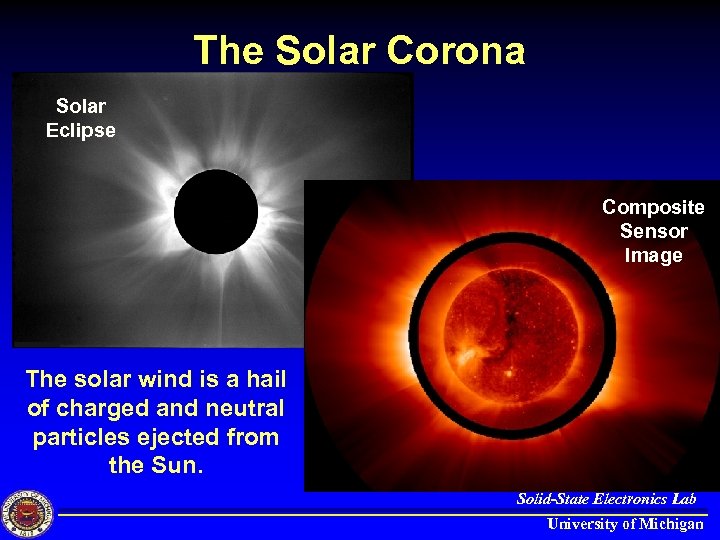

The Solar Corona Solar Eclipse Composite Sensor Image The solar wind is a hail of charged and neutral particles ejected from the Sun. Solid-State Electronics Lab University of Michigan

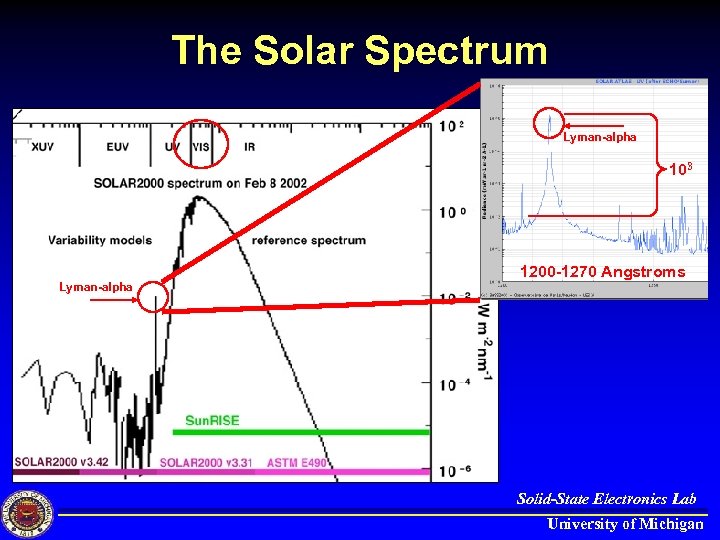

The Solar Spectrum Lyman-alpha 103 Lyman-alpha 1200 -1270 Angstroms Solid-State Electronics Lab University of Michigan

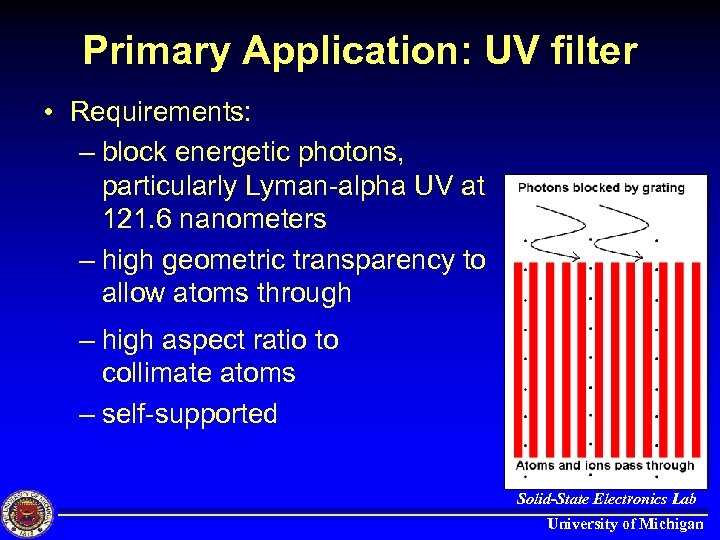

Primary Application: UV filter • Requirements: – block energetic photons, particularly Lyman-alpha UV at 121. 6 nanometers – high geometric transparency to allow atoms through – high aspect ratio to collimate atoms – self-supported Solid-State Electronics Lab University of Michigan

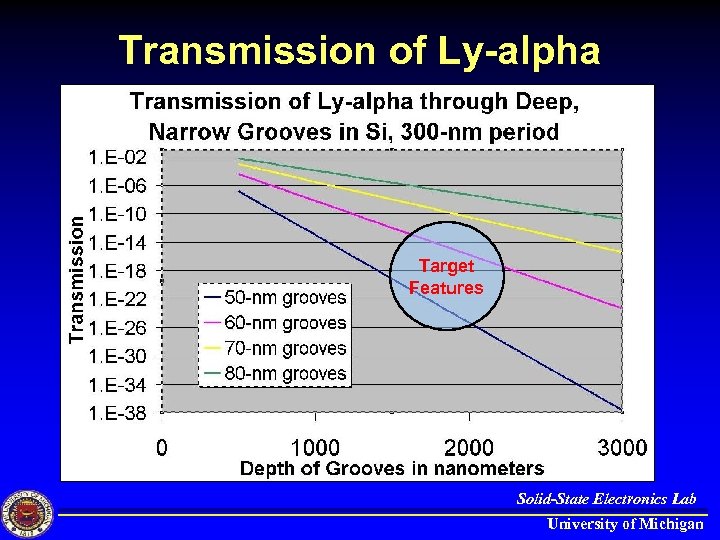

Transmission of Ly-alpha Target Features Solid-State Electronics Lab University of Michigan

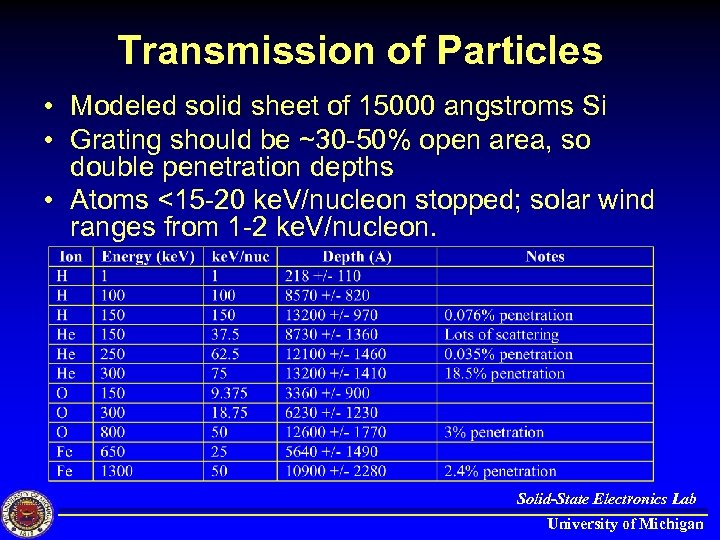

Transmission of Particles • Modeled solid sheet of 15000 angstroms Si • Grating should be ~30 -50% open area, so double penetration depths • Atoms <15 -20 ke. V/nucleon stopped; solar wind ranges from 1 -2 ke. V/nucleon. Solid-State Electronics Lab University of Michigan

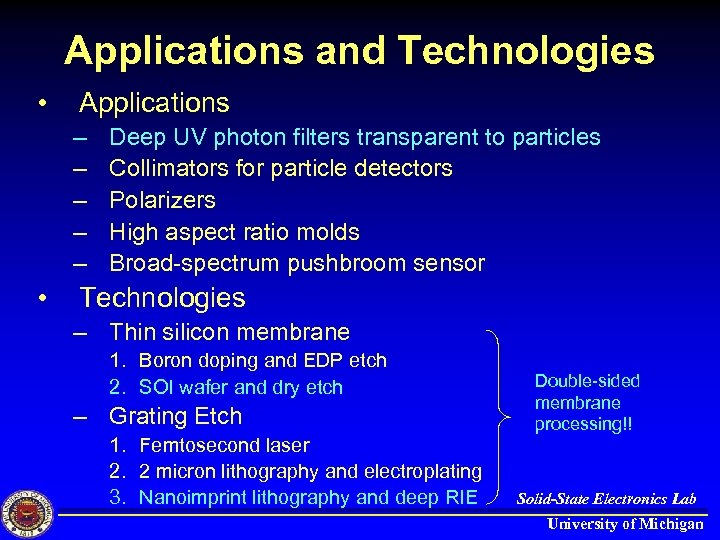

Applications and Technologies • Applications – – – • Deep UV photon filters transparent to particles Collimators for particle detectors Polarizers High aspect ratio molds Broad-spectrum pushbroom sensor Technologies – Thin silicon membrane 1. Boron doping and EDP etch 2. SOI wafer and dry etch – Grating Etch 1. Femtosecond laser 2. 2 micron lithography and electroplating 3. Nanoimprint lithography and deep RIE Double-sided membrane processing!! Solid-State Electronics Lab University of Michigan

Fabrication Techniques • Three techniques attempted – Femtosecond laser etch – Optical lithography – Nanoimprint lithography with DRIE • Constraints – Grating etch time – Grating line width – Aspect ratio – Sidewall straightness Solid-State Electronics Lab University of Michigan

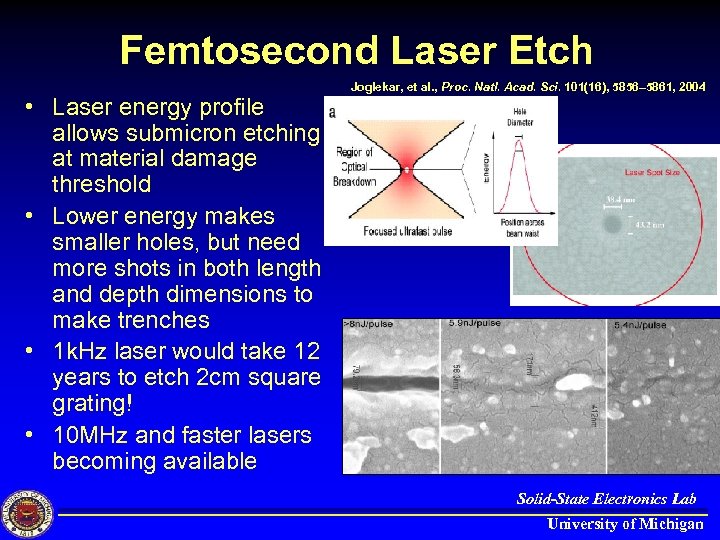

Femtosecond Laser Etch • Laser energy profile allows submicron etching at material damage threshold • Lower energy makes smaller holes, but need more shots in both length and depth dimensions to make trenches • 1 k. Hz laser would take 12 years to etch 2 cm square grating! • 10 MHz and faster lasers becoming available Joglekar, et al. , Proc. Natl. Acad. Sci. 101(16), 5856– 5861, 2004 Solid-State Electronics Lab University of Michigan

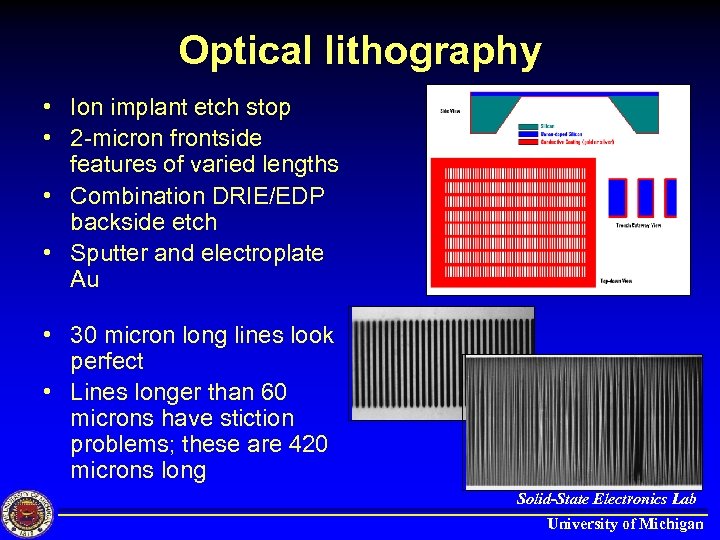

Optical lithography • Ion implant etch stop • 2 -micron frontside features of varied lengths • Combination DRIE/EDP backside etch • Sputter and electroplate Au • 30 micron long lines look perfect • Lines longer than 60 microns have stiction problems; these are 420 microns long Solid-State Electronics Lab University of Michigan

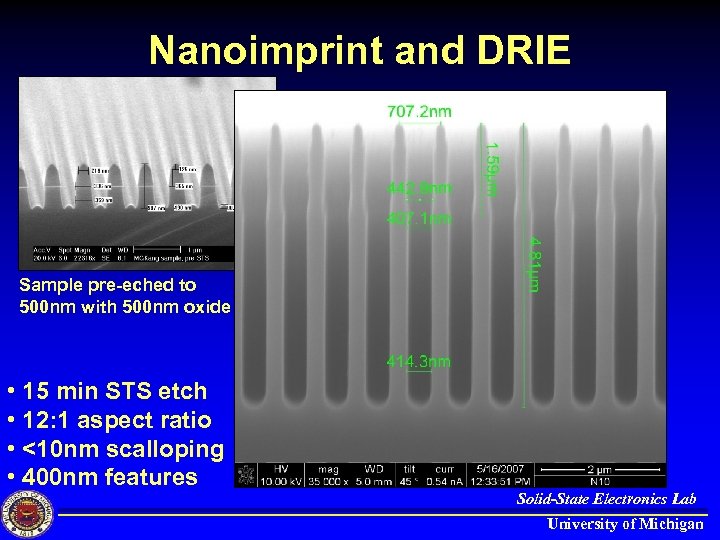

Nanoimprint and DRIE Sample pre-eched to 500 nm with 500 nm oxide • 15 min STS etch • 12: 1 aspect ratio • <10 nm scalloping • 400 nm features Solid-State Electronics Lab University of Michigan

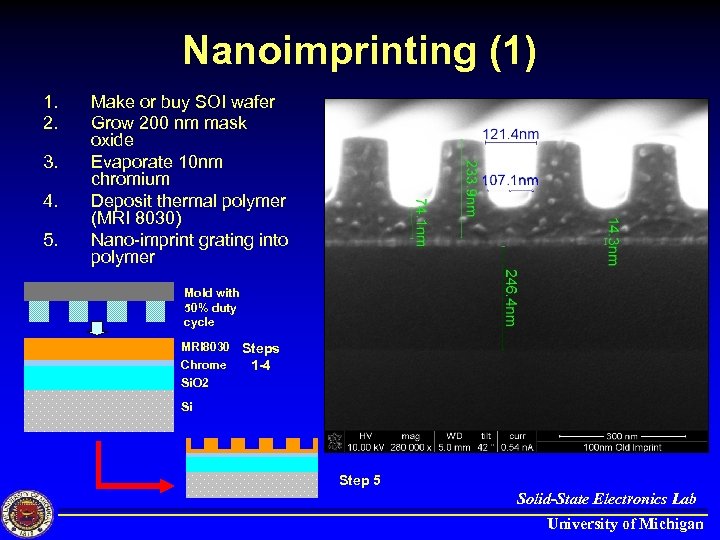

Nanoimprinting (1) 1. 2. 3. 4. 5. Make or buy SOI wafer Grow 200 nm mask oxide Evaporate 10 nm chromium Deposit thermal polymer (MRI 8030) Nano-imprint grating into polymer Mold with 50% duty cycle MRI 8030 Chrome Si. O 2 Steps 1 -4 Si Step 5 Solid-State Electronics Lab University of Michigan

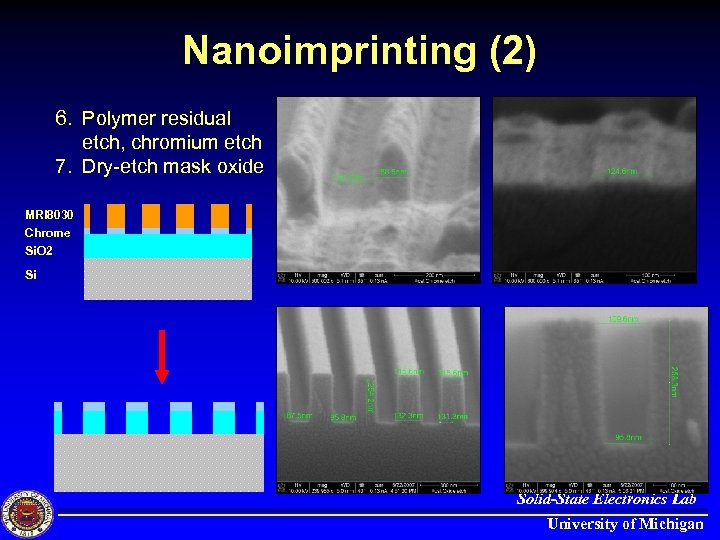

Nanoimprinting (2) 6. Polymer residual etch, chromium etch 7. Dry-etch mask oxide MRI 8030 Chrome Si. O 2 Si Solid-State Electronics Lab University of Michigan

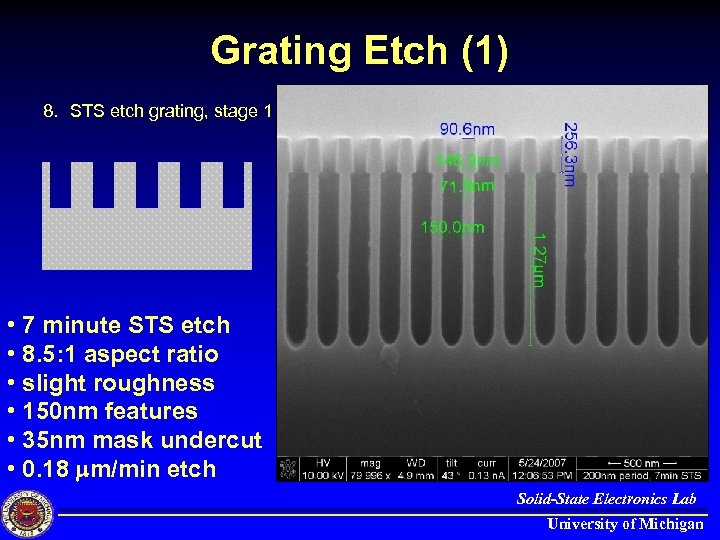

Grating Etch (1) 8. STS etch grating, stage 1 • 7 minute STS etch • 8. 5: 1 aspect ratio • slight roughness • 150 nm features • 35 nm mask undercut • 0. 18 m/min etch Solid-State Electronics Lab University of Michigan

Grating Etch (2) 9. Dry oxidize sample to narrow grating lines and create secondstage etch mask 10. STS etch to oxide layer etch-stop Concerns 1. Controllability of oxidation must be within 10 nm 2. Oxide stress 3. Aspect ratio of mask slowing or stopping second-stage etch 4. Stopping on buried oxide without widening lines Solid-State Electronics Lab University of Michigan

Gas Ratio Characterization From standard Bosch (left) to first-run modification (middle) to current process (right) Solid-State Electronics Lab University of Michigan

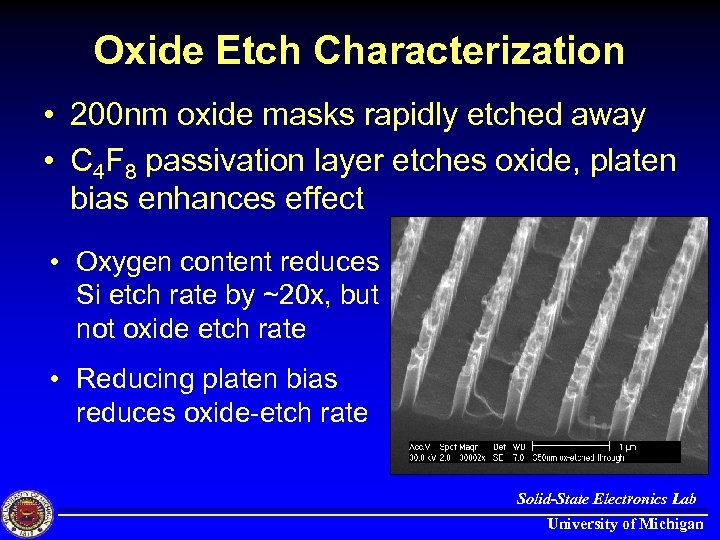

Oxide Etch Characterization • 200 nm oxide masks rapidly etched away • C 4 F 8 passivation layer etches oxide, platen bias enhances effect • Oxygen content reduces Si etch rate by ~20 x, but not oxide etch rate • Reducing platen bias reduces oxide-etch rate Solid-State Electronics Lab University of Michigan

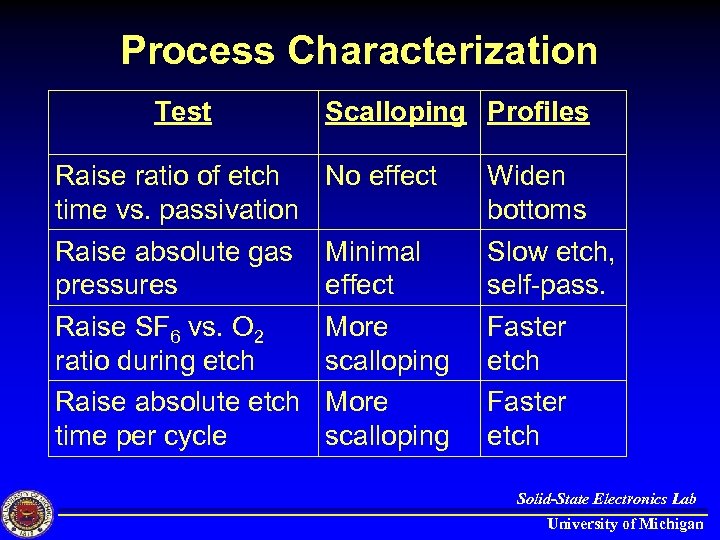

Process Characterization Test Raise ratio of etch time vs. passivation Raise absolute gas pressures Raise SF 6 vs. O 2 ratio during etch Raise absolute etch time per cycle Scalloping Profiles No effect Minimal effect More scalloping Widen bottoms Slow etch, self-pass. Faster etch Solid-State Electronics Lab University of Michigan

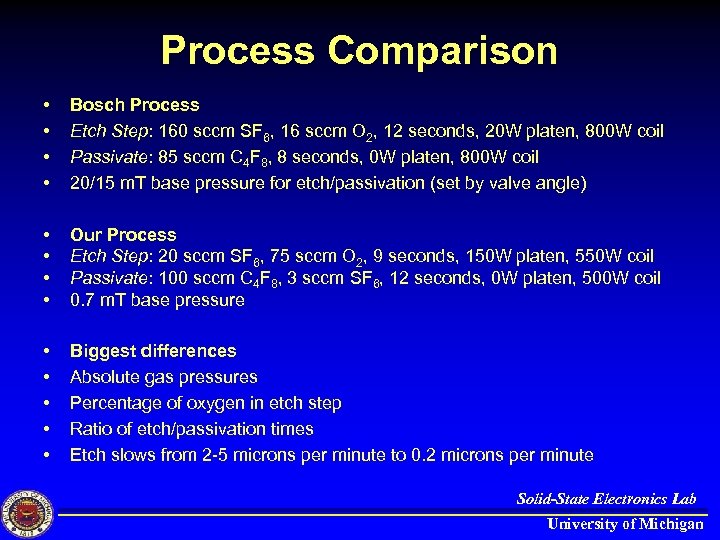

Process Comparison • • Bosch Process Etch Step: 160 sccm SF 6, 16 sccm O 2, 12 seconds, 20 W platen, 800 W coil Passivate: 85 sccm C 4 F 8, 8 seconds, 0 W platen, 800 W coil 20/15 m. T base pressure for etch/passivation (set by valve angle) • • Our Process Etch Step: 20 sccm SF 6, 75 sccm O 2, 9 seconds, 150 W platen, 550 W coil Passivate: 100 sccm C 4 F 8, 3 sccm SF 6, 12 seconds, 0 W platen, 500 W coil 0. 7 m. T base pressure • • • Biggest differences Absolute gas pressures Percentage of oxygen in etch step Ratio of etch/passivation times Etch slows from 2 -5 microns per minute to 0. 2 microns per minute Solid-State Electronics Lab University of Michigan

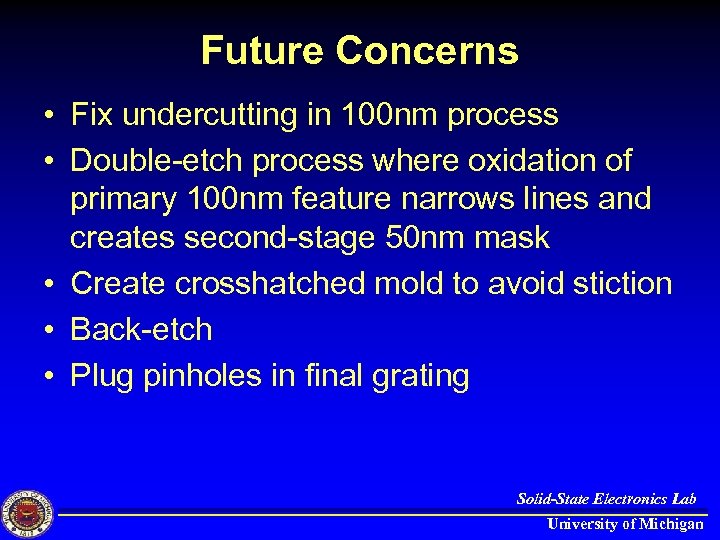

Future Concerns • Fix undercutting in 100 nm process • Double-etch process where oxidation of primary 100 nm feature narrows lines and creates second-stage 50 nm mask • Create crosshatched mold to avoid stiction • Back-etch • Plug pinholes in final grating Solid-State Electronics Lab University of Michigan

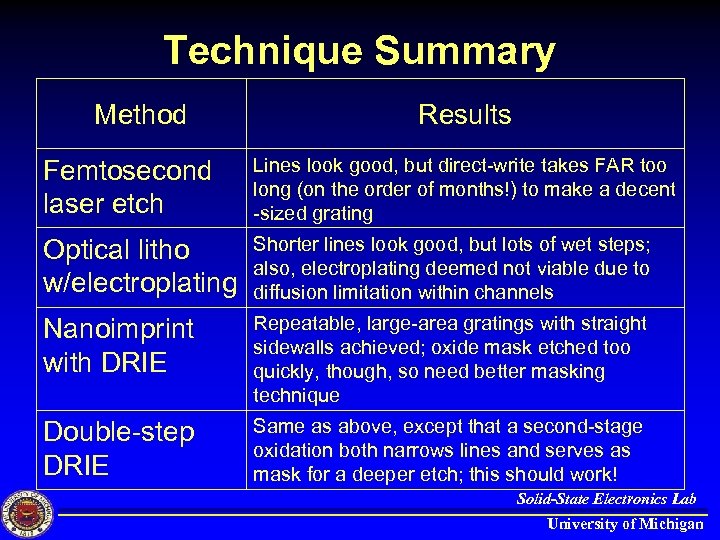

Technique Summary Method Results Femtosecond laser etch Lines look good, but direct-write takes FAR too long (on the order of months!) to make a decent -sized grating Optical litho w/electroplating Shorter lines look good, but lots of wet steps; also, electroplating deemed not viable due to diffusion limitation within channels Nanoimprint with DRIE Repeatable, large-area gratings with straight sidewalls achieved; oxide mask etched too quickly, though, so need better masking technique Double-step DRIE Same as above, except that a second-stage oxidation both narrows lines and serves as mask for a deeper etch; this should work! Solid-State Electronics Lab University of Michigan

Thank You! Any questions? Solid-State Electronics Lab University of Michigan

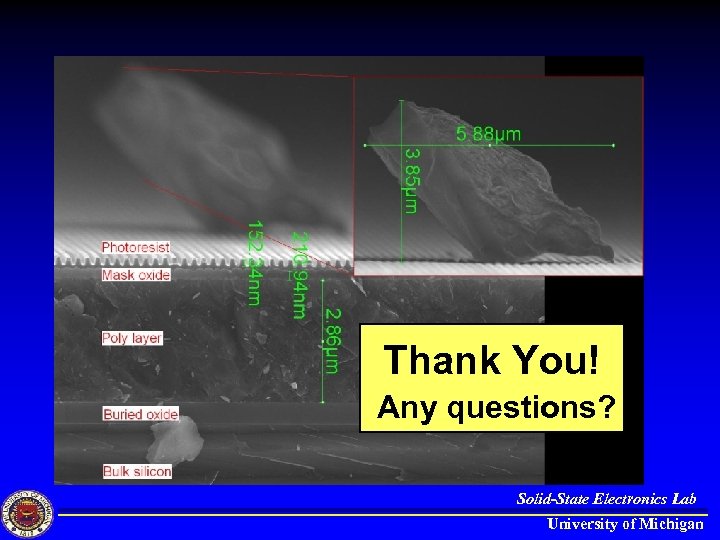

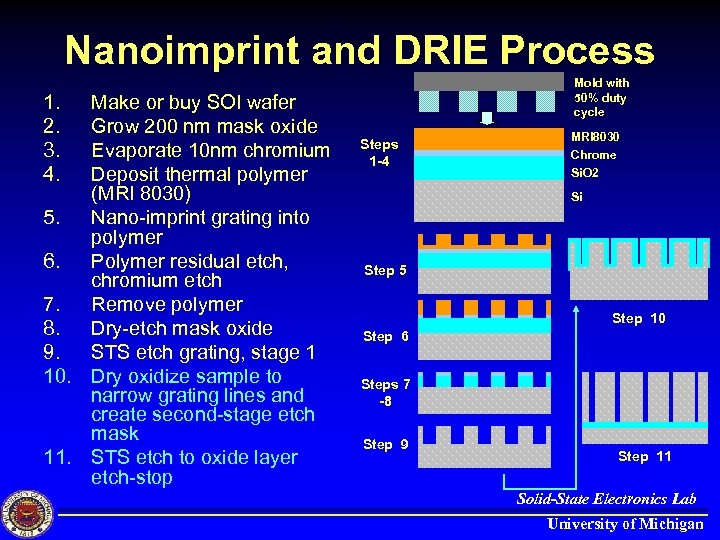

Nanoimprint and DRIE Process 1. 2. 3. 4. Make or buy SOI wafer Grow 200 nm mask oxide Evaporate 10 nm chromium Deposit thermal polymer (MRI 8030) 5. Nano-imprint grating into polymer 6. Polymer residual etch, chromium etch 7. Remove polymer 8. Dry-etch mask oxide 9. STS etch grating, stage 1 10. Dry oxidize sample to narrow grating lines and create second-stage etch mask 11. STS etch to oxide layer etch-stop Mold with 50% duty cycle Steps 1 -4 MRI 8030 Chrome Si. O 2 Si Step 5 Step 10 Step 6 Steps 7 -8 Step 9 Step 11 Solid-State Electronics Lab University of Michigan

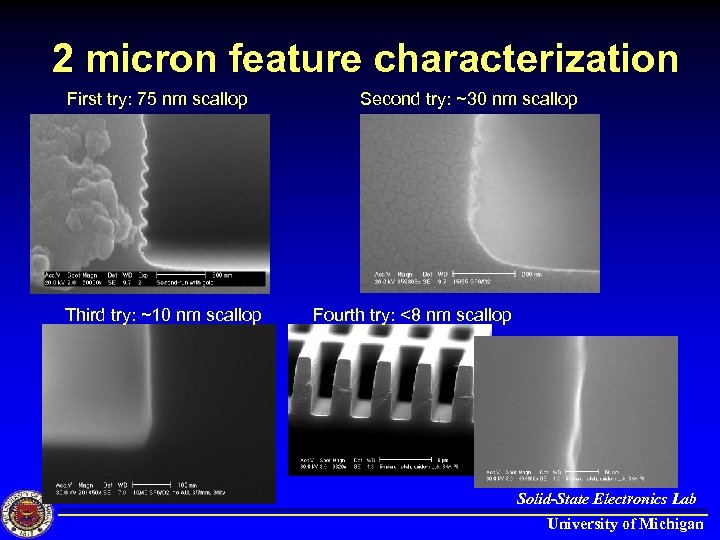

2 micron feature characterization First try: 75 nm scallop Third try: ~10 nm scallop Second try: ~30 nm scallop Fourth try: <8 nm scallop Solid-State Electronics Lab University of Michigan

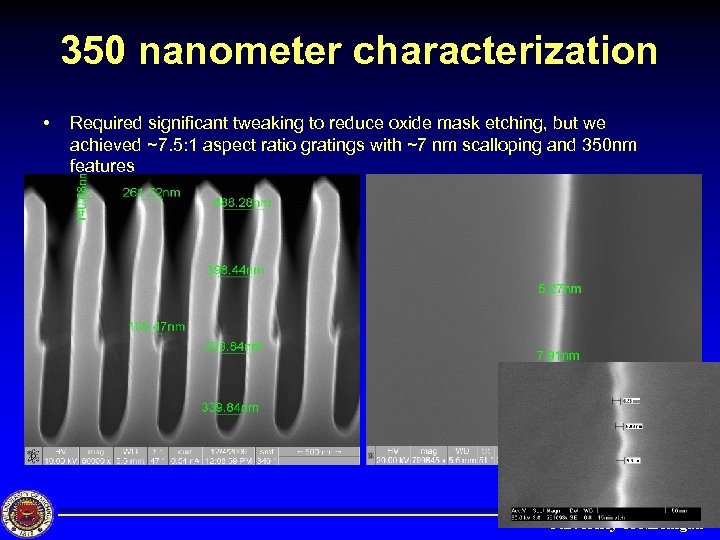

350 nanometer characterization • Required significant tweaking to reduce oxide mask etching, but we achieved ~7. 5: 1 aspect ratio gratings with ~7 nm scalloping and 350 nm features Solid-State Electronics Lab University of Michigan

5ebb202104deb09890ae8f878b0a8f76.ppt