6de87b89eb4c79156c2625f731ff2c40.ppt

- Количество слайдов: 24

Data Manipulation, Communication and Architecture Fall 2012

Data Manipulation, Communication and Architecture Fall 2012

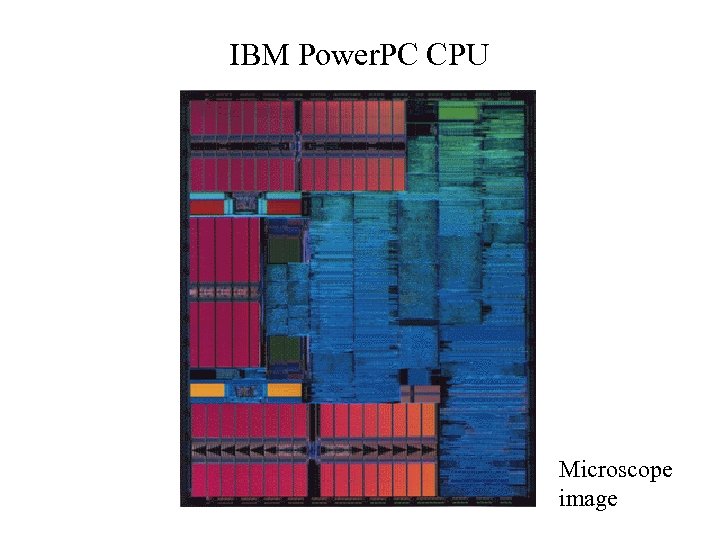

IBM Power. PC CPU Microscope image

IBM Power. PC CPU Microscope image

IBM Power. PC CPU

IBM Power. PC CPU

Architecture and CPU • The essential parts of a computer can be divided up into several parts: – The circuitry that performs operations (addition, subtraction, logic, …) on data is called the central processing unit, or CPU. • The CPU is divided up into two parts: the Arithmetic/Logic unit and the Control unit. – The primary place where data is stored is located in another area we know as main memory. • Main memory is connected to the CPU via a bus, which is used to transfer bit sequences. The bus is simply a collection of wires.

Architecture and CPU • The essential parts of a computer can be divided up into several parts: – The circuitry that performs operations (addition, subtraction, logic, …) on data is called the central processing unit, or CPU. • The CPU is divided up into two parts: the Arithmetic/Logic unit and the Control unit. – The primary place where data is stored is located in another area we know as main memory. • Main memory is connected to the CPU via a bus, which is used to transfer bit sequences. The bus is simply a collection of wires.

CPU con’t • In between the arithmetic/logic unit and the Control unit are registers. – General-purpose registers – Special-purpose registers • General-purpose registers serve as temporary holding places for data (binary sequences) being manipulated by the CPU. They hold the inputs to the A/L unit and provide storage for the results of the operations. • The Control unit coordinates all these activities. For example: – It transfers the data from main memory into the general purpose registers, informs the A/L unit which registers hold the data, activates the appropriate circuitry within the A/L unit to perform an operation, and then tells the A/L unit which register to put the result in.

CPU con’t • In between the arithmetic/logic unit and the Control unit are registers. – General-purpose registers – Special-purpose registers • General-purpose registers serve as temporary holding places for data (binary sequences) being manipulated by the CPU. They hold the inputs to the A/L unit and provide storage for the results of the operations. • The Control unit coordinates all these activities. For example: – It transfers the data from main memory into the general purpose registers, informs the A/L unit which registers hold the data, activates the appropriate circuitry within the A/L unit to perform an operation, and then tells the A/L unit which register to put the result in.

Machine Instructions • Each CPU has a limited number of instructions it can execute. These are called machine instructions. These can be classified into 3 groups: – Data transfer group – Arithmetic/logic group – Control group

Machine Instructions • Each CPU has a limited number of instructions it can execute. These are called machine instructions. These can be classified into 3 groups: – Data transfer group – Arithmetic/logic group – Control group

Data transfer • Instructions to move (copy) data from one location to another. – Fill a register with the contents of a memory cell -- LOAD – Copy the contents in a register to a memory cell -- STORE – I/O instructions (to communicate with other parts of the computer)

Data transfer • Instructions to move (copy) data from one location to another. – Fill a register with the contents of a memory cell -- LOAD – Copy the contents in a register to a memory cell -- STORE – I/O instructions (to communicate with other parts of the computer)

Arithmetic/Logic • Instructions to perform operations within the A/L unit. – – – ADD AND OR Shift bits within a register -- SHIFT Shift bits within a register but keep ones that fall off -- ROTATE

Arithmetic/Logic • Instructions to perform operations within the A/L unit. – – – ADD AND OR Shift bits within a register -- SHIFT Shift bits within a register but keep ones that fall off -- ROTATE

Control • Instructions to direct the execution of the program. – Stop doing something -- HALT – Execute a different instruction than the one next in line, conditionally or unconditionally -- JUMP

Control • Instructions to direct the execution of the program. – Stop doing something -- HALT – Execute a different instruction than the one next in line, conditionally or unconditionally -- JUMP

The Stored-Program Concept • Early machines -- Data was one thing and programs were another. (Not very flexible) • Today -- Data and programs are both represented in binary. The program is stored in main memory just as the data is. This is called the. . . Stored-program concept

The Stored-Program Concept • Early machines -- Data was one thing and programs were another. (Not very flexible) • Today -- Data and programs are both represented in binary. The program is stored in main memory just as the data is. This is called the. . . Stored-program concept

Stored-Program Concept • Benefits: – Very flexible. We can run many different programs on the same machine without any physical modifications. – Machines can be mass produced and then people can decide later what they will do. • Requirements: – We must have a way to write instructions in binary (just as our data is) and then have a way for the computer to interpret and execute them.

Stored-Program Concept • Benefits: – Very flexible. We can run many different programs on the same machine without any physical modifications. – Machines can be mass produced and then people can decide later what they will do. • Requirements: – We must have a way to write instructions in binary (just as our data is) and then have a way for the computer to interpret and execute them.

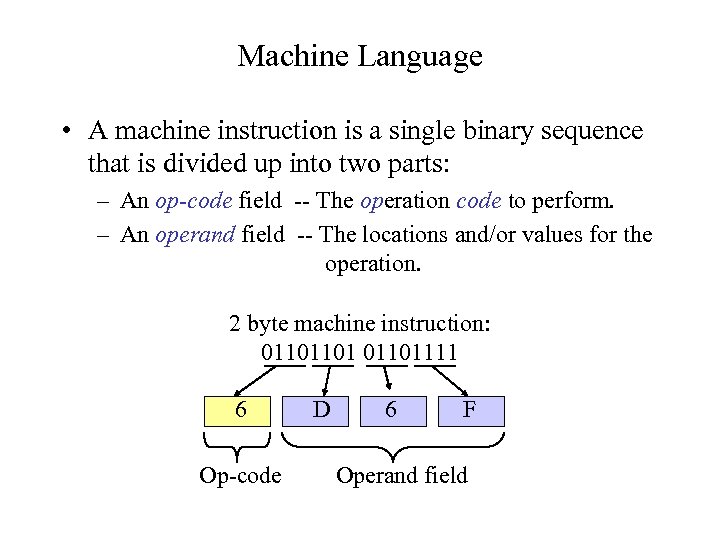

Machine Language • A machine instruction is a single binary sequence that is divided up into two parts: – An op-code field -- The operation code to perform. – An operand field -- The locations and/or values for the operation. 2 byte machine instruction: 01101101111 6 Op-code D 6 F Operand field

Machine Language • A machine instruction is a single binary sequence that is divided up into two parts: – An op-code field -- The operation code to perform. – An operand field -- The locations and/or values for the operation. 2 byte machine instruction: 01101101111 6 Op-code D 6 F Operand field

Program Execution • To execute a program we need more organization in the control unit: – We get this organization from two special-purpose registers called the program counter and the instruction register.

Program Execution • To execute a program we need more organization in the control unit: – We get this organization from two special-purpose registers called the program counter and the instruction register.

• The program counter holds the address (in main memory) of the next instruction to be executed. This enables the machine to keep track of where it is in the program. (The program is usually stored in main memory with the instructions written in consecutive order. ) • The instruction register holds the complete instruction (op-code + operand) being executed.

• The program counter holds the address (in main memory) of the next instruction to be executed. This enables the machine to keep track of where it is in the program. (The program is usually stored in main memory with the instructions written in consecutive order. ) • The instruction register holds the complete instruction (op-code + operand) being executed.

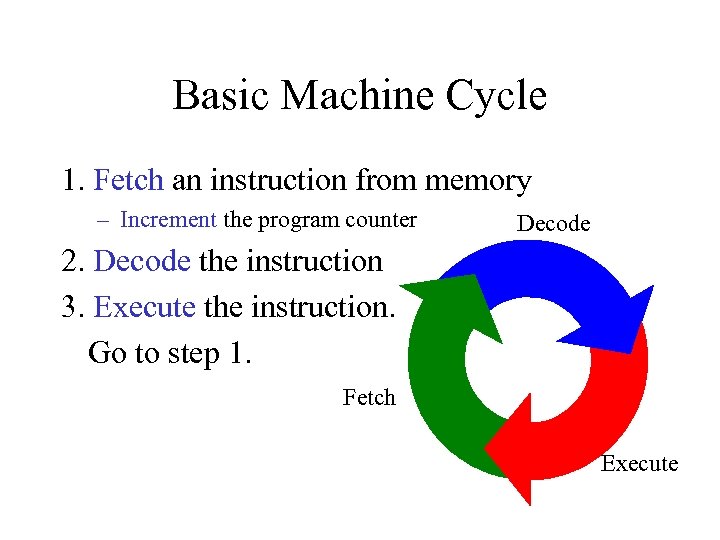

Basic Machine Cycle 1. Fetch an instruction from memory – Increment the program counter Decode 2. Decode the instruction 3. Execute the instruction. Go to step 1. Fetch Execute

Basic Machine Cycle 1. Fetch an instruction from memory – Increment the program counter Decode 2. Decode the instruction 3. Execute the instruction. Go to step 1. Fetch Execute

Machine Cycle and the Clock • The machine cycle is run continuously through the use of a clock. The clock is a regular signal (pulse train of 0 followed by a 1 followed by a 0, etc. , or more correctly a voltage pulse train of off voltage, on voltage, . . . ) driven by an oscillator set at a particular frequency. This is the “MHz” of the machine (500 MHz == 500 million cycles/second, GHz = billion of cycles/second). This is the number of machine cycles performed per second. • When comparing the capabilities of different computers we cannot simply compare clock frequencies. . .

Machine Cycle and the Clock • The machine cycle is run continuously through the use of a clock. The clock is a regular signal (pulse train of 0 followed by a 1 followed by a 0, etc. , or more correctly a voltage pulse train of off voltage, on voltage, . . . ) driven by an oscillator set at a particular frequency. This is the “MHz” of the machine (500 MHz == 500 million cycles/second, GHz = billion of cycles/second). This is the number of machine cycles performed per second. • When comparing the capabilities of different computers we cannot simply compare clock frequencies. . .

Sect. 2. 5: Communicating with Other Devices • The core of a computer is made up of the CPU and Main Memory. How does this core communicate with all the other devices: (CD, Modem, Monitor, Hard Drive, . . . ? – With an intermediary device called a controller. – See Figure 2. 8

Sect. 2. 5: Communicating with Other Devices • The core of a computer is made up of the CPU and Main Memory. How does this core communicate with all the other devices: (CD, Modem, Monitor, Hard Drive, . . . ? – With an intermediary device called a controller. – See Figure 2. 8

Controller • 1 controller for each device. • A little computer all its own that runs a program to interface with the CPU and the particular device being run. • Listens for signals from the CPU and acts accordingly by “controlling” the device to perform whatever function desired by the CPU. • If it can directly access (read/write) the Main Memory then it has Direct Memory Access or DMA.

Controller • 1 controller for each device. • A little computer all its own that runs a program to interface with the CPU and the particular device being run. • Listens for signals from the CPU and acts accordingly by “controlling” the device to perform whatever function desired by the CPU. • If it can directly access (read/write) the Main Memory then it has Direct Memory Access or DMA.

Controller, con’t • Many controllers, all with DMA, can have a disabling effect on the performance of the computer. This is known as the von Neumann bottleneck. – This is where the CPU and all the controllers are competing for bus access. • How, exactly, does the CPU access a device (through a controller)? – Memory-mapped I/O communication system. • The CPU executes instructions for the device as if it were in main memory. It executes a LOAD, or STORE, … But the address does not correspond to an address in main memory. The main memory is designed to ignore this instruction, while the particular controller is designed to respond to it. See Fig. 2. 9 The address is called a port.

Controller, con’t • Many controllers, all with DMA, can have a disabling effect on the performance of the computer. This is known as the von Neumann bottleneck. – This is where the CPU and all the controllers are competing for bus access. • How, exactly, does the CPU access a device (through a controller)? – Memory-mapped I/O communication system. • The CPU executes instructions for the device as if it were in main memory. It executes a LOAD, or STORE, … But the address does not correspond to an address in main memory. The main memory is designed to ignore this instruction, while the particular controller is designed to respond to it. See Fig. 2. 9 The address is called a port.

Data transfer between components • Rarely a one-way conversation. • Components “talk” to each other. – e. g. The CPU sends commands and data to the printer. The printer and CPU “talk” back and forth through the controller. CPU -- fast, Printer -- slow. Communication: CPU, “Printer, ready? ”, Printer, “Ready”, CPU, “Sending data”, Printer, “OK”, Printer, “Buffer full, quit sending data”, CPU, “OK”, … – Typical command: Status Word. • The status word is a binary sequence where each bit corresponds to the condition of the device. E. g. bits may correspond to: “Ready”, or “Not ready”, “paper tray full” or “paper tray empty”, …

Data transfer between components • Rarely a one-way conversation. • Components “talk” to each other. – e. g. The CPU sends commands and data to the printer. The printer and CPU “talk” back and forth through the controller. CPU -- fast, Printer -- slow. Communication: CPU, “Printer, ready? ”, Printer, “Ready”, CPU, “Sending data”, Printer, “OK”, Printer, “Buffer full, quit sending data”, CPU, “OK”, … – Typical command: Status Word. • The status word is a binary sequence where each bit corresponds to the condition of the device. E. g. bits may correspond to: “Ready”, or “Not ready”, “paper tray full” or “paper tray empty”, …

Data Communication Rates • Data transfer rates are typically measured in bits per second, or bps. (i. e. bits/second) • When rates are high we will use: Kbps, Mbps, or Gbps: – Kbps = kilo bits/second = 1000 bps (not 1024 bps!) – Mbps = mega bits/second = 1 x 106 bps – Gbps = giga bits/second = 1 x 109 bps

Data Communication Rates • Data transfer rates are typically measured in bits per second, or bps. (i. e. bits/second) • When rates are high we will use: Kbps, Mbps, or Gbps: – Kbps = kilo bits/second = 1000 bps (not 1024 bps!) – Mbps = mega bits/second = 1 x 106 bps – Gbps = giga bits/second = 1 x 109 bps

• Two basic types of communication schemes: – Parallel communication • All bits are sent at the same time on different wires (one wire per bit) • Fast, but requires relatively complex electronics • Internal bus, standard components – Serial communication • • • Transfer of one bit at a time over a single wire. Slow, but requires only simple electronics. Communication between computers, modems, some printers. Phone lines are inherently serial. Example: USB peripherals -- Universal Serial Bus

• Two basic types of communication schemes: – Parallel communication • All bits are sent at the same time on different wires (one wire per bit) • Fast, but requires relatively complex electronics • Internal bus, standard components – Serial communication • • • Transfer of one bit at a time over a single wire. Slow, but requires only simple electronics. Communication between computers, modems, some printers. Phone lines are inherently serial. Example: USB peripherals -- Universal Serial Bus

Other Architectures • Two common architectures for CPU’s: – Complex Instruction Set Computer (CISC) • Intel Pentium/Celeron series (20 year old architecture!) – Reduced Instruction Set Computer (RISC) • IBM, Motorola Power. PC, DEC/Compaq Alpha, Silicon Graphics MIPS chips, Sun Microsystems Ultra. Sparc – Other: Intel’s Merced CPU goes beyond both these with a completely new architecture (EPIC)

Other Architectures • Two common architectures for CPU’s: – Complex Instruction Set Computer (CISC) • Intel Pentium/Celeron series (20 year old architecture!) – Reduced Instruction Set Computer (RISC) • IBM, Motorola Power. PC, DEC/Compaq Alpha, Silicon Graphics MIPS chips, Sun Microsystems Ultra. Sparc – Other: Intel’s Merced CPU goes beyond both these with a completely new architecture (EPIC)

• Other interesting things … – Pipelining: Pre-fetching an instruction. Fetching more instructions than needed so the next one will be ready faster. (A waste of time if the current instruction is a jump. ) • Most of the time, however, this increases throughput (the total amount of work a machine can accomplish in a given amount of time). – Parallel processing: • “Simulated” parallel processing • True parallel processing (requires more than 1 CPU per machine) New multi core processors and Master- Slave configurations.

• Other interesting things … – Pipelining: Pre-fetching an instruction. Fetching more instructions than needed so the next one will be ready faster. (A waste of time if the current instruction is a jump. ) • Most of the time, however, this increases throughput (the total amount of work a machine can accomplish in a given amount of time). – Parallel processing: • “Simulated” parallel processing • True parallel processing (requires more than 1 CPU per machine) New multi core processors and Master- Slave configurations.