aeda064d7031b319fd23a57c59c303f8.ppt

- Количество слайдов: 5

DAC 2000 Panel Proposals 529, 535 Andrew B. Kahng January 13, 2000

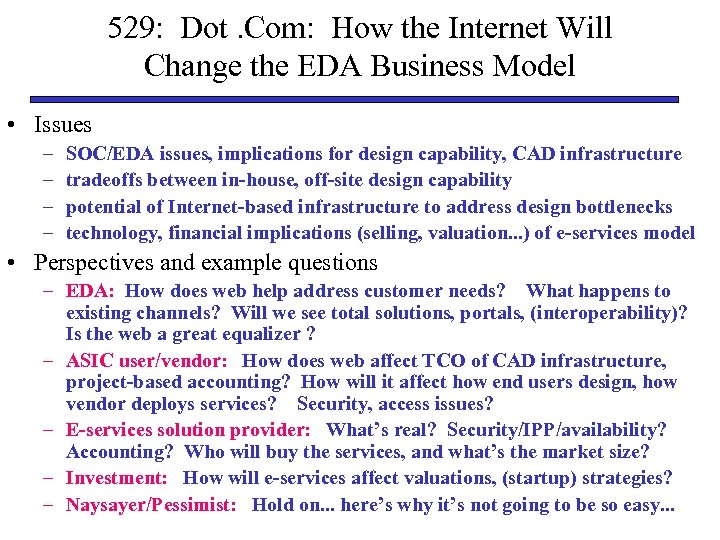

529: Dot. Com: How the Internet Will Change the EDA Business Model • Issues – – SOC/EDA issues, implications for design capability, CAD infrastructure tradeoffs between in-house, off-site design capability potential of Internet-based infrastructure to address design bottlenecks technology, financial implications (selling, valuation. . . ) of e-services model • Perspectives and example questions – EDA: How does web help address customer needs? What happens to existing channels? Will we see total solutions, portals, (interoperability)? Is the web a great equalizer ? – ASIC user/vendor: How does web affect TCO of CAD infrastructure, project-based accounting? How will it affect how end users design, how vendor deploys services? Security, access issues? – E-services solution provider: What’s real? Security/IPP/availability? Accounting? Who will buy the services, and what’s the market size? – Investment: How will e-services affect valuations, (startup) strategies? – Naysayer/Pessimist: Hold on. . . here’s why it’s not going to be so easy. . .

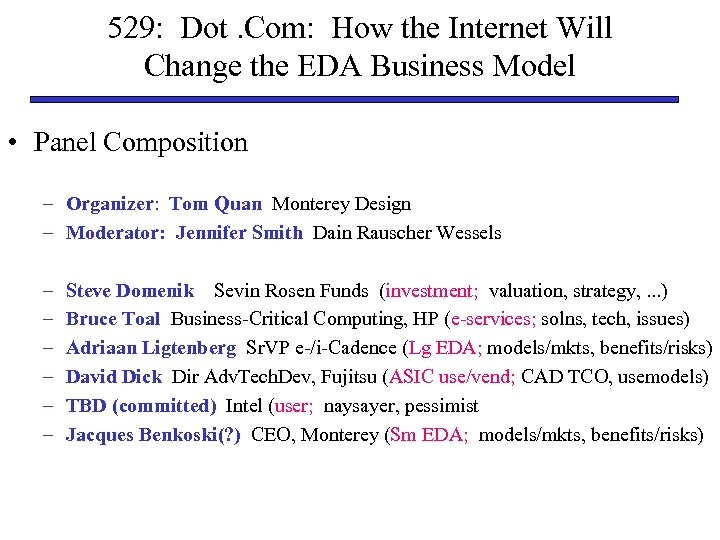

529: Dot. Com: How the Internet Will Change the EDA Business Model • Panel Composition – Organizer: Tom Quan Monterey Design – Moderator: Jennifer Smith Dain Rauscher Wessels – – – Steve Domenik Sevin Rosen Funds (investment; valuation, strategy, . . . ) Bruce Toal Business-Critical Computing, HP (e-services; solns, tech, issues) Adriaan Ligtenberg Sr. VP e-/i-Cadence (Lg EDA; models/mkts, benefits/risks) David Dick Dir Adv. Tech. Dev, Fujitsu (ASIC use/vend; CAD TCO, usemodels) TBD (committed) Intel (user; naysayer, pessimist Jacques Benkoski(? ) CEO, Monterey (Sm EDA; models/mkts, benefits/risks)

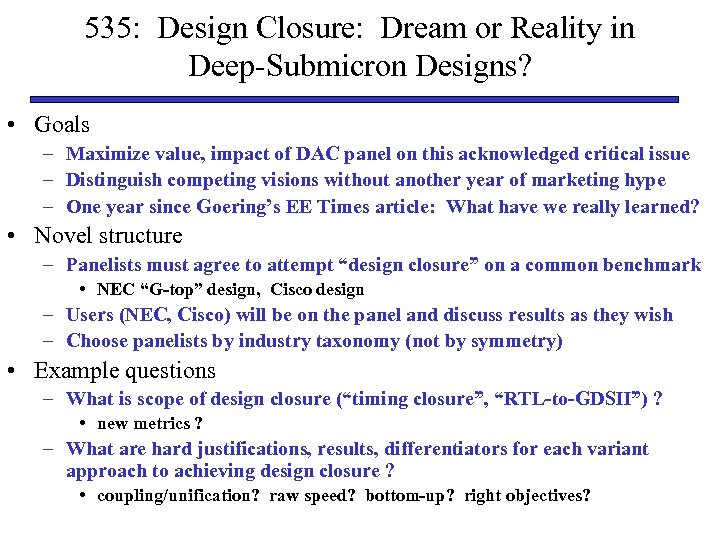

535: Design Closure: Dream or Reality in Deep-Submicron Designs? • Goals – Maximize value, impact of DAC panel on this acknowledged critical issue – Distinguish competing visions without another year of marketing hype – One year since Goering’s EE Times article: What have we really learned? • Novel structure – Panelists must agree to attempt “design closure” on a common benchmark • NEC “G-top” design, Cisco design – Users (NEC, Cisco) will be on the panel and discuss results as they wish – Choose panelists by industry taxonomy (not by symmetry) • Example questions – What is scope of design closure (“timing closure”, “RTL-to-GDSII”) ? • new metrics ? – What are hard justifications, results, differentiators for each variant approach to achieving design closure ? • coupling/unification? raw speed? bottom-up? right objectives?

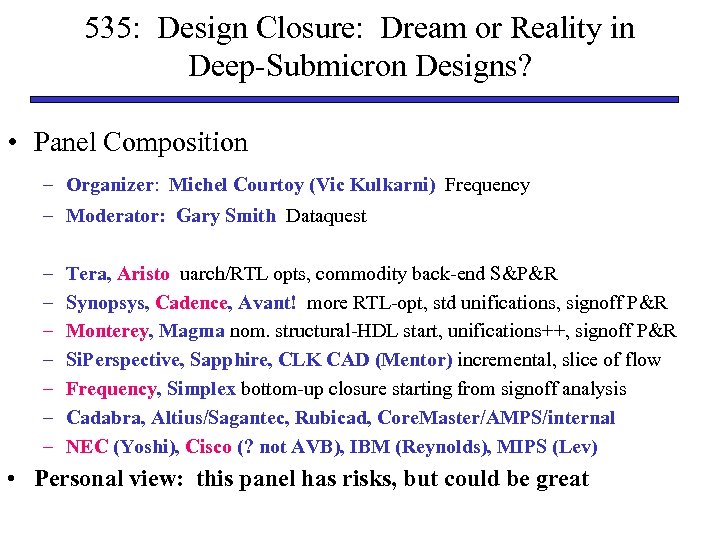

535: Design Closure: Dream or Reality in Deep-Submicron Designs? • Panel Composition – Organizer: Michel Courtoy (Vic Kulkarni) Frequency – Moderator: Gary Smith Dataquest – – – – Tera, Aristo uarch/RTL opts, commodity back-end S&P&R Synopsys, Cadence, Avant! more RTL-opt, std unifications, signoff P&R Monterey, Magma nom. structural-HDL start, unifications++, signoff P&R Si. Perspective, Sapphire, CLK CAD (Mentor) incremental, slice of flow Frequency, Simplex bottom-up closure starting from signoff analysis Cadabra, Altius/Sagantec, Rubicad, Core. Master/AMPS/internal NEC (Yoshi), Cisco (? not AVB), IBM (Reynolds), MIPS (Lev) • Personal view: this panel has risks, but could be great

aeda064d7031b319fd23a57c59c303f8.ppt