c537a6d7b671428b7f458aaea233b843.ppt

- Количество слайдов: 35

CSE 211 Computer Organization and Design Lecture : 3 Tutorial: 1 Practical: 0 Credit: 4 Deepak Kumar (Asst. Professor, LPU) 1

CSE 211 Computer Organization and Design Lecture : 3 Tutorial: 1 Practical: 0 Credit: 4 Deepak Kumar (Asst. Professor, LPU) 1

Basic Computer Organization and Design 2 Overview ØInstruction Codes Ø Computer Registers Ø Computer Instructions Ø Timing and Control Ø Instruction Cycle Ø Memory Reference Instructions Ø Input-Output and Interrupt Ø Complete Computer Description CSE 211

Basic Computer Organization and Design 2 Overview ØInstruction Codes Ø Computer Registers Ø Computer Instructions Ø Timing and Control Ø Instruction Cycle Ø Memory Reference Instructions Ø Input-Output and Interrupt Ø Complete Computer Description CSE 211

Basic Computer Organization and Design 3 Basic Computer Instructions Basic Computer Instruction Format 1. Memory-Reference Instructions 15 I 14 12 11 Opcode 0 Address 2. Register-Reference Instructions 15 12 11 Register operation 0 1 1 1 3. Input-Output Instructions 15 12 11 1 1 CSE 211 (OP-code = 000 ~ 110) (OP-code = 111, I = 0) 0 (OP-code =111, I = 1) 0 I/O operation

Basic Computer Organization and Design 3 Basic Computer Instructions Basic Computer Instruction Format 1. Memory-Reference Instructions 15 I 14 12 11 Opcode 0 Address 2. Register-Reference Instructions 15 12 11 Register operation 0 1 1 1 3. Input-Output Instructions 15 12 11 1 1 CSE 211 (OP-code = 000 ~ 110) (OP-code = 111, I = 0) 0 (OP-code =111, I = 1) 0 I/O operation

Basic Computer Organization and Design 4 Basic Computer Instructions Ø Only 3 bits are used for operation code Ø It may seem computer is restricted to eight different operations Ø however register reference and input output instructions use remaining 12 bit as part of operation code Ø so total number of instruction can exceed 8 ØInfact total no. of instructions chosen for basic computer is 25 CSE 211

Basic Computer Organization and Design 4 Basic Computer Instructions Ø Only 3 bits are used for operation code Ø It may seem computer is restricted to eight different operations Ø however register reference and input output instructions use remaining 12 bit as part of operation code Ø so total number of instruction can exceed 8 ØInfact total no. of instructions chosen for basic computer is 25 CSE 211

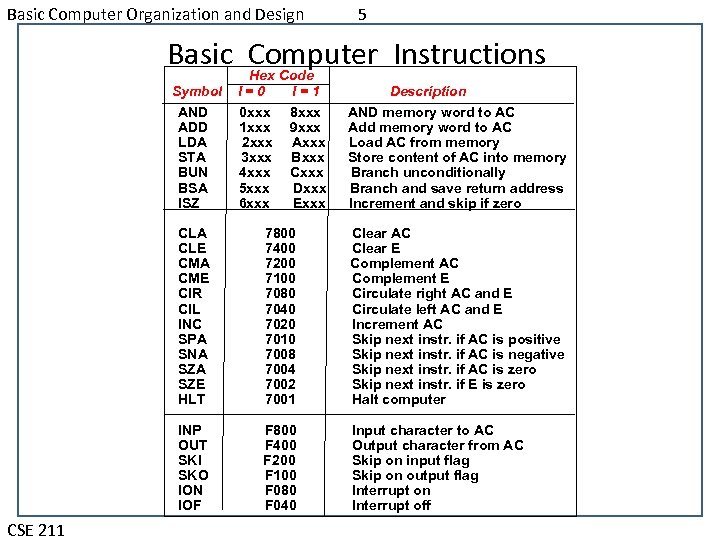

Basic Computer Organization and Design 5 Basic Computer Instructions Symbol AND ADD LDA STA BUN BSA ISZ Description AND memory word to AC Add memory word to AC Load AC from memory Store content of AC into memory Branch unconditionally Branch and save return address Increment and skip if zero CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT 7800 7400 7200 7100 7080 7040 7020 7010 7008 7004 7002 7001 Clear AC Clear E Complement AC Complement E Circulate right AC and E Circulate left AC and E Increment AC Skip next instr. if AC is positive Skip next instr. if AC is negative Skip next instr. if AC is zero Skip next instr. if E is zero Halt computer INP OUT SKI SKO ION IOF CSE 211 Hex Code I=0 I=1 0 xxx 8 xxx 1 xxx 9 xxx 2 xxx Axxx 3 xxx Bxxx 4 xxx Cxxx 5 xxx Dxxx 6 xxx Exxx F 800 F 400 F 200 F 100 F 080 F 040 Input character to AC Output character from AC Skip on input flag Skip on output flag Interrupt on Interrupt off

Basic Computer Organization and Design 5 Basic Computer Instructions Symbol AND ADD LDA STA BUN BSA ISZ Description AND memory word to AC Add memory word to AC Load AC from memory Store content of AC into memory Branch unconditionally Branch and save return address Increment and skip if zero CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT 7800 7400 7200 7100 7080 7040 7020 7010 7008 7004 7002 7001 Clear AC Clear E Complement AC Complement E Circulate right AC and E Circulate left AC and E Increment AC Skip next instr. if AC is positive Skip next instr. if AC is negative Skip next instr. if AC is zero Skip next instr. if E is zero Halt computer INP OUT SKI SKO ION IOF CSE 211 Hex Code I=0 I=1 0 xxx 8 xxx 1 xxx 9 xxx 2 xxx Axxx 3 xxx Bxxx 4 xxx Cxxx 5 xxx Dxxx 6 xxx Exxx F 800 F 400 F 200 F 100 F 080 F 040 Input character to AC Output character from AC Skip on input flag Skip on output flag Interrupt on Interrupt off

Basic Computer Organization and Design 6 Instruction Set Completeness A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable. The set of instructions are said to be complete if computer includes a sufficient number of instruction in each of the following categories : Ø Functional Instructions - Arithmetic, logic, and shift instructions - ADD, CMA, INC, CIR, CIL, AND, CMA, CLA ØTransfer Instructions - Data transfers between the main memory and the processor registers - LDA, STA ØControl Instructions - Program sequencing and control - BUN, BSA, ISZ ØInput/output Instructions - Input and output - INP, OUT CSE 211

Basic Computer Organization and Design 6 Instruction Set Completeness A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable. The set of instructions are said to be complete if computer includes a sufficient number of instruction in each of the following categories : Ø Functional Instructions - Arithmetic, logic, and shift instructions - ADD, CMA, INC, CIR, CIL, AND, CMA, CLA ØTransfer Instructions - Data transfers between the main memory and the processor registers - LDA, STA ØControl Instructions - Program sequencing and control - BUN, BSA, ISZ ØInput/output Instructions - Input and output - INP, OUT CSE 211

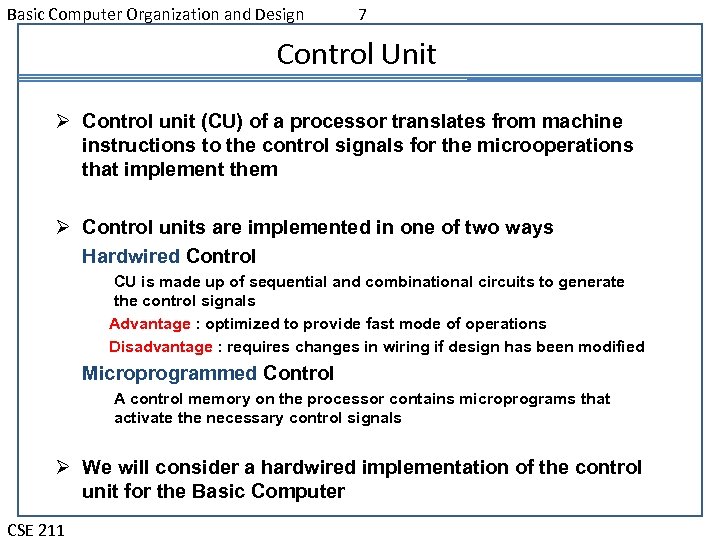

Basic Computer Organization and Design 7 Control Unit Ø Control unit (CU) of a processor translates from machine instructions to the control signals for the microoperations that implement them Ø Control units are implemented in one of two ways Hardwired Control CU is made up of sequential and combinational circuits to generate the control signals Advantage : optimized to provide fast mode of operations Disadvantage : requires changes in wiring if design has been modified Microprogrammed Control A control memory on the processor contains microprograms that activate the necessary control signals Ø We will consider a hardwired implementation of the control unit for the Basic Computer CSE 211

Basic Computer Organization and Design 7 Control Unit Ø Control unit (CU) of a processor translates from machine instructions to the control signals for the microoperations that implement them Ø Control units are implemented in one of two ways Hardwired Control CU is made up of sequential and combinational circuits to generate the control signals Advantage : optimized to provide fast mode of operations Disadvantage : requires changes in wiring if design has been modified Microprogrammed Control A control memory on the processor contains microprograms that activate the necessary control signals Ø We will consider a hardwired implementation of the control unit for the Basic Computer CSE 211

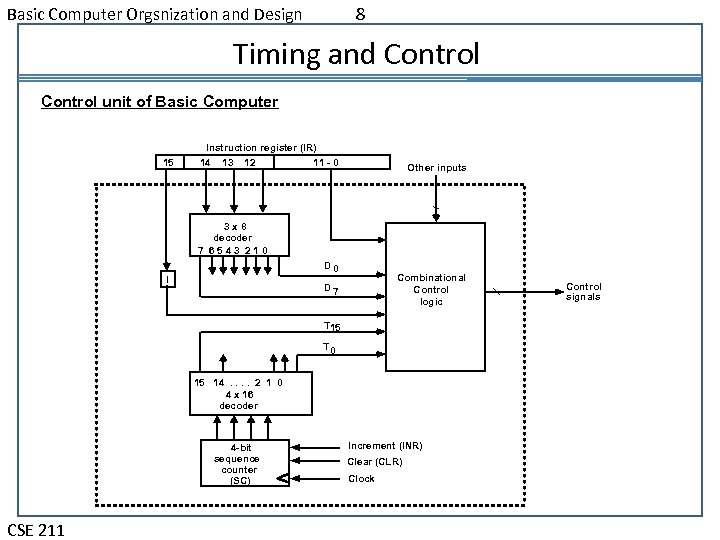

Basic Computer Orgsnization and Design 8 Timing and Control unit of Basic Computer 15 Instruction register (IR) 14 13 12 11 - 0 Other inputs 3 x 8 decoder 7 6543 210 D 0 I Combinational Control logic D 7 T 15 T 0 15 14. . 2 1 0 4 x 16 decoder 4 -bit sequence counter (SC) CSE 211 Increment (INR) Clear (CLR) Clock Control signals

Basic Computer Orgsnization and Design 8 Timing and Control unit of Basic Computer 15 Instruction register (IR) 14 13 12 11 - 0 Other inputs 3 x 8 decoder 7 6543 210 D 0 I Combinational Control logic D 7 T 15 T 0 15 14. . 2 1 0 4 x 16 decoder 4 -bit sequence counter (SC) CSE 211 Increment (INR) Clear (CLR) Clock Control signals

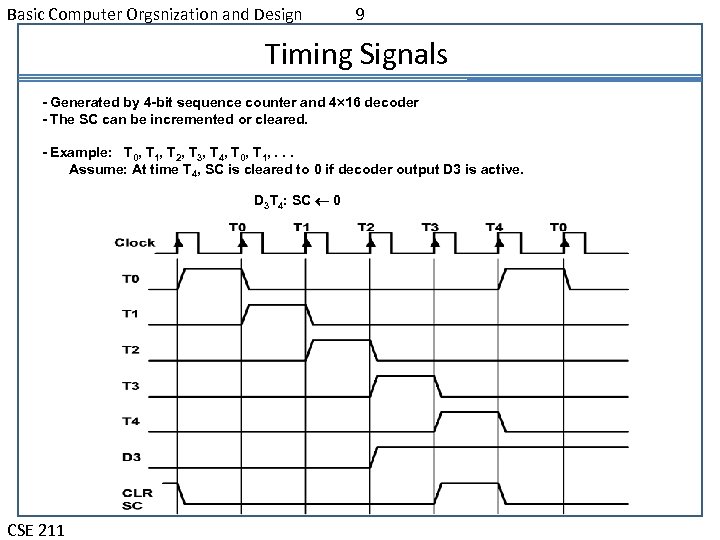

Basic Computer Orgsnization and Design 9 Timing Signals - Generated by 4 -bit sequence counter and 4 16 decoder - The SC can be incremented or cleared. - Example: T 0, T 1, T 2, T 3, T 4, T 0, T 1, . . . Assume: At time T 4, SC is cleared to 0 if decoder output D 3 is active. D 3 T 4: SC 0 CSE 211

Basic Computer Orgsnization and Design 9 Timing Signals - Generated by 4 -bit sequence counter and 4 16 decoder - The SC can be incremented or cleared. - Example: T 0, T 1, T 2, T 3, T 4, T 0, T 1, . . . Assume: At time T 4, SC is cleared to 0 if decoder output D 3 is active. D 3 T 4: SC 0 CSE 211

Basic Computer Orgsnization and Design 10 Instruction Cycle Ø In Basic Computer, a machine instruction is executed in the following cycle: 1. Fetch an instruction from memory 2. Decode the instruction 3. Read the effective address from memory if the instruction has an indirect address 4. Execute the instruction Ø After an instruction is executed, the cycle starts again at step 1, for the next instruction Note: Every different processor has its own (different) instruction cycle CSE 211

Basic Computer Orgsnization and Design 10 Instruction Cycle Ø In Basic Computer, a machine instruction is executed in the following cycle: 1. Fetch an instruction from memory 2. Decode the instruction 3. Read the effective address from memory if the instruction has an indirect address 4. Execute the instruction Ø After an instruction is executed, the cycle starts again at step 1, for the next instruction Note: Every different processor has its own (different) instruction cycle CSE 211

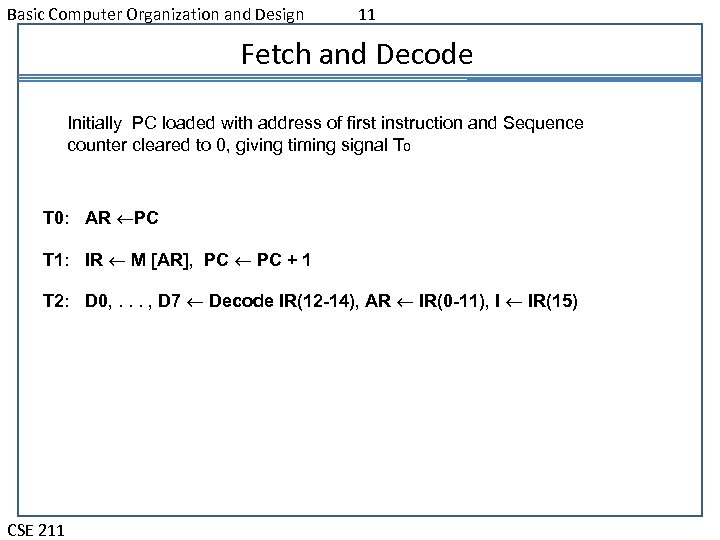

Basic Computer Organization and Design 11 Fetch and Decode Initially PC loaded with address of first instruction and Sequence counter cleared to 0, giving timing signal T 0: AR PC T 1: IR M [AR], PC + 1 T 2: D 0, . . . , D 7 Decode IR(12 -14), AR IR(0 -11), I IR(15) CSE 211

Basic Computer Organization and Design 11 Fetch and Decode Initially PC loaded with address of first instruction and Sequence counter cleared to 0, giving timing signal T 0: AR PC T 1: IR M [AR], PC + 1 T 2: D 0, . . . , D 7 Decode IR(12 -14), AR IR(0 -11), I IR(15) CSE 211

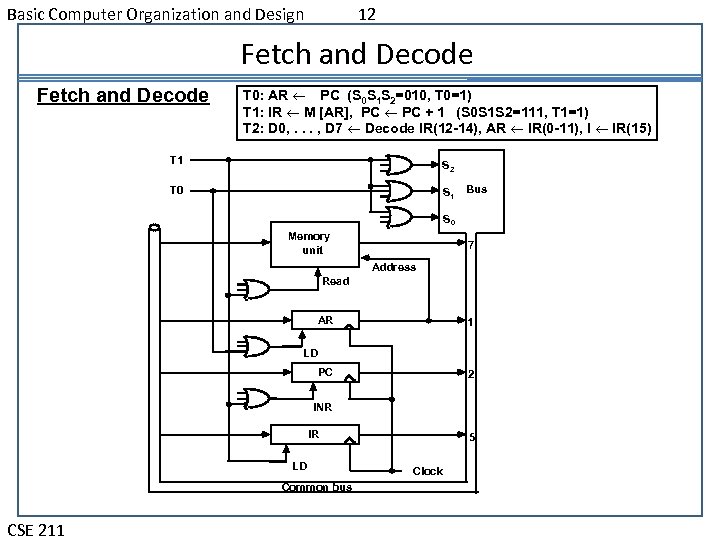

Basic Computer Organization and Design 12 Fetch and Decode T 0: AR PC (S 0 S 1 S 2=010, T 0=1) T 1: IR M [AR], PC + 1 (S 0 S 1 S 2=111, T 1=1) T 2: D 0, . . . , D 7 Decode IR(12 -14), AR IR(0 -11), I IR(15) T 1 S 2 T 0 S 1 Bus S 0 Memory unit 7 Address Read AR 1 LD PC 2 INR IR LD Common bus CSE 211 5 Clock

Basic Computer Organization and Design 12 Fetch and Decode T 0: AR PC (S 0 S 1 S 2=010, T 0=1) T 1: IR M [AR], PC + 1 (S 0 S 1 S 2=111, T 1=1) T 2: D 0, . . . , D 7 Decode IR(12 -14), AR IR(0 -11), I IR(15) T 1 S 2 T 0 S 1 Bus S 0 Memory unit 7 Address Read AR 1 LD PC 2 INR IR LD Common bus CSE 211 5 Clock

Basic Computer Organization and Design 13 Fetch and Decode Ø Figure shows how first two statements are implemented in bus system Ø At T 0 : Ø Ø Ø At T 1 : Ø Ø CSE 211 1. Place the content of PC into bus by making S 2 S 1 S 0=010 Transfer the content of bus to AR by enabling the LD input of AR 1. Enable read input of memory 2. Place content of bus by making S 2 S 1 S 0=111 3. Transfer content of bus to IR by enabling the LD input of IR 4. Increment PC by enabling the INR input of PC

Basic Computer Organization and Design 13 Fetch and Decode Ø Figure shows how first two statements are implemented in bus system Ø At T 0 : Ø Ø Ø At T 1 : Ø Ø CSE 211 1. Place the content of PC into bus by making S 2 S 1 S 0=010 Transfer the content of bus to AR by enabling the LD input of AR 1. Enable read input of memory 2. Place content of bus by making S 2 S 1 S 0=111 3. Transfer content of bus to IR by enabling the LD input of IR 4. Increment PC by enabling the INR input of PC

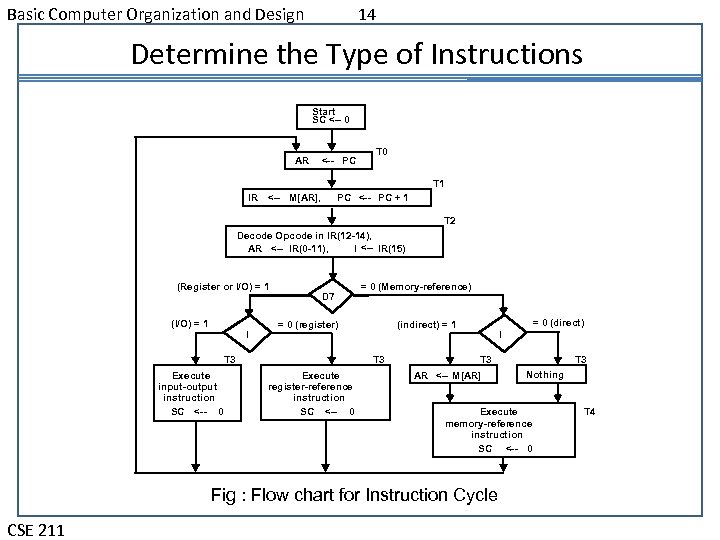

Basic Computer Organization and Design 14 Determine the Type of Instructions Start SC <-- 0 AR <-- PC T 0 T 1 IR <-- M[AR], PC <-- PC + 1 T 2 Decode Opcode in IR(12 -14), AR <-- IR(0 -11), I <-- IR(15) (Register or I/O) = 1 (I/O) = 1 I D 7 = 0 (register) T 3 Execute input-output instruction SC <-- 0 = 0 (Memory-reference) T 3 Execute register-reference instruction SC <-- 0 = 0 (direct) (indirect) = 1 I T 3 AR <-- M[AR] Nothing Execute memory-reference instruction SC <-- 0 Fig : Flow chart for Instruction Cycle CSE 211 T 3 T 4

Basic Computer Organization and Design 14 Determine the Type of Instructions Start SC <-- 0 AR <-- PC T 0 T 1 IR <-- M[AR], PC <-- PC + 1 T 2 Decode Opcode in IR(12 -14), AR <-- IR(0 -11), I <-- IR(15) (Register or I/O) = 1 (I/O) = 1 I D 7 = 0 (register) T 3 Execute input-output instruction SC <-- 0 = 0 (Memory-reference) T 3 Execute register-reference instruction SC <-- 0 = 0 (direct) (indirect) = 1 I T 3 AR <-- M[AR] Nothing Execute memory-reference instruction SC <-- 0 Fig : Flow chart for Instruction Cycle CSE 211 T 3 T 4

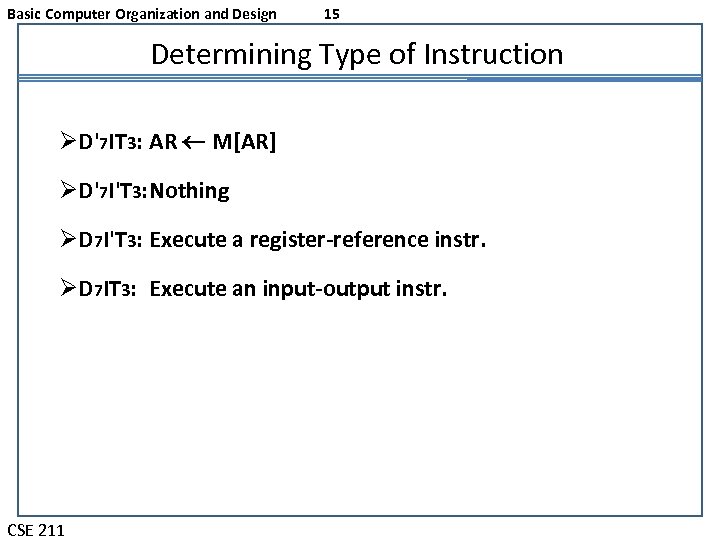

Basic Computer Organization and Design 15 Determining Type of Instruction ØD'7 IT 3: AR M[AR] ØD'7 I'T 3: Nothing ØD 7 I'T 3: Execute a register-reference instr. ØD 7 IT 3: Execute an input-output instr. CSE 211

Basic Computer Organization and Design 15 Determining Type of Instruction ØD'7 IT 3: AR M[AR] ØD'7 I'T 3: Nothing ØD 7 I'T 3: Execute a register-reference instr. ØD 7 IT 3: Execute an input-output instr. CSE 211

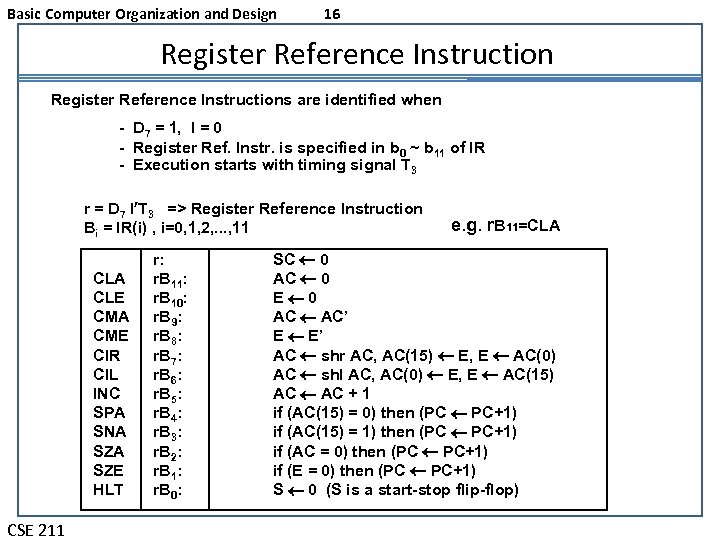

Basic Computer Organization and Design 16 Register Reference Instructions are identified when - D 7 = 1, I = 0 - Register Ref. Instr. is specified in b 0 ~ b 11 of IR - Execution starts with timing signal T 3 r = D 7 I T 3 => Register Reference Instruction Bi = IR(i) , i=0, 1, 2, . . . , 11 CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT CSE 211 r: r. B 11: r. B 10: r. B 9: r. B 8: r. B 7: r. B 6: r. B 5: r. B 4: r. B 3: r. B 2: r. B 1: r. B 0: e. g. r. B 11=CLA SC 0 AC 0 E 0 AC AC’ E E’ AC shr AC, AC(15) E, E AC(0) AC shl AC, AC(0) E, E AC(15) AC + 1 if (AC(15) = 0) then (PC PC+1) if (AC(15) = 1) then (PC PC+1) if (AC = 0) then (PC PC+1) if (E = 0) then (PC PC+1) S 0 (S is a start-stop flip-flop)

Basic Computer Organization and Design 16 Register Reference Instructions are identified when - D 7 = 1, I = 0 - Register Ref. Instr. is specified in b 0 ~ b 11 of IR - Execution starts with timing signal T 3 r = D 7 I T 3 => Register Reference Instruction Bi = IR(i) , i=0, 1, 2, . . . , 11 CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT CSE 211 r: r. B 11: r. B 10: r. B 9: r. B 8: r. B 7: r. B 6: r. B 5: r. B 4: r. B 3: r. B 2: r. B 1: r. B 0: e. g. r. B 11=CLA SC 0 AC 0 E 0 AC AC’ E E’ AC shr AC, AC(15) E, E AC(0) AC shl AC, AC(0) E, E AC(15) AC + 1 if (AC(15) = 0) then (PC PC+1) if (AC(15) = 1) then (PC PC+1) if (AC = 0) then (PC PC+1) if (E = 0) then (PC PC+1) S 0 (S is a start-stop flip-flop)

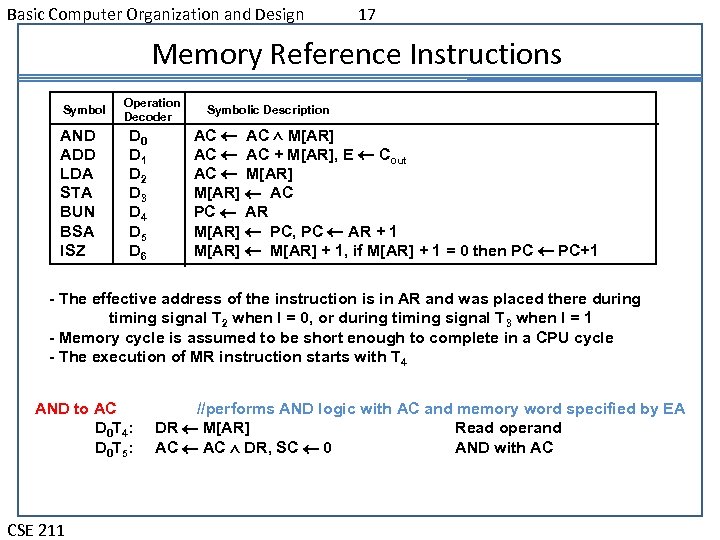

Basic Computer Organization and Design 17 Memory Reference Instructions Symbol AND ADD LDA STA BUN BSA ISZ Operation Decoder D 0 D 1 D 2 D 3 D 4 D 5 D 6 Symbolic Description AC M[AR] AC + M[AR], E Cout AC M[AR] AC PC AR M[AR] PC, PC AR + 1 M[AR] + 1, if M[AR] + 1 = 0 then PC PC+1 - The effective address of the instruction is in AR and was placed there during timing signal T 2 when I = 0, or during timing signal T 3 when I = 1 - Memory cycle is assumed to be short enough to complete in a CPU cycle - The execution of MR instruction starts with T 4 AND to AC D 0 T 4 : D 0 T 5 : CSE 211 //performs AND logic with AC and memory word specified by EA DR M[AR] Read operand AC DR, SC 0 AND with AC

Basic Computer Organization and Design 17 Memory Reference Instructions Symbol AND ADD LDA STA BUN BSA ISZ Operation Decoder D 0 D 1 D 2 D 3 D 4 D 5 D 6 Symbolic Description AC M[AR] AC + M[AR], E Cout AC M[AR] AC PC AR M[AR] PC, PC AR + 1 M[AR] + 1, if M[AR] + 1 = 0 then PC PC+1 - The effective address of the instruction is in AR and was placed there during timing signal T 2 when I = 0, or during timing signal T 3 when I = 1 - Memory cycle is assumed to be short enough to complete in a CPU cycle - The execution of MR instruction starts with T 4 AND to AC D 0 T 4 : D 0 T 5 : CSE 211 //performs AND logic with AC and memory word specified by EA DR M[AR] Read operand AC DR, SC 0 AND with AC

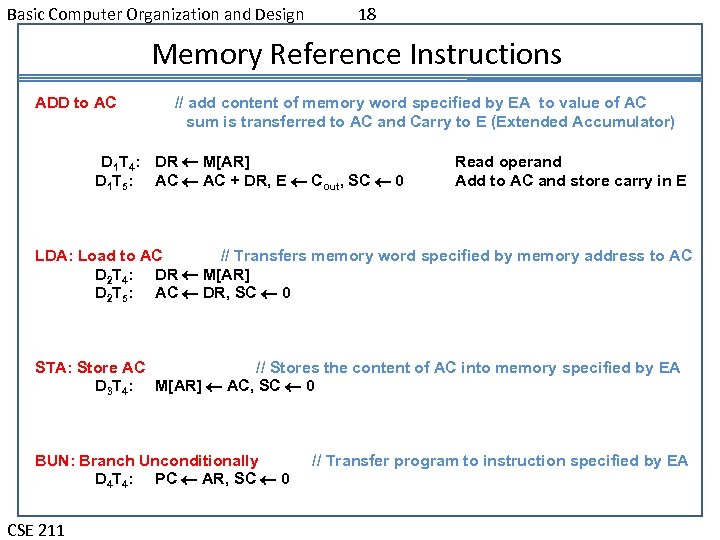

Basic Computer Organization and Design 18 Memory Reference Instructions ADD to AC // add content of memory word specified by EA to value of AC sum is transferred to AC and Carry to E (Extended Accumulator) D 1 T 4: DR M[AR] D 1 T 5: AC + DR, E Cout, SC 0 Read operand Add to AC and store carry in E LDA: Load to AC // Transfers memory word specified by memory address to AC D 2 T 4: DR M[AR] D 2 T 5: AC DR, SC 0 STA: Store AC // Stores the content of AC into memory specified by EA D 3 T 4: M[AR] AC, SC 0 BUN: Branch Unconditionally D 4 T 4: PC AR, SC 0 CSE 211 // Transfer program to instruction specified by EA

Basic Computer Organization and Design 18 Memory Reference Instructions ADD to AC // add content of memory word specified by EA to value of AC sum is transferred to AC and Carry to E (Extended Accumulator) D 1 T 4: DR M[AR] D 1 T 5: AC + DR, E Cout, SC 0 Read operand Add to AC and store carry in E LDA: Load to AC // Transfers memory word specified by memory address to AC D 2 T 4: DR M[AR] D 2 T 5: AC DR, SC 0 STA: Store AC // Stores the content of AC into memory specified by EA D 3 T 4: M[AR] AC, SC 0 BUN: Branch Unconditionally D 4 T 4: PC AR, SC 0 CSE 211 // Transfer program to instruction specified by EA

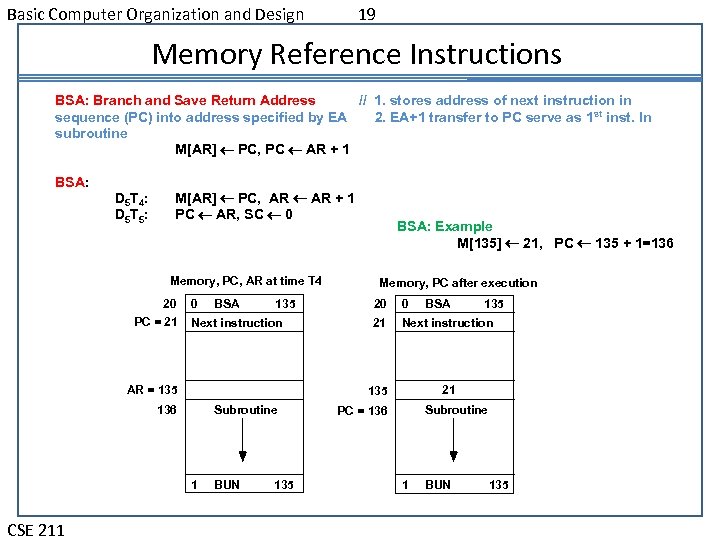

Basic Computer Organization and Design 19 Memory Reference Instructions BSA: Branch and Save Return Address // 1. stores address of next instruction in sequence (PC) into address specified by EA 2. EA+1 transfer to PC serve as 1 st inst. In subroutine M[AR] PC, PC AR + 1 BSA: D 5 T 4: D 5 T 5: M[AR] PC, AR + 1 PC AR, SC 0 Memory, PC, AR at time T 4 20 PC = 21 0 BSA 135 Memory, PC after execution 136 Subroutine 1 BUN 135 20 0 21 Next instruction 135 Next instruction AR = 135 CSE 211 BSA: Example M[135] 21, PC 135 + 1=136 BSA 135 21 Subroutine PC = 136 1 BUN 135

Basic Computer Organization and Design 19 Memory Reference Instructions BSA: Branch and Save Return Address // 1. stores address of next instruction in sequence (PC) into address specified by EA 2. EA+1 transfer to PC serve as 1 st inst. In subroutine M[AR] PC, PC AR + 1 BSA: D 5 T 4: D 5 T 5: M[AR] PC, AR + 1 PC AR, SC 0 Memory, PC, AR at time T 4 20 PC = 21 0 BSA 135 Memory, PC after execution 136 Subroutine 1 BUN 135 20 0 21 Next instruction 135 Next instruction AR = 135 CSE 211 BSA: Example M[135] 21, PC 135 + 1=136 BSA 135 21 Subroutine PC = 136 1 BUN 135

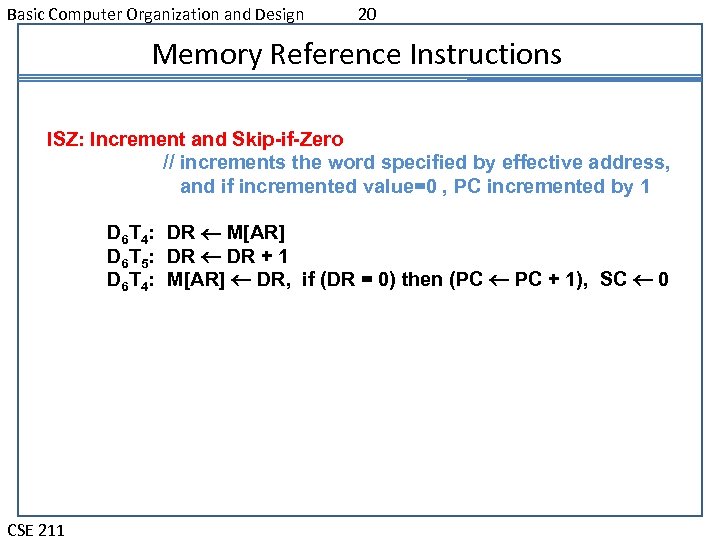

Basic Computer Organization and Design 20 Memory Reference Instructions ISZ: Increment and Skip-if-Zero // increments the word specified by effective address, and if incremented value=0 , PC incremented by 1 D 6 T 4: DR M[AR] D 6 T 5: DR + 1 D 6 T 4: M[AR] DR, if (DR = 0) then (PC PC + 1), SC 0 CSE 211

Basic Computer Organization and Design 20 Memory Reference Instructions ISZ: Increment and Skip-if-Zero // increments the word specified by effective address, and if incremented value=0 , PC incremented by 1 D 6 T 4: DR M[AR] D 6 T 5: DR + 1 D 6 T 4: M[AR] DR, if (DR = 0) then (PC PC + 1), SC 0 CSE 211

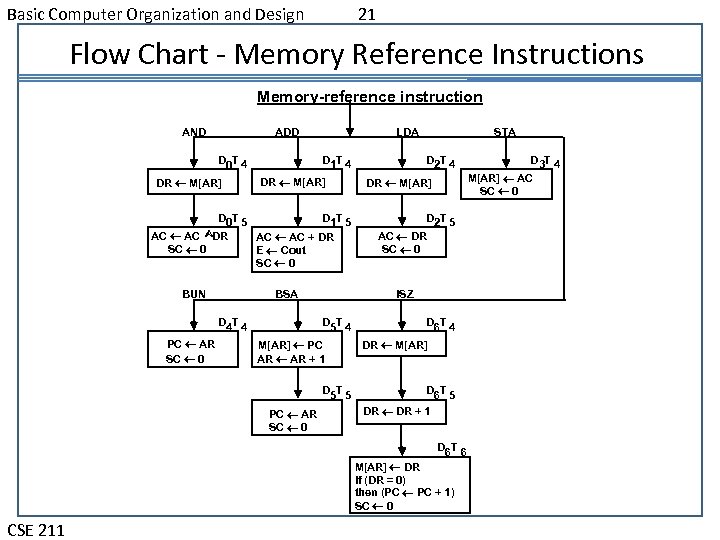

Basic Computer Organization and Design 21 Flow Chart - Memory Reference Instructions Memory-reference instruction AND ADD D T 4 0 DR M[AR] D 1 T 4 DR M[AR] D 0 T 5 AC DR SC 0 BUN AC + DR E Cout SC 0 BSA M[AR] PC AR + 1 D 5 T 5 D 2 T 5 AC DR SC 0 D 6 T 4 DR M[AR] D 6 T 5 DR + 1 D 6 T 6 M[AR] DR If (DR = 0) then (PC PC + 1) SC 0 CSE 211 D 3 T 4 M[AR] AC SC 0 DR M[AR] ISZ D 5 T 4 PC AR SC 0 STA D 2 T 4 D 1 T 5 D 4 T 4 PC AR SC 0 LDA

Basic Computer Organization and Design 21 Flow Chart - Memory Reference Instructions Memory-reference instruction AND ADD D T 4 0 DR M[AR] D 1 T 4 DR M[AR] D 0 T 5 AC DR SC 0 BUN AC + DR E Cout SC 0 BSA M[AR] PC AR + 1 D 5 T 5 D 2 T 5 AC DR SC 0 D 6 T 4 DR M[AR] D 6 T 5 DR + 1 D 6 T 6 M[AR] DR If (DR = 0) then (PC PC + 1) SC 0 CSE 211 D 3 T 4 M[AR] AC SC 0 DR M[AR] ISZ D 5 T 4 PC AR SC 0 STA D 2 T 4 D 1 T 5 D 4 T 4 PC AR SC 0 LDA

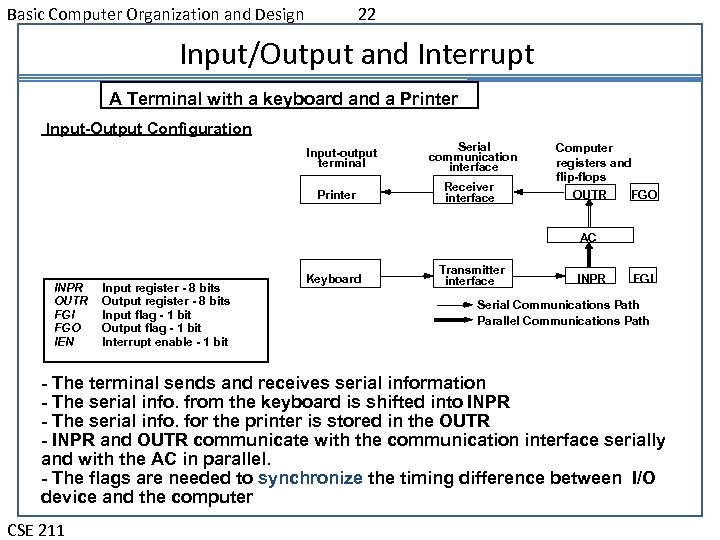

Basic Computer Organization and Design 22 Input/Output and Interrupt A Terminal with a keyboard and a Printer Input-Output Configuration Input-output terminal Printer Serial communication interface Receiver interface Computer registers and flip-flops OUTR FGO AC INPR OUTR FGI FGO IEN Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit Keyboard Transmitter interface INPR FGI Serial Communications Path Parallel Communications Path - The terminal sends and receives serial information - The serial info. from the keyboard is shifted into INPR - The serial info. for the printer is stored in the OUTR - INPR and OUTR communicate with the communication interface serially and with the AC in parallel. - The flags are needed to synchronize the timing difference between I/O device and the computer CSE 211

Basic Computer Organization and Design 22 Input/Output and Interrupt A Terminal with a keyboard and a Printer Input-Output Configuration Input-output terminal Printer Serial communication interface Receiver interface Computer registers and flip-flops OUTR FGO AC INPR OUTR FGI FGO IEN Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit Keyboard Transmitter interface INPR FGI Serial Communications Path Parallel Communications Path - The terminal sends and receives serial information - The serial info. from the keyboard is shifted into INPR - The serial info. for the printer is stored in the OUTR - INPR and OUTR communicate with the communication interface serially and with the AC in parallel. - The flags are needed to synchronize the timing difference between I/O device and the computer CSE 211

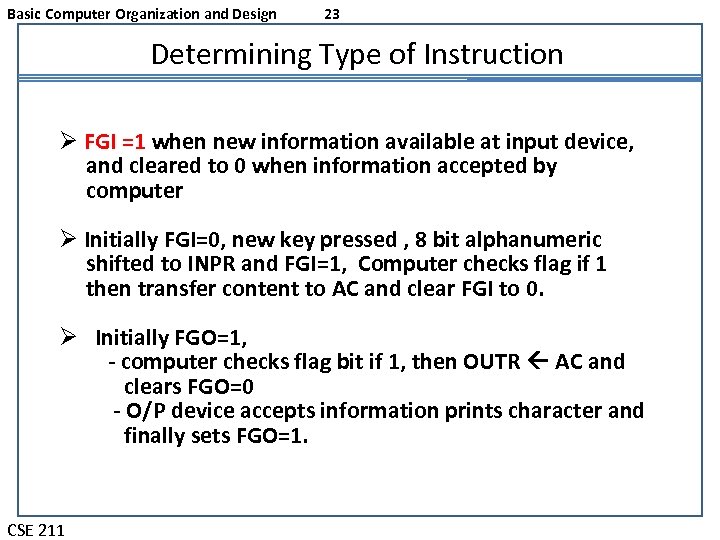

Basic Computer Organization and Design 23 Determining Type of Instruction Ø FGI =1 when new information available at input device, and cleared to 0 when information accepted by computer Ø Initially FGI=0, new key pressed , 8 bit alphanumeric shifted to INPR and FGI=1, Computer checks flag if 1 then transfer content to AC and clear FGI to 0. Ø Initially FGO=1, - computer checks flag bit if 1, then OUTR AC and clears FGO=0 - O/P device accepts information prints character and finally sets FGO=1. CSE 211

Basic Computer Organization and Design 23 Determining Type of Instruction Ø FGI =1 when new information available at input device, and cleared to 0 when information accepted by computer Ø Initially FGI=0, new key pressed , 8 bit alphanumeric shifted to INPR and FGI=1, Computer checks flag if 1 then transfer content to AC and clear FGI to 0. Ø Initially FGO=1, - computer checks flag bit if 1, then OUTR AC and clears FGO=0 - O/P device accepts information prints character and finally sets FGO=1. CSE 211

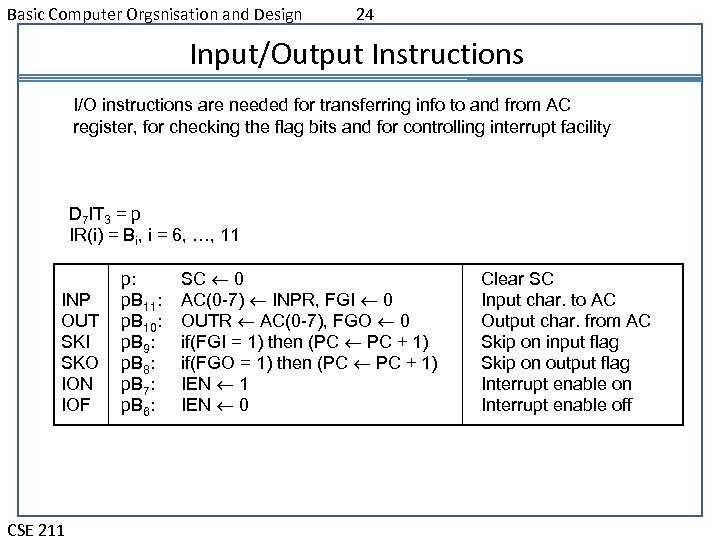

Basic Computer Orgsnisation and Design 24 Input/Output Instructions I/O instructions are needed for transferring info to and from AC register, for checking the flag bits and for controlling interrupt facility D 7 IT 3 = p IR(i) = Bi, i = 6, …, 11 INP OUT SKI SKO ION IOF CSE 211 p: p. B 11: p. B 10: p. B 9: p. B 8: p. B 7: p. B 6: SC 0 AC(0 -7) INPR, FGI 0 OUTR AC(0 -7), FGO 0 if(FGI = 1) then (PC PC + 1) if(FGO = 1) then (PC PC + 1) IEN 1 IEN 0 Clear SC Input char. to AC Output char. from AC Skip on input flag Skip on output flag Interrupt enable on Interrupt enable off

Basic Computer Orgsnisation and Design 24 Input/Output Instructions I/O instructions are needed for transferring info to and from AC register, for checking the flag bits and for controlling interrupt facility D 7 IT 3 = p IR(i) = Bi, i = 6, …, 11 INP OUT SKI SKO ION IOF CSE 211 p: p. B 11: p. B 10: p. B 9: p. B 8: p. B 7: p. B 6: SC 0 AC(0 -7) INPR, FGI 0 OUTR AC(0 -7), FGO 0 if(FGI = 1) then (PC PC + 1) if(FGO = 1) then (PC PC + 1) IEN 1 IEN 0 Clear SC Input char. to AC Output char. from AC Skip on input flag Skip on output flag Interrupt enable on Interrupt enable off

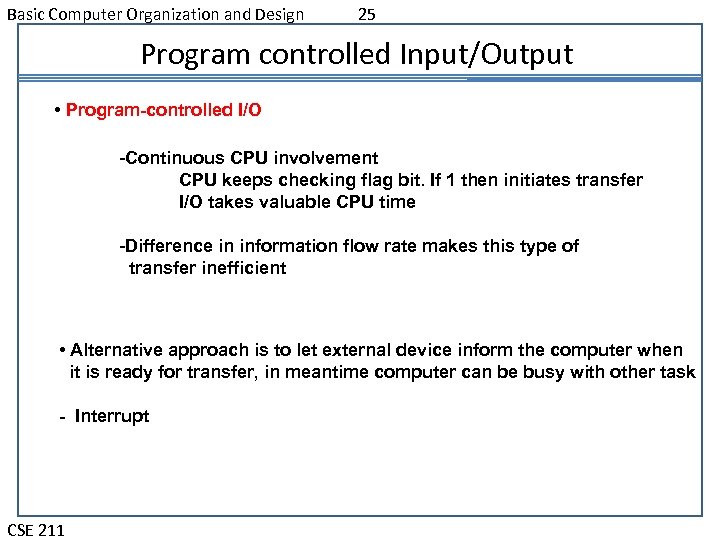

Basic Computer Organization and Design 25 Program controlled Input/Output • Program-controlled I/O -Continuous CPU involvement CPU keeps checking flag bit. If 1 then initiates transfer I/O takes valuable CPU time -Difference in information flow rate makes this type of transfer inefficient • Alternative approach is to let external device inform the computer when it is ready for transfer, in meantime computer can be busy with other task - Interrupt CSE 211

Basic Computer Organization and Design 25 Program controlled Input/Output • Program-controlled I/O -Continuous CPU involvement CPU keeps checking flag bit. If 1 then initiates transfer I/O takes valuable CPU time -Difference in information flow rate makes this type of transfer inefficient • Alternative approach is to let external device inform the computer when it is ready for transfer, in meantime computer can be busy with other task - Interrupt CSE 211

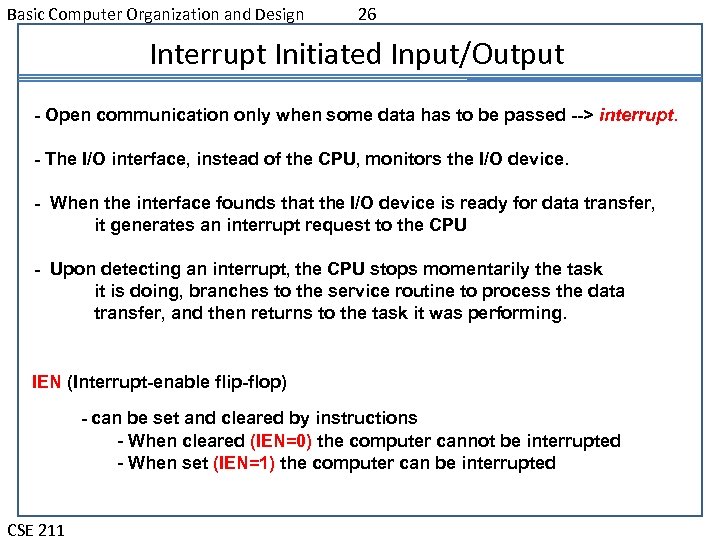

Basic Computer Organization and Design 26 Interrupt Initiated Input/Output - Open communication only when some data has to be passed --> interrupt. - The I/O interface, instead of the CPU, monitors the I/O device. - When the interface founds that the I/O device is ready for data transfer, it generates an interrupt request to the CPU - Upon detecting an interrupt, the CPU stops momentarily the task it is doing, branches to the service routine to process the data transfer, and then returns to the task it was performing. IEN (Interrupt-enable flip-flop) - can be set and cleared by instructions - When cleared (IEN=0) the computer cannot be interrupted - When set (IEN=1) the computer can be interrupted CSE 211

Basic Computer Organization and Design 26 Interrupt Initiated Input/Output - Open communication only when some data has to be passed --> interrupt. - The I/O interface, instead of the CPU, monitors the I/O device. - When the interface founds that the I/O device is ready for data transfer, it generates an interrupt request to the CPU - Upon detecting an interrupt, the CPU stops momentarily the task it is doing, branches to the service routine to process the data transfer, and then returns to the task it was performing. IEN (Interrupt-enable flip-flop) - can be set and cleared by instructions - When cleared (IEN=0) the computer cannot be interrupted - When set (IEN=1) the computer can be interrupted CSE 211

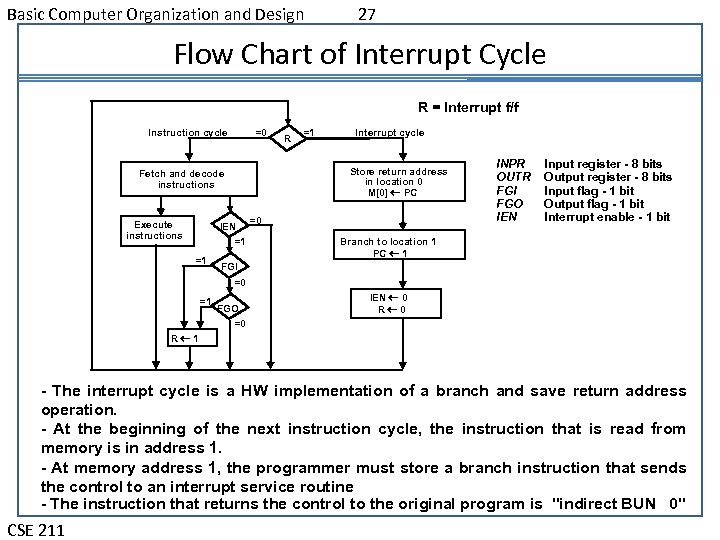

Basic Computer Organization and Design 27 Flow Chart of Interrupt Cycle R = Interrupt f/f =0 Instruction cycle IEN =1 =1 =1 Interrupt cycle Store return address in location 0 M[0] PC Fetch and decode instructions Execute instructions R =0 INPR OUTR FGI FGO IEN Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit Branch to location 1 PC 1 FGI =0 =1 FGO IEN 0 R 0 =0 R 1 - The interrupt cycle is a HW implementation of a branch and save return address operation. - At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1. - At memory address 1, the programmer must store a branch instruction that sends the control to an interrupt service routine - The instruction that returns the control to the original program is "indirect BUN 0" CSE 211

Basic Computer Organization and Design 27 Flow Chart of Interrupt Cycle R = Interrupt f/f =0 Instruction cycle IEN =1 =1 =1 Interrupt cycle Store return address in location 0 M[0] PC Fetch and decode instructions Execute instructions R =0 INPR OUTR FGI FGO IEN Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit Branch to location 1 PC 1 FGI =0 =1 FGO IEN 0 R 0 =0 R 1 - The interrupt cycle is a HW implementation of a branch and save return address operation. - At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1. - At memory address 1, the programmer must store a branch instruction that sends the control to an interrupt service routine - The instruction that returns the control to the original program is "indirect BUN 0" CSE 211

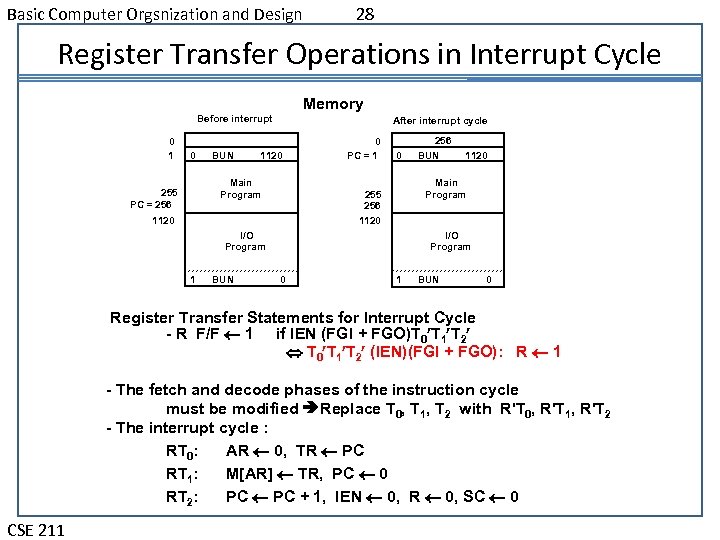

Basic Computer Orgsnization and Design 28 Register Transfer Operations in Interrupt Cycle Memory Before interrupt 0 1 0 BUN After interrupt cycle 1120 Main Program 255 PC = 256 0 PC = 1 256 0 I/O Program 1 BUN 1120 Main Program 255 256 1120 BUN I/O Program 0 1 BUN 0 Register Transfer Statements for Interrupt Cycle - R F/F 1 if IEN (FGI + FGO)T 0 T 1 T 2 (IEN)(FGI + FGO): R 1 - The fetch and decode phases of the instruction cycle must be modified Replace T 0, T 1, T 2 with R'T 0, R'T 1, R'T 2 - The interrupt cycle : RT 0: AR 0, TR PC RT 1: M[AR] TR, PC 0 RT 2: PC + 1, IEN 0, R 0, SC 0 CSE 211

Basic Computer Orgsnization and Design 28 Register Transfer Operations in Interrupt Cycle Memory Before interrupt 0 1 0 BUN After interrupt cycle 1120 Main Program 255 PC = 256 0 PC = 1 256 0 I/O Program 1 BUN 1120 Main Program 255 256 1120 BUN I/O Program 0 1 BUN 0 Register Transfer Statements for Interrupt Cycle - R F/F 1 if IEN (FGI + FGO)T 0 T 1 T 2 (IEN)(FGI + FGO): R 1 - The fetch and decode phases of the instruction cycle must be modified Replace T 0, T 1, T 2 with R'T 0, R'T 1, R'T 2 - The interrupt cycle : RT 0: AR 0, TR PC RT 1: M[AR] TR, PC 0 RT 2: PC + 1, IEN 0, R 0, SC 0 CSE 211

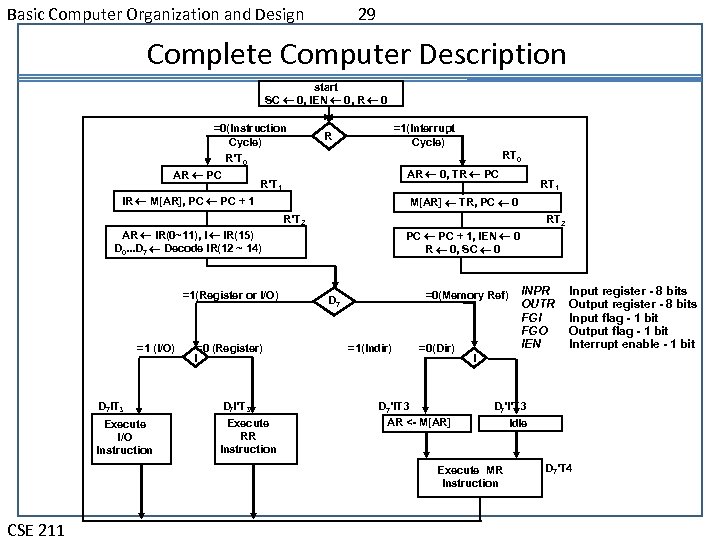

Basic Computer Organization and Design 29 Complete Computer Description start SC 0, IEN 0, R 0 =0(Instruction Cycle) =1(Interrupt Cycle) R RT 0 R’T 0 AR PC AR 0, TR PC R’T 1 IR M[AR], PC + 1 RT 1 M[AR] TR, PC 0 R’T 2 RT 2 AR IR(0~11), I IR(15) D 0. . . D 7 Decode IR(12 ~ 14) =1(Register or I/O) =1 (I/O) =0 (Register) I D 7 IT 3 D 7 I’T 3 Execute I/O Instruction Execute RR Instruction PC + 1, IEN 0 R 0, SC 0 =0(Memory Ref) D 7 =1(Indir) =0(Dir) D 7’IT 3 AR <- M[AR] Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit I D 7’I’T 3 Execute MR Instruction CSE 211 INPR OUTR FGI FGO IEN Idle D 7’T 4

Basic Computer Organization and Design 29 Complete Computer Description start SC 0, IEN 0, R 0 =0(Instruction Cycle) =1(Interrupt Cycle) R RT 0 R’T 0 AR PC AR 0, TR PC R’T 1 IR M[AR], PC + 1 RT 1 M[AR] TR, PC 0 R’T 2 RT 2 AR IR(0~11), I IR(15) D 0. . . D 7 Decode IR(12 ~ 14) =1(Register or I/O) =1 (I/O) =0 (Register) I D 7 IT 3 D 7 I’T 3 Execute I/O Instruction Execute RR Instruction PC + 1, IEN 0 R 0, SC 0 =0(Memory Ref) D 7 =1(Indir) =0(Dir) D 7’IT 3 AR <- M[AR] Input register - 8 bits Output register - 8 bits Input flag - 1 bit Output flag - 1 bit Interrupt enable - 1 bit I D 7’I’T 3 Execute MR Instruction CSE 211 INPR OUTR FGI FGO IEN Idle D 7’T 4

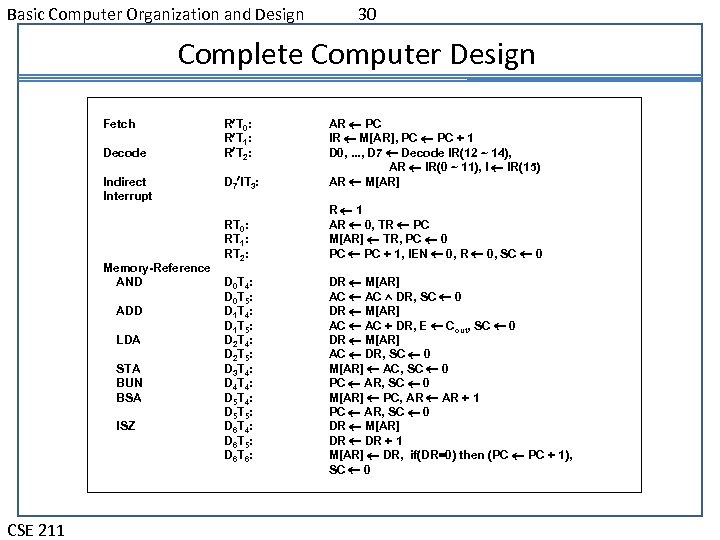

Basic Computer Organization and Design 30 Complete Computer Design Fetch Decode Indirect Interrupt Memory-Reference AND ADD LDA STA BUN BSA ISZ CSE 211 D 7 IT 3: AR PC IR M[AR], PC + 1 D 0, . . . , D 7 Decode IR(12 ~ 14), AR IR(0 ~ 11), I IR(15) AR M[AR] RT 0: RT 1: RT 2: R 1 AR 0, TR PC M[AR] TR, PC 0 PC + 1, IEN 0, R 0, SC 0 R T 0: R T 1: R T 2: D 0 T 4: D 0 T 5: D 1 T 4: D 1 T 5: D 2 T 4: D 2 T 5: D 3 T 4: D 4 T 4: D 5 T 5: D 6 T 4: D 6 T 5: D 6 T 6: DR M[AR] AC DR, SC 0 DR M[AR] AC + DR, E Cout, SC 0 DR M[AR] AC DR, SC 0 M[AR] AC, SC 0 PC AR, SC 0 M[AR] PC, AR + 1 PC AR, SC 0 DR M[AR] DR + 1 M[AR] DR, if(DR=0) then (PC PC + 1), SC 0

Basic Computer Organization and Design 30 Complete Computer Design Fetch Decode Indirect Interrupt Memory-Reference AND ADD LDA STA BUN BSA ISZ CSE 211 D 7 IT 3: AR PC IR M[AR], PC + 1 D 0, . . . , D 7 Decode IR(12 ~ 14), AR IR(0 ~ 11), I IR(15) AR M[AR] RT 0: RT 1: RT 2: R 1 AR 0, TR PC M[AR] TR, PC 0 PC + 1, IEN 0, R 0, SC 0 R T 0: R T 1: R T 2: D 0 T 4: D 0 T 5: D 1 T 4: D 1 T 5: D 2 T 4: D 2 T 5: D 3 T 4: D 4 T 4: D 5 T 5: D 6 T 4: D 6 T 5: D 6 T 6: DR M[AR] AC DR, SC 0 DR M[AR] AC + DR, E Cout, SC 0 DR M[AR] AC DR, SC 0 M[AR] AC, SC 0 PC AR, SC 0 M[AR] PC, AR + 1 PC AR, SC 0 DR M[AR] DR + 1 M[AR] DR, if(DR=0) then (PC PC + 1), SC 0

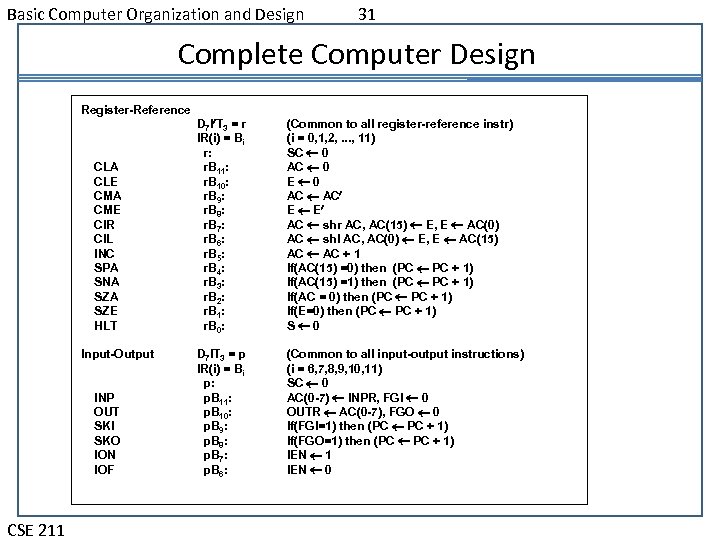

Basic Computer Organization and Design 31 Complete Computer Design Register-Reference CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT Input-Output INP OUT SKI SKO ION IOF CSE 211 D 7 I T 3 = r IR(i) = Bi r: r. B 11: r. B 10: r. B 9: r. B 8: r. B 7: r. B 6: r. B 5: r. B 4: r. B 3: r. B 2: r. B 1: r. B 0: (Common to all register-reference instr) (i = 0, 1, 2, . . . , 11) SC 0 AC 0 E 0 AC E E AC shr AC, AC(15) E, E AC(0) AC shl AC, AC(0) E, E AC(15) AC + 1 If(AC(15) =0) then (PC PC + 1) If(AC(15) =1) then (PC PC + 1) If(AC = 0) then (PC PC + 1) If(E=0) then (PC PC + 1) S 0 D 7 IT 3 = p IR(i) = Bi p: p. B 11: p. B 10: p. B 9: p. B 8: p. B 7: p. B 6: (Common to all input-output instructions) (i = 6, 7, 8, 9, 10, 11) SC 0 AC(0 -7) INPR, FGI 0 OUTR AC(0 -7), FGO 0 If(FGI=1) then (PC PC + 1) If(FGO=1) then (PC PC + 1) IEN 1 IEN 0

Basic Computer Organization and Design 31 Complete Computer Design Register-Reference CLA CLE CMA CME CIR CIL INC SPA SNA SZE HLT Input-Output INP OUT SKI SKO ION IOF CSE 211 D 7 I T 3 = r IR(i) = Bi r: r. B 11: r. B 10: r. B 9: r. B 8: r. B 7: r. B 6: r. B 5: r. B 4: r. B 3: r. B 2: r. B 1: r. B 0: (Common to all register-reference instr) (i = 0, 1, 2, . . . , 11) SC 0 AC 0 E 0 AC E E AC shr AC, AC(15) E, E AC(0) AC shl AC, AC(0) E, E AC(15) AC + 1 If(AC(15) =0) then (PC PC + 1) If(AC(15) =1) then (PC PC + 1) If(AC = 0) then (PC PC + 1) If(E=0) then (PC PC + 1) S 0 D 7 IT 3 = p IR(i) = Bi p: p. B 11: p. B 10: p. B 9: p. B 8: p. B 7: p. B 6: (Common to all input-output instructions) (i = 6, 7, 8, 9, 10, 11) SC 0 AC(0 -7) INPR, FGI 0 OUTR AC(0 -7), FGO 0 If(FGI=1) then (PC PC + 1) If(FGO=1) then (PC PC + 1) IEN 1 IEN 0

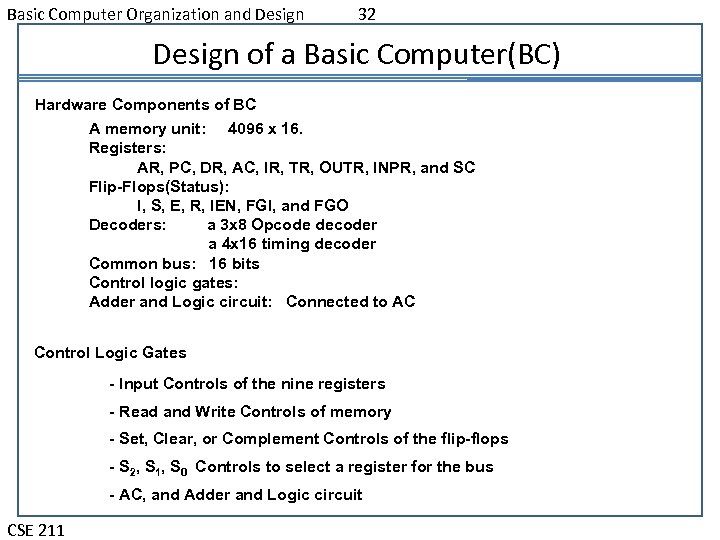

Basic Computer Organization and Design 32 Design of a Basic Computer(BC) Hardware Components of BC A memory unit: 4096 x 16. Registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC Flip-Flops(Status): I, S, E, R, IEN, FGI, and FGO Decoders: a 3 x 8 Opcode decoder a 4 x 16 timing decoder Common bus: 16 bits Control logic gates: Adder and Logic circuit: Connected to AC Control Logic Gates - Input Controls of the nine registers - Read and Write Controls of memory - Set, Clear, or Complement Controls of the flip-flops - S 2, S 1, S 0 Controls to select a register for the bus - AC, and Adder and Logic circuit CSE 211

Basic Computer Organization and Design 32 Design of a Basic Computer(BC) Hardware Components of BC A memory unit: 4096 x 16. Registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC Flip-Flops(Status): I, S, E, R, IEN, FGI, and FGO Decoders: a 3 x 8 Opcode decoder a 4 x 16 timing decoder Common bus: 16 bits Control logic gates: Adder and Logic circuit: Connected to AC Control Logic Gates - Input Controls of the nine registers - Read and Write Controls of memory - Set, Clear, or Complement Controls of the flip-flops - S 2, S 1, S 0 Controls to select a register for the bus - AC, and Adder and Logic circuit CSE 211

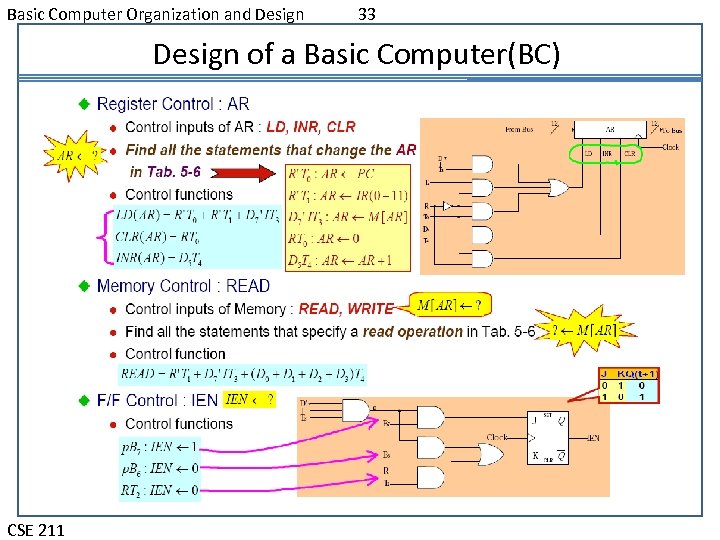

Basic Computer Organization and Design 33 Design of a Basic Computer(BC) CSE 211

Basic Computer Organization and Design 33 Design of a Basic Computer(BC) CSE 211

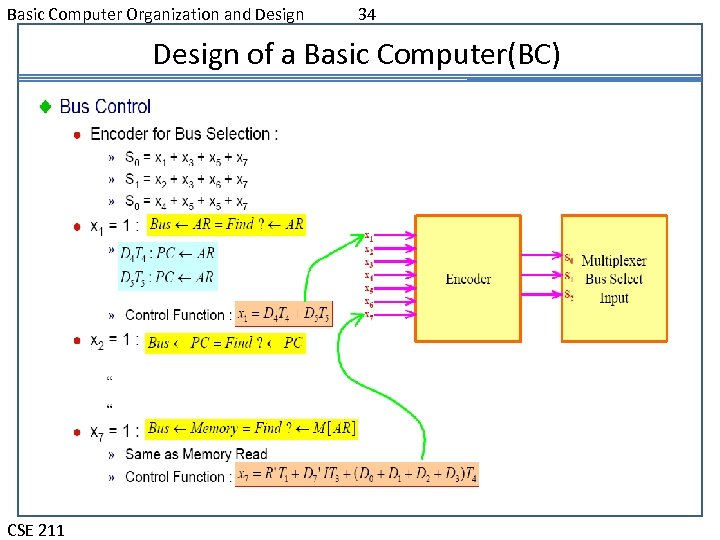

Basic Computer Organization and Design 34 Design of a Basic Computer(BC) CSE 211

Basic Computer Organization and Design 34 Design of a Basic Computer(BC) CSE 211

Any Questions ? 35

Any Questions ? 35