c8a54cf55176e136aaa40fe85d85a50d.ppt

- Количество слайдов: 22

CSC Trigger Status, MPC and Sorter B. Paul Padley Rice University November 2003 CPT Week, Nov 2003, B. Paul Padley, Rice University 1

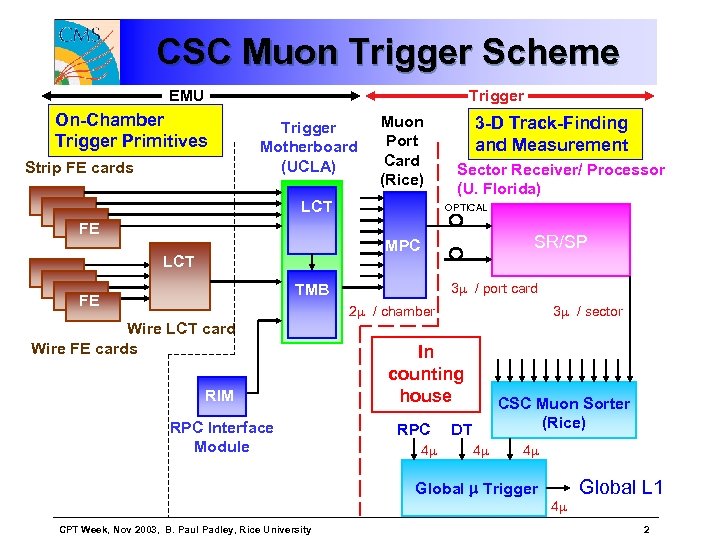

CSC Muon Trigger Scheme EMU Trigger On-Chamber Trigger Primitives Strip FE cards Trigger Motherboard (UCLA) Muon Port Card (Rice) LCT FE 3 -D Track-Finding and Measurement Sector Receiver/ Processor (U. Florida) OPTICAL SR/SP MPC LCT 3 / port card TMB FE 2 / chamber Wire LCT card Wire FE cards RIM RPC Interface Module 3 / sector In counting house RPC 4 CSC Muon Sorter (Rice) DT 4 4 Global Trigger 4 CPT Week, Nov 2003, B. Paul Padley, Rice University SP Global L 1 2

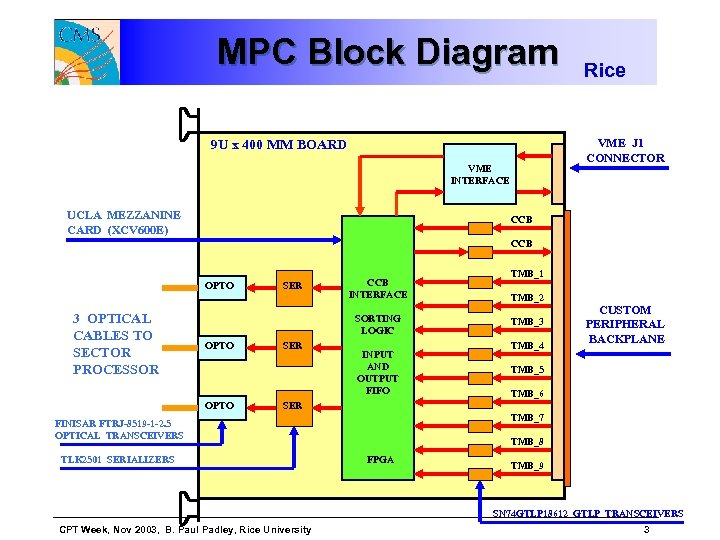

MPC Block Diagram VME J 1 CONNECTOR 9 U x 400 MM BOARD VME INTERFACE UCLA MEZZANINE CARD (XCV 600 E) Rice CCB OPTO 3 OPTICAL CABLES TO SECTOR PROCESSOR SER CCB INTERFACE SORTING LOGIC OPTO SER INPUT AND OUTPUT FIFO TMB_1 TMB_2 TMB_3 TMB_4 CUSTOM PERIPHERAL BACKPLANE TMB_5 TMB_6 SER TMB_7 FINISAR FTRJ-8519 -1 -2. 5 OPTICAL TRANSCEIVERS TLK 2501 SERIALIZERS TMB_8 FPGA TMB_9 SN 74 GTLP 18612 GTLP TRANSCEIVERS CPT Week, Nov 2003, B. Paul Padley, Rice University 3

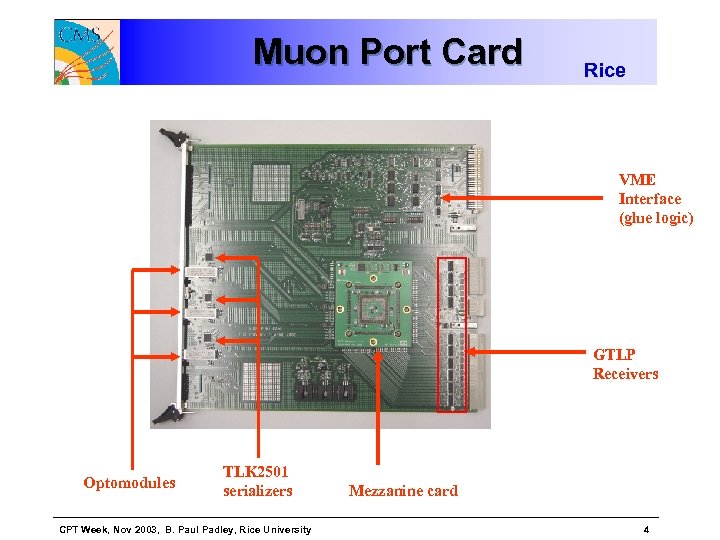

Muon Port Card Rice VME Interface (glue logic) GTLP Receivers Optomodules TLK 2501 serializers CPT Week, Nov 2003, B. Paul Padley, Rice University Mezzanine card 4

MPC Design Status Rice 3 boards were fabricated and assembled in summer 2002 Tested MPC standalone (sorter logic) and with one and two Trigger Motherboards and full-size custom backplane CPT Week, Nov 2003, B. Paul Padley, Rice University 5

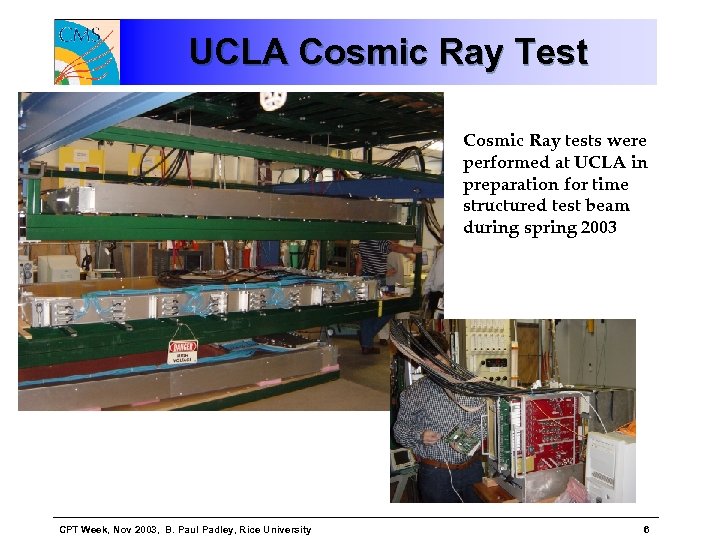

UCLA Cosmic Ray Test Cosmic Ray tests were performed at UCLA in preparation for time structured test beam during spring 2003 CPT Week, Nov 2003, B. Paul Padley, Rice University 6

Beam Test With 2 CSC’s at X 5 a / CPT Week, Nov 2003, B. Paul Padley, Rice University 7

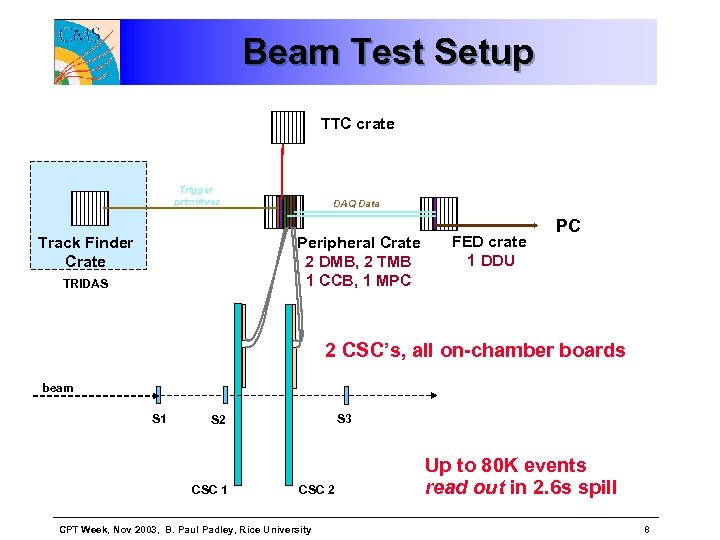

Beam Test Setup TTC crate Trigger primitives Track Finder Crate DAQ Data Peripheral Crate 2 DMB, 2 TMB 1 CCB, 1 MPC TRIDAS FED crate 1 DDU PC 2 CSC’s, all on-chamber boards beam S 1 S 3 S 2 CSC 1 CSC 2 CPT Week, Nov 2003, B. Paul Padley, Rice University Up to 80 K events read out in 2. 6 s spill 8

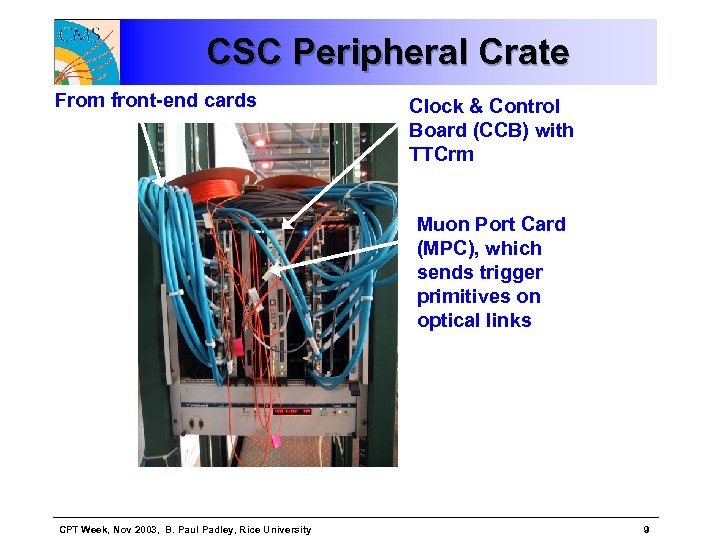

CSC Peripheral Crate From front-end cards Clock & Control Board (CCB) with TTCrm Muon Port Card (MPC), which sends trigger primitives on optical links CPT Week, Nov 2003, B. Paul Padley, Rice University 9

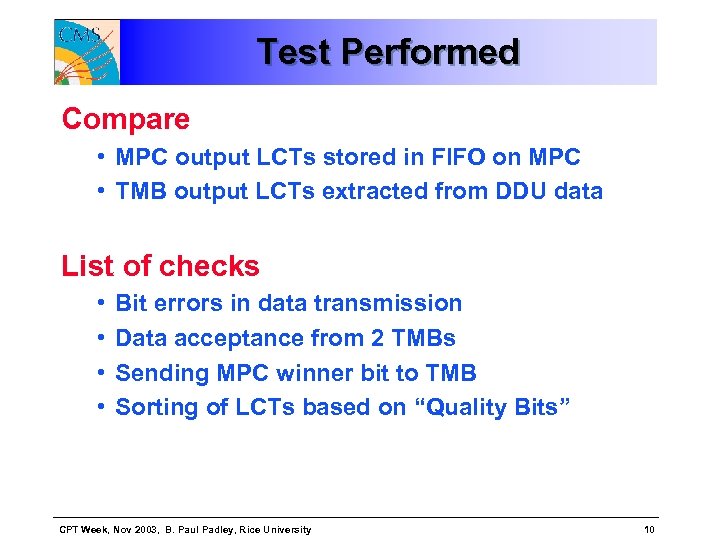

Test Performed Compare • MPC output LCTs stored in FIFO on MPC • TMB output LCTs extracted from DDU data List of checks • • Bit errors in data transmission Data acceptance from 2 TMBs Sending MPC winner bit to TMB Sorting of LCTs based on “Quality Bits” CPT Week, Nov 2003, B. Paul Padley, Rice University 10

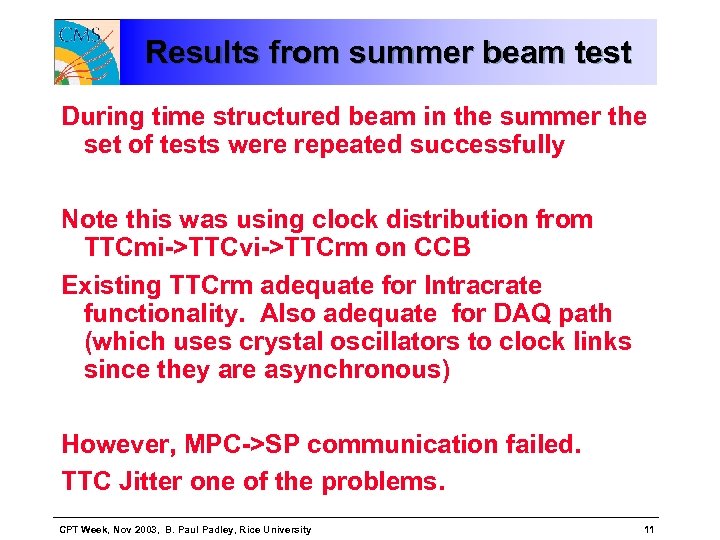

Results from summer beam test During time structured beam in the summer the set of tests were repeated successfully Note this was using clock distribution from TTCmi->TTCvi->TTCrm on CCB Existing TTCrm adequate for Intracrate functionality. Also adequate for DAQ path (which uses crystal oscillators to clock links since they are asynchronous) However, MPC->SP communication failed. TTC Jitter one of the problems. CPT Week, Nov 2003, B. Paul Padley, Rice University 11

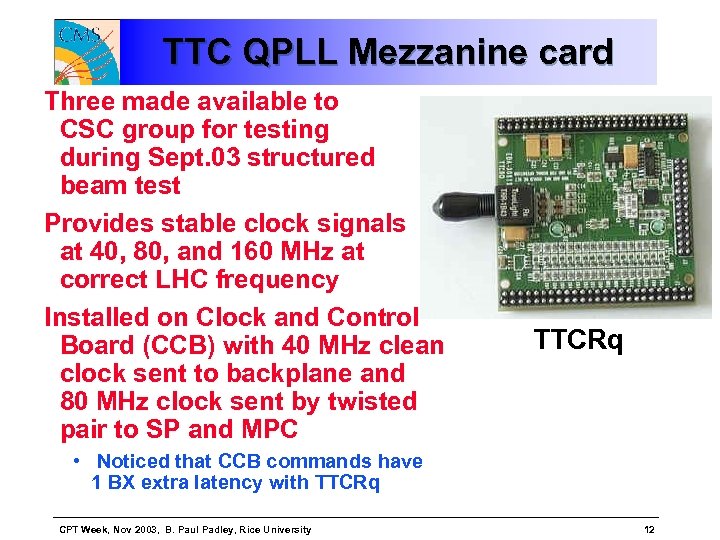

TTC QPLL Mezzanine card Three made available to CSC group for testing during Sept. 03 structured beam test Provides stable clock signals at 40, 80, and 160 MHz at correct LHC frequency Installed on Clock and Control Board (CCB) with 40 MHz clean clock sent to backplane and 80 MHz clock sent by twisted pair to SP and MPC TTCRq • Noticed that CCB commands have 1 BX extra latency with TTCRq CPT Week, Nov 2003, B. Paul Padley, Rice University 12

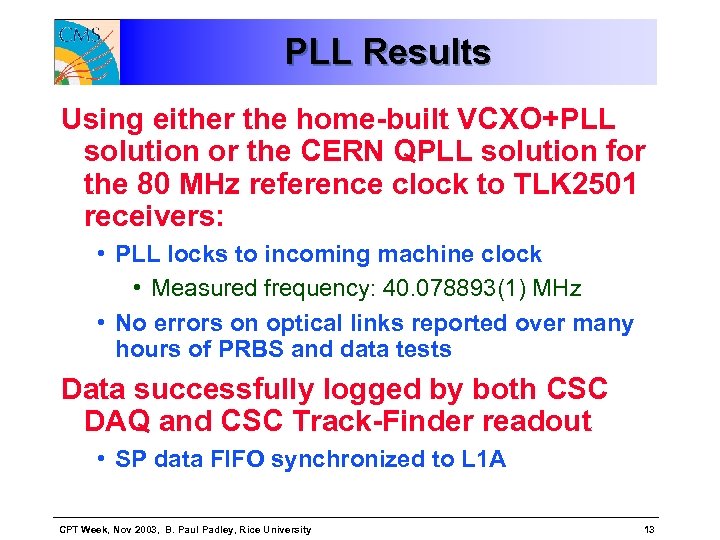

PLL Results Using either the home-built VCXO+PLL solution or the CERN QPLL solution for the 80 MHz reference clock to TLK 2501 receivers: • PLL locks to incoming machine clock • Measured frequency: 40. 078893(1) MHz • No errors on optical links reported over many hours of PRBS and data tests Data successfully logged by both CSC DAQ and CSC Track-Finder readout • SP data FIFO synchronized to L 1 A CPT Week, Nov 2003, B. Paul Padley, Rice University 13

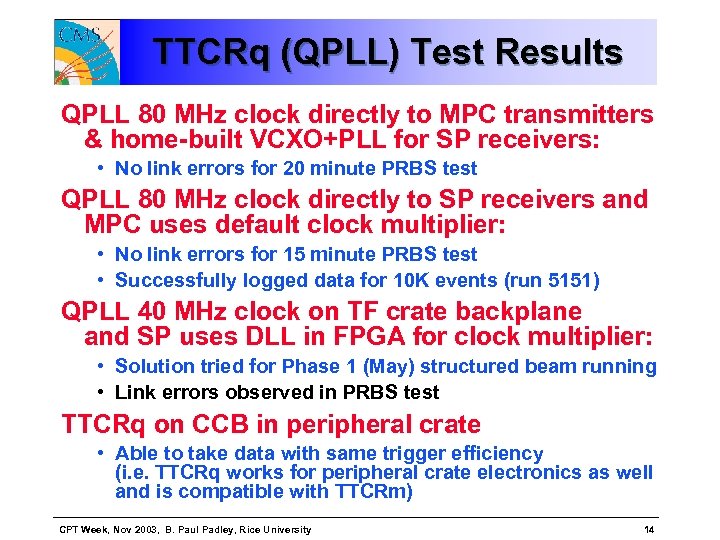

TTCRq (QPLL) Test Results QPLL 80 MHz clock directly to MPC transmitters & home-built VCXO+PLL for SP receivers: • No link errors for 20 minute PRBS test QPLL 80 MHz clock directly to SP receivers and MPC uses default clock multiplier: • No link errors for 15 minute PRBS test • Successfully logged data for 10 K events (run 5151) QPLL 40 MHz clock on TF crate backplane and SP uses DLL in FPGA for clock multiplier: • Solution tried for Phase 1 (May) structured beam running • Link errors observed in PRBS test TTCRq on CCB in peripheral crate • Able to take data with same trigger efficiency (i. e. TTCRq works for peripheral crate electronics as well and is compatible with TTCRm) CPT Week, Nov 2003, B. Paul Padley, Rice University 14

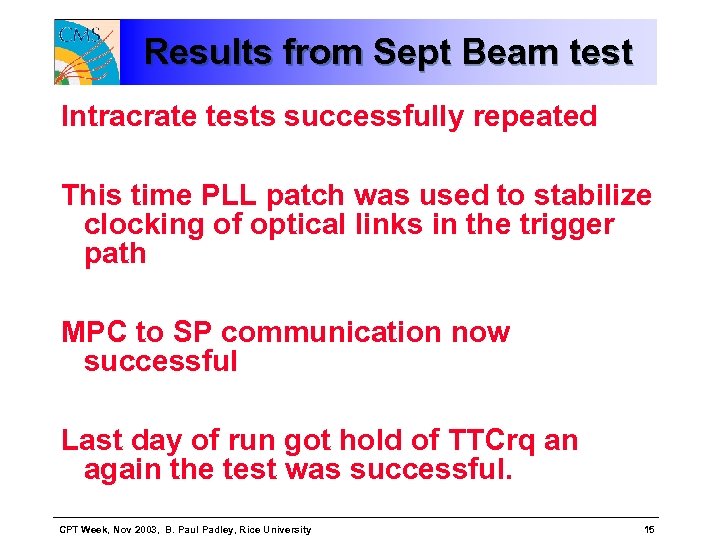

Results from Sept Beam test Intracrate tests successfully repeated This time PLL patch was used to stabilize clocking of optical links in the trigger path MPC to SP communication now successful Last day of run got hold of TTCrq an again the test was successful. CPT Week, Nov 2003, B. Paul Padley, Rice University 15

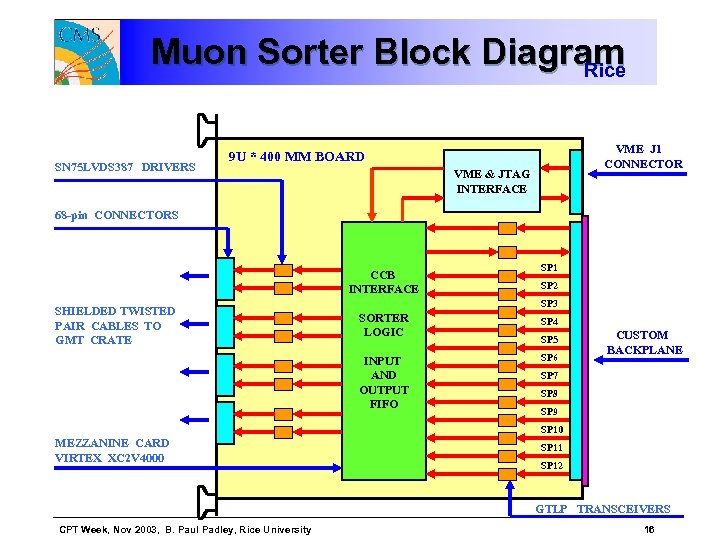

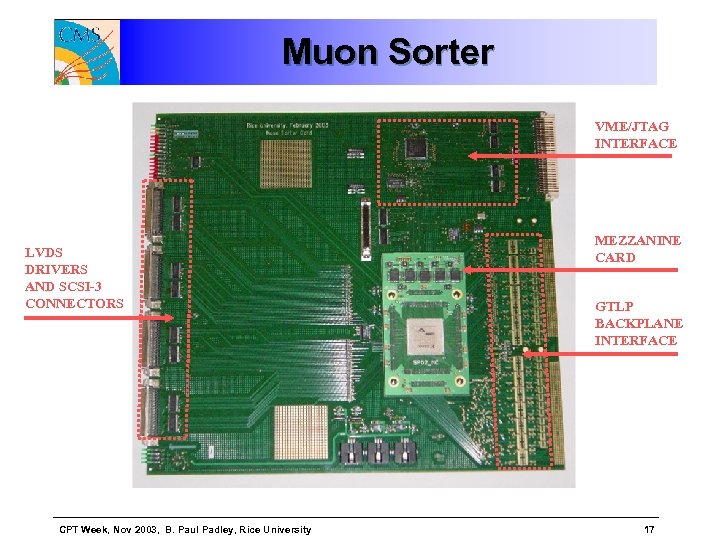

Muon Sorter Block Diagram Rice SN 75 LVDS 387 DRIVERS VME J 1 CONNECTOR 9 U * 400 MM BOARD VME & JTAG INTERFACE 68 -pin CONNECTORS CCB INTERFACE SHIELDED TWISTED PAIR CABLES TO GMT CRATE SP 1 SP 2 SP 3 SORTER LOGIC INPUT AND OUTPUT FIFO SP 4 SP 5 SP 6 CUSTOM BACKPLANE SP 7 SP 8 SP 9 SP 10 MEZZANINE CARD VIRTEX XC 2 V 4000 SP 11 SP 12 GTLP TRANSCEIVERS CPT Week, Nov 2003, B. Paul Padley, Rice University 16

Muon Sorter VME/JTAG INTERFACE LVDS DRIVERS AND SCSI-3 CONNECTORS CPT Week, Nov 2003, B. Paul Padley, Rice University MEZZANINE CARD GTLP BACKPLANE INTERFACE 17

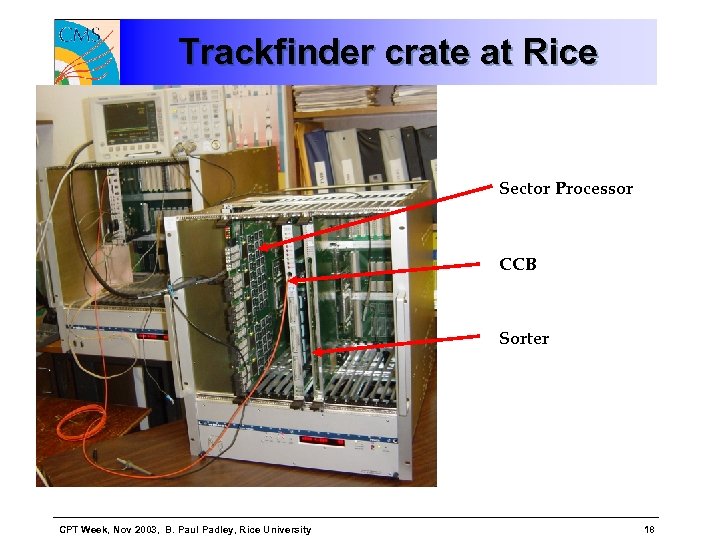

Trackfinder crate at Rice Sector Processor CCB Sorter CPT Week, Nov 2003, B. Paul Padley, Rice University 18

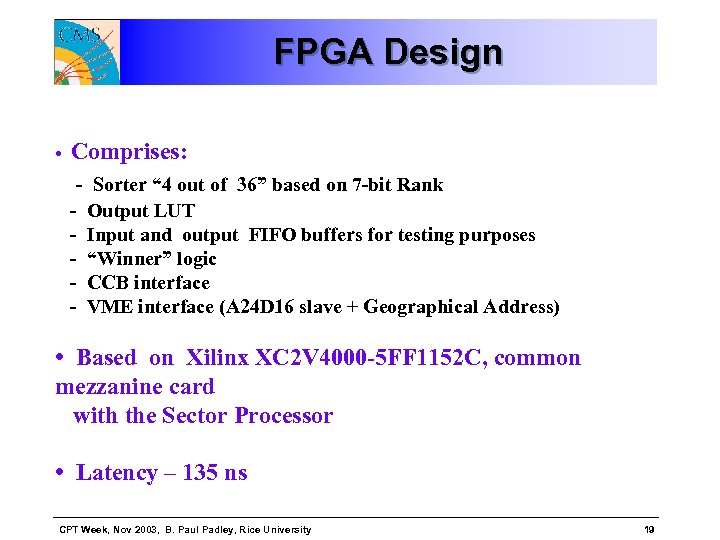

FPGA Design • Comprises: - Sorter “ 4 out of 36” based on 7 -bit Rank - Output LUT - Input and output FIFO buffers for testing purposes - “Winner” logic - CCB interface - VME interface (A 24 D 16 slave + Geographical Address) • Based on Xilinx XC 2 V 4000 -5 FF 1152 C, common mezzanine card with the Sector Processor • Latency – 135 ns CPT Week, Nov 2003, B. Paul Padley, Rice University 19

Muon Sorter Status and Plans Have 4 boards in hand, one is stuffed (except backplane interface) Have a dedicated Wiener 9 U crate with VME J 1 backplane and custom Track Finder backplane installed Sector Processor – to – MS interface test currently underway CPT Week, Nov 2003, B. Paul Padley, Rice University 20

Milestones Rice Sep-02 Prototype construction: • MPC done, • CCB done • waiting for new TTCrq, and will then redo • As a result of TTCrx Jitter problem need resdesign with TTcrq • Muon Sorter Done CPT Week, Nov 2003, B. Paul Padley, Rice University 21

More Milestones • Apr-03 Prototype testing done: Underway • Sep-03 Final designs done • MPC significantly delayed (until summer ’ 04) • Although MPC prototype was completed summer ’ 02, integration testing of it will not be completed until spring ‘ 04 • Oct-04 Production done • At risk given the final design schedule • Apr-05 Installation done CPT Week, Nov 2003, B. Paul Padley, Rice University 22

c8a54cf55176e136aaa40fe85d85a50d.ppt