b905021dbcacba509844edc1e8c08842.ppt

- Количество слайдов: 14

CS 152 b Final Report Group 6

Background Our goal was to design and implement a functional Group 6 staff 16 -bit RISC processor using the Xilinx software. The constrains on our chip design was that it must be able The R 2 -Yu 2 processor to run on a Xess board and must adhere to the Randy Grant – Technical lead Young standards specified by our primary customer Cho Enterprises out of UCLA. Robert Johnson – VHDL master Anthony (moo) Yu – Datapath guru George Yu – Software designer

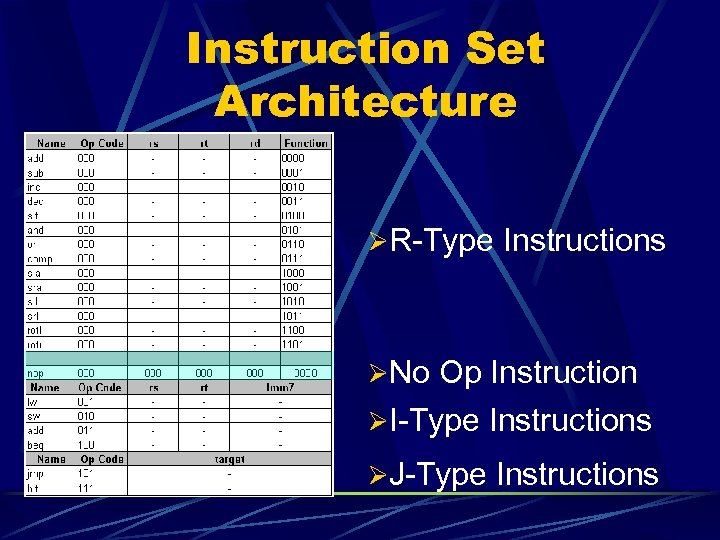

Instruction Set Architecture ØR-Type Instructions ØNo Op Instruction ØI-Type Instructions ØJ-Type Instructions

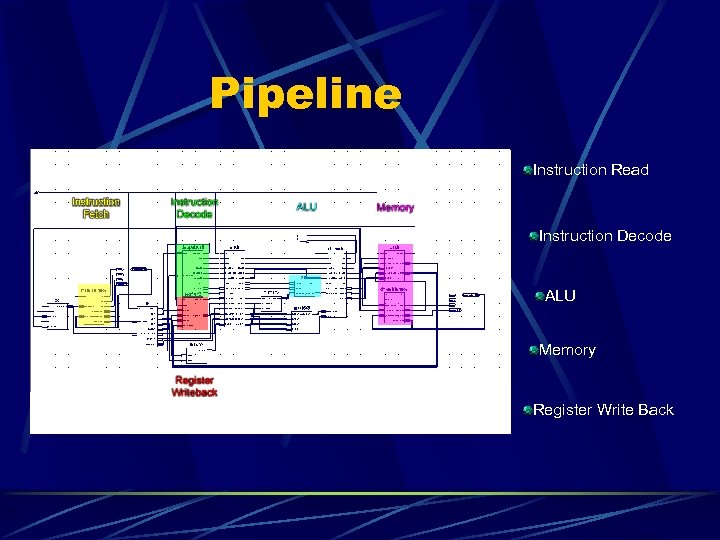

Pipeline Instruction Read Instruction Decode ALU Memory Register Write Back

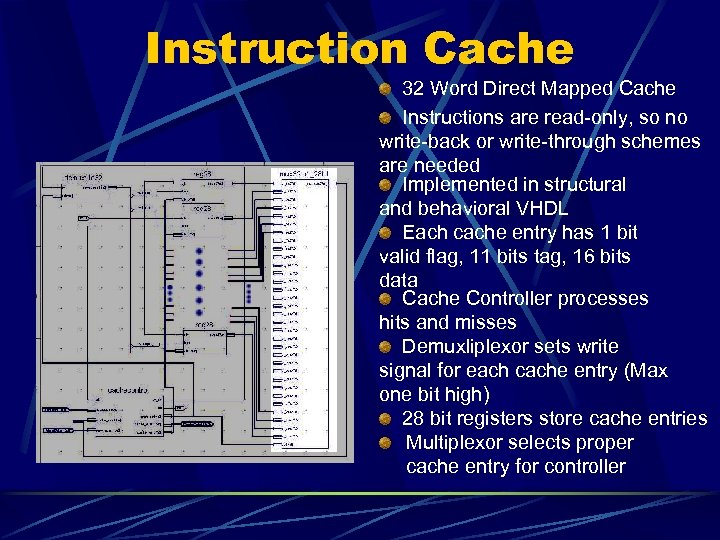

Instruction Cache 32 Word Direct Mapped Cache Instructions are read-only, so no write-back or write-through schemes are needed Implemented in structural and behavioral VHDL Each cache entry has 1 bit valid flag, 11 bits tag, 16 bits data Cache Controller processes hits and misses Demuxliplexor sets write signal for each cache entry (Max one bit high) 28 bit registers store cache entries Multiplexor selects proper cache entry for controller

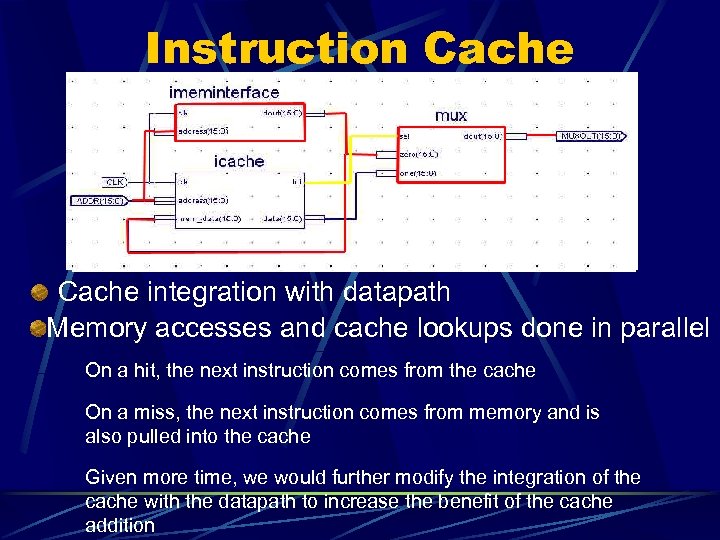

Instruction Cache integration with datapath Memory accesses and cache lookups done in parallel On a hit, the next instruction comes from the cache On a miss, the next instruction comes from memory and is also pulled into the cache Given more time, we would further modify the integration of the cache with the datapath to increase the benefit of the cache addition

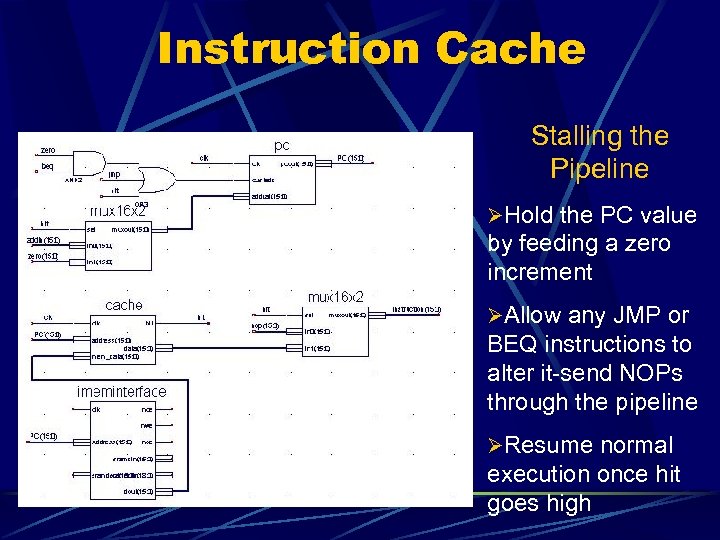

Instruction Cache Stalling the Pipeline ØHold the PC value by feeding a zero increment ØAllow any JMP or BEQ instructions to alter it-send NOPs through the pipeline ØResume normal execution once hit goes high

Typical Compiler Scanner Takes in input file and tokenizes the input Parser Transforms token stream into a grammatical phrases Code Generation Creates assembly code from the grammar Linker Turns the assembly code into the native bit code of the computer

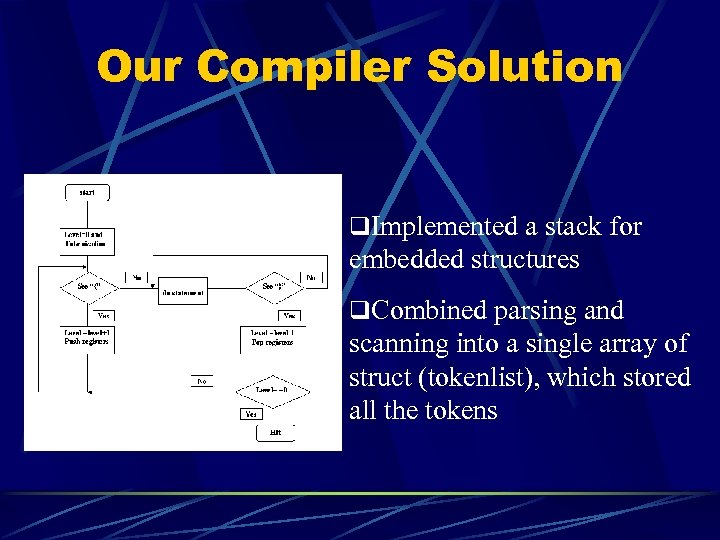

Our Compiler Solution q. Implemented a stack for embedded structures q. Combined parsing and scanning into a single array of struct (tokenlist), which stored all the tokens

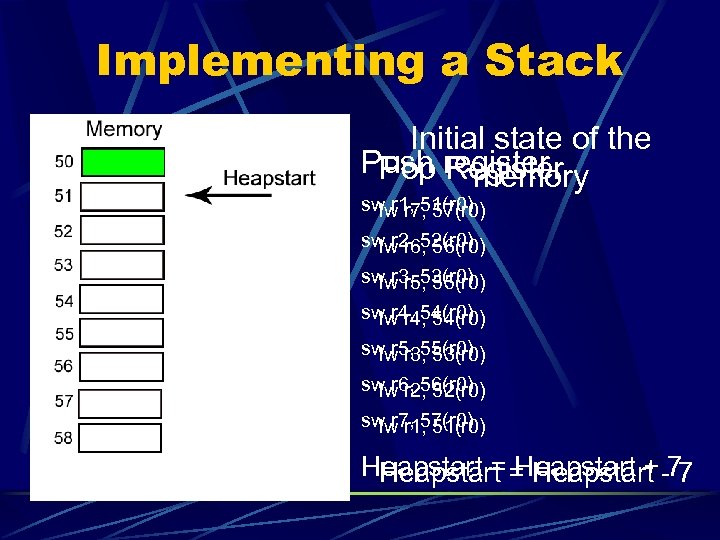

Implementing a Stack Initial state of the Push register Pop Register memory sw r 1, 51(r 0) lw r 7, 57(r 0) sw r 2, 52(r 0) lw r 6, 56(r 0) sw r 3, 53(r 0) lw r 5, 55(r 0) sw r 4, 54(r 0) lw r 4, 54(r 0) sw r 5, 55(r 0) lw r 3, 53(r 0) sw r 6, 56(r 0) lw r 2, 52(r 0) sw r 7, 57(r 0) lw r 1, 51(r 0) Heapstart = Heapstart + 7 Heapstart = Heapstart - 7

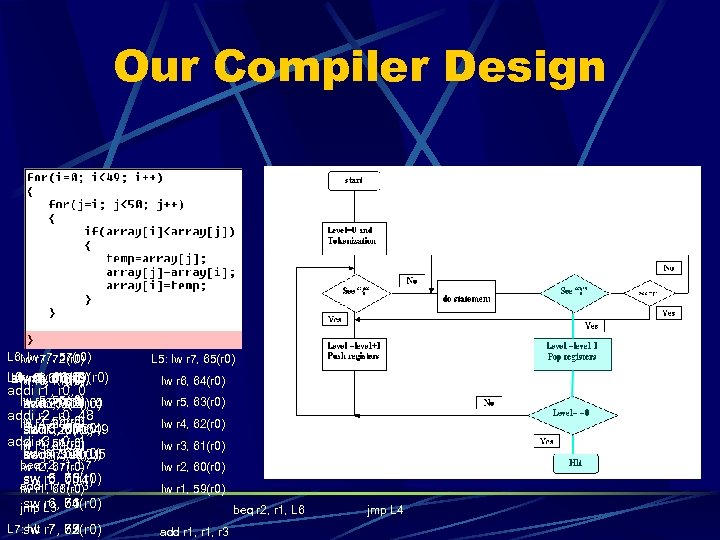

Our Compiler Design L 6: lw r 7, 57(r 0) lw r 7, 72(r 0) L 5: lw r 7, 65(r 0) lw r 6, 56(r 0) sw r 1, 66(r 0) L 4: sw r 1, 59(r 0) L 3: sw r 1, 51(r 0) sw r 5, 50(r 0) lw r 5, 0(r 3) lw r 4, 51(r 0) lw r 6, 71(r 0) lw r 6, 64(r 0) addi r 1, r 0, 0 lw r 5, 55(r 0) lw r 5, 70(r 0) sw r 2, 67(r 0) sw r 2, 60(r 0) sw r 2, 52(r 0) add r 5, r 6, r 0 lw r 6, 0(r 4) add r 1, r 0, r 4 addi r 2, r 0, 48 lw r 2, 52(r 0) lw r 4, 69(r 0) sw r 3, 68(r 0) sw r 3, 61(r 0) sw r 3, 53(r 0) sw r 5, 0(r 3) slt r 7, r 6, r 5 addi r 2, r 0, 49 addi r 3, r 0, 1 lw r 1, 51(r 0) lw r 3, 68(r 0) sw r 4, 69(r 0) sw r 4, 62(r 0) sw r 4, 54(r 0) lw r 6, 50(r 0) beq r 7, r 0, L 5 addi r 3, r 0, 1 lw r 5, 63(r 0) lw r 4, 62(r 0) lw r 3, 61(r 0) beq r 2, r 1, L 7 lw r 2, 67(r 0) lw r 2, 60(r 0) lw r 1, 66(r 0) lw r 1, 59(r 0) sw r 5, 70(r 0) sw r 5, 63(r 0) sw r 5, 55(r 0) sw r 6, 0(r 4) add r 1, r 3 sw r 6, 71(r 0) sw r 6, 64(r 0) sw r 6, 56(r 0) jmp L 3 beq r 2, r 1, L 6 L 7: hlt sw r 7, 72(r 0) sw r 7, 65(r 0) sw r 7, 57(r 0) add r 1, r 3 jmp L 4

Conclusion In Conclusion the Group 6 16 -bit RISC Processor Meets and Exceeds Design Requirements!

References ØCache Reference Computer Organization & Design The Hardware/Software Interface by Patterson & Hennessy ØVHDL Reference http: //www. ee. ucla. edu/~young/csm 152 b/vhdl_comp. pdf ØCompiler Reference http: //cs. wisc. edu/~bodik/cs 536/Notes/1. Overview. html

Thank You For viewing this presentation you qualify for Group 6’s special offer For a limited time only you can get a copy of the Group 6 processor schematic for only $999. 95 1 -800 -BUY-RISC 1 -800 -289 -7472

b905021dbcacba509844edc1e8c08842.ppt