0bdd788515885dd6f0d7c90ffc5d9d1c.ppt

- Количество слайдов: 22

CPLD Competition File Number Here

Session Objectives w Review Strengths & Weaknesses of key competitors: — Lattice — Vantis — Altera w Highlights areas to attack and win File Number Here

Competitor Profile: Vantis (AMD) w Old AMD PLD division — now a separate fabless company — dependent on AMD fabs (+ UMC for FPGA in ‘ 98) — SPLDs and CPLDs now; announced new ‘VF 1’ FPGA line w Minimal software, customer service functions — management focused only on components, not solutions — relies on AMD for process development w Dropped down to 4 rd largest PLD company — fell from 3 rd in ‘ 97 behind Lattice — dependent on declining SPLD sales File Number Here

Vantis Thrust Products w Mach 4 LV: 3. 3 V Low & Mid density ISP — 32 to 256 macrocells — speeds to 7. 5 ns (slower than 5 V devices) — good JTAG support w Mach 5 LV: 3. 3 V High-density ISP — 128 to 512 macrocells — raw speeds to 7. 5 ns, but only specific input-output paths — good JTAG support w Other products — 5 V versions of Mach 4, Mach 5 — Mach 1, 2, 3: Low density, some with ISP retrofit File Number Here

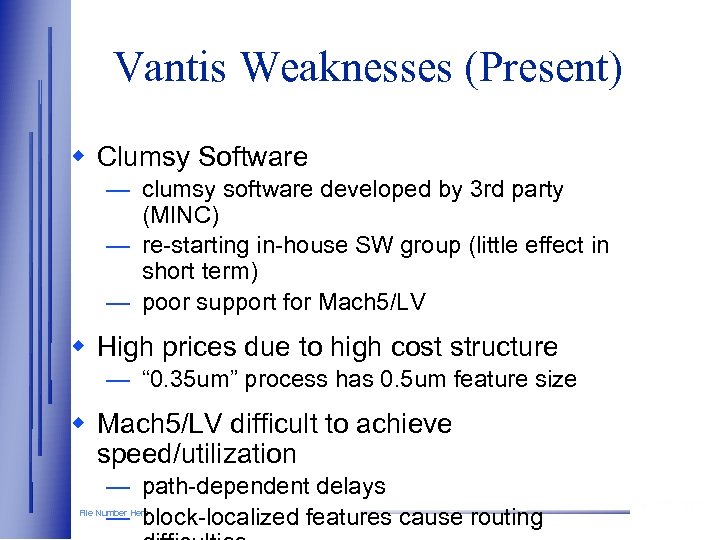

Vantis Weaknesses (Present) w Clumsy Software — clumsy software developed by 3 rd party (MINC) — re-starting in-house SW group (little effect in short term) — poor support for Mach 5/LV w High prices due to high cost structure — “ 0. 35 um” process has 0. 5 um feature size w Mach 5/LV difficult to achieve speed/utilization — path-dependent delays — block-localized features cause routing File Number Here

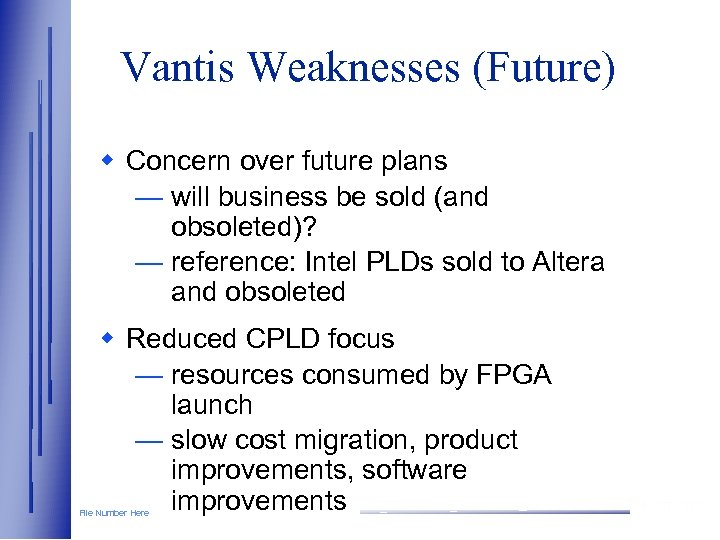

Vantis Weaknesses (Future) w Concern over future plans — will business be sold (and obsoleted)? — reference: Intel PLDs sold to Altera and obsoleted w Reduced CPLD focus — resources consumed by FPGA launch — slow cost migration, product improvements, software improvements File Number Here

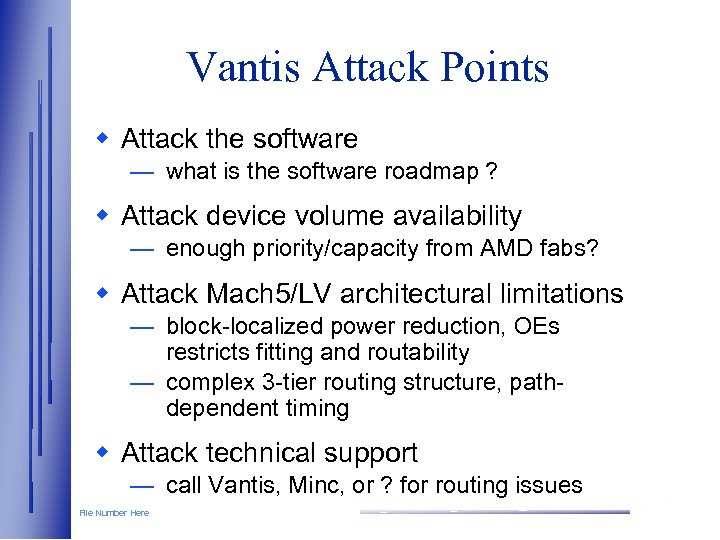

Vantis Attack Points w Attack the software — what is the software roadmap ? w Attack device volume availability — enough priority/capacity from AMD fabs? w Attack Mach 5/LV architectural limitations — block-localized power reduction, OEs restricts fitting and routability — complex 3 -tier routing structure, pathdependent timing w Attack technical support — call Vantis, Minc, or ? for routing issues File Number Here

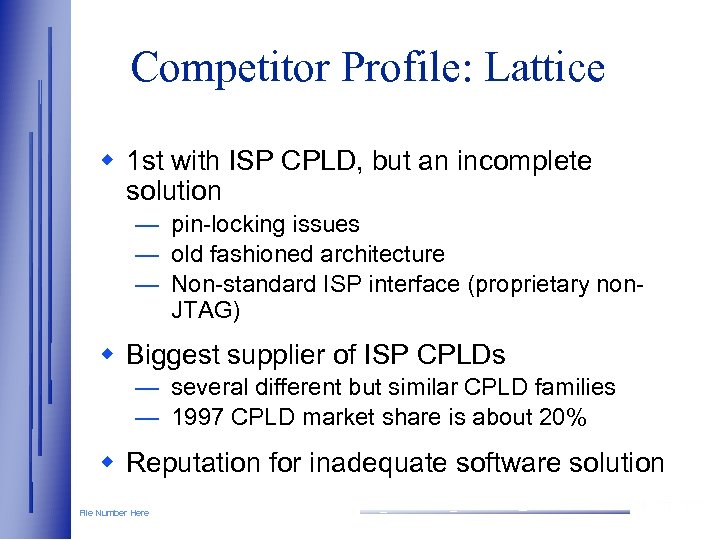

Competitor Profile: Lattice w 1 st with ISP CPLD, but an incomplete solution — pin-locking issues — old fashioned architecture — Non-standard ISP interface (proprietary non. JTAG) w Biggest supplier of ISP CPLDs — several different but similar CPLD families — 1997 CPLD market share is about 20% w Reputation for inadequate software solution File Number Here

Lattice Thrust Products w isp. LSI 2000 V: — 3. 3 v ISP (de-rated 5 V parts) — 2032 V offers no power savings over same speed 5 V 2032 — latch-up risk in mixed 3. 3 V/5 V systems — higher cost, slower speed grades than 5 V versions w isp. LSI 1000 E/2000 — 32 to 192 macrocells — improved routing, but not enough w Other products: — isp. LSI 3000: large & difficult-to-use (192 to 320 macrocells) File Number Here

Lattice Weaknesses (Present) w Software performance — hampered by the restrictive silicon architecture — ease of use issues — pin-locking issues — poor routing at high utilization w Restrictive, 6 -year old architecture — limited product-term allocation options — no individual output enables (OE) — block-localized clock signals File Number Here

Lattice Weaknesses (Future) w Proprietary, non-standard ISP interface (isp. LSI 1 K/2 K) — difficult board integration with JTAG components w Limited to CPLD devices only — against industry trend toward a single logic vendor File Number Here

Lattice Attack Points w Attack 3. 3 V IC deficiencies: — latch-up risk (requires significant design effort to compensate) — no or minimal power savings over 5 V — slower, higher price w Attack software capability — why can’t use more than 80% device utilization? w Attack EEPROM process roadmap — what is the long-term process migration path? w Lack of JTAG on lead products (isp. LSI File Number Here

Competitor Profile: Altera w Largest supplier of CPLDs — note: Flex 8 K and 10 K are not CPLDs w Company focused on IC/software technology — not focused on solutions or customer support File Number Here

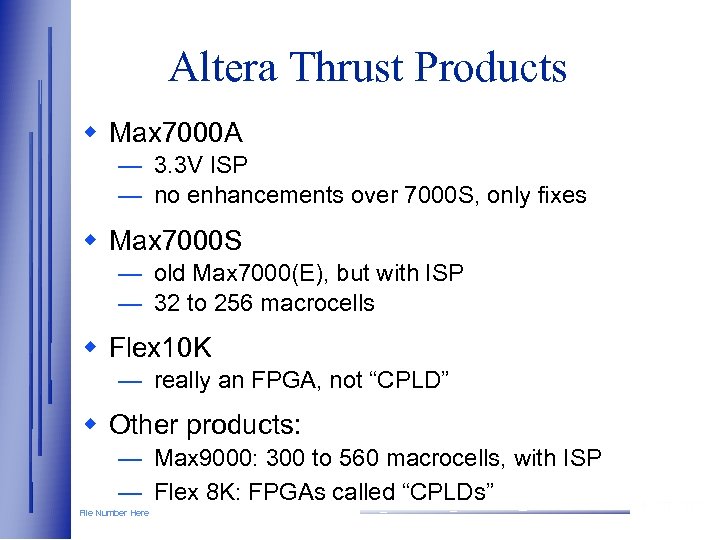

Altera Thrust Products w Max 7000 A — 3. 3 V ISP — no enhancements over 7000 S, only fixes w Max 7000 S — old Max 7000(E), but with ISP — 32 to 256 macrocells w Flex 10 K — really an FPGA, not “CPLD” w Other products: — Max 9000: 300 to 560 macrocells, with ISP — Flex 8 K: FPGAs called “CPLDs” File Number Here

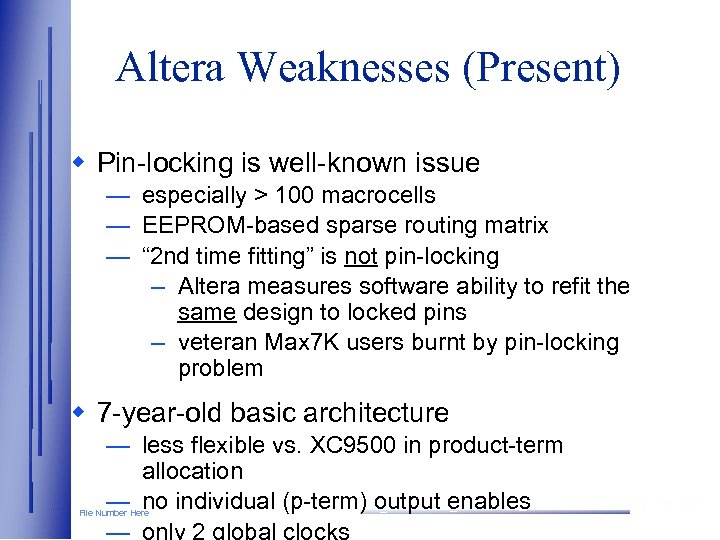

Altera Weaknesses (Present) w Pin-locking is well-known issue — especially > 100 macrocells — EEPROM-based sparse routing matrix — “ 2 nd time fitting” is not pin-locking – Altera measures software ability to refit the same design to locked pins – veteran Max 7 K users burnt by pin-locking problem w 7 -year-old basic architecture — less flexible vs. XC 9500 in product-term allocation — no individual (p-term) output enables — only 2 global clocks File Number Here

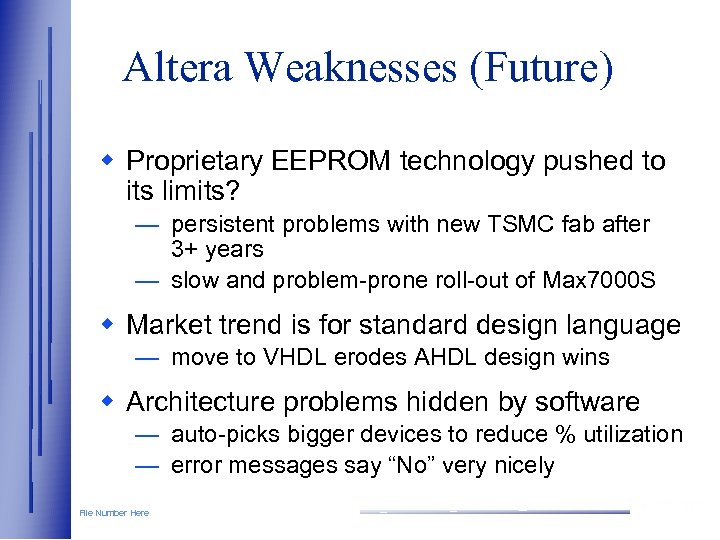

Altera Weaknesses (Future) w Proprietary EEPROM technology pushed to its limits? — persistent problems with new TSMC fab after 3+ years — slow and problem-prone roll-out of Max 7000 S w Market trend is for standard design language — move to VHDL erodes AHDL design wins w Architecture problems hidden by software — auto-picks bigger devices to reduce % utilization — error messages say “No” very nicely File Number Here

Altera Attack Points w Attack AHDL fortress — no design portability — convert AHDL designs to VHDL — sell Foundation with VHDL upgrade w Attack reliance on old architectures and processes — XC 9500 is new technology, new benefits w Attack ISP device availability, quality — sampled defective devices to customers with charge loss problems — 3 year delay on Max 7000 S family rollout — only 100 program/erase cycles, 10 year data retention File Number Here

Reference Materials File Number Here

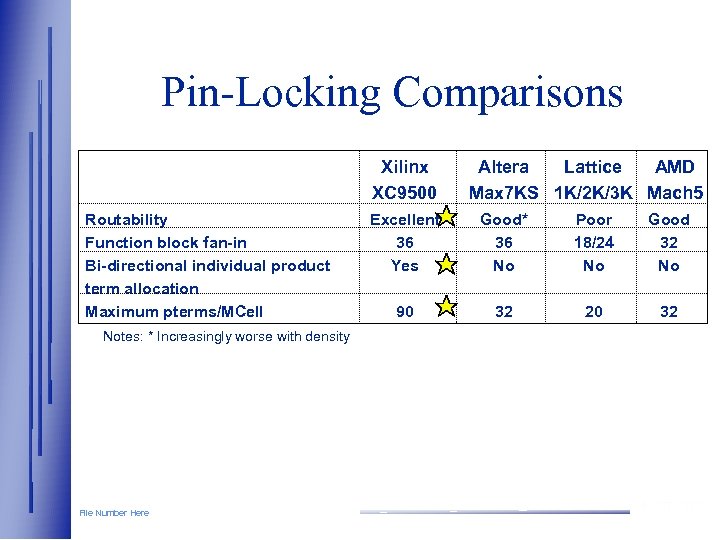

Pin-Locking Comparisons Xilinx XC 9500 Routability Function block fan-in Bi-directional individual product term allocation Maximum pterms/MCell Notes: * Increasingly worse with density File Number Here Altera Lattice AMD Max 7 KS 1 K/2 K/3 K Mach 5 Excellent 36 Yes Good* 36 No Poor 18/24 No Good 32 No 90 32 20 32

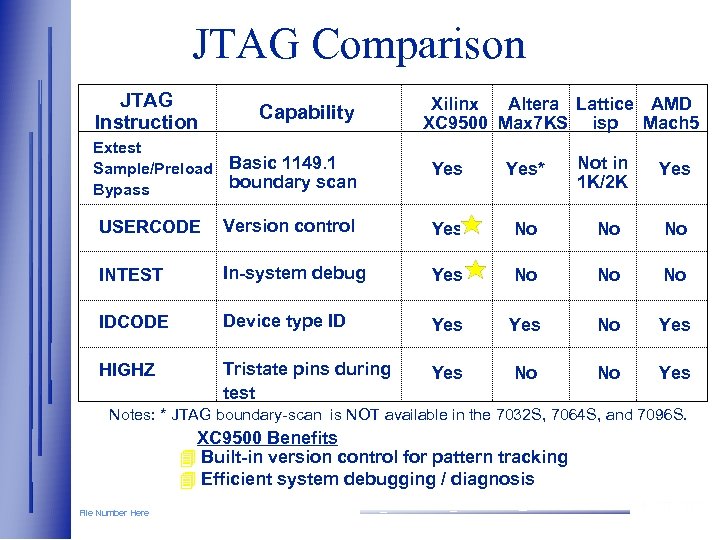

JTAG Comparison JTAG Instruction Capability Altera Lattice AMD Xilinx XC 9500 Max 7 KS isp Mach 5 Extest Sample/Preload Basic 1149. 1 boundary scan Bypass Yes* USERCODE Version control Yes No No No INTEST In-system debug Yes No No No IDCODE Device type ID Yes No Yes HIGHZ Tristate pins during test Yes No No Yes Not in 1 K/2 K Yes Notes: * JTAG boundary-scan is NOT available in the 7032 S, 7064 S, and 7096 S. XC 9500 Benefits 4 Built-in version control for pattern tracking 4 Efficient system debugging / diagnosis File Number Here

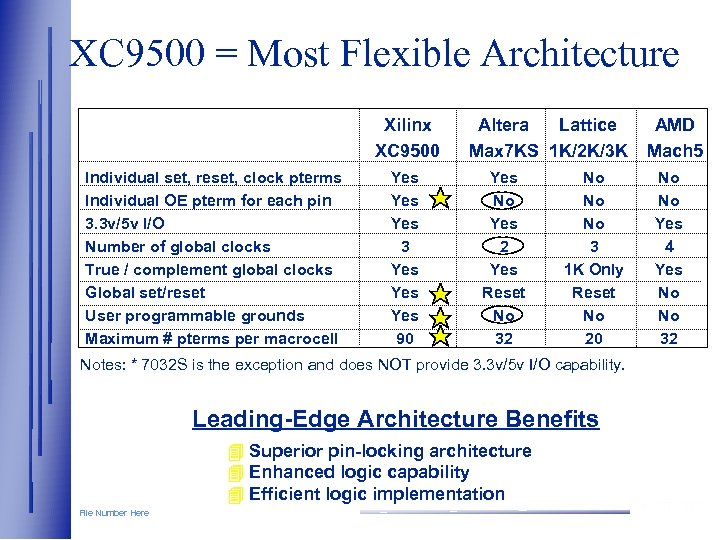

XC 9500 = Most Flexible Architecture Xilinx XC 9500 Individual set, reset, clock pterms Individual OE pterm for each pin 3. 3 v/5 v I/O Number of global clocks True / complement global clocks Global set/reset User programmable grounds Maximum # pterms per macrocell Yes Yes 3 Yes Yes 90 Altera Lattice Max 7 KS 1 K/2 K/3 K Yes No Yes 2 Yes Reset No 32 No No No 3 1 K Only Reset No 20 Notes: * 7032 S is the exception and does NOT provide 3. 3 v/5 v I/O capability. Leading-Edge Architecture Benefits 4 Superior pin-locking architecture 4 Enhanced logic capability 4 Efficient logic implementation File Number Here AMD Mach 5 No No Yes 4 Yes No No 32

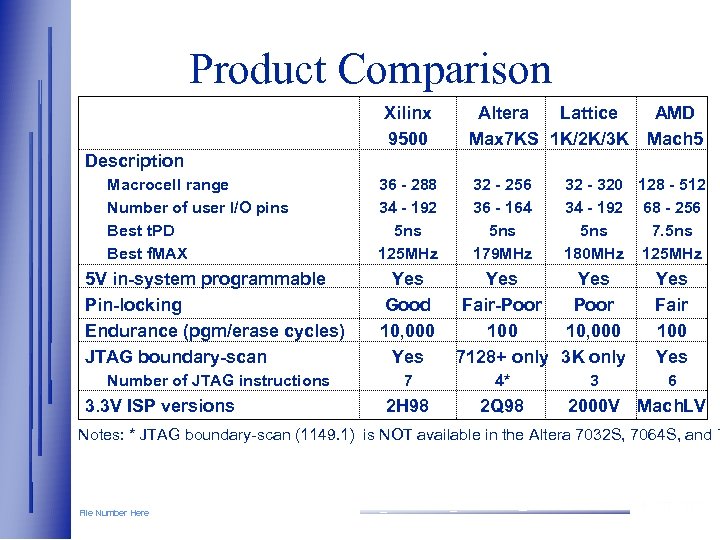

Product Comparison Xilinx 9500 Altera Lattice Max 7 KS 1 K/2 K/3 K AMD Mach 5 Description Macrocell range Number of user I/O pins Best t. PD Best f. MAX 36 - 288 34 - 192 5 ns 125 MHz 32 - 256 36 - 164 5 ns 179 MHz 5 V in-system programmable Pin-locking Endurance (pgm/erase cycles) JTAG boundary-scan Yes Good 10, 000 Yes Number of JTAG instructions 7 4* 2 H 98 2 Q 98 3. 3 V ISP versions 32 - 320 128 - 512 34 - 192 68 - 256 5 ns 7. 5 ns 180 MHz 125 MHz Yes Fair-Poor 100 10, 000 7128+ only 3 K only 3 Yes Fair 100 Yes 6 2000 V Mach. LV Notes: * JTAG boundary-scan (1149. 1) is NOT available in the Altera 7032 S, 7064 S, and 7 File Number Here

0bdd788515885dd6f0d7c90ffc5d9d1c.ppt