7af0ce61c31d280f6ac59a3513b2cee1.ppt

- Количество слайдов: 47

COSC 4 P 13 Operating Systems : Design and Implementation

COSC 4 P 13 Operating Systems : Design and Implementation

Course Description(1) u The Goals for this course u Understand UNIX u Understand Operating Systems u Prerequisites: u COSC 2 P 13 : Introduction to Operating Systems u COSC 2 P 91 : Procedural Programming u COSC 1 P 12 : Computer Organization and Assembly Language

Course Description(1) u The Goals for this course u Understand UNIX u Understand Operating Systems u Prerequisites: u COSC 2 P 13 : Introduction to Operating Systems u COSC 2 P 91 : Procedural Programming u COSC 1 P 12 : Computer Organization and Assembly Language

Course Description(2) u An intensive study of computer operating system design u Multiprogramming u Time-sharing u Real-time processing u Job and task control u Synchronization of concurrent processes and processors u Resource scheduling u Protection u Management of hierarchical storage.

Course Description(2) u An intensive study of computer operating system design u Multiprogramming u Time-sharing u Real-time processing u Job and task control u Synchronization of concurrent processes and processors u Resource scheduling u Protection u Management of hierarchical storage.

How to study this course u Read and remember u Read the book, remember the concepts and commands u Think operating systems as natural administrative agents u Practice u Coding with UNIX, use and understand of UNIX commands and get the results

How to study this course u Read and remember u Read the book, remember the concepts and commands u Think operating systems as natural administrative agents u Practice u Coding with UNIX, use and understand of UNIX commands and get the results

The Textbook Used u Uresh Vahalia, UNIX Internals: The New Frontiers, Prentice Hall, 1996 u Why we use this book? u UNIX is one of the popular operating systems of the world. u If you understand UNIX, you can understand other operating systems.

The Textbook Used u Uresh Vahalia, UNIX Internals: The New Frontiers, Prentice Hall, 1996 u Why we use this book? u UNIX is one of the popular operating systems of the world. u If you understand UNIX, you can understand other operating systems.

References u William Stallings, Operating Systems, 4 th Ed. , Prentice Hall, 2000 u A. Tanenbaum, Modern Operating Systems, 2 nd ed. Prentice Hall 2001 u Kay A. Robbins and Steven Robbins, Practical UNIX Programming, Prentice Hall, 1996 u W. R. Stevens, Advanced Programming in the UNIX Environment, Addison Wesley, 1992

References u William Stallings, Operating Systems, 4 th Ed. , Prentice Hall, 2000 u A. Tanenbaum, Modern Operating Systems, 2 nd ed. Prentice Hall 2001 u Kay A. Robbins and Steven Robbins, Practical UNIX Programming, Prentice Hall, 1996 u W. R. Stevens, Advanced Programming in the UNIX Environment, Addison Wesley, 1992

Operating System Overview u u u Computer System Computer Hardware u Components u Registers u Instruction execution u Interrupt u Memory Hierarchy and I/O Operating System u Services of OS u Major Achievements u Characteristics of Modern OS

Operating System Overview u u u Computer System Computer Hardware u Components u Registers u Instruction execution u Interrupt u Memory Hierarchy and I/O Operating System u Services of OS u Major Achievements u Characteristics of Modern OS

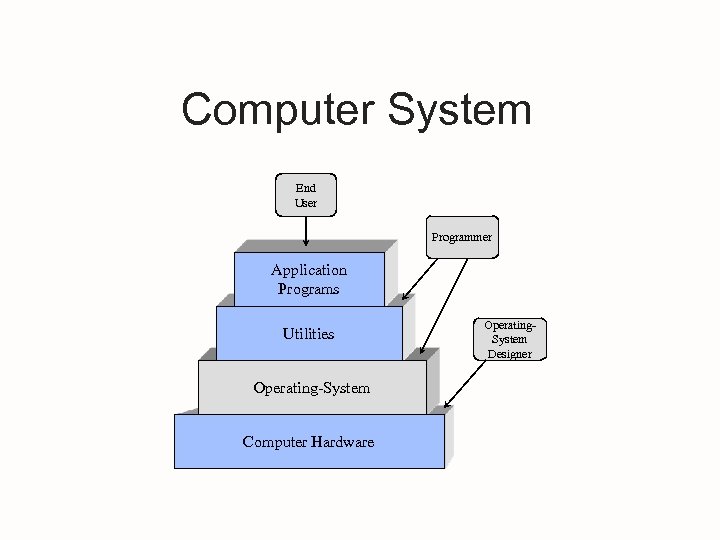

Computer System End User Programmer Application Programs Utilities Operating-System Computer Hardware Operating. System Designer

Computer System End User Programmer Application Programs Utilities Operating-System Computer Hardware Operating. System Designer

Computer Hardware u u Processor Main Memory u referred to as real memory or primary memory u volatile I/O modules u secondary memory devices u communications equipment u terminals System interconnection u communication among processors, memory, and I/O modules

Computer Hardware u u Processor Main Memory u referred to as real memory or primary memory u volatile I/O modules u secondary memory devices u communications equipment u terminals System interconnection u communication among processors, memory, and I/O modules

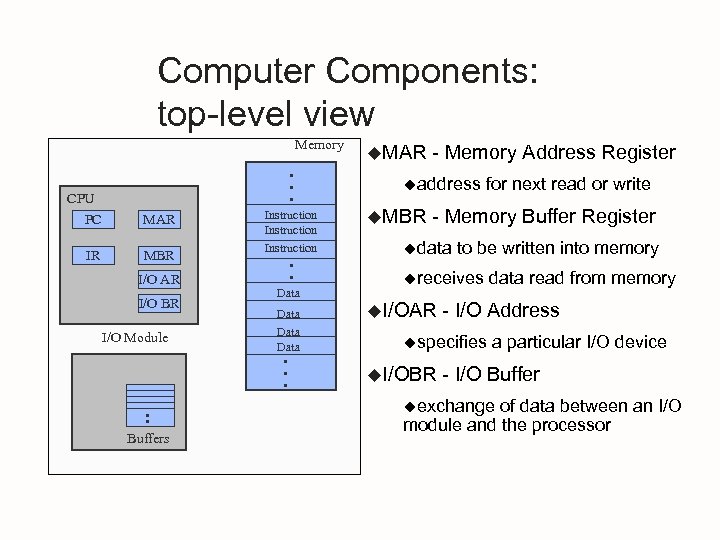

Computer Components: top-level view Memory . . . CPU PC MAR IR MBR I/O AR I/O BR I/O Module . . Buffers Instruction . . Data . . . u. MAR - Memory Address Register uaddress u. MBR for next read or write - Memory Buffer Register udata to be written into memory ureceives u. I/OAR - I/O Address uspecifies u. I/OBR data read from memory a particular I/O device - I/O Buffer uexchange of data between an I/O module and the processor

Computer Components: top-level view Memory . . . CPU PC MAR IR MBR I/O AR I/O BR I/O Module . . Buffers Instruction . . Data . . . u. MAR - Memory Address Register uaddress u. MBR for next read or write - Memory Buffer Register udata to be written into memory ureceives u. I/OAR - I/O Address uspecifies u. I/OBR data read from memory a particular I/O device - I/O Buffer uexchange of data between an I/O module and the processor

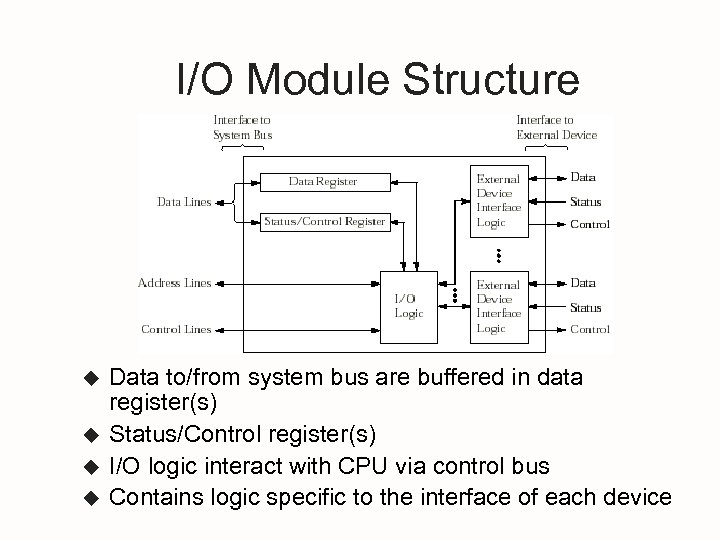

I/O Module Structure u u Data to/from system bus are buffered in data register(s) Status/Control register(s) I/O logic interact with CPU via control bus Contains logic specific to the interface of each device

I/O Module Structure u u Data to/from system bus are buffered in data register(s) Status/Control register(s) I/O logic interact with CPU via control bus Contains logic specific to the interface of each device

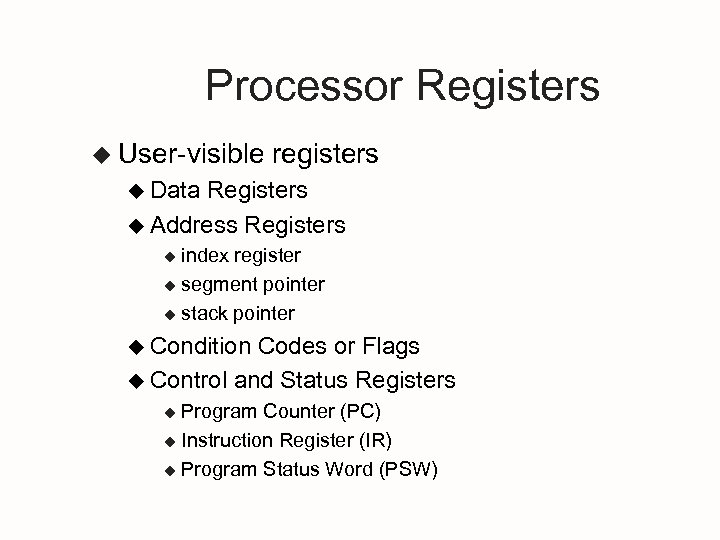

Processor Registers u User-visible registers u Data Registers u Address Registers index register u segment pointer u stack pointer u u Condition Codes or Flags u Control and Status Registers Program Counter (PC) u Instruction Register (IR) u Program Status Word (PSW) u

Processor Registers u User-visible registers u Data Registers u Address Registers index register u segment pointer u stack pointer u u Condition Codes or Flags u Control and Status Registers Program Counter (PC) u Instruction Register (IR) u Program Status Word (PSW) u

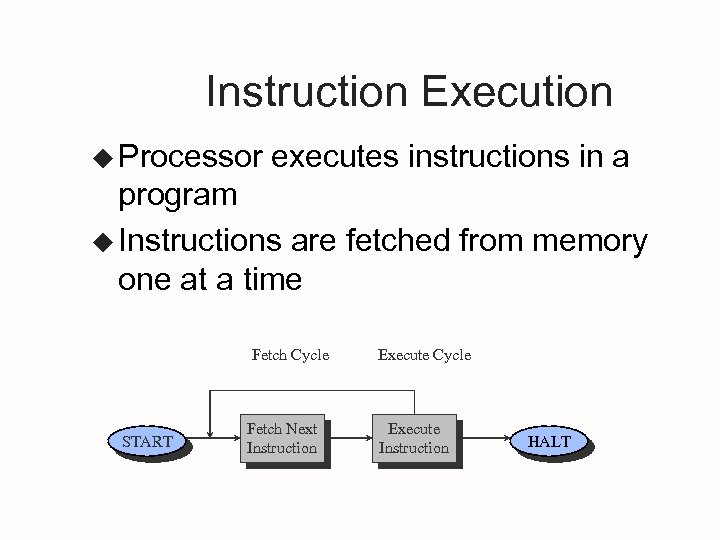

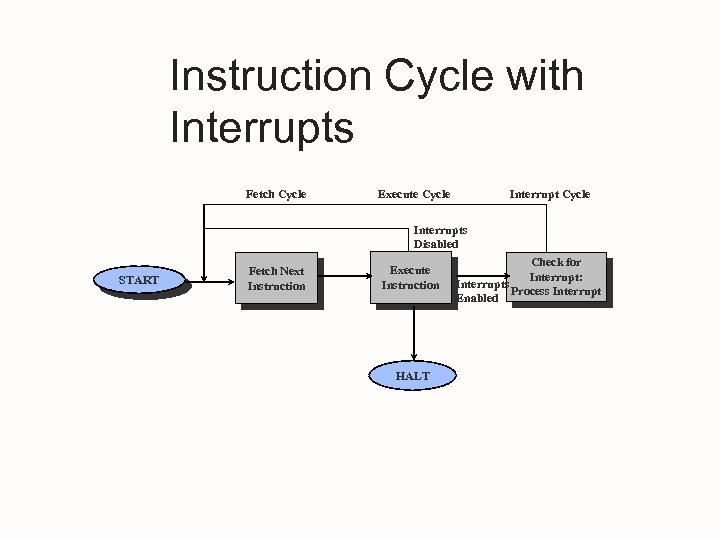

Instruction Execution u Processor executes instructions in a program u Instructions are fetched from memory one at a time Fetch Cycle START Fetch Next Instruction Execute Cycle Execute Instruction HALT

Instruction Execution u Processor executes instructions in a program u Instructions are fetched from memory one at a time Fetch Cycle START Fetch Next Instruction Execute Cycle Execute Instruction HALT

Instruction Fetch and Execute u The processor fetches the instruction from memory u Program counter (PC) holds address of the instruction to be fetched next u Program counter is incremented after each fetch

Instruction Fetch and Execute u The processor fetches the instruction from memory u Program counter (PC) holds address of the instruction to be fetched next u Program counter is incremented after each fetch

Instruction Register u Fetched instruction is placed here u Types of instructions u Processor-memory u transfer data between processor and memory u Processor-I/O u data transferred to or from a peripheral device u Data u processing arithmetic or logic operation on data u Control u alter sequence of execution

Instruction Register u Fetched instruction is placed here u Types of instructions u Processor-memory u transfer data between processor and memory u Processor-I/O u data transferred to or from a peripheral device u Data u processing arithmetic or logic operation on data u Control u alter sequence of execution

Interrupts u An interruption of the normal processing of processor u Improves processing efficiency u Allows the processor to execute other instructions while an I/O operation is in progress u A suspension of a process caused by an event external to that process and performed in such a way that the process can be resumed

Interrupts u An interruption of the normal processing of processor u Improves processing efficiency u Allows the processor to execute other instructions while an I/O operation is in progress u A suspension of a process caused by an event external to that process and performed in such a way that the process can be resumed

Classes of Interrupts u Program u arithmetic overflow u division by zero u execute illegal instruction u reference outside user’s memory space u Timer u I/O u Hardware failure

Classes of Interrupts u Program u arithmetic overflow u division by zero u execute illegal instruction u reference outside user’s memory space u Timer u I/O u Hardware failure

Instruction Cycle with Interrupts Fetch Cycle Execute Cycle Interrupts Disabled START Fetch Next Instruction Execute Instruction HALT Check for Interrupt: Interrupts Process Interrupt Enabled

Instruction Cycle with Interrupts Fetch Cycle Execute Cycle Interrupts Disabled START Fetch Next Instruction Execute Instruction HALT Check for Interrupt: Interrupts Process Interrupt Enabled

Interrupt Handler u. A program that determines nature of the interrupt and performs whatever actions are needed u Control is transferred to this program u Generally part of the operating system

Interrupt Handler u. A program that determines nature of the interrupt and performs whatever actions are needed u Control is transferred to this program u Generally part of the operating system

Interrupt Cycle u Processor checks for interrupts u If no interrupts fetch the next instruction for the current program u If an interrupt is pending, suspend execution of the current program, and execute the interrupt handler

Interrupt Cycle u Processor checks for interrupts u If no interrupts fetch the next instruction for the current program u If an interrupt is pending, suspend execution of the current program, and execute the interrupt handler

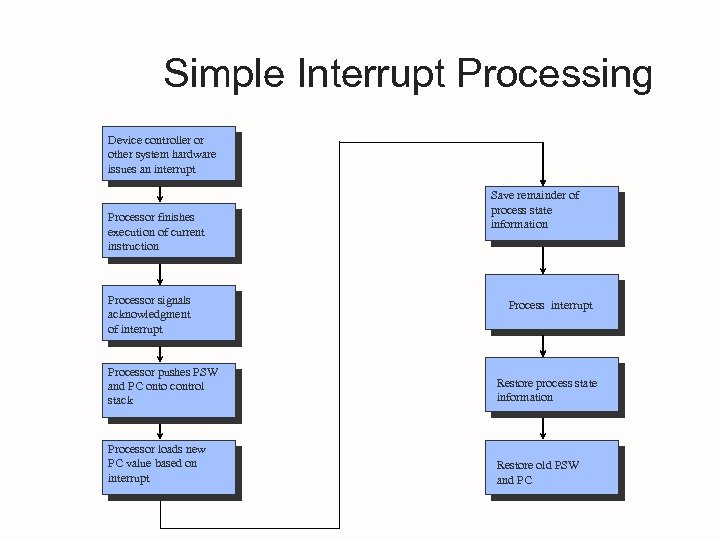

Simple Interrupt Processing Device controller or other system hardware issues an interrupt Processor finishes execution of current instruction Processor signals acknowledgment of interrupt Save remainder of process state information Process interrupt Processor pushes PSW and PC onto control stack Restore process state information Processor loads new PC value based on interrupt Restore old PSW and PC

Simple Interrupt Processing Device controller or other system hardware issues an interrupt Processor finishes execution of current instruction Processor signals acknowledgment of interrupt Save remainder of process state information Process interrupt Processor pushes PSW and PC onto control stack Restore process state information Processor loads new PC value based on interrupt Restore old PSW and PC

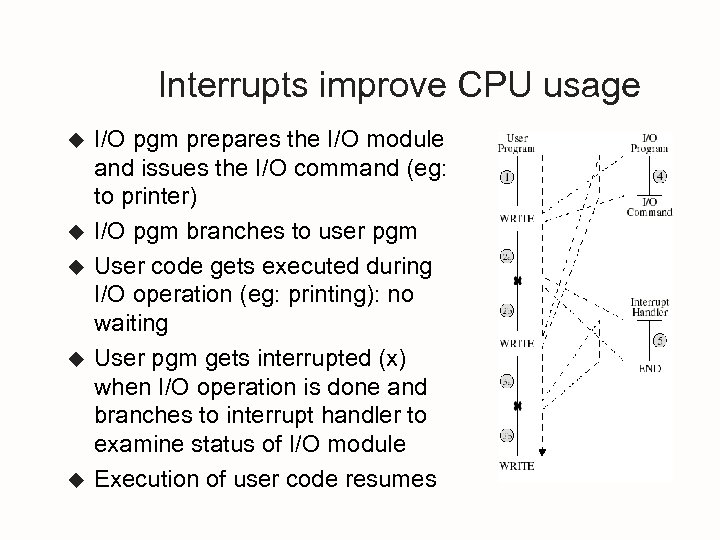

Interrupts improve CPU usage u u u I/O pgm prepares the I/O module and issues the I/O command (eg: to printer) I/O pgm branches to user pgm User code gets executed during I/O operation (eg: printing): no waiting User pgm gets interrupted (x) when I/O operation is done and branches to interrupt handler to examine status of I/O module Execution of user code resumes

Interrupts improve CPU usage u u u I/O pgm prepares the I/O module and issues the I/O command (eg: to printer) I/O pgm branches to user pgm User code gets executed during I/O operation (eg: printing): no waiting User pgm gets interrupted (x) when I/O operation is done and branches to interrupt handler to examine status of I/O module Execution of user code resumes

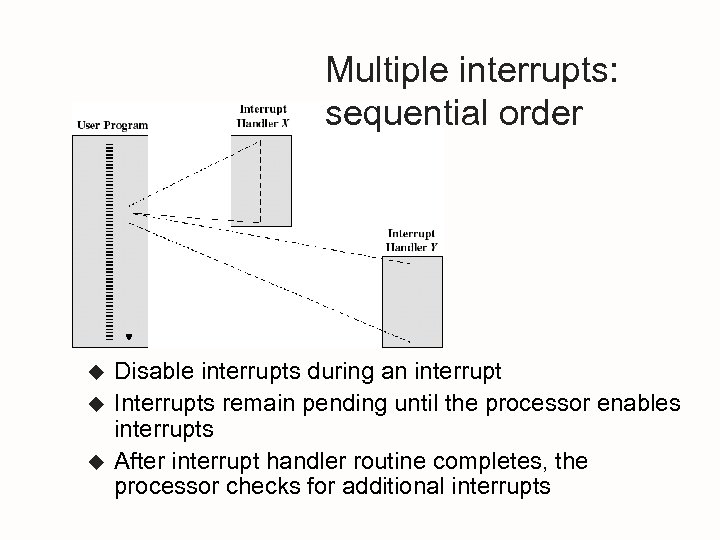

Multiple interrupts: sequential order u u u Disable interrupts during an interrupt Interrupts remain pending until the processor enables interrupts After interrupt handler routine completes, the processor checks for additional interrupts

Multiple interrupts: sequential order u u u Disable interrupts during an interrupt Interrupts remain pending until the processor enables interrupts After interrupt handler routine completes, the processor checks for additional interrupts

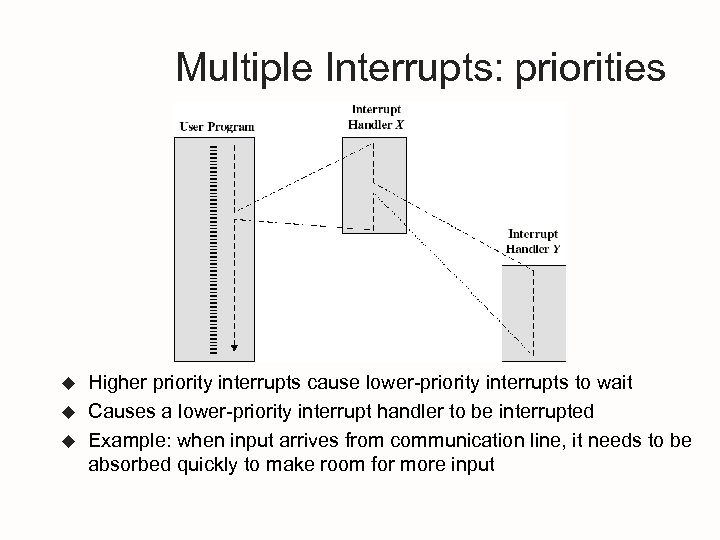

Multiple Interrupts: priorities u u u Higher priority interrupts cause lower-priority interrupts to wait Causes a lower-priority interrupt handler to be interrupted Example: when input arrives from communication line, it needs to be absorbed quickly to make room for more input

Multiple Interrupts: priorities u u u Higher priority interrupts cause lower-priority interrupts to wait Causes a lower-priority interrupt handler to be interrupted Example: when input arrives from communication line, it needs to be absorbed quickly to make room for more input

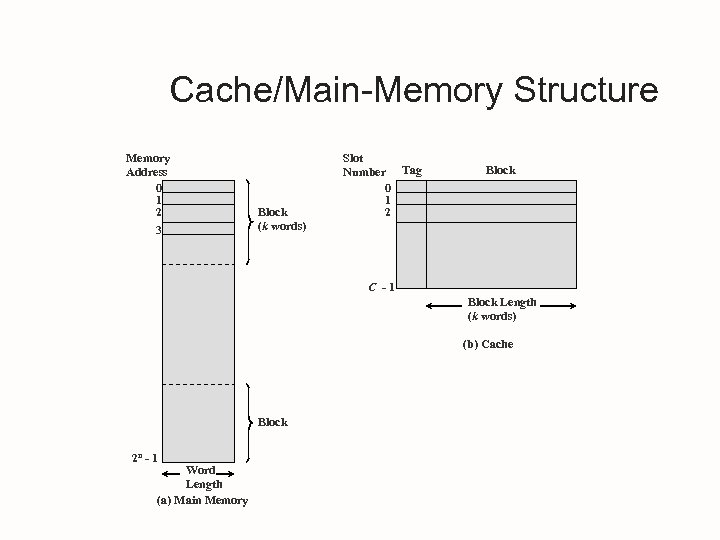

Cache/Main-Memory Structure Memory Address 0 1 2 3 Block (k words) Slot Number Tag 0 1 2 Block C -1 Block Length (k words) (b) Cache Block 2 n - 1 Word Length (a) Main Memory

Cache/Main-Memory Structure Memory Address 0 1 2 3 Block (k words) Slot Number Tag 0 1 2 Block C -1 Block Length (k words) (b) Cache Block 2 n - 1 Word Length (a) Main Memory

Cache Design u Cache size u Block size u Mapping function u Replacement algorithm

Cache Design u Cache size u Block size u Mapping function u Replacement algorithm

I/O Techniques u Programmed I/O u Interrupt-Driven I/O u Direct Memory Access

I/O Techniques u Programmed I/O u Interrupt-Driven I/O u Direct Memory Access

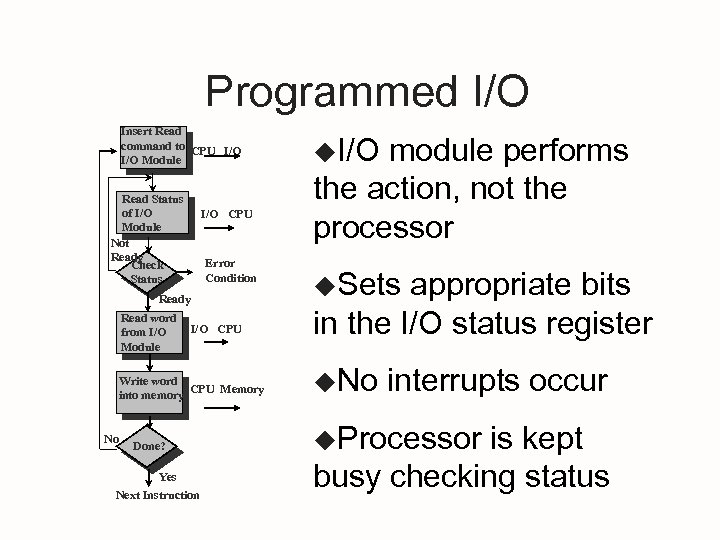

Programmed I/O Insert Read command to CPU I/O Module Read Status of I/O Module Not Ready Check Status I/O CPU Error Condition Ready Read word from I/O Module I/O CPU Write word CPU Memory into memory No Done? Yes Next Instruction u. I/O module performs the action, not the processor u. Sets appropriate bits in the I/O status register u. No interrupts occur u. Processor is kept busy checking status

Programmed I/O Insert Read command to CPU I/O Module Read Status of I/O Module Not Ready Check Status I/O CPU Error Condition Ready Read word from I/O Module I/O CPU Write word CPU Memory into memory No Done? Yes Next Instruction u. I/O module performs the action, not the processor u. Sets appropriate bits in the I/O status register u. No interrupts occur u. Processor is kept busy checking status

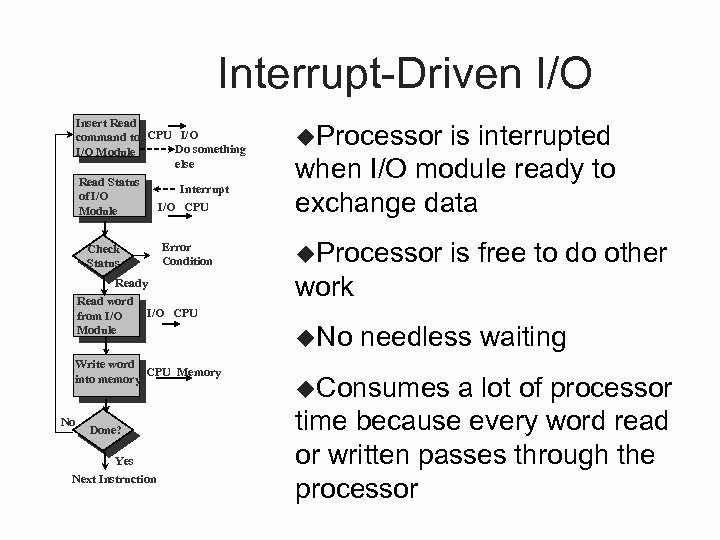

Interrupt-Driven I/O Insert Read command to CPU I/O Do something I/O Module else Read Status of I/O Module Interrupt I/O CPU Error Condition Check Status Ready Read word from I/O Module is interrupted when I/O module ready to exchange data u. Processor is free to do other work I/O CPU Write word CPU Memory into memory No u. Processor Done? Yes Next Instruction u. No needless waiting u. Consumes a lot of processor time because every word read or written passes through the processor

Interrupt-Driven I/O Insert Read command to CPU I/O Do something I/O Module else Read Status of I/O Module Interrupt I/O CPU Error Condition Check Status Ready Read word from I/O Module is interrupted when I/O module ready to exchange data u. Processor is free to do other work I/O CPU Write word CPU Memory into memory No u. Processor Done? Yes Next Instruction u. No needless waiting u. Consumes a lot of processor time because every word read or written passes through the processor

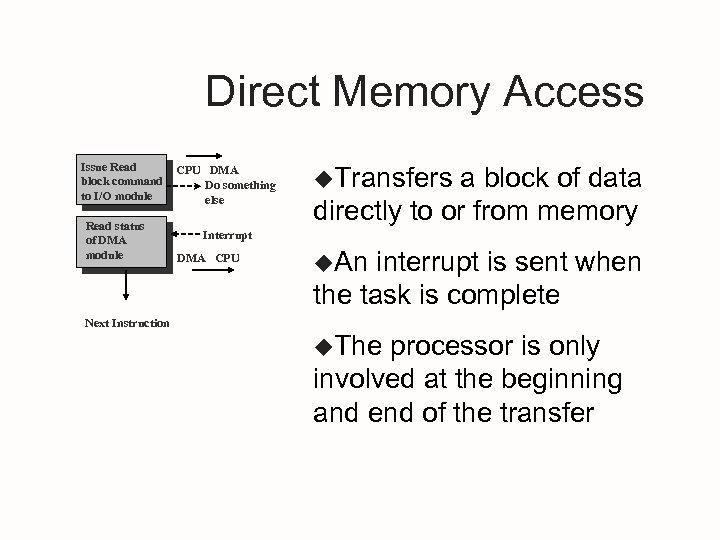

Direct Memory Access Issue Read block command to I/O module Read status of DMA module Next Instruction CPU DMA Do something else u. Transfers a block of data directly to or from memory Interrupt DMA CPU u. An interrupt is sent when the task is complete u. The processor is only involved at the beginning and end of the transfer

Direct Memory Access Issue Read block command to I/O module Read status of DMA module Next Instruction CPU DMA Do something else u. Transfers a block of data directly to or from memory Interrupt DMA CPU u. An interrupt is sent when the task is complete u. The processor is only involved at the beginning and end of the transfer

Operating System u Making computing power available to users by controlling the hardware u a program that controls execution of application programs u an interface between the user and hardware u Directs the processor in the use of system resources u Directs the processor when executing other programs

Operating System u Making computing power available to users by controlling the hardware u a program that controls execution of application programs u an interface between the user and hardware u Directs the processor in the use of system resources u Directs the processor when executing other programs

Services Provided by the OS u Facilities u editors, u Program u loading u Access u deals u System for Program creation compilers, linkers, and debuggers execution in memory, I/O and file initialization to I/O and files with the specifics of I/O and file formats access u Protection of access to resources and data u Resolves conflicts for resource contention

Services Provided by the OS u Facilities u editors, u Program u loading u Access u deals u System for Program creation compilers, linkers, and debuggers execution in memory, I/O and file initialization to I/O and files with the specifics of I/O and file formats access u Protection of access to resources and data u Resolves conflicts for resource contention

Services Provided by the OS u Error Detection u internal and external hardware errors memory error u device failure u u software errors arithmetic overflow u access forbidden memory locations u u Inability of OS to grant request of application u Error Response u simply report error to the application u Retry the operation u Abort the application

Services Provided by the OS u Error Detection u internal and external hardware errors memory error u device failure u u software errors arithmetic overflow u access forbidden memory locations u u Inability of OS to grant request of application u Error Response u simply report error to the application u Retry the operation u Abort the application

Services Provided by the OS u Accounting u collect statistics on resource usage u monitor performance (eg: response time) u used for system parameter tuning to improve performance u useful for anticipating future enhancements u used for billing users (on multiuser systems)

Services Provided by the OS u Accounting u collect statistics on resource usage u monitor performance (eg: response time) u used for system parameter tuning to improve performance u useful for anticipating future enhancements u used for billing users (on multiuser systems)

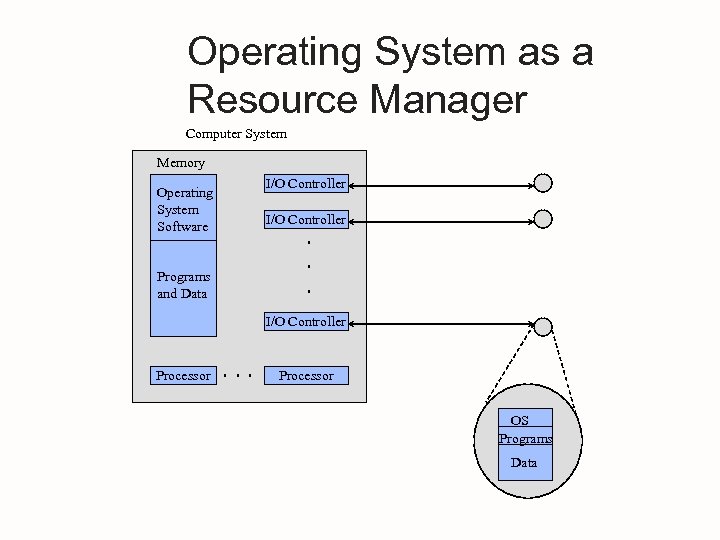

Operating System as a Resource Manager Computer System Memory I/O Controller Operating System Software I/O Controller . . . Programs and Data I/O Controller Processor . . . Processor OS Programs Data

Operating System as a Resource Manager Computer System Memory I/O Controller Operating System Software I/O Controller . . . Programs and Data I/O Controller Processor . . . Processor OS Programs Data

Ability to Evolve u Must be able to adapt to hardware upgrades and new types of hardware. Examples: u Character vs graphic terminals u Introduction of paging hardware u Must be able to offer new services, eg: internet support

Ability to Evolve u Must be able to adapt to hardware upgrades and new types of hardware. Examples: u Character vs graphic terminals u Introduction of paging hardware u Must be able to offer new services, eg: internet support

Major Achievements u Processes u Memory Management u Information protection and security u Scheduling and resource management u System structure

Major Achievements u Processes u Memory Management u Information protection and security u Scheduling and resource management u System structure

Memory Management u Process isolation u Automatic allocation and management u Support for modular programming u Protection and access control u Long-term storage

Memory Management u Process isolation u Automatic allocation and management u Support for modular programming u Protection and access control u Long-term storage

Virtual Memory u Allows programmers to address memory from a logical point of view u While program is running portions of the program and data are kept in blocks on disk

Virtual Memory u Allows programmers to address memory from a logical point of view u While program is running portions of the program and data are kept in blocks on disk

File System u Implements long-term store u Information stored in named objects called files

File System u Implements long-term store u Information stored in named objects called files

Categories of Security and Protection u Access control u regulate user access to the system u Information flow control u regulate flow of data within the system and its delivery to users u Certification u proving that access and flow control perform according to specifications

Categories of Security and Protection u Access control u regulate user access to the system u Information flow control u regulate flow of data within the system and its delivery to users u Certification u proving that access and flow control perform according to specifications

Scheduling and Resource Management u Fairness u give equal and fair access to all processes u Differential responsiveness u discriminate jobs between different classes of u Efficiency u maximize throughput, minimize response time, and accommodate as many uses as possible

Scheduling and Resource Management u Fairness u give equal and fair access to all processes u Differential responsiveness u discriminate jobs between different classes of u Efficiency u maximize throughput, minimize response time, and accommodate as many uses as possible

Characteristics of Modern Operating Systems u Microkernel architecture u assigns only a few essential functions to the kernel u address space u interprocess communication (IPC) u basic scheduling

Characteristics of Modern Operating Systems u Microkernel architecture u assigns only a few essential functions to the kernel u address space u interprocess communication (IPC) u basic scheduling

Characteristics of Modern Operating Systems u Multithreading u process u is divided into threads that can run simultaneously u Process is a collection of one or more threads u Thread u dispatchable unit of work u executes sequentially and is interruptable

Characteristics of Modern Operating Systems u Multithreading u process u is divided into threads that can run simultaneously u Process is a collection of one or more threads u Thread u dispatchable unit of work u executes sequentially and is interruptable

Characteristics of Modern Operating Systems u Symmetric u there multiprocessing are multiple processors u these processors share the same main memory and I/O facilities u All processors can perform the same functions

Characteristics of Modern Operating Systems u Symmetric u there multiprocessing are multiple processors u these processors share the same main memory and I/O facilities u All processors can perform the same functions

Characteristics of Modern Operating Systems u Distributed u provides operating systems the illusion of a single main memory u used for distributed file system

Characteristics of Modern Operating Systems u Distributed u provides operating systems the illusion of a single main memory u used for distributed file system

Characteristics of Modern Operating Systems u Object-oriented u used design for adding modular extensions to a small kernel u enables programmers to customize an operating system without disrupting system integrity

Characteristics of Modern Operating Systems u Object-oriented u used design for adding modular extensions to a small kernel u enables programmers to customize an operating system without disrupting system integrity